# New Jersey Semi-Conductor Products, Inc.

20 STERN AVE. SPRINGFIELD, NEW JERSEY 07081 U.S.A. TELEPHONE: (973) 376-2922

(212) 227-6005

FAX: (973) 376-8960

3N128

### SILICON N-CHANNEL MOS FIELD-EFFECT TRANSISTOR

... designed for VHF amplifier and oscillator applications in communications equipment.

- High Forward Transadmittance |yfs| = 5000 μmhos (Min) @ f = 1.0 kHz

- Low Input Capacitance —

C<sub>iss</sub> = 7.0 pF (Max) @ f = 1.0 MHz

- Low Noise Figure –

NF = 5.0 dB (Max) @ f = 200 MHz

- High Power Gain —

PG = 13.5 dB (Min) @ f = 200 MHz

- Complete "y" Parameter Curves

- Third Order Intermodulation Distortion Performance Curve Provided

N-CHANNEL MOS FIELD-EFFECT TRANSISTOR

### \* MAXIMUM RATINGS

| Rating                                                         | Symbol                           | Value       | Unit                     |  |

|----------------------------------------------------------------|----------------------------------|-------------|--------------------------|--|

| Drain-Source Voltage                                           | V <sub>DS</sub>                  | +20         | Vdc                      |  |

| Drain-Gate Voltage                                             | V <sub>DG</sub>                  | +20         | Vdc                      |  |

| Gate-Source Voltage                                            | VGS                              | ±10         | Vdc                      |  |

| Drain Current                                                  | ĭD                               | 50          | mAdc                     |  |

| Power Dissipation ® T <sub>A</sub> = 25°C<br>Derate above 25°C | PD                               | 330<br>2.2  | mW<br>mW/ <sup>Q</sup> C |  |

| Operating and Storage Junction<br>Temperature Range            | ⊤ <sub>J</sub> ,T <sub>stg</sub> | -65 to +175 | °C                       |  |

\*Indicates JEDEC Registered Data.

#### HANDLING PRECAUTIONS

MOS field-effect transistors have extremely high input resistance. They can be damaged by the accumulation of excess static charge. Avoid possible damage to the devices while handling, testing, or in actual operation, by following the procedures outlined below:

- To avoid the build-up of static charge, the leads of the devices should remain shorted together with a metal ring except when being tested or used.

- 2. Avoid unnecessary handling. Pick up devices by the case instead of the leads.

- Do not insert or remove devices from circuits with the power on because transient voltages may cause permanent damage to the devices.

NJ Semi-Conductors reserves the right to change test conditions, parameter limits and package dimensions without notice. Information furnished by NJ Semi-Conductors is believed to be both accurate and reliable at the time of going to press. However, NJ Semi-Conductors assumes no responsibility for any errors or omissions discovered in its use. NJ Semi-Conductors encourages customers to verify that datasheets are current before placing orders.

#### \*ELECTRICAL CHARACTERISTICS (T<sub>A</sub> = 25°C unless otherwise noted)

| Characteristic                                                                                                                              | Symbol               | Min      | Max         | Unit  |

|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------|-------------|-------|

| OFF CHARACTERISTICS                                                                                                                         |                      |          |             |       |

| Gate-Source Breakdown Voltage (1)<br>(I <sub>G</sub> = -10 μAdc, V <sub>DS</sub> = 0)                                                       | V(BR)GSS             | -50      | -           | Vdc   |

| Gate-Source Cutoff Voltage<br>(V <sub>DS</sub> = 15 Vdc, I <sub>D</sub> = 50 μAdc)                                                          | VGS(off)             | -0.5     | -8.0        | Vdc   |

| Gate Reverse Current<br>$(V_{GS} = -8.0 \text{ Vdc}, V_{DS} = 0)$<br>$(V_{GS} = -8.0 \text{ Vdc}, V_{DS} = 0, T_{A} = 125^{\circ}\text{C})$ | GSS                  | _        | 0.05<br>5.0 | nAdc  |

| ON CHARACTERISTICS                                                                                                                          |                      |          |             |       |

| Zero-Gate-Voltage Drain Current (2)<br>(VDS = 15 Vdc, VGS = 0)                                                                              | DSS                  | 5.0      | 25          | mAdc  |

| SMALL-SIGNAL CHARACTERISTICS                                                                                                                |                      |          |             |       |

| Forward Transadmittance<br>(V <sub>DS</sub> = 15 Vdc, I <sub>D</sub> = 5.0 mAdc, f = 1.0 kHz)                                               | V <sub>fs</sub>      | 5000     | 12,000      | μmhos |

| Forward Transconductance<br>(V <sub>DS</sub> = 15 Vdc, i <sub>D</sub> = 5.0 mAdc, f = 200 MHz)                                              | Re(yfs)              | 5000     | _           | μmhos |

| Output Conductance<br>(V <sub>DS</sub> = 15 Vdc, I <sub>D</sub> = 5.0 mAdc, f = 200 MHz)                                                    | Re(y <sub>OS</sub> ) |          | 500         | μmhos |

| Input Conductance<br>(V <sub>DS</sub> = 15 Vdc, I <sub>D</sub> = 5.0 mAdc, f = 200 MHz)                                                     | Re(y <sub>is</sub> ) | <u> </u> | 800         | μmhos |

| Input Capacitance<br>(V <sub>DS</sub> = 15 Vdc, I <sub>D</sub> = 5.0 mAdc, f = 1.0 MHz)                                                     | Ciss                 | _        | 7.0         | pF    |

| Reverse Transfer Capacitance<br>(V <sub>DS</sub> = 15 Vdc, I <sub>D</sub> = 5.0 mAdc, f = 1.0 MHz)                                          | C <sub>rss</sub>     | 0.05     | 0.35        | pF    |

| Noise Figure $(V_{DS} = 15 \text{ Vdc}, I_D = 5.0 \text{ mAdc}, f = 200 \text{ MHz})$                                                       | NF                   | =        | 5.0         | dB    |

| Power Gain<br>(V <sub>DS</sub> = 15 Vdc, I <sub>D</sub> = 5.0 mAdc, f = 200 MHz)                                                            | PG                   | 13.5     | 23          | dB    |

#### \*Indicates JEDEC Registered Data.

- (1) Caution Destructive Test, can damage gate oxide beyond operation.

- (2) Pulse Test: Pulse Width = 300 μs, Duty Cycle = 2.0%.

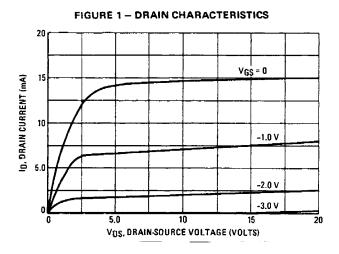

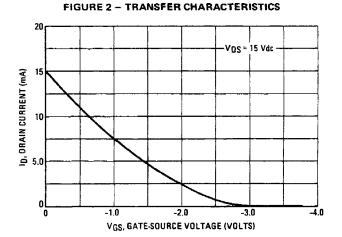

# TYPICAL CHARACTERISTICS (TA = 25°C)