WD83C690 Ethernet LAN Controller

# TABLE OF CONTENTS

| 1.0 Description and Application                       |

|-------------------------------------------------------|

| 1.1 Features                                          |

| 1.2 System Interface                                  |

| 2.0 Operational Description                           |

| 2.1 Receive Feedback Multiplexor                      |

| 2.2 Carrier Sensing                                   |

| 2.3 CRC Checker                                       |

| 2.4 Receive Deserializer                              |

| 2.5 Address Recognition Logic                         |

| 2.6 Receive Protocol Finite State Machine             |

| 2.7 Receiver Error Counters                           |

| 2.8 FIFOs                                             |

| 2.9 Transmitter Protocol Finite State Machine (TPFSM) |

| 2.10 Transmitter Serializer                           |

| 2.11 Transmitter CRC Generator                        |

| 2.12 Preamble Generator                               |

| 2.13 Jam Generator                                    |

| 2.14 Serial Stream Mux                                |

| 2.14 Senai Stream Mux                                 |

| 2.16 Collision Detection Logic                        |

| 2.17 DMA Controller                                   |

| 2.17 DMA controller                                   |

| 2.19 Bus Interface and Internal Bus Arbitrator        |

| 2.19 Bus internace and internal Bus Arbitrator        |

|                                                       |

| 3.0 Operation of the Serial Interface Sections        |

| 3.1 Receive Functions                                 |

| 3.1.1 Receiving a Frame40-6                           |

| 3.1.2 End of Frame                                    |

| 3.2 Transmitter                                       |

| 3.2.1 Initialization for Transmission40-9             |

| 3.2.2 Transmission Process40-9                        |

| 3.2.3 Transmit Underrun40-9                           |

| 3.2.4 Collisions                                      |

| 3.2.5 Extensions to the 802.3 10base5 Protocol40-9    |

| 4.0 Memory Interface                                  |

| 4.1 Memory Access Time                                |

| 4.2 DMA Bursts                                        |

| 4.3 Transmit Packet Buffering                         |

| 4.4 Receive Packet Buffering                          |

# APPENDICES

| Appendix A Hardware Characteristics  | 40-17 |

|--------------------------------------|-------|

| Appendix B Register Designations     | 40-18 |

| Appendix C Pin Designations          | 40-31 |

| Appendix D Operating Characteristics | 40-35 |

# LIST OF ILLUSTRATIONS

| 1-1  | WD83C690 System Interface                             | 40-2  |

|------|-------------------------------------------------------|-------|

| 2-1  | General System Block Diagram                          | 40-6  |

| 4-1  | Receiver Buffer Format                                | 40-11 |

| 4-2  | Receiver Buffer Structure                             | 40-12 |

| 4-3  | Receiver Buffer Ring in Typical Setup Configuration   | 40-14 |

| 4-4  | Receiver Buffer Ring, Typical Operating Configuration | 40-14 |

|      | Same Buffer Ring, After Removing One Packet           |       |

| 4-6  | Full Receiver Buffer Ring, No Overflow                | 40-15 |

| 4-7  | Receiver Buffer Ring Verging on Overflow Condition    | 40-16 |

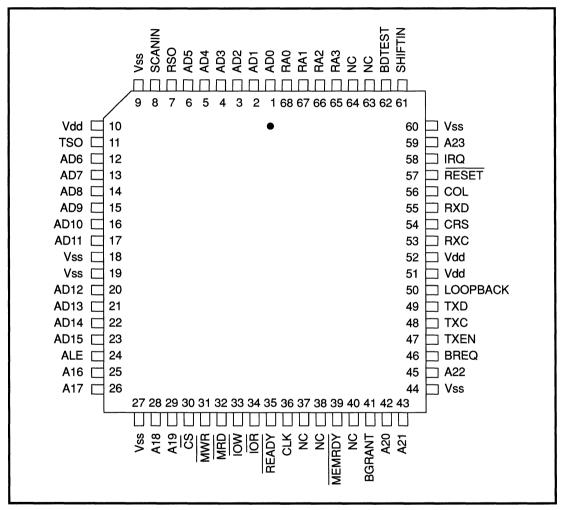

| C-1  | 68-Pin Ethernet Controller                            | 40-31 |

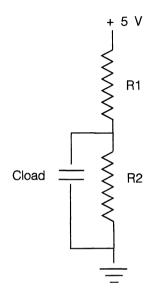

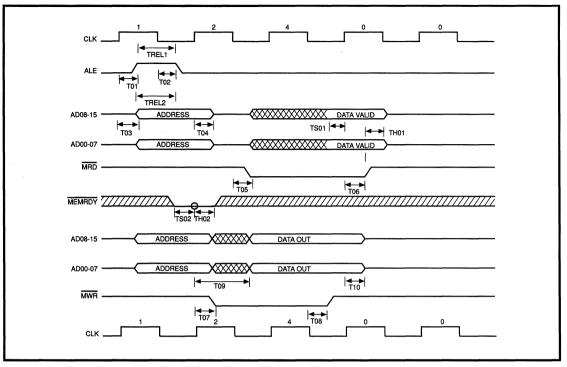

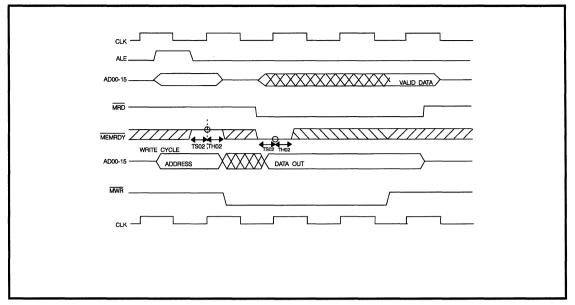

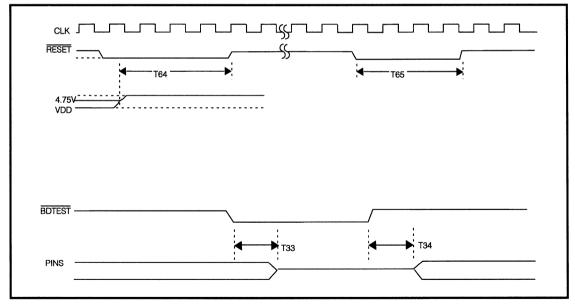

| D-1  | Host Access Timing                                    | 40-43 |

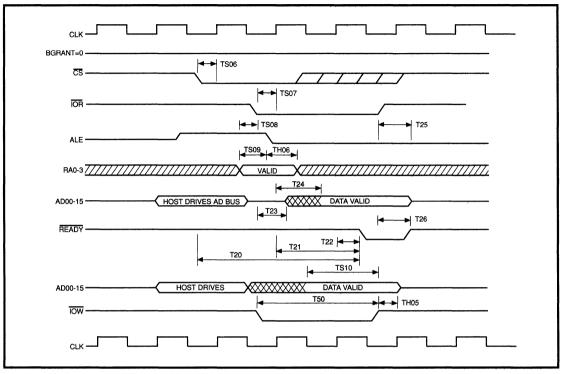

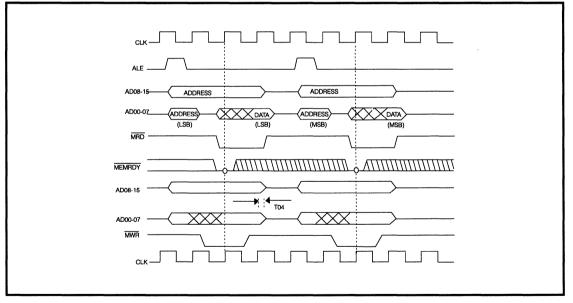

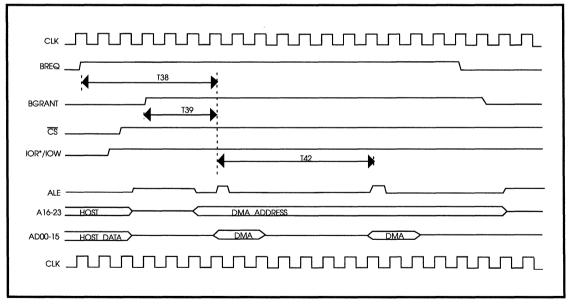

| D-2  | 16-Bit Bus, 4-Cycle DMA Read and Write Timing         | 40-44 |

|      | 16-Bit Bus, 5-Cycle DMA Read and Write Timing         |       |

|      | 8-Bit Bus, DMA Read and Write Timing                  |       |

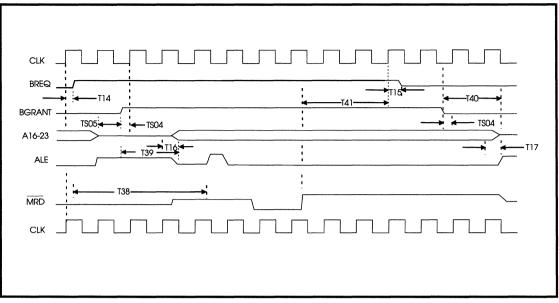

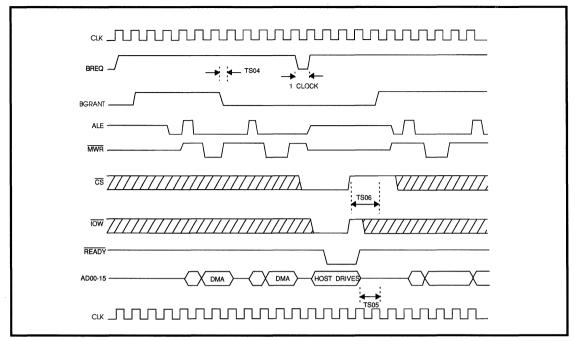

| D-5  | Bus Request Timing for Normal DMA Burst               | 40-46 |

| D-6  | 16-Bit Bus DMA Burst Timing                           | 40-46 |

| D-7  | DMA Burst Timing, Bus Busy                            | 40-47 |

| D-8  | 8-Bit Bus, Interrupted DMA Burst                      | 40-48 |

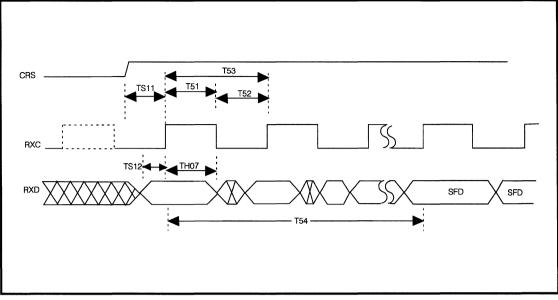

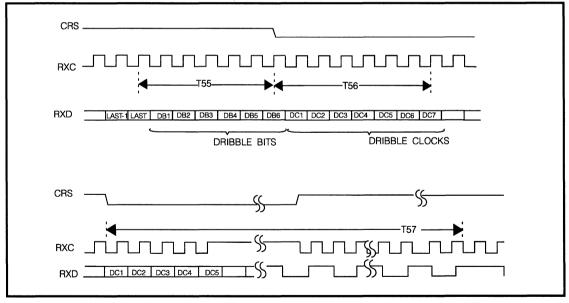

| D-9  | Receiver Serial Timing, Start of Frame Reception      | 40-49 |

|      | 0 Receiver Serial Timing,End of Frame                 |       |

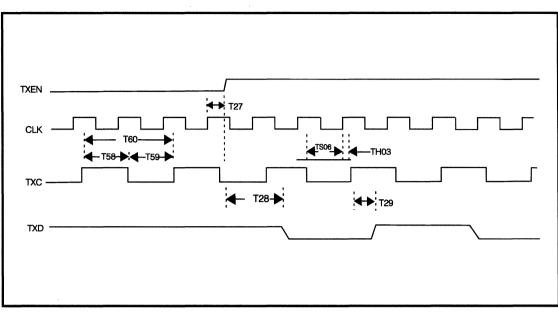

|      | 1 Transmit Serial Timing, Start of Frame              |       |

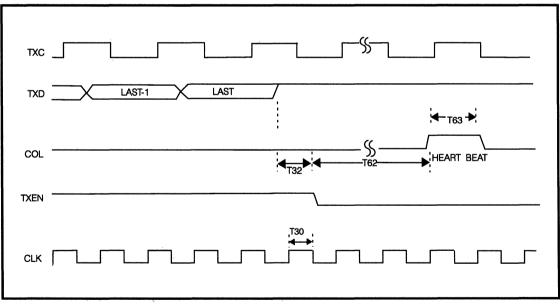

| D-1: | 2 Transmit Serial Timing, End of Frame                | 40-50 |

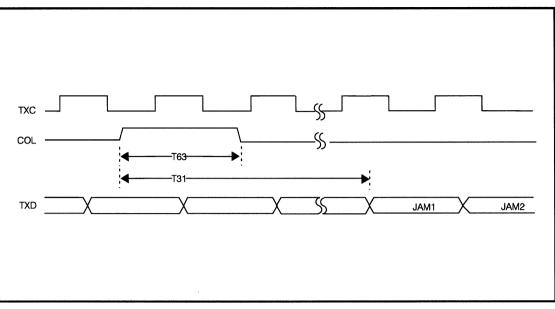

|      | 3 Transmit Serial Timing, Collision                   |       |

| D-1- | 4 Other Timing                                        | 40-51 |

## LIST OF TABLES

| A-1 Summary of Hardware Characteristics      | 40-17 |

|----------------------------------------------|-------|

| B-1 Register Addresses                       | 40-18 |

| B-2 Alphabetical Register Descriptions       | 40-20 |

| C-1 Pin Designations                         | 40-32 |

| D-1 Output Timing                            | 40-36 |

| D-2 Input Timing Setup and Hold Requirements | 40-40 |

| D-3 List of Timing Diagrams                  | 40-42 |

## 1.0 DESCRIPTION AND APPLICATION

The WD83C690 Ethernet LAN Controller (ELC) is a VLSI device designed to interface with networks such as Ethernet, Cheapernet, and StarLAN. Functionally similar to the National DP8390 device, the WD83C690 incorporates an original architecture and provides several new registers (for en-hancements, block address, and test control). The device is implemented in a single-clock, singlephase synchronous design, with the exception of serial portions of the receiver and transmitter. The WD83C690's signal functions, polarity requirements, and timings are compatible with the WD83C583 and WD83C593 bus interface devices.

## **1.1 FEATURES**

- Meets the IEEE 802.3 protocol for networks such as Ethernet, Cheapernet, and StarLAN

- Provides direct memory address (DMA) channel for transferring data between memory and the host

- Implements an original, sophisticated architecture in standard cell technology

- Provides programmable wait states and slot times

- · Provides full duplex loopback capability

- Requires single, 5V power supply

- Supports physical, promiscuous, and broadcast address filtering

- Provides efficient, versatile buffer management

**4** N

### 1.2 SYSTEM INTERFACE

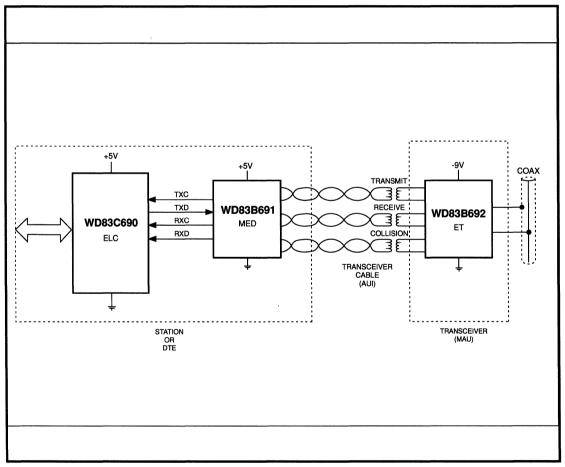

The WD83C690 is part of a three-device set that implements the complete IEEE 802.3-compatible network node electronics. The WD83C691 Manchester Encoder/Decoder (MED) and the WD83B692 Ethernet Transceiver (ET) comprise the other two devices in the set. The WD83C691 provides the Manchester encoding/decoding functions, while the WD83B692 serves as a coaxial cable line driver/receiver. Figure 1-1 illustrates how the devices interface.

FIGURE 1-1. WD83C690 SYSTEM INTERFACE

## 2.0 OPERATIONAL DESCRIPTION

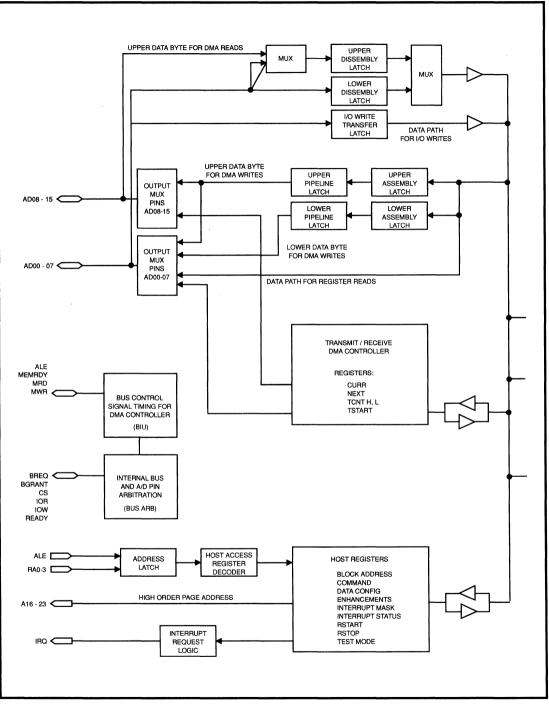

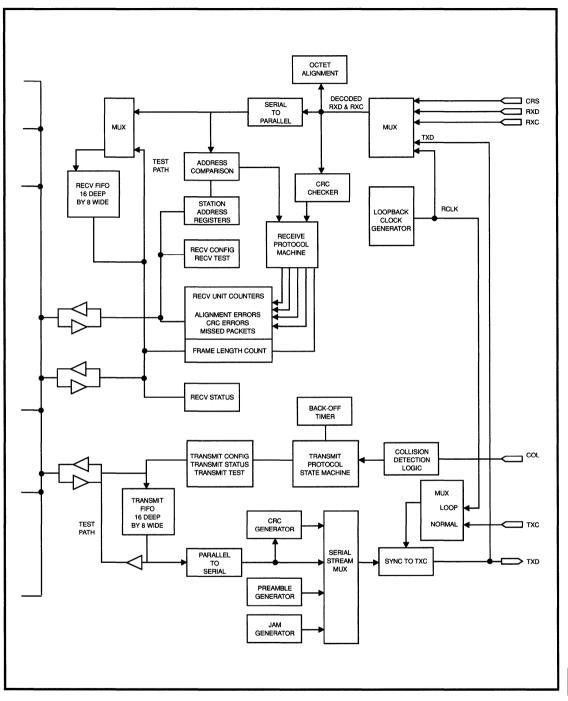

This section describes the functional blocks that comprise the Ethernet LAN controller. A general system block diagram is shown in Figure 2.1. Sections 3 and 4 provide more detailed explanations of the receive and transmit functions and memory interface.

## 2.1 RECEIVE FEEDBACK MULTIPLEXOR

For testing purposes, an internal multiplexor at the network interface end of the receiver permits the loopback of transmitted data, and the use of transmit enable as a carrier sense signal. The multiplexor can be programmed via the transmit configuration register.

#### **2.2 CARRIER SENSING**

Carrier sensing is done externally and brought into the WD83C690 through the CRS pin. Received data and clock are brought in through the RXD and RXC pins, respectively, and feed the CRC checker, the octet alignment circuit, and the serial-to-parallel converter.

#### 2.3 CRC CHECKER

The receiver section performs the cyclic redundancy check (CRC) for the incoming serial data. The CRC computation includes the address, data, and CRC fields. It excludes the preamble and SFD.

The CRC polynomial used is AUTODIN II (X32 + X26 + X23 + X22 + X16 + X12 + X11 + X10 + X8 + X7 + X5 + X4 + X2 + X1 + 1).

#### 2.4 RECEIVE DESERIALIZER

The receive deserializer clocks incoming bits into an eight-bit serial-to-parallel shift register, and, when an octet is complete, loads the parallel data into the receiver "first in, first out" buffer (FIFO). Octet alignment is determined by a synchronization circuit which detects the start of frame delimiter (SFD).

## 2.5 ADDRESS RECOGNITION LOGIC

The destination address is compared to a 6-byte station address stored in the internal registers, and, if all bytes match (or if promiscuous mode is enabled), the frame is received. When multicast addressing is enabled, only the individual/group bit of the destination address is checked. No filtering of group addresses is done. Broadcast frames are received when the broadcast enable bit is active.

If the address is rejected, the receive FIFO is cleared and none of the frame is stored. If the address is accepted, buffering of the frame begins.

#### 2.6 RECEIVE PROTOCOL FINITE STATE MACHINE (RPFSM)

The Receive Protocol Finite State Machine (RPFSM) determines whether the incoming frame will be saved in memory, and coordinates the operation of all other blocks in the receiver section. This involves generating status information regarding each frame (the information is placed in the receiver status register) and keeping track of the length of the frame via a 16-bit-wide frame length byte counter attached to the state machine. The block is controlled by the receiver configuration register and the START and STOP bits from the command register. The receiver error counters are also under control of this circuit.

#### 2.7 RECEIVER ERROR COUNTERS

There are three error counters in the receiver section: the CRC error counter, the frame alignment error counter, and the missed packet counter. Each counter is eight bits wide and can be incremented up to 255, where it remains until the counter clears (when the register is read or the device reset).

The CRC error counter, under control of the receive protocol finite state machine, is incremented when a received frame's computed CRC does not match the appended CRC.

The frame alignment error counter is advanced when a frame with too many dribble bits and a CRC error at the same time is received.

The missed packet counter is incremented when a frame that would ordinarily be stored in memory was not stored (either because the receiver was operating in monitor mode, or because there was insufficient memory to store the entire frame).

## 2.8 FIFOS

The transmitter and receiver sections have similar, but independent, 16-byte deep FIFOs. These FIFOs have a programmable threshold level that allows the transmit receive (TR) direct memory access controller (TRDMA) to determine when there is a need to move data between the WD83C690 and memory.

#### 2.9 TRANSMITTER PROTOCOL FINITE STATE MACHINE (TPFSM)

The transmitter protocol finite state machine (TPFSM) coordinates the operation of all blocks that comprise the transmitter section. It decides when to transmit, when to defer transmission, and, in the event of a collision, when to back off and attempt to transmit again. The transmit configuration register controls the operation of this state machine, which updates the transmit status register after each attempt to send a frame.

#### 2.10 TRANSMIT SERIALIZER

The transmit serializer converts the 8-bit parallel data from the transmit FIFO into serial data. Serial data is clocked out of the TXD pin (least significant bit first) by the rising edge of an external clock at the TXC pin.

## 2.11 TRANSMITTER CRC GENERATOR

Using the same polynomial as the receiver CRC checker, the transmit section generates CRC serially and appends it to each outgoing frame. (CRC is clocked-out most significant bit first.)

## 2.12 PREAMBLE GENERATOR

The preamble generator block generates a data pattern of alternating "1" and "0" bits.

#### 2.13 JAM GENERATOR

This block generates a pattern of consecutive "1" bits. It drives the TXD pin when a collision is detected.

### 2.14 SERIAL STREAM MUX

Using the serial stream multiplexor, the TPFSM composes each frame from its constituent parts.

#### 2.15 SYNC-TO-TXC

To ensure minimal output jitter, the transmit data stream is reclocked to the rising edge of TXC prior to driving the pin.

#### 2.16 COLLISION DETECTION LOGIC

Collisions are sensed externally during transmission, then input through the COL pin.

#### 2.17 DMA CONTROLLER

There is an internal direct memory access (DMA) controller, TRDMA, which moves packets between buffer memory and the WD83C690.

The DMA generates 16-bit addresses, supplemented by 8 bits of static address in the high order positions (A16-23). The DMA controller supports memory cycles as short as 200 nsec, which can be slowed down using the MEM-READY pin or by programming a default number of wait states into the configuration register.

#### 2.18 ASSEMBLY AND DISASSEMBLY LATCHES

The TRDMA does all of its transfers as pairs of 8-bit bytes. The assembly and dissassembly latches match the internal 8-bit data path to the external data bus. When interfacing to a 16-bit bus, the assembly latches combine two 8-bit words to form a 16-bit word; when interfacing with an 8-bit bus, they supply the two consecutive bytes of a transfer. The disassembly latches perform the opposite function.

#### 2.19 BUS INTERFACE AND INTERNAL BUS ARBITRATOR

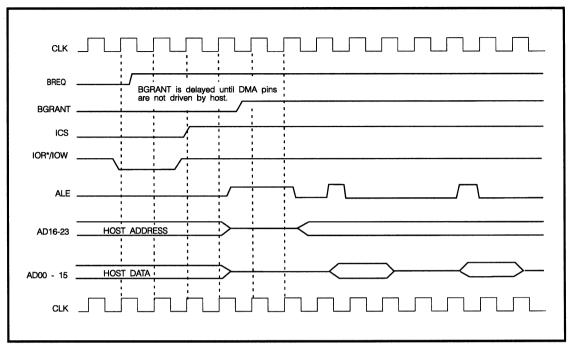

The bus interface unit (BIU) and internal bus arbitrator control access to the WD83C690's internal registers and ensure that the device does not attempt a DMA transfer until it has access to the memory bus. The BIU transfers data from buffer memory to the internal disassembly latches and from the internal assembly latches to buffer memory. It generates the bus request (BREQ), memory strobes (MRD and MWR) and the address strobe (ALE).

To control the initiation of a transfer and insertion of wait states, the BIU observes the bus grant (BGRANT) and memory ready (MEMRDY) signals.

Until BGRANT becomes true, the memory strobes, address outputs, and ALE outputs are tri-stated. Once BGRANT is issued, the host must not drive the address, data, ALE, or memory strobes until BREQ is dropped and BGRANT taken away at the end of the DMA burst. Failure to adhere to this rule will result in contention on the lines and corruption of the data transferred. Refer to the timing diagrams in Appendix D for more details.

When the DMA bursts are complete and BGRANT is negated, the host can access the internal bus. Although BREQ may again become active in response to new DMA needs, the arbitration logic permits access until BGRANT becomes true. The internal arbitrator generates the READY signal to tell the host that the requested I/O access has been made and the internal bus is available.

The host may force the WD83C690 to interrupt a DMA burst by removing the BGRANT signal while BREQ is still active. When this happens, the BIU completes the current byte or word transfer, then relinquishes the bus by dropping BREQ for one clock. The internal bus arbitration unit disables the DMA until BGRANT is again true, at which time, the burst continues where it left off.

### 2.20 ACCESSING INTERNAL REGISTERS

To access an internal register, the host must assert the chip select (CS) signal and wait until READY is asserted before driving the bus. When the WD83C690 is not involved in a DMA operation, it is not necessary to wait for READY to be asserted prior to driving the address, ALE, and data lines. CS must be maintained throughout the access.

In multiplexed bus applications, ALE latches the register address into the WD83C690. In non-multiplexed bus applications, ALE should be driven high or pulled up during register access to allow the address to flow through the internal transparent latch.

To read from a register, IOR must be asserted by the host (either before or after CS). It is recognized by the internal bus arbitrator (BUSARB) circuit, which enables data flow from the addressed register to the AD00-07 pins. During read operations (which are always done through the AD00-07 pins), AD08-15 are tri-stated. READY indicates when the host can sample data and terminate the read operation.

To write to a register, IOW must be asserted by the host and recognized by the internal BUSARB. When the bus is free for the transfer, READY is asserted and the register address is latched internally. Data is latched into an intermediate transfer latch with the trailing edge of IOW, and, two clocks later, transferred to the destination register.

FIGURE 2-1. GENERAL SYSTEM BLOCK DIAGRAM (Continued)

40

## 3.0 OPERATION OF THE SERIAL IN-TERFACE SECTIONS

When the stop bit in the command register is cleared and the start bit is set, the transmit and receive sections are enabled. This permits the serial interface sections to recognize incoming frames and to act on requests for transmitting frames. Once enabled, the serial interface sections remain enabled until the stop bit is set. Clearing the start bit does not disable the serial interface.

If the stop bit is set while the transmit and receive sections are operational, they will finish handling the current frame, then go to a soft reset condition and ignore incoming frames and requests for transmission. Before the transmitter stops, however, it will complete the retransmission of any colliding packets. When both sections are stopped, the RST bit in the interrupt status register is set (although the DMA controller may remain active), and the receiver status registers are reinitialized.

## 3.1 RECEIVE FUNCTIONS

This section describes how the receiver section operates.

## 3.1.1 RECEIVING A FRAME

The preamble field is used to train the external Manchester decoder and to detect carrier. If carrier sense (CRS) is true, the preamble passes through the receive deserializer which discards it while searching for the consecutive "1" bits that mark the start-frame-delimiter (SFD). The deserializer loads the receive FIFO with octets (bytes), beginning with the first bit after SFD.

While the destination address (DA field) is being checked for recognition, the receive DMA is disabled. If the frame is accepted, the DMA is enabled, and when the FIFO fills to the programmed burst level, transfer to memory begins. If the frame's address is not accepted, the receive unit clears out the FIFO and waits for the start of the next frame.

The destination address, source address, and data fields are passed to buffer memory. In some protocols, the first 2 bytes of the data field denote a frame length. These bytes are not interpreted by the WD83C690, but treated as ordinary data.

## 3.1.2 END OF FRAME

Upon loss of carrier sense, dribble clocks (receive clocks that occur after the loss of carrier) on the RXC pin flush the remainder of the received frame through the deserializer and CRC checker. The CRC of all received octets is computed and compared to the CRC at the end of the frame, and the result is recorded in the receiver status register. The CRC from each received frame is sent to memory with the frame via DMA, and included in the byte count posted in the buffer header.

The deserializer counts the number of bits left over after the last complete octet. If the number is greater than 6, a frame alignment error is reported.

If the receive unit detects errors in the frame, it may abort reception, depending on how the bits, "save errored packets" and "accept runt frames", have been configured. If reception is aborted, the DMA controller stops sending bytes to the buffer, the receive unit clears out the FIFO, the receive status register (RSR) and the interrupt status register (ISR) are updated, and the receive unit waits for the next frame to begin.

For frames that are not accepted, a header is not posted, and the previous contents of the header location remain unchanged. We recommend that the header portions of recycled buffers be cleared out so that they are not subject to misinterpretation during subsequent host processing.

The received packet length must be less than 65,024 bytes, including DA, SA, data, and CRC. In addition, the buffer ring must have enough space for the entire frame and a 4-byte header. Packets larger than the available buffer space cannot be received, regardless of the SEP bit in the RECEIVE CONFIG register. Such frames are posted as ring over-writes and cause the over-write (OVW) interrupt to be set. Receiver interrupts (RXE, PRX) are posted after the frame has been completely posted to memory by DMA. If DMA aborts, these interrupts are not set for the current frame (if set previously, they remain unchanged). Packets shorter than 64 bytes are received only when the "accept runts" bit is enabled.

#### **3.2 TRANSMITTER**

This section describes how the transmitter section operates.

#### 3.2.1 INITIALIZATION FOR TRANSMISSION

The host builds packets to be transmitted in buffer memory. These packets must include the DA, SA and data fields. CRC is not read from buffer memory unless CRC generation is disabled. If it is disabled, the user is expected to place the computed CRC in the last four bytes of memory with the bit order reversed so that when clocked out least significant bit first, the CRC is presented to the serial interface most significant bit first.

The transmit start and transmit length (TSTART and TLENGTH) registers must be properly programmed before the TXP bit in the command register is set by the host. Once the TXP bit is set, the transmit unit can request the frame from the TRDMA unit. TXP can be cleared only by the transmitter upon completion of an attempted transmission.

#### **3.2.2 TRANSMISSION PROCESS**

TRDMA fills the transmit FIFO with bursts of data until there is no room left for an entire data burst. Burst lengths of 2, 4, or 8 bytes are repeated until they result in a full FIFO. A burst length of 12 bytes stops TRDMA and leaves only 12 bytes in the FIFO. When all bursts are done, TRDMA notifies the transmit unit that the FIFO is ready for transmission to begin.

The transmit unit waits until the media is clear for transmission, then generates 62 bits of preamble and SFD. Following this operation, it pulls bytes out of the transmit FIFO, serializes them, shifts their bits to the TXD pin, and computes the packet's CRC. During this operation, the TRDMA monitors the condition of the FIFO to determine when there is room for other bursts of data. As soon as there is room, additional bursts are performed.

When the DMA has filled the transmit FIFO with the last byte of the packet, it sets a flag. The transmitter continues to pull data out of the FIFO until it becomes empty, which marks the end of the frame. CRC computation stops and the CRC is appended serially to the frame, most significant bit first.

#### **3.2.3 TRANSMIT UNDERRUN**

If the FIFO becomes empty before the internal flag is set, a transmit underrun condition results and a transmit error is posted. Transmission of the packet is aborted and an interrupt may be generated.

#### 3.2.4 COLLISIONS

When a collision is reported on the COL pin, the transmitter sends thirty-two "1" bits as a jam signal, terminates transmission, then tries again (up to 16 times).

If there are fewer than 16 retries, the transmitter randomly selects a backoff delay, in slot-time units, from the range,  $0 \le R < 2^{K}$  (where K is 10 or the number of retries, whichever is less). The transmitter requests retransmission of the frame from memory and delay is initiated. Note: in accord with the 802.3 specifications, the carrier sense is ignored during the last third of the interframe gap.

When retransmitting a frame, the DMA controller clears out the transmit FIFO, loads its pointer to the start of the frame in memory, and waits for the abort signal to subside. The FIFO is then loaded in the same manner as it was initially. If the maximum number of collisions (16) is exceeded, transmission is aborted without further retries or back-off delay.

#### 3.2.5 EXTENSIONS TO THE 802.3 10base5 PROTOCOL

The 802.3 10base5 protocol uses frame lengths between 64 and 4096 bytes, inclusive. The transmitter section can send frames containing more than 16 and fewer than 65,276 bytes in length. The ability to transmit shorter or longer frames may be useful in other variations of the 802.3 protocol.

To support these variations, the slot time is program-selectable (the choices are 256-, 512-, or 1024-bit times).

## 4.0 MEMORY INTERFACE

As previously noted, the DMA channel generates a 16-bit linear address which can be used with a static 8-bit upper address stored in a page register. This enables the WD83C690's 64-Kbyte address space to be positioned on any 64-Kbyte boundary within the host's 16-Mbyte address space.

#### 4.1 MEMORY ACCESS TIME

Once granted control of the memory bus, the DMA channel can perform memory accesses in as little as 200 nsec. The actual cycle time depends on the number of wait states requested by memory. Wait states add 50 nsec each to the cycle time. For systems in which memory access time is known at design time, a choice of 0, 1, 2, or 3 automatic wait states can be programmed into the enhancement register. Automatic wait states apply to all memory cycles, regardless of the direction in which the data is moving.

Wait states are also inserted when the MEMRDY line is pulled high, even if the automatic wait states have expired.

#### 4.2 DMA BURSTS

To economize on arbitration time, the TRDMA channel collects transfers into bursts of 2 bytes (1 word), 4 bytes (2 words), 8 bytes (4 words), or 12 bytes (6 words). The choices provide a trade-off between bus latency and efficiency. The same burst length applies to transmit and receive operations.

When a data burst is required, the BREQ line requests the memory bus. An external arbitrator drives BGRANT high, enabling the address pin drivers, and a multiplexed address is driven onto the bus. An ALE signal coordinates the external address latches. Data is then either driven out or read in. In byte mode operation, the evenly-addressed byte is always accessed first.

Provided that the BGRANT line remains high, the entire burst proceeds as back-to-back cycles without relinquishing the bus. The DMA controller, however, can be preempted on a word boundary by removing BGRANT. On completion of the present word transfer (or second byte of a paired-byte transfer), the WD83C690 tri-states its address and data drivers and suspends DMA operations. (While DMA is suspended, the device's registers can be accessed.) When BGRANT is asserted again the DMA process picks up where it left off. Be careful when preempting DMA bursts. If memory is not regained soon enough, FIFO overflow or underrun can result.

#### 4.3 TRANSMIT PACKET BUFFERING

A packet to be transmitted is placed by the host into buffer memory. The packet must include the DA, SA, and data fields. The preamble, SFD, and (normally) CRC are not included in the buffer. If CRC generation is suppressed, the CRC field for the packet is also supplied by the host. The packet is placed in a contiguous block of memory, starting on a 256-byte boundary.

Valid 802.3 packets have at least 48 bytes of data. If data with fewer bytes are to be transmitted on an 802.3 network, it is the host's responsibility to build a packet with pad data included. The WD83C690 can transmit frames of any programmed length, even those which are too short to be valid frames on an 802.3 network.

TRDMA transfers the number of bytes programmed into the transmit frame length high-and low-byte (TCNTH, TCNTL) register pair, starting from the address, TSTART, 00.

#### 4.4 RECEIVE PACKET BUFFERING

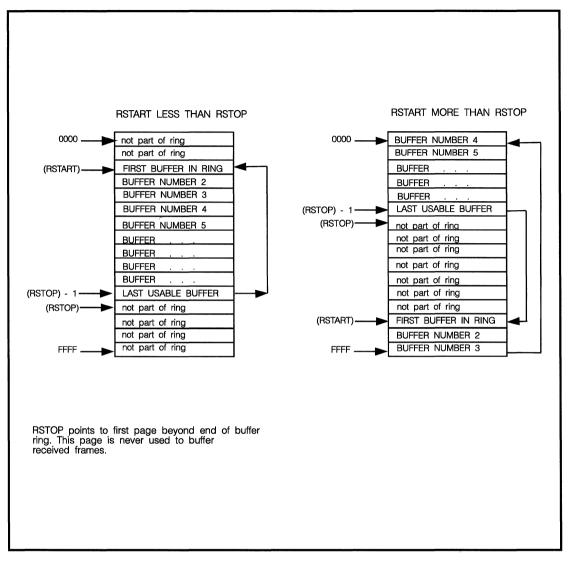

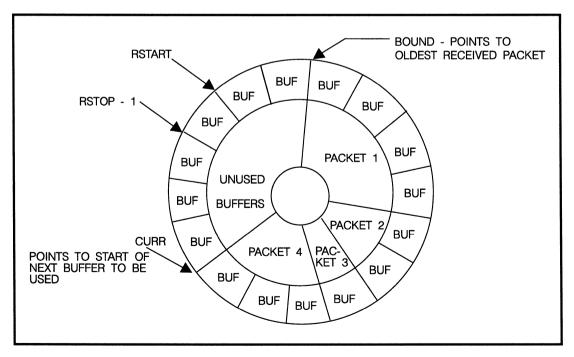

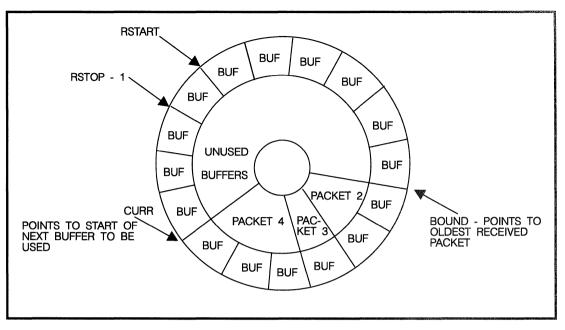

All received packets are stored in a circular set of 256-byte buffers. The values written into the receive start and receive stop page registers (RSTART and RSTOP) by the host when the WD83C690 is initialized determine the number and location of the buffers in the ring. RSTART points to the first buffer in the ring, and RSTOP points to the buffer after the last one in the ring.

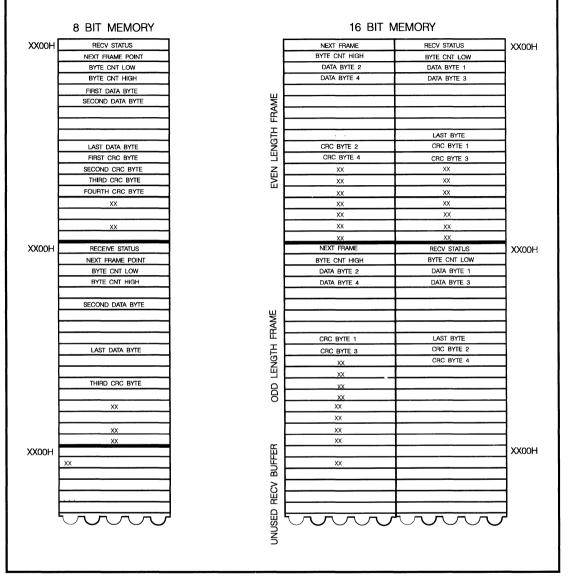

Each packet received is stored in one or more of these buffers, with a 4-byte header inserted at the start of the first buffer. Figure 4-1 illustrates the format of a received packet in memory.

## FIGURE 4-1. RECEIVER BUFFER FORMAT

Frames that extend to the buffer pointed to by RSTOP are continued in the buffer pointed to by RSTART. RSTOP can be either greater than RSTART + 1 or less than RSTART. Making RSTOP equal to RSTART or RSTART + 1 leads to unpredictable results. The relationship of these registers to ring placement in memory is illustrated in Figure 4-2.

Up to 254 buffers can be allocated to the ring. The receiver DMA uses as many as required to store a packet. This enables you to configure the device to receive frames nearly as long as 64K bytes, a

## FIGURE 4-2. RECEIVER BUFFER STRUCTURE

feature that may be useful in customized CSMA networks.

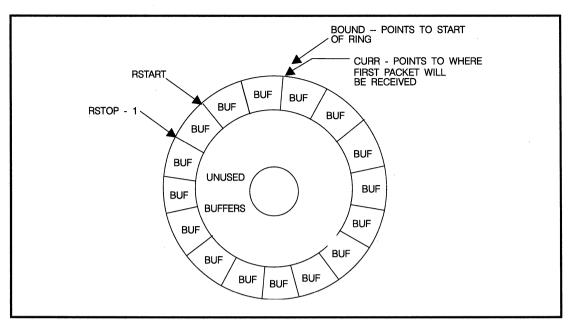

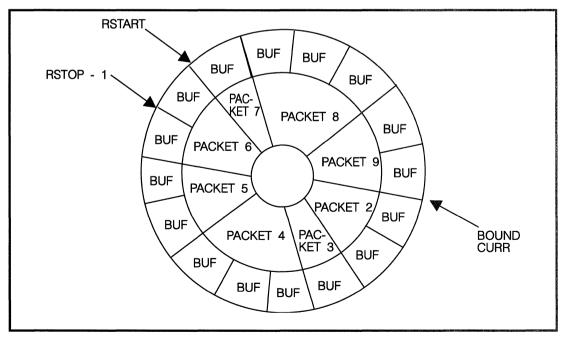

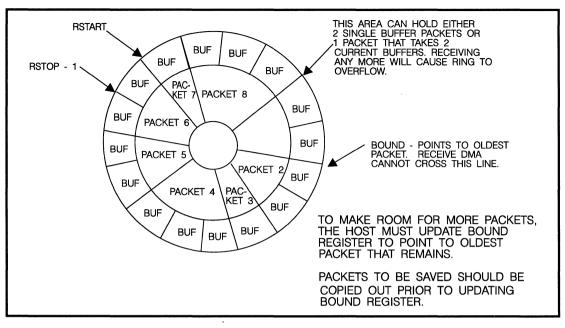

The receive DMA uses two additional registers to manage the buffer ring: the current (CURR) page register and the boundary (BOUND) page register. CURR points to the first buffer that is not part of a completely-received packet. When TRDMA is storing a frame, for example, CURR points to the start of the frame being stored. When TRDMA is not storing a frame, CURR points to the first buffer that will be used for the next frame to be received.

The receive boundary page register (BOUND) protects received frames from being overwritten by later frames. It points to the first buffer in the ring that is not to be overwritten. When the receive DMA process attempts to open the buffer pointed to by BOUND, reception is aborted and the overwrite (OVW) flag in the receiver status register is set.

Normally, BOUND is set up to point to the oldest received packet in the ring. The pointer is managed by the host. To discard an unwanted frame, the host simply rewrites BOUND to point to the next packet. To prevent misinterpretation of the discarded packet as a received packet, it is advisable to write zeros into the first word.

CURR is updated by the receive DMA after a frame is received. Conversely, BOUND is updated by host software after data is removed from the ring. When the last frame has been removed from the ring buffer, BOUND has the same value as CURR, and the ring is considered empty by the WD83C690.

The WD83C690 distinguishes between empty, full, and partially-filled buffer rings on the basis of the BOUND and CURR pointer values. Whenever BOUND is not equal to CURR, the buffer ring is assumed to be partially filled, starting with the buffer pointed to by BOUND and ending with the buffer prior to that pointed to by CURR. When BOUND equals CURR, the ring is full only if CURR was changed by the TRDMA controller more recently than BOUND was changed by the host. When BOUND is changed more recently than CURR, the ring is considered empty.

Note: you can initialize BOUND and CURR to point to any buffer within the ring, for example RSTART. Because RSTOP is outside the ring, the registers should not point to RSTOP. (This would result in the TRDMA storing frames outside the ring in an unpredictable manner.)

Provided the buffer is in the ring, you can give BOUND and CURR the same value. Figure 4-3 illustrates the relationship between pointers in a typical initialized ring. Figure 4-4 shows a ring that has received a few frames (this is its normal condition), and Figure 4-5 shows the same ring after proper removal of the oldest received packet. Figure 4-6 shows a ring that is completely full, and Figure 4-7 shows a ring on the verge of overflow.

FIGURE 4-3. RECEIVER BUFFER RING, TYPICAL SETUP CONFIGURATION

FIGURE 4-4. RECEIVER BUFFER RING, TYPICAL OPERATING CONFIG.

FIGURE 4-5. SAME BUFFER RING, AFTER REMOVING ONE PACKET

FIGURE 4-6. FULL RECEIVER BUFFER RING, NO OVERFLOW

40

FIGURE 4-7. RECEIVER BUFFER RING VERGING ON OVERFLOW

## A.0 APPENDIX A

## A.1 HARDWARE CHARACTERISTICS

| FEATURE                  | CHARACTERISTERIC(S)                                                                                                                                             |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Package                  | PLCC-68                                                                                                                                                         |

| Supplies                 | Single 5V supply                                                                                                                                                |

| Technology               | CMOS                                                                                                                                                            |

| IEEE 802.3 compatibility | Yes                                                                                                                                                             |

| Individual addresses     | Filters completely                                                                                                                                              |

| Group addresses          | No filter; only enable/disable                                                                                                                                  |

| Broadcast address        | Enable/disable                                                                                                                                                  |

| Collision detection      | External input                                                                                                                                                  |

| Buffer block size        | Fixed at 256 bytes                                                                                                                                              |

| Transmit buffers         | One frame, contiguous blocks                                                                                                                                    |

| Receive buffers          | Circular buffer<br>Many frames<br>65 Kbyte maximum frame size                                                                                                   |

| DMA channel              | Transmit/receive<br>8/16 bit data<br>Full duplex operation<br>Muxed address/data<br>Interruptible bursts<br>Programmable wait states<br>Programmable burst size |

| Memory addressing        | 64 Kbyte buffer region within<br>16 Mbyte address space.                                                                                                        |

| Loopback                 | Full duplex –allows reception of entire frame.                                                                                                                  |

| Clock relationships      | Device and transmit clocks must be synchronous.                                                                                                                 |

| Clock frequency          | Device clock must be 20 MHz. RXC and TXC may be 1,2, or 10 MHz.                                                                                                 |

## TABLE A-1. SUMMARY OF HARDWARE CHARACTERISTICS

## B.0 APPENDIX B

## **B.1 REGISTER DESIGNATIONS**

| REG<br>ADDR | PAGE 0<br>READ | PAGE 0<br>WRITE | PAGE 1<br>READ | PAGE 1<br>WRITE |

|-------------|----------------|-----------------|----------------|-----------------|

| 0           | COMMAND        | COMMAND         | COMMAND        | COMMAND         |

| 1           | TRINCRL        | RSTART          | STA0           | STA0            |

| 2           | TRINCRH        | RSTOP           | STA1           | STA1            |

| 3           | BOUND          | BOUND           | STA2           | STA2            |

| 4           | TSTAT          | TSTART          | STA3           | STA3            |

| 5.          | COLCNT         | TCNTL           | STA4           | STA4            |

| 6           | · .            | TCNTH           | STA5           | STA5            |

| 7           | INTSTAT        | INTSTAT         | CURR           | CURR            |

| 8           | -              | . —             | -              | -               |

| 9           |                |                 |                | -               |

| A           |                |                 | _              | -               |

| В           |                | -               | . –            | -               |

| С           | RSTAT          | RCON            | -              | -               |

| D           | ALICNT         | *TCON           | <b>-</b> ,     | -               |

| E           | CRCCNT         | *DCON           | -              | -               |

| F           | MPCNT          | INTMASK         | _              | -               |

## TABLE B-1. REGISTER ADDRESSES

\*Register contains new or modified bits.

| REG<br>ADDR | PAGE 2<br>READ | PAGE 2<br>WRITE | PAGE 3<br>READ | PAGE 3<br>WRITE |

|-------------|----------------|-----------------|----------------|-----------------|

| 0           | COMMAND        | COMMAND         | COMMAND        | COMMAND         |

| 1           | RSTART         | *TRINCRL        | *TEST          | *TEST           |

| 2           | RSTOP          | *TRINCRH        | _              | -               |

| 3           | _              |                 |                | -               |

| 4           | TSTART         | _               | -              | -               |

| 5           | NEXT           | NEXT            | -              | -               |

| 6           | *BLOCK         | *BLOCK          |                | -               |

| 7           | *ENH           | *ENH            |                | -               |

| 8           | _              |                 | _              | -               |

| 9           | _              | _               | _              | -               |

| A           | _              |                 | _              | -               |

| В           | _              |                 | _              | -               |

| С           | RCON           | -               | _              | -               |

| D           | *TCON          | -               | -              | -               |

| E           | *DCON          | _               | -              | -               |

| F           | INTMASK        | -               | -              | -               |

TABLE B-1. REGISTER ADDRESSES (Continued)

\*Register contains new or modified bits.

| Name:                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                   | R/W Ac                 | ldr:                   |                          |                          |                         |                          |                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------|--------------------------|--------------------------|-------------------------|--------------------------|-----------------------------------------------------------------------------------------------------|

| ALICNT                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                   | OD/-                   | iur.                   |                          |                          |                         |                          |                                                                                                     |

| <b>Description:</b> Th                                                                                                                                                                                                                                                                                                                                                                                        | d with a f                                                                                                                                                                                                                                                        | rame alig              | nment e                | rror. Only               | / packets                | whose a                 | ddress is                | he receive unit when a a accepted are in-                                                           |

| MSB<br>NAME<br>INIT                                                                                                                                                                                                                                                                                                                                                                                           | 7<br>CT7<br>0                                                                                                                                                                                                                                                     | 6<br>CT6<br>0          | 5<br>CT5<br>0          | 4<br>CT4<br>0            | 3<br>СТЗ<br>0            | 2<br>CT2<br>0           | 1<br>CT1<br>0            | 0<br>СТО<br>0                                                                                       |

| <b>Name:</b><br>BLOCK                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                   | <b>R/W Ac</b><br>26/26 | ar:                    |                          |                          |                         |                          |                                                                                                     |

| transfer cycle, the                                                                                                                                                                                                                                                                                                                                                                                           | Description:This is a page register for the upper 8 bits of memory address.During each memory/transfer cycle, the contents of this register are driven out onto the A16-A23 pins, which are not multiplexedand need not be latched by the host system.MSB76543210 |                        |                        |                          |                          |                         |                          |                                                                                                     |

| NAME                                                                                                                                                                                                                                                                                                                                                                                                          | A23                                                                                                                                                                                                                                                               | A22                    | A21                    | A20                      | A19                      |                         | Å17                      | A16                                                                                                 |

| INIT                                                                                                                                                                                                                                                                                                                                                                                                          | 0                                                                                                                                                                                                                                                                 | 0                      | 0                      | 0                        | 0                        | 0                       | 0                        | 0                                                                                                   |

| Name:<br>BOUND                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                   | <b>R/W Ac</b><br>03/03 | ldr:                   |                          |                          |                         |                          |                                                                                                     |

| oldest used recei<br>when linking toge                                                                                                                                                                                                                                                                                                                                                                        | ve buffer<br>other buff<br>ation is a                                                                                                                                                                                                                             | : TRDM/<br>ers to sto  | A compai<br>pre a rece | res the co<br>eived fran | ontents of<br>ne. If the | this regise<br>contents | ster to the<br>s match t | register points to the<br>e next buffer address<br>he next buffer address,<br>poundaries, only A08– |

| MSB                                                                                                                                                                                                                                                                                                                                                                                                           | 7                                                                                                                                                                                                                                                                 | 6                      | 5                      | 4                        | 3                        | 2                       | 1                        | 0                                                                                                   |

| NAME                                                                                                                                                                                                                                                                                                                                                                                                          | A15                                                                                                                                                                                                                                                               | A14                    | A13                    | A12                      | A11                      | A10                     | A09                      | A08                                                                                                 |

| INIT                                                                                                                                                                                                                                                                                                                                                                                                          | 0                                                                                                                                                                                                                                                                 | 0                      | 0                      | 0                        | 0                        | 0                       | 0                        | 0                                                                                                   |

| Name:<br>COLCNT                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                   | <b>R/W Ac</b><br>05/   | ldr:                   |                          |                          |                         |                          |                                                                                                     |

| <b>Description:</b> This register contains the number of collisions detected during attempted transmission of the current (or most recent) packet. It is cleared at the start of transmission. For each collision encountered, the count is incremented. If no collisions are detected, the counter reads zero. If more than 15 collisions occur, the abort bit of TSR is set and the count is reset to zero. |                                                                                                                                                                                                                                                                   |                        |                        |                          |                          |                         |                          |                                                                                                     |

| мѕв                                                                                                                                                                                                                                                                                                                                                                                                           | 7                                                                                                                                                                                                                                                                 | 6                      | 5                      | 4                        | 3                        | 2                       | 1                        | 0                                                                                                   |

| NAME                                                                                                                                                                                                                                                                                                                                                                                                          | 0                                                                                                                                                                                                                                                                 | Õ                      | Õ                      | 0<br>0                   | СТЗ                      | CT2                     | ĊT1                      | СТО                                                                                                 |

| INIT                                                                                                                                                                                                                                                                                                                                                                                                          | 0                                                                                                                                                                                                                                                                 | 0                      | 0                      | 0                        | 0                        | 0                       | 0                        | 0                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                   |                        |                        |                          |                          |                         |                          |                                                                                                     |

## TABLE B-2. ALPHABETICAL REGISTER DESCRIPTIONS

| Name:<br>COMMAND                                                                                                                                                                                                                                                |                                             | <b>R/W Ad</b><br>x0/x0                                                                                                                                                                                                                                                                                                                                                                   | dr:                                  |                                                 |                                                     |                                                  |                                   |                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-------------------------------------------------|-----------------------------------------------------|--------------------------------------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------|

| <b>Description:</b> Th pages.                                                                                                                                                                                                                                   | e comma                                     | nd regist                                                                                                                                                                                                                                                                                                                                                                                | er is usec                           | l to initiali                                   | ze the de                                           | vice, sta                                        | rt transmi                        | ssions, and switch                                                                                                  |

| MSB<br>NAME<br>INIT                                                                                                                                                                                                                                             | 7<br>PS1<br>0                               | 6<br>PS0<br>0                                                                                                                                                                                                                                                                                                                                                                            | 5<br>CMD.5<br>1                      | 4<br>CMD.4<br>0                                 | 3<br>CMD.3<br>0                                     | 2<br>TXP<br>0                                    | 1<br>STA<br>0                     | 0<br>STP<br>1                                                                                                       |

| Notes:                                                                                                                                                                                                                                                          |                                             |                                                                                                                                                                                                                                                                                                                                                                                          |                                      |                                                 |                                                     |                                                  |                                   |                                                                                                                     |

| PS1, PS0                                                                                                                                                                                                                                                        | Page se                                     | elect, a tw                                                                                                                                                                                                                                                                                                                                                                              | o-bit field                          | l <b>.</b>                                      |                                                     |                                                  |                                   |                                                                                                                     |

| Bits 5,4,3                                                                                                                                                                                                                                                      |                                             |                                                                                                                                                                                                                                                                                                                                                                                          |                                      |                                                 |                                                     |                                                  |                                   | dware in the<br>lational 8390.)                                                                                     |

| ТХР                                                                                                                                                                                                                                                             | initiate t<br>or abort<br>in the T          | Transmit packet. Set this bit after loading transmit buffer and control registers to initiate transmission of a packet. The WD83C690 clears this bit upon completion, or abortion, of the transmission. The host can clear the bit by setting TESTMODE in the TEST CONTROL register and writing "0" into COMMAND.TXP. When TESTMODE is not set, writing "0" into COMMAND.TXP is ignored. |                                      |                                                 |                                                     |                                                  |                                   |                                                                                                                     |

| STA                                                                                                                                                                                                                                                             | or after<br>registers<br>normal<br>register | the WD83<br>s prior to<br>operation<br>is set, no                                                                                                                                                                                                                                                                                                                                        | 3C690 is<br>bringing t<br>of the tra | reset. (A<br>he device<br>insmit an<br>an be se | Ithough tl<br>e on line,<br>d receive<br>nt or rece | ne user's<br>this is the<br>portions<br>ived. Or | software<br>actual c<br>of the de | after power is applied<br>should set the other<br>command that allows<br>vice.) Until the<br>his bit may be cleared |

| STP                                                                                                                                                                                                                                                             |                                             |                                                                                                                                                                                                                                                                                                                                                                                          |                                      |                                                 |                                                     |                                                  |                                   | are completed before<br>ve sections have<br>ved until the start bit is                                              |

| Name:<br>CRCCNT                                                                                                                                                                                                                                                 |                                             | <b>R/W Ad</b><br>0E/                                                                                                                                                                                                                                                                                                                                                                     | dr:                                  |                                                 |                                                     |                                                  |                                   |                                                                                                                     |

| <b>Description:</b> This register is the CRC error counter. It is incremented by the receive unit when a packet is received with a CRC error. Only packets whose address is accepted are included in the tally. The counter stops at 255, and clears when read. |                                             |                                                                                                                                                                                                                                                                                                                                                                                          |                                      |                                                 |                                                     |                                                  |                                   |                                                                                                                     |

| MSB<br>NAME<br>INIT                                                                                                                                                                                                                                             | 7<br>CT7<br>0                               | 6<br>CT6<br>0                                                                                                                                                                                                                                                                                                                                                                            | 5<br>CT5<br>0                        | 4<br>CT4<br>0                                   | 3<br>CT3<br>0                                       | 2<br>CT2<br>0                                    | 1<br>CT1<br>0                     | 0<br>СТО<br>0                                                                                                       |

| TA                                                                                                                                                                                                                                                              | BLE B-2                                     | ALPHA                                                                                                                                                                                                                                                                                                                                                                                    | BETICA                               | L REGIS                                         | TER DES                                             | CRIPTIC                                          | NS (Cor                           | ntinued)                                                                                                            |

| Name:<br>CURR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                  | <b>R/W Ad</b><br>17/17                                                                                                                       | dr:              |               |                                      |               |                              |                 |                                  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------|--------------------------------------|---------------|------------------------------|-----------------|----------------------------------|--|

| <b>Description:</b> This register points to the first buffer used to store the current frame. It is used internally by TRDMA to facilitate the storage of buffer header information, and to provide a backup address for recovering buffers in case of a flawed packet. The register should be initialized after the device has been reset and thereafter not altered by the user unless the ring overflows. Note: Because all buffers are aligned on 256-byte boundaries, only A08 through A15 are specified. |                  |                                                                                                                                              |                  |               |                                      |               |                              |                 |                                  |  |

| MSB<br>NAME<br>INIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7<br>A15<br>0    | 6<br>A14<br>0                                                                                                                                | 5<br>A13<br>0    | 4<br>A12<br>0 | 3<br>A11<br>0                        | 2<br>A10<br>0 | 1<br>A09<br>0                | 0<br>A08<br>0   |                                  |  |

| Name:<br>DCON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                  | <b>R/W Ad</b><br>2E/0E                                                                                                                       | dr:              |               |                                      |               |                              |                 |                                  |  |

| Description: The                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | e data co        | onfiguratio                                                                                                                                  | n registe        | r define      | s charact                            | eristics o    | f the men                    | nory interfa    | ace.                             |  |

| MSB<br>NAME<br>INIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7<br>-<br>0      | 6<br>BSIZE1<br>0                                                                                                                             | 5<br>BSIZE0<br>0 | 4<br>-<br>0   | 3<br>-<br>0                          | 2<br>-<br>0   | 1<br>-<br>0                  | 0<br>BUS16<br>0 |                                  |  |