# MOS INTEGRATED CIRCUIT $\mu$ PD78P312A

## 16-/8- BIT SINGLE-CHIP MICROCOMPUTER

#### **DESCRIPTION**

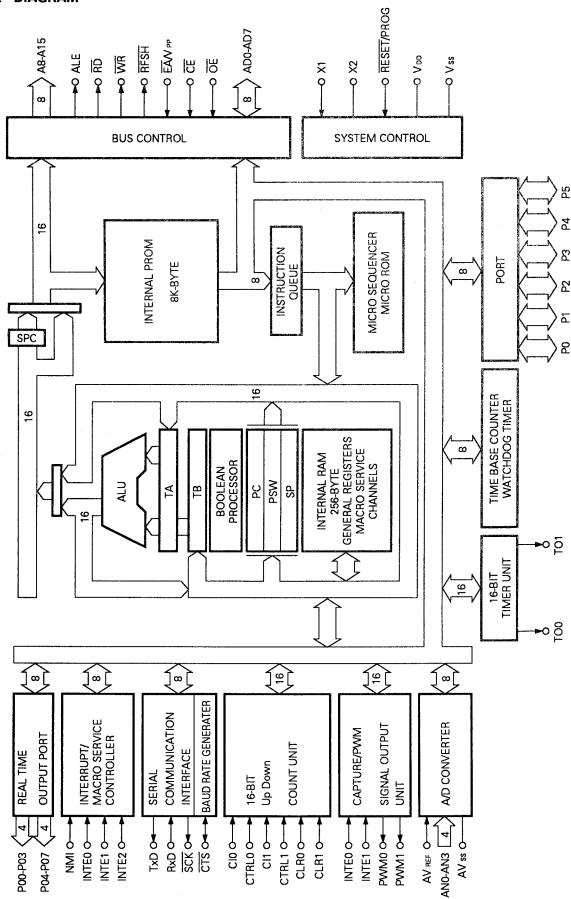

$\mu$ PD78P312A is a 16-/8-bit single-chip microcomputer having the same functions as  $\mu$ PD78312A, except that the internal mask ROM of  $\mu$ PD78312A is replaced with one-time ROM or EPROM. Allowing data to be written only once, the one-time EPROM product is suited for small-scale production of various types of products, or early development of the application system. The EPROM version allows programs to be written more than once and is ideal for system evaluation.

A detailed functional description is provided in the following user's manual. Be sure to read this manual when designing your system.

μPD78312A User's Manual: IEM-5086

#### **FEATURES**

- Compatible with μPD78312A

- Can be replaced with μPD78312A, which integrates mask ROM, when the application system is massproduced

- Internal PROM: 8,192 x 8 bits

- · Data can be written only once (one-time PROM product without window)

- · Erasable by ultraviolet ray. Electrically rewritten (EPROM product with window)

- PROM programming characteristics: Compatible with μPD27C256A

- Available as QTOP<sup>TM</sup> microcomputer

Remarks: QTOP microcomputer is the generic name for the NEC built-in PROM single-chip micro computer providing total support of program writing, printing, screening, and verifying.

#### ORDERING INFORMATION

| Part Number      | Package                                         | Internal ROM  |

|------------------|-------------------------------------------------|---------------|

| μPD78P312ACW     | 64-pin plastic shrink DIP (750 mil)             | One-time PROM |

| μPD78P312AGF-3BE | 64-pin plastic QFP (14 x 20 mm)                 | ditto         |

| μPD78P312AGQ-36  | 64-pin plastic QUIP                             | ditto         |

| μPD78P312AL      | 68-pin plastic QFJ (☐ 950 mil)                  | ditto         |

| μPD78P312ADW     | 64-pin shrink DIP with ceramic window (750 mil) | EPROM         |

| μPD78P312AR      | 64-pin QUIP with ceramic window                 | ditto         |

## QUALITY GRADE

Standard

Please refer to "Quality Grade on NEC Semiconductor Devices" (Document number IEI-1209) published by NEC Corporation to know the specification of quality grade on the devices and their recommended

The information in this document is subject to change without notices.

Document No. IC-2512B (0. D. No. IC-7772B) Date Published November 1993 P

Printed in Japan

\*

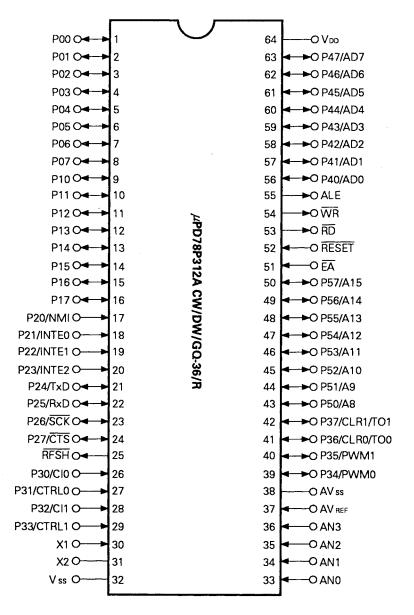

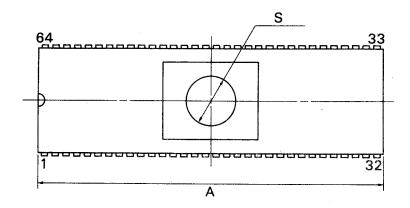

#### PIN CONFIGURATION (Top View)

- (1) Normal operation mode

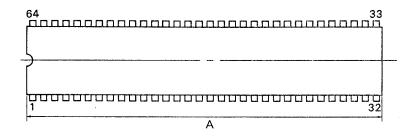

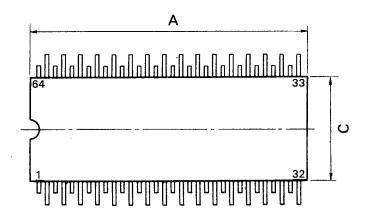

- (a) 64-pin plastic shrink DIP/QUIP

64-pin shrink DIP/QUIP with ceramic window

| P00-P07 | : | Port0        | ALE          | : | Address Latch Enable          | NMI         | :  | Nonmaskable Interrupt    |

|---------|---|--------------|--------------|---|-------------------------------|-------------|----|--------------------------|

| P10-P17 | : | Port1        | RFSH         | : | Refresh                       | INTEO-INTE2 | 2: | Interrupt From Externals |

| P20-P27 | : | Port2        | X1, X2       | : | Crystal                       | AN0-AN3     | :  | Analog Input             |

| P30-P37 | : | Port3        | RESET        | : | Reset                         | AVREF       | :  | Reference Voltage        |

| P40-P47 | : | Port4        | ĒÄ           | : | External Access               | AVss        | :  | Analog Vss               |

| P50-P57 | : | Port5        | CI0, CI1     | : | Count Pulse Input             | RxD         | :  | Receive Serial Data      |

| AD0-AD7 | : | Address/Data | CTRL0, CTRL1 | : | Control Pulse Input           | TxD         | :  | Transfer Serial Data     |

| A8-A15  | : | Address      | CLR0, CLR1   | : | Timer Clear Input             | SCK         | :  | Serial Clock             |

| RD      | : | Read Strobe  | PWM0, PWM1   | : | Pulse Width Modulation Output | CTS         | :  | Clear To Send            |

| WR      | : | Write Strobe | TO0, TO1     | : | Timer Output                  | IC          | :  | Internally Connected     |

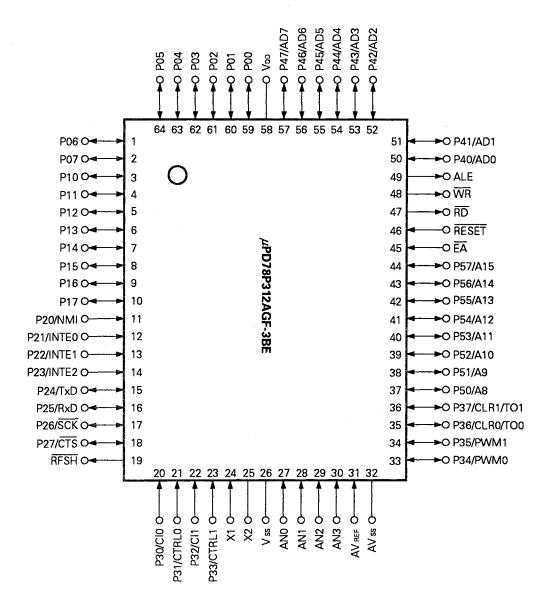

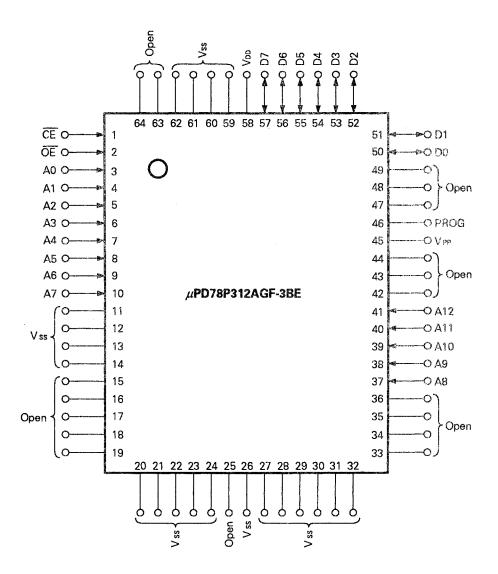

### (b) 64-pin plastic QFP (14 x 20 mm)

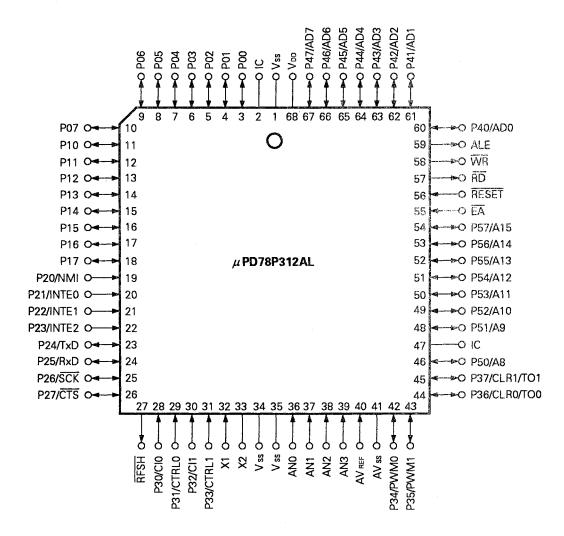

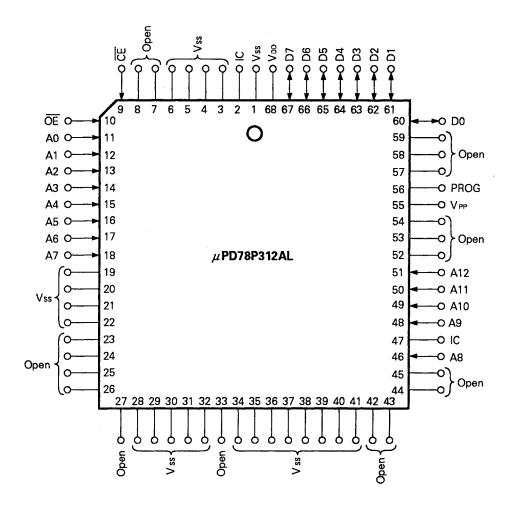

#### (c) 68-pin plastic QFJ ( 950 mil)

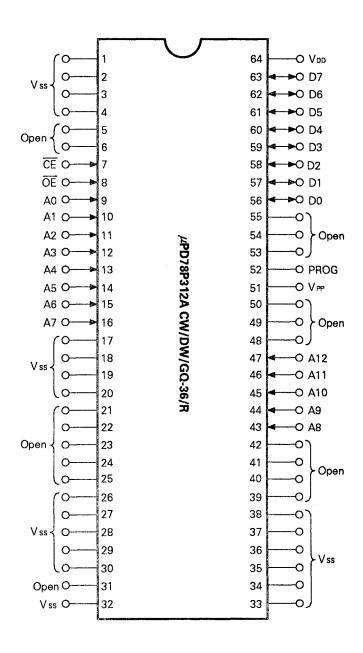

## (2) PROM programming mode

NEC

(a) 64-pin plastic shrink DIP/QUIP

64-pin shrink DIP/QUIP ceramic window

Note: 1. Vss : Ground this pin.

2. Open: Do not connect this pin.

## (b) 64-pin plastic QFP (14 x 20 mm)

Note: 1. V<sub>ss</sub>: Ground this pin.

2. Open: Do not connect this pin.

## (c) 68-pin plastic QFJ (☐ 950 mil)

Note: 1.  $V_{ss}$ : Ground this pin.

2. Open: Do not connect this pin.

## **BLOCK DIAGRAM**

# **CONTENTS**

| 1.   | PIN F           | UNCTIONS1                                                           | 0           |

|------|-----------------|---------------------------------------------------------------------|-------------|

|      | 1.1             | PORT PINS                                                           |             |

|      | 1.2             | ALL OTHER PINS (IN NORMAL OPERATION MODE)                           | 11          |

|      | 1.3             | ALL OTHER PINS (ON PROM PROGRAMMING MODE)1                          | 12          |

|      | 1.4             | PIN INPUT/OUTPUT CIRCUITS                                           | 13          |

|      | 1.5             | RECOMMENDED CONDITIONS FOR UNUSED PINS                              | 15          |

| 2.   | СОМ             | PARISON OF FAMILY PRODUCTS1                                         | 6           |

| 3.   | PRO             | И PROGRAMMING1                                                      | 7           |

|      | 3.1             | PROM PROGRAMMING MODE                                               | 17          |

|      | 3.2             | PROM WRITE PROCEDURE                                                |             |

|      | 3.3             | PROM READ PROCEDURE                                                 | 19          |

|      | 3.4             | ERASING PROCEDURE (EPROM PRODUCT ONLY)1                             | 19          |

|      | 3.5             | SCREENING OF ONE-TIME PROM PRODUCTS                                 | l9 <b>≯</b> |

| 4.   | ELEC            | TRICAL CHARACTERISTICS2                                             | 20          |

| 5.   | EXTE            | RNAL DIMENSIONS3                                                    | 6           |

| 6.   | RECO            | DMMENDED SOLDERING CONDITIONS4                                      | 2           |

| APF  | PENDIX          | A DIMENTIONS OF CONVERSION SOCKET AND RECOMMENDED MOUNTING PATTERN4 | 14 *        |

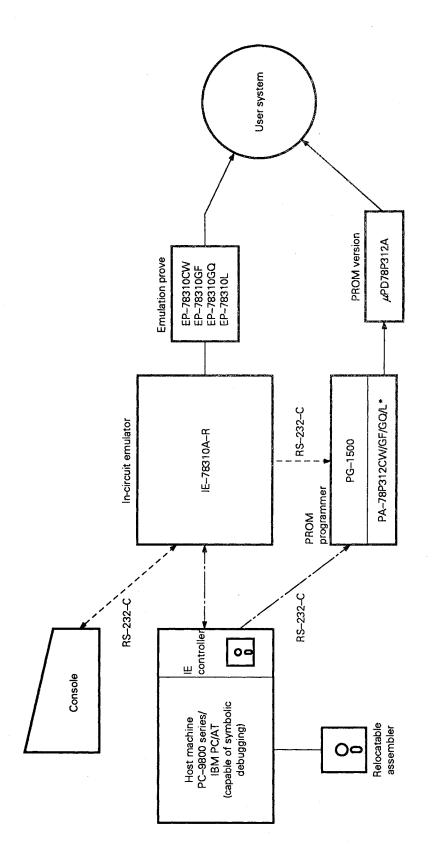

| A Dr | אר <i>אוראו</i> | P DEVELOPMENT TOOLS                                                 | 16          |

## 1. PIN FUNCTIONS

## 1.1 PORT PINS

| Pin Name | Input/<br>Output    | Shared<br>Pin #    | Function                                                                                              |  |

|----------|---------------------|--------------------|-------------------------------------------------------------------------------------------------------|--|

| P00-P05  |                     | -                  | (Port 0)                                                                                              |  |

| P06      | Input/<br>output,   | (CE)               | This is an 8-bit input/output port that can be specified for input or output in bit units.            |  |

| P07      | real-time<br>output | ( <del>OE</del> )  | This port can be used as two independent 4-bit real-time output ports (channels)                      |  |

| P10-P17  | Input/<br>Output    | (A0-A7)            | (Port 1) This is an 8-bit input/output port that can be specified for input or output in bit units.   |  |

| P20      |                     | NMI                | (Port 2)                                                                                              |  |

| P21      |                     | INTEO              | P20 to P23 are input port pins. P24 to P27 are input/output port pins each of which can be            |  |

| P22      | Input               | INTE1              | independently specified for input or output.                                                          |  |

| P23      |                     | INTE2              |                                                                                                       |  |

| P24      |                     | TxD                |                                                                                                       |  |

| P25      | Input/<br>output    | RxD                |                                                                                                       |  |

| P26      |                     | SCK                |                                                                                                       |  |

| P27      |                     | CTS                |                                                                                                       |  |

| P30      |                     | CIO                | (Port 3)                                                                                              |  |

| P31      | J                   | CTRLO              | P30 to P33 are input port pins. P34 to P37 are input/output port pins each of which can be            |  |

| P32      | Input               | CI1                | independently specified for input or output.                                                          |  |

| P33      |                     | CTRL1              |                                                                                                       |  |

| P34      |                     | PWM0               |                                                                                                       |  |

| P35      | Input/              | PWM1               |                                                                                                       |  |

| P36      | output              | TO0-CLR0           |                                                                                                       |  |

| P37      |                     | TO1-CLR1           |                                                                                                       |  |

| P40-P47  | Input/<br>output    | AD0-AD7<br>(D0-D7) | (Port 4) This is an 8-bit input/output port that can be specified for input or output in 8-bit units. |  |

| P50-P54  | Input/              | A8-A12<br>(A8-A12) | (Port 5) This is an 8-bit input/output port that can be specified for                                 |  |

| P55-P57  | output              | A13-A15            | input or output in bit units.                                                                         |  |

<sup>\*:</sup> Parentheses indicate the pin name shared in the PROM programming mode.

## 1.2 ALL OTHER PINS (IN NORMAL OPERATION MODE)

(1/2)

| Pin Name | Input/<br>Output | Shared<br>Pin*      | Function                                                                                                                                                                        |  |

|----------|------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NMI      | Input            | P20                 | Non-maskable interrupt request pin                                                                                                                                              |  |

| INTEO    |                  | P21                 | External interrupt request input pin                                                                                                                                            |  |

| INTE1    | Input            | P22                 |                                                                                                                                                                                 |  |

| INTE2    | P23              |                     |                                                                                                                                                                                 |  |

| TxD      | Output           | P24                 | Serial data output pin                                                                                                                                                          |  |

| RxD      | Input            | P25                 | Serial data input pin                                                                                                                                                           |  |

| SCK      | Output           | P26                 | Serial clock output pin                                                                                                                                                         |  |

| стѕ      | Input/<br>Output | P27                 | <ul> <li>In the asynchronous mode, this pin serves as the transmit enable control pin.</li> <li>In the I/O interface mode, this pin inputs/outputs the serial clock.</li> </ul> |  |

| CIO      |                  | P30                 | These pins input the external count clock for the count                                                                                                                         |  |

| CI1      | Input            | P32                 | unit.                                                                                                                                                                           |  |

| CTRLO    |                  | P31                 | These pins input the count operation selection control                                                                                                                          |  |

| CTRL1    | Input            | P33                 | signal for the count unit.                                                                                                                                                      |  |

| CLR0     | I                | P36/TO0             | Count unit clear signal input pin                                                                                                                                               |  |

| CLR1     | Input            | P37/TO1             |                                                                                                                                                                                 |  |

| PWM0     | 0                | P34                 | PWM output pin                                                                                                                                                                  |  |

| PWM1     | Output           | P35                 |                                                                                                                                                                                 |  |

| TO0      | <b>0</b>         | P36/CLR0            | Timer unit pulse output pin                                                                                                                                                     |  |

| TO1      | Output           | P37/CLR1            |                                                                                                                                                                                 |  |

| AD0-AD7  | Input/<br>Output | P40-P47<br>(D0-D7)  | Multiplexed address/data but pins used when the external memory space is expanded.                                                                                              |  |

| A8-A12   | Output           | P50-P54<br>(A8-A12) | Address bus pins when the external memory space is expanded.                                                                                                                    |  |

| A13-A15  |                  | P55-P57             |                                                                                                                                                                                 |  |

| WR       | Output           | -                   | External memory write signal output pin                                                                                                                                         |  |

| RD       | Output           | -                   | External memory read signal output pin                                                                                                                                          |  |

| ALE      | Output           | _                   | This pin outputs the timing signal used to externally latch the address output when accessing the external memory.                                                              |  |

| AN0-AN3  | Input            |                     | A/D converter analog input pin                                                                                                                                                  |  |

| AVREF    | Input            | _                   | A/D converter reference voltage input pin                                                                                                                                       |  |

| AVss     | _                |                     | A/D converter GND pin                                                                                                                                                           |  |

<sup>•:</sup> Parentheses indicate the pin name shared in the PROM programming mode.

(2/2)

| Pin Name | Input/<br>Output | Shared<br>Pin* | Function                                                                                                                                                                                                  |  |

|----------|------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| X1       | Input            | <u></u>        | The system clock crystal is connected across these pins.                                                                                                                                                  |  |

| X2       | -                |                | <ul> <li>When using an external clock, the X1 pin inputs the external clock.</li> </ul>                                                                                                                   |  |

| RFSH     | Output           | -              | This pin outputs the refresh pulse to the externally connected pseudo-static memory.                                                                                                                      |  |

| RESET    | Input            | (PROG)         | System reset pin                                                                                                                                                                                          |  |

| VDD      |                  | _              | Positive power supply pin                                                                                                                                                                                 |  |

| Vss      |                  |                | GND                                                                                                                                                                                                       |  |

| ĒĀ       | Input            | (VPP)          | This pin is usually connected to Vob. When this pin is connected to Vss, the ROM-less mode is set in which the external memory can be accessed. The level of this pin cannot be changed during operation. |  |

| IC       | -                | -              | Internally connected. Leave this pin open.                                                                                                                                                                |  |

<sup>\*:</sup> Parentheses indicate the pin name shared in the PROM programming mode.

# 1.3 ALL OTHER PINS (ON PROM PROGRAMMING MODE)

| Pin Name        | Input/<br>Output | Shared<br>Pin       | Function                                          |  |

|-----------------|------------------|---------------------|---------------------------------------------------|--|

| A0-A7           |                  | P10-P17             | Address input pins                                |  |

| A8-A12          | Input            | P50-P54/<br>A8-A12  |                                                   |  |

| D0-D7           | Input/<br>output | P40-P47/<br>AD0-AD7 | Data input/output pins                            |  |

| CE              | Input            | P06                 | Chip-enable input pin/program pulse input pin     |  |

| ŌĒ              | Input            | P07                 | Output-enable input pin                           |  |

| PROG            | _                | RESET               | PROM programming mode set pin                     |  |

| VPP             |                  | EA                  | Program write/verify high voltage application pin |  |

| V <sub>DD</sub> | -                | _                   | Positive power supply pin                         |  |

| Vss             | _                | _                   | GND                                               |  |

## 1.4 PIN INPUT/OUTPUT CIRCUITS

Table 1-1 and Fig. 1-1 describe each pin input/output circuit in a simplified manner.

Table 1-1 Input/Output Circuit Type for Each Pin

| Pin*                  | Input/output<br>circuit type | Pin*                    | Input/output<br>circuit type |

|-----------------------|------------------------------|-------------------------|------------------------------|

| P00-P05               |                              | P34/PWM0                |                              |

| P06/(CE)              | 5                            | P35/PWM1                | 5                            |

| P07/( <del>0E</del> ) |                              | P36/TO0/CLR0            | _                            |

| P10-P17/(A0-A7)       | 5                            | P37/TO1/CLR1            | 6                            |

| P20/NMI               | 2                            | P40-P47/AD0-AD7/(D0-D7) | 5                            |

| P21/INTE0             |                              | P50-P54/A8-A12/(A8-A12) | _                            |

| P22/INTE1             | 1                            | P55-P57/A13-A15         | 5                            |

| P23/INTE2             |                              | WR                      |                              |

| P24/TxD               |                              | RD                      | 3                            |

| P25/RxD               |                              | ALE                     |                              |

| P26/SCK               | 5                            | EA                      | 1                            |

| P27/CTS               |                              | AN0-AN3                 | 7                            |

| P30/CIO               |                              | RFSH                    | 3                            |

| P31/CTRL0             | 1                            | RESET/(PROG)            | 2                            |

| P32/Cl1               |                              |                         |                              |

| P33/CTRL1             |                              |                         |                              |

<sup>\*:</sup> Parentheses indicate pin used for PROM programming.

Fig. 1-1 Pin Input/Output Circuits

## 1.5 RECOMMENDED CONDITIONS FOR UNUSED PINS

| Pin                                      | Recommended connection                                                     |

|------------------------------------------|----------------------------------------------------------------------------|

| P00-P07<br>P10-P17                       | Input mode: Connect to Vpp through a pull-up resistor<br>Output mode: Open |

| P20-P23                                  | Connect to Vss                                                             |

| P30-P33                                  | Connect to either Vss or VDD                                               |

| P24-P27<br>P34-P37<br>P40-P47<br>P50-P57 | Input mode: Connect to VDD through a pull-up resistor Output mode: Open    |

| WR<br>RD<br>ALE<br>RFSH                  | Open                                                                       |

| AN0-AN3                                  | Connect to either Vss or VDD                                               |

| AVref<br>AVss                            | Connect to Vss                                                             |

#### 2. COMPARISON OF FAMILY PRODUCTS

The  $\mu$ PD78P312A is a version of the  $\mu$ PD78312A in which the internal mask ROM is replaced with an one-time PROM or EPROM. The  $\mu$ PD78P312A is an upgraded version of the  $\mu$ PD78P312. Table 2-1 shows a comparison of the  $\mu$ PD78P312A, and  $\mu$ PD78310A. Table 2-2 shows a comparison of the  $\mu$ PD78P312A and  $\mu$ PD78P312. Except where noted, these products are identical with respect to function.

Refer to the documents provided for the  $\mu$ PD78312A and  $\mu$ PD78310A for details concerning the internal hardware such as CPU functions.

Table 2-1 Comparison of  $\mu$ PD78P312A,  $\mu$ PD78312A, and  $\mu$ PD78310A

|                 | ltem                  | APD78P312A                                                                                                                    | μPD78312A                      | μPD78310A                                                                                                               |

|-----------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------|

|                 | Program memory        | • PROM<br>• 8,192 x 8 bits                                                                                                    | • Mask ROM<br>• 8,192 x 8 bits | Not internally provided                                                                                                 |

|                 | PROM programming mode | Provided No                                                                                                                   |                                | one                                                                                                                     |

| Pin<br>function | Ports 4, 5            |                                                                                                                               |                                | None (These ports<br>always serve as the<br>address bus, data bus)                                                      |

|                 | ĒĀ                    | Provided                                                                                                                      |                                | Provided (However, must<br>be operated with this pin<br>set to low)                                                     |

| Ext             | ernal memory access   | External memory can b<br>256 bytes, 4K bytes, 16i<br>using the memory expa<br>(MM).                                           | K bytes, or 56K bytes,         | Always accesses 64K bytes of the external memory (regardless of the setting in the memory expansion mode register (MM). |

| Without window  |                       | • 64-pin plastic shrink DIP (75)<br>• 64-pin plastic QUIP<br>• 64-pin plastic QFP (14 x 20 r<br>• 68-pin plastic QFJ (□ 950 m |                                | nm)                                                                                                                     |

| Package         | With window           | <ul> <li>64-pin ceramic<br/>shrink DIP with<br/>window<br/>(750 mil)</li> <li>64-pin ceramic<br/>QUIP with window</li> </ul>  | P                              | Vone                                                                                                                    |

Table 2-2 Difference Between  $\mu$ PD78P312A and  $\mu$ PD78P312

| ltem                                                                                                                                         | µРD78Р312A | μPD78 <b>P312</b> |

|----------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------|

| Mode 4 in count unit<br>(4 x multiplication mode)                                                                                            | Provided   | Not provided      |

| Count start triggered by external pulse of interval timer                                                                                    | Provided   | Not provided      |

| 16 bit data transfer instruction used between memory and a pair register  • MOVW rp1, !addr 16 instruction  • MOVW !addr 16, rp1 instruction | Provided   | Not provided      |

#### 3. PROM PROGRAMMING

The ROM contained in  $\mu$ PD78P312A is an electrically erasable PROM with 8,192 x 8 bit configuration. The pins listed in the table below are used to program the PROM.

When used in the normal operation mode, 5 V  $\pm$ 10% is applied to the V<sub>DD</sub> and V<sub>PP</sub> pins. A voltage higher than V<sub>DD</sub> should not be applied to other pins.

The programming characteristics of the  $\mu$ PD78P312A are identical to those of the  $\mu$ PD27C256A.

| Pin Name | Function                                                             |

|----------|----------------------------------------------------------------------|

| VPP      | High voltage input (write/verify mode), high level input (read mode) |

| PROG     | High voltage input (write/verify mode, read mode)                    |

| A0-A7    | Address input (lower 8 bits)                                         |

| A8-A12   | Address input (upper 8 bits)                                         |

| D0-D7    | Data input (write mode), data output (verify mode)                   |

| CE       | Program pulse input                                                  |

| ŌĒ       | Output enable input                                                  |

| VDD      | Power supply pin                                                     |

Note: 1. Attach a light baffle film to  $\mu$ PD78P312A with an erase window to protect the EPROM from being erased accidentally.

2. The one-time PROM product,  $\mu$ PD78P312A, cannot be erased by ultraviolet rays, because it is not provided with a window.

### 3.1 PROM PROGRAMMING MODE

When +6 V is applied to the Vpp pin and +12.5 V is applied to the PROG pin and Vpp pin, the  $\mu$ PD78P312A enters the program write/verify mode. Operation in this mode is determined according to the setting of  $\overline{CE}$  and  $\overline{OE}$  pins as indicated in the table below. Additionally, when set to the read mode, the  $\mu$ PD78P312A can read the contents of PROM.

| Operation mode specification |      |     |                                    |         | 0                                |                          |  |  |

|------------------------------|------|-----|------------------------------------|---------|----------------------------------|--------------------------|--|--|

| VPP                          | Voo  | CE  | ŌĒ                                 | PROG    | Operation mode                   |                          |  |  |

|                              |      | L   | Н                                  |         | Write mo                         | ode                      |  |  |

| +12.5 V                      | +6 V | н   | L<br>H                             |         | Verify mode Program inhibit mode |                          |  |  |

|                              |      |     |                                    | +12.5 V |                                  |                          |  |  |

|                              |      |     | Data is output from the D0-D7 pins |         |                                  |                          |  |  |

| VPP=VDD=+5 V                 |      | L/H | Н                                  | -       | mode                             | D0-D7 are high impedance |  |  |

Remarks: H indicates high level; L indicates low level.

Note: When +12.5 V is applied to VPP and +6 V is applied to VDD, both CE and OE must not be set to low level (L) simultaneously.

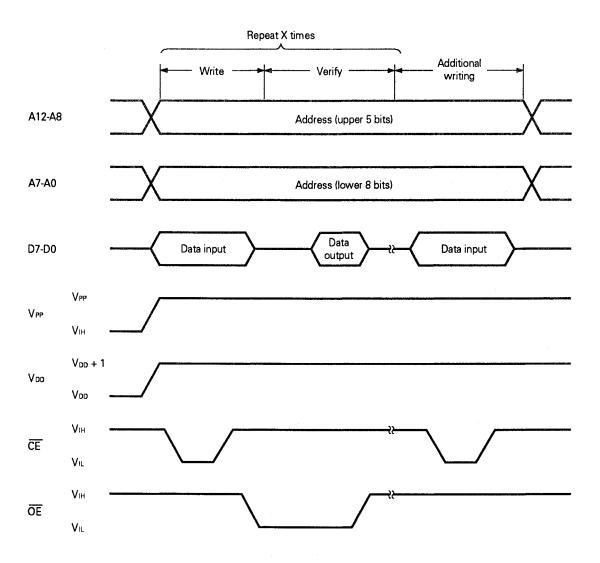

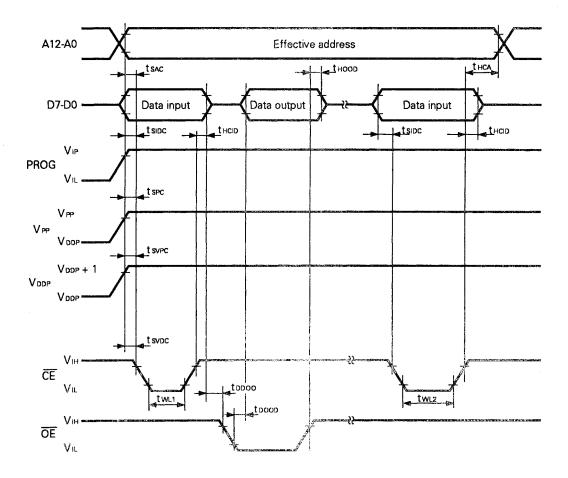

#### 3.2 PROM WRITE PROCEDURE

Data can be written to the PROM using the following procedure. High speed data write operation is possible.

- (1) Process the pins not used in accordance with the description in Pin Configuration, and supply +6 V to the Vpp pin and +12.5 V to the Vpp pin.

- (2) Provide the initial address.

- (3) Provide write data.

- (4) Provide a 1 ms program pulse (active low) to the CE pin.

- (5) Verify mode. If the data has been written, proceed to (7), if not, repeat steps (3) to (5). If the data cannot be correctly written in 25 attempts, go to step (6).

- (6) Classify the PROM as defective and cease write operation.

- (7) Provide write data and supply (for additional writing) program pulses for 3 ms times the number of repeats performed between steps (3) to (5).

- (8) Increment the address.

- (9) Repeat steps (3) to (8) until the end address is reached.

Fig. 3-1 PROM Write/Verify Timing

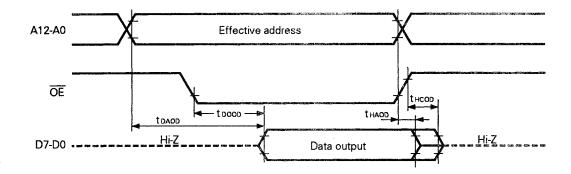

#### 3.3 PROM READ PROCEDURE

The contents of the PROM can be read out to the external data bus (D0-D7) using the following procedure.

- (1) Process the unused pins in accordance with the description in Pin Configuration.

- (2) Supply +5 V to the VDD pin and VPP pin, and +12.5 V to the PROG pin.

- (3) Input the address of the data to be read to the A0 to A12 pins.

- (4) Read mode.

- (5) Data is output to the D0 to D7 pins.

Fig. 3-2 shows the timing for this sequence from steps (2) to (5).

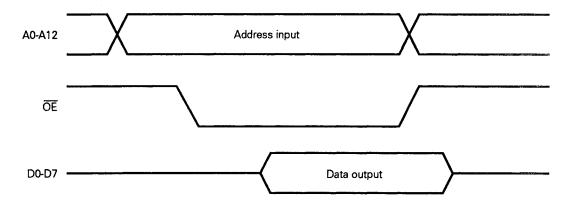

Fig. 3-2 PROM Read Timing

#### 3.4 ERASING PROCEDURE (EPROM PRODUCT ONLY)

Data on the  $\mu$ PD78P312ADW/R EPROM can be erased by exposing the EPROM to light with a wavelength shorter than 400 nm. Therefore, if the EPROM is exposed to direct sunlight or the light of a fluorescent lamp for a long time, the data on the EPROM may be erased. To protect the data, mask the EPROM window with a light baffle film, which is attached as an accessory.

Usually, cast a 254 nm ultraviolet ray onto the window of the EPROM to erase the memory contents. To completely erase the EPROM contents, a minimum of 15 W·s/cm<sup>2</sup> (strength of the ultraviolet light x erase time) of exposure is necessary. This means that, when a 12,000  $\mu$ W/cm<sup>2</sup> ultraviolet lamp is used, about 15 to 20 minutes are required to completely erase the EPROM contents. The time required to erase the EPROM contents, however, may be lengthened if the file of the ultraviolet lamp used is ending, or if the window of the EPROM is soiled. The distance between the ultraviolet lamp and the window should be 2.5 cm or shorter.

#### 3.5 SCREENING OF ONE-TIME PROM PRODUCTS

One-time PROM products (µPD78P312ACW, 78P312AGF-3BE, 78P312AGQ-36, and 78P312AL) cannot be completely tested by NEC before shipment. It is recommended that screening be implemented under the following conditions to verify the PROM after the necessary data has been written:

| Storage Temperature | Storage Time |

|---------------------|--------------|

| 125°C               | 24 hours     |

NEC offers changed services including writing, printing, screening, and verifying one-time PROMs by the device called a QTOP microcomputer. For details, consult NEC.

## 4. ELECTRICAL CHARACTERISTICS

## Absolute Maximum Rating (Ta = 25°C)

| ltem                      | Symbol                                                                                                                                                                                     | Conditions            | Rating          | Units |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------|-------|

|                           | Voo                                                                                                                                                                                        |                       | -0.5 to +7.0    | ٧     |

| <b>3</b>                  | Wer supply voltage  AVss  Vpp  Dut voltage  Vi1 Other than RESET  Vi2 RESET  Vi2 RESET  Wilevel output current  IoL  Single pin  All output pins total  Single pin  Single pin  Single pin | -0.5 to Voo+0.3       | ٧               |       |

| Power supply voltage      | AVss                                                                                                                                                                                       |                       | -0.5 to +0.5    | ٧     |

|                           | Vob   -0.5 to +7.0                                                                                                                                                                         | ٧                     |                 |       |

|                           | Vn                                                                                                                                                                                         | Other than RESET      | -0.5 to Vpp+0.5 | ٧     |

| Input voitage             | V <sub>12</sub>                                                                                                                                                                            | RESET                 | -0.5 to +13.5   | ٧     |

| Output voltage            | Vo                                                                                                                                                                                         |                       | -0.5 to Van+0.5 | ٧     |

| 1 1                       |                                                                                                                                                                                            | Single pin            | 4.0             | mA    |

| Low level output current  | IOL                                                                                                                                                                                        | All output pins total | 60              | mA    |

|                           |                                                                                                                                                                                            | Single pin            | -2              | mA    |

| High level output current | Іон                                                                                                                                                                                        | All output pins total | -15             | mA    |

| Operating temperature     | Topt                                                                                                                                                                                       |                       | -10 to +70      | °C    |

| Storage temperature       | Tatg                                                                                                                                                                                       |                       | -65 to +150     | °C    |

## **Operating Condition**

| Item Oscillation frequency | Та           | VDD         |

|----------------------------|--------------|-------------|

| 4 MHz ≤ fxx ≤ 12 MHz       | -10 to +70°C | +5.0 V ±10% |

## Capacitance (Ta = 25°C, V<sub>DD</sub> = Vss = 0 V)

| ltem                     | Symbol | Conditions                                       | MIN. | TYP. | MAX. | Units |

|--------------------------|--------|--------------------------------------------------|------|------|------|-------|

| Input capacitance        | Cı     | 4 1 1 1                                          |      |      | 10   | рF    |

| Output capacitance       | Со     | f = 1 MHz<br>Pin not used for measurement is 0 V |      |      | 20   | рF    |

| Input/Output capacitance | Cio    |                                                  |      |      | 20   | pF    |

Oscillator Characteristics (Ta = -10 to +70°C, VDD = +5.0 V  $\pm$ 10%, Vss = AVss = 0 V, 4 V  $\leq$  AVREF  $\leq$  VDD)

| Oscillator                                          | Recommended circuit       | ltem                                       | MIN. | MAX. | Units |

|-----------------------------------------------------|---------------------------|--------------------------------------------|------|------|-------|

| Ceramic<br>oscillator<br>or<br>crystal<br>resonator | X1 X2 C2                  | Oscillation frequency (fxx)                | 4    | 12   | MHz   |

|                                                     | X1 X2                     | X1 input frequency (fx)                    | 4    | 12   | MHz   |

| External clock                                      | <b>├</b> ── <b>&gt;</b> ○ | X1 input rise, fall time<br>(txx, txr)     | 0    | 12   | ns    |

|                                                     | HCMOS inverter            | X1 input high/low level width (twxH, twxL) | 30   |      | ns    |

Notes 1: Oscillator circuit must be located as close as possible to the X1 and X2 pins.

2: To prevent noise from affecting operation, avoid locating other signal lines within portion enclosed in dotted line.

## **Recommended Oscillator Circuit Constants**

## Ceramic oscillator

| Manufacturer |              | Frequency | External capac | citance (pF)                                                                                                   |

|--------------|--------------|-----------|----------------|----------------------------------------------------------------------------------------------------------------|

| wanufacturer | Product name | (MHz)     | C1             | C2                                                                                                             |

|              | CSA8.00MT    | 8.0       |                |                                                                                                                |

|              | CSA10.0MT    | 10.0      | 30             | 30                                                                                                             |

|              | CSA12.0MT    | 12.0      | 1              |                                                                                                                |

| Murata Mfg.  | CST8.00MT    | 8.0       |                | agamata yann qoʻgʻidi. Magan - qoʻgʻig yili daminin oʻrini, in damini damini damini damini damini damini damin |

|              | CST10.0MT    | 10.0      | Internal       | Internal                                                                                                       |

|              | CST12.0MT    | 12.0      |                |                                                                                                                |

|              | KBR-8.0M     | 8.0       |                |                                                                                                                |

| Kyocera      | KBR-10.0M    | 10.0      | 33             | 33                                                                                                             |

|              | KBR-12.0M    | 12.0      |                |                                                                                                                |

|              | FCR10.0MC    | 10.0      |                |                                                                                                                |

| TDK          | FCR12.0MC    | 12.0      | Internal       | Internal                                                                                                       |

# Crystal resonator

| Manufacturer   | Product name | Frequency           | External capacitano C1 22 | citance [pF] |

|----------------|--------------|---------------------|---------------------------|--------------|

| ivianuracturer | Froduct name | [MHz]               | C1                        | C2           |

| Kinseki        | HC-49U       | 8.0<br>10.0<br>12.0 | 22                        | 22           |

# DC Characteristics (Ta = -10°C to +70°C, $V_{DD}$ = +5.0 V ±10%, $V_{SS}$ = 0 V)

| ltem                            | Symbol           |                 | Conditions              | MIN.                 | TYP. | MAX. | Units |

|---------------------------------|------------------|-----------------|-------------------------|----------------------|------|------|-------|

| Low level                       | VIL1             | Other than EA   | 0                       |                      | 0.8  | V    |       |

| input voltage                   | VIL2             | EA              |                         | 0                    |      | 0.5  | ٧     |

|                                 | ViH1             | Except the P20/ | NMI, X1, X2, RESET pins | 2.2                  |      | Voo  | ٧     |

| High level<br>input voltage     | V <sub>1H2</sub> | P20/NMI, X1, X2 | RESET pins              | 3.8                  |      | Voo  | ٧     |

| Low level<br>output voltage     | Vor              | loL = 2.0 mA    |                         | 11.52                | 0.45 | ٧    |       |

| High level output voltage       | Voн              | lон = -1.0 mA   |                         | V <sub>DD</sub> -1.0 |      |      | ٧     |

| Input current                   | l <sub>1</sub>   | P20/NMI, RESET  | 0.45 V < V1 < VDD       |                      |      | ±10  | μА    |

| Input leakage current           | lu               |                 |                         |                      |      | ±10  | μΑ    |

| Input/output<br>leakage current | lro              |                 |                         |                      |      | ±10  | μΑ    |

| AVREF current                   | Alref            | fclk = 6 MHz    |                         |                      | 1.5  | 5    | mA    |

| V <sub>DD</sub> power supply    | I <sub>DD1</sub> | Operating mode  |                         | 30                   | 60   | mA   |       |

| current                         | IDD2             | HALT mode, fcu  | c = 6 MHz               |                      | 5    | 15   | mA    |

| Data retention voltage          | VDDDR            | STOP mode       |                         | 2.5                  |      |      | V     |

| 5                               |                  | STOP mode       | VDDDR = 2.5 V           |                      | 3    | 15   | μА    |

| Data retention current          | IDDDR            | STUP mode       | VDDDR = 5.0 V ±10%      |                      | 10   | 50   | μΑ    |

#### **AC Characteristics**

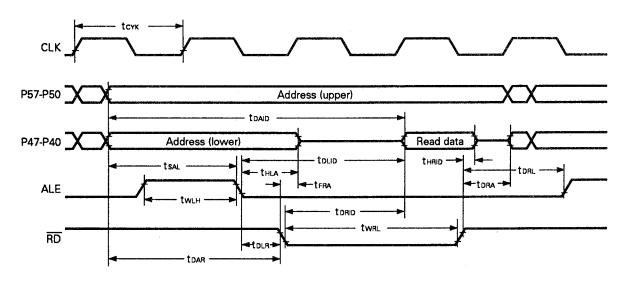

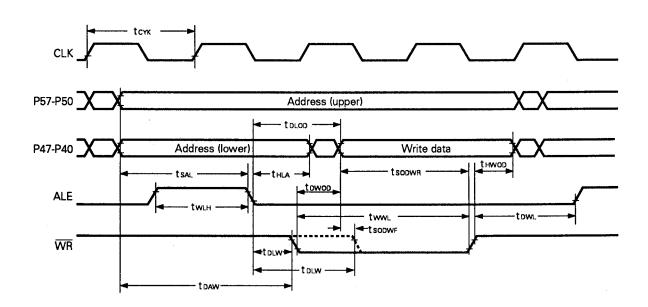

Read/Write operation (Ta =-10°C to +70°C,  $V_{DD}$  = +5 V ±10%,  $V_{SS}$  = 0 V)

| Item                                                                    | Symbol | Conditions   | MIN. | MAX. | Units |

|-------------------------------------------------------------------------|--------|--------------|------|------|-------|

| Internal system clock cycle time *1                                     | tcyk   |              | 166  | 1000 | ns    |

| Address set up time (vs. ALE ↓ )                                        | İsal   |              | 150  |      | ns    |

| Address hold time (vs. ALE ↓ )                                          | thla   |              | 30   |      | ns    |

| Address → RD ↓ delay time                                               | tdar   |              | 233  |      | ns    |

| RD ↓ → address float time                                               | tfra   |              |      | 0    | ns    |

| Address → data input time                                               | toaid  |              |      | 413  | ns    |

| ALE ↓ → data input time                                                 | tolio  |              |      | 233  | ns    |

| RD ↓ → data input time                                                  | torio  |              |      | 180  | ns    |

| ALE $\downarrow \rightarrow \overline{\text{RD}} \downarrow$ delay time | tous   |              | 63   |      | ns    |

| Data hold time (vs. $\overline{RD}$ $\uparrow$ )                        | THRID  |              | o    |      | ns    |

| RD ↑ → address active time                                              | tora   |              | 53   |      | ns    |

| RD ↑ → ALE ↑ delay time                                                 | tonu   |              | 116  |      | ns    |

| RD low level width                                                      | twal   |              | 200  |      | ns    |

| ALE high level width                                                    | twlh   |              | 126  |      | ns    |

| Address → WR ↓ delay time                                               | toaw   |              | 233  |      | ns    |

| ALE ↓ → data output time                                                | tolod  |              |      | 193  | ns    |

| $\overline{ m WR}\downarrow  ightarrow$ data output time                | towod  |              |      | 100  | ns    |

|                                                                         |        |              | 63   |      | ns    |

| ALE ↓ → WR ↓ delay time *2                                              | tolw   | Refresh mode | 116  |      | ns    |

| Data set up time (vs. WR ↑)                                             | tsopwr |              | 150  |      | ns    |

| Data set up time (vs. WR ↓) *3                                          | tsodwr | Refresh mode | 33   |      | ns    |

| Data hold time (vs. WR ↑)                                               | tнwop  |              | 20   |      | ns    |

| WR ↑ → ALE ↑ delay time                                                 | towl   |              | 116  |      | ns    |

| WR low level width                                                      | twwL   |              | 200  |      | ns    |

<sup>\*1:</sup> The internal system clock (fclk) is the oscillation clock (fxx) divided by 2 or 8, depending on the STBC register specification. The value in this table is indicated as fxx = 12 MHz and fclk = fxx/2.

Remarks: This table shows the characteristics when the number of weight cycles is 0.

<sup>\*2:</sup> During pulse refresh operation, the falling edge of the WR signal is delayed by a half clock. Therefore, the value in the lower row is used as the value of tolw.

<sup>\*3:</sup> When accessing a pseudo-static RAM (μPD428128 etc.) from which the data is clocked in at the falling edge of the WR signal, the data set up time is not tsopws, but tsopws.

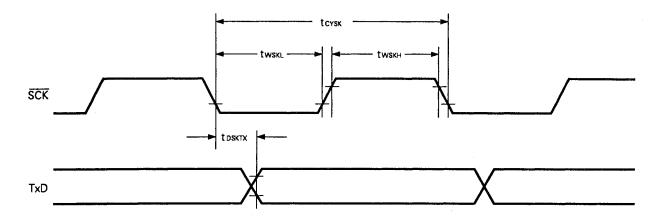

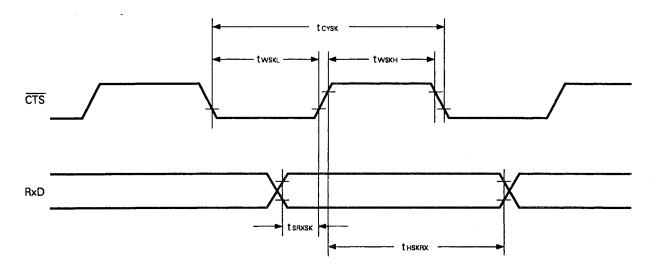

Serial Operation (Ta = -10°C to +70°C,  $VDD = +5.0 \text{ V} \pm 10\%$ , Vss = 0 V)

| ltem                                           | Symbol |        | Conditions |    | MIN. | MAX. | Units |

|------------------------------------------------|--------|--------|------------|----|------|------|-------|

|                                                |        |        | SCK        | *1 | 1.33 |      | με    |

| Serial clock cycle time                        | tcysk  | Output | CTS        | *2 | 1.33 |      | μs    |

|                                                |        | Input  | CTS        | *3 | 1    |      | μs    |

|                                                |        | 0      | SCK        | *1 | 580  |      | ns    |

| Serial clock low level width                   | twskL  | Output | CTS        | *2 | 580  |      | ns    |

|                                                |        | Input  | CTS        | *3 | 420  |      | ns    |

|                                                |        | 0      | SCK        | *1 | 580  |      | ns    |

| Serial clock high level width                  | twskH  | Output | CTS        | *2 | 580  |      | ns    |

|                                                |        | Input  | CTS        | *3 | 420  |      | ns    |

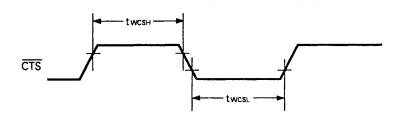

|                                                | twcsн, |        |            | *4 |      |      |       |

| CTS high, low level width                      | twcsL  |        |            |    | 3    |      | tcyk  |

| RxD set up time (vs. CTS ↑)                    | tsrxsk |        |            |    | 80   |      | ns    |

| RxD hold time (vs. CTS ↑)                      | thskax |        |            |    | 80   |      | ns    |

| $\overline{SCK} \downarrow \to TxD$ delay time | tosktx |        |            |    |      | 210  | ns    |

- \*1: When transmitting at 750 kbps in the I/O interface mode.

- \*2: When receiving at 750 kbps in the I/O interface mode.

- \*3: When receiving at 1 Mbps in the I/O interface mode.

- \*4: In the asynchronous mode.

A/D Converter Characteristics (Ta = -10°C to +70°C, VDD = +5 V  $\pm$ 10%, 4 V  $\leq$  AVREF  $\leq$  VDD, AVss = Vss = 0 V)

| Item                      | Symbol | Conditions                                  | MIN. | TYP.    | MAX.      | Units |

|---------------------------|--------|---------------------------------------------|------|---------|-----------|-------|

| Resolution                |        |                                             | 8    |         |           | bit   |

| Over all error *          |        | 4.0 V ≤ AVREF ≤ VDD, 166 ns ≤ tcyk ≤ 500 ns |      |         | 0.4       | %     |

| Quantified error          |        |                                             |      |         | ±1/2      | LSB   |

|                           |        | 166 ns ≤ tcvk ≤ 250 ns                      | 180  |         |           | tcyk  |

| Conversion time           | tconv  | 250 ns ≤ tcyk ≤ 500 ns                      | 120  | 0 ± 100 |           | tcyk  |

|                           |        | 166 ns ≤ tcvk ≤ 250 ns                      | 36   |         |           | tcyk  |

| Sampling time             | TSAMP  | 250 ns ≤ tcγκ ≤ 500 ns                      | 24   |         |           | tcyk  |

| Analog input              | VIAN   |                                             | -0.3 |         | AVREF+0.3 | ٧     |

| Analog input impedance    | RAN    |                                             |      | 1000    |           | МΩ    |

| Reference voltage         | AVREF  | ·                                           | 4    |         | Voo       | ٧     |

| AV <sub>REF</sub> current | Aires  | fclk = 6 MHz                                |      | 1.5     | 5.0       | mA    |

<sup>\*:</sup> Not including any quantified errors. Expressed as a percentage of the full-scale value.

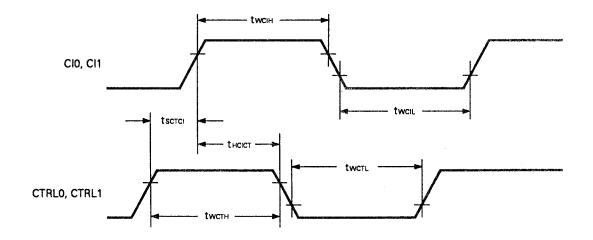

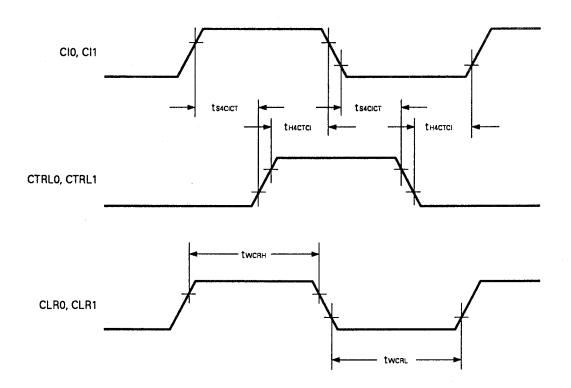

# Count Unit Operation (Ta = -10°C to +70°C, $V_{DD}$ = +5.0 V ±10%, $V_{SS}$ = 0 V)

| ltem                                | Symbol          | Conditions                                                                                                             | MIN. | MAX. | Units |

|-------------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------|------|------|-------|

| Cl0, Cl1 high, low level width      | twoih,          |                                                                                                                        | 3    |      | tcyk  |

| CTRL0, CTRL1 high, low level width  | twcтн,<br>twcтL |                                                                                                                        | 3    |      | tcyk  |

| CTRL0, CTRL1 set up time (vs. Cl 1) | tscrci          | When the operation mode of the count unit is specified as mode 3, and the CI pin input to the rising edge is effective | 2    |      | tcyk  |

| CTRL0, CTRL1 hold time (vs. Cl ↑)   | tнсіст          | When the operation mode of the count unit is specified as mode 3, and the CI pin input to the rising edge is effective | 5    |      | tcyk  |

| CLR0, CLR1 high, low level width    | twenh,          |                                                                                                                        | 3    | -    | tcyk  |

| CIO, CI1 set up time (vs. CI 1)     | ts4ctci         | With the operation mode of the count unit is specified as mode 4                                                       | 6    |      | tcyk  |

| Cl0, Cl1 hold time (vs. Cl ↑)       | TH4CICT         | With the operation mode of the count unit is specified as mode 4                                                       | 6    |      | tcyk  |

| Cl0, Cl1, CTRL0, CTRL1 cycle time   | tcyc4           | With the operation mode of the count unit is specified as mode 4                                                       | 4    |      | μs    |

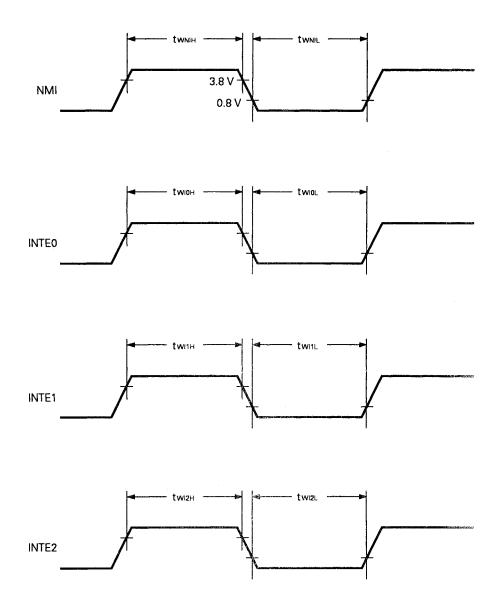

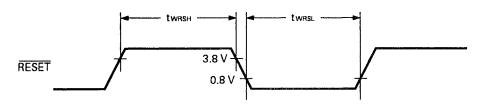

# Other Operation (Ta = -10°C to +70°C, $V_{DD}$ = +5.0 V ±10%, $V_{SS}$ = 0 V)

| ltem                          | Symbol | Conditions | MIN. | MAX. | Units |

|-------------------------------|--------|------------|------|------|-------|

| NMI high, low level width     | twnih, |            | 10   |      |       |

| Name ingli, low level width   | twniL  |            | 10   |      | μs    |

| NTE0 high, low level width    | twюн,  |            | 3    | -    | tcyk  |

| Title High, low level width   | twioL  |            |      |      | LCTK  |

| INTE1 high, low level width   | twiih, |            | 3    |      | tcyk  |

| Title ingli, low level width  | twiiL  |            |      |      |       |

| INTE2 high, low level width   | twizh, |            | 3    |      | tcyk  |

| w. L                          | twi2L  |            |      |      |       |

| RESET high, low level width   | twrsh, |            | 10   |      | μs    |

|                               | twrsL  |            |      |      | سر    |

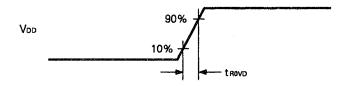

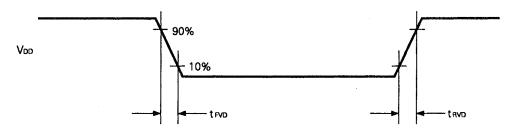

| Voo rise time (using SBF bit) | trovo  |            | 4    |      | ms    |

|                               |        |            |      |      |       |

| Vpp rise, fall time           | tavo,  |            | 200  |      | μs    |

|                               | trvo   |            |      |      |       |

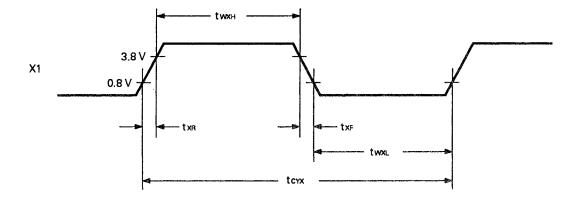

## External Clock Timing (Ta = -10°C to +70°C, $VDD = +5.0 \text{ V} \pm 10\%$ , Vss = 0 V)

| Item                      | Symbol | Conditions | MIN. | MAX. | Units |

|---------------------------|--------|------------|------|------|-------|

| X1 input high level width | twxн   |            | 30   | 130  | ns    |

| X1 input low level width  | twxL   |            | 30   | 130  | ns    |

| X1 input rise time        | txR    |            | 0    | 30   | ns    |

| X1 input fall time        | txF    |            | 0    | 30   | ns    |

| X1 input cycle time       | tcyx   |            | 83   | 250  | ns    |

## Definition of Bus Timing Depending on tcvk

| ltem         | Calculation formula                | MIN./MAX. | Units |

|--------------|------------------------------------|-----------|-------|

| <b>t</b> sal | 1.5T - 100                         | MIN.      | ns    |

| tdar         | 2T - 100                           | MIN.      | ns    |

| <b>TDAID</b> | (3.5 + n)T - 170                   | MAX.      | ns    |

| tolio        | (2 + n)T - 100                     | MAX.      | ns    |

| torio        | (1.5 + n)T - 70                    | MAX.      | ns    |

| TOLR         | 0.5T - 20                          | MIN.      | ns    |

| TDRL         | T - 50                             | MIN.      | ns    |

| tora         | 0.5T - 30                          | MIN.      | ns    |

| twaL         | (1.5 + n)T - 50                    | MIN.      | ns    |

| twLH         | T - 40                             | MIN.      | ns    |

| toaw         | 2T - 100                           | MIN.      | ns    |

| tolop        | 0.5T + 110                         | MAX.      | ns    |

| •            | 0.5T - 20 (Normal operation)       | MIN.      | ns    |

| toLW         | T - 50 (Refresh mode)              | MIN.      | ns    |

| tsoowr       | (1.5 + n)T - 100                   | MIN.      | ns    |

| tsopwf       | 0.5T - 50                          | MIN.      | ns    |

| towL         | T - 50                             | MIN.      | ns    |

| •            | (1.5 + n)T - 50 (Normal operation) | MIN.      | ns    |

| twwL         | (1 + n)T - 50 (Refresh mode)       | MIN.      | ns    |

Remarks 1: n is the number of WAIT states inserted by the specification in the MM register.

2: T = tcyk = 1/fclk (fclk is the internal system clock frequency)

3: Items not shown in this table do not depend on the frequency of the internal system clock (fclk).

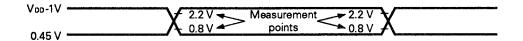

## **AC Timing Measurement Position**

## **Timing Wave-Forms**

## Read operation:

## Write operation:

## Serial Operation:

## Transmission in I/O interface mode:

## Receive in I/O interface mode:

## Transmit enable input timing (asynchronous mode):

## **Count Unit Input Timing**

## Mode 3 operation

## Mode 4 operation

# Interrupt Input Timing

# Reset Input Timing

# **External Clock Timing**

# **Power On Timing**

## **Data Retention Timing**

# DC Programming Characteristics (Ta = $25 \pm 5$ °C, V<sub>IP</sub> = $12.0 \pm 0.5$ V, Vss = 0 V)

| ltem                                  | Symbol | Symbol* | Conditions                                                                          | MIN.       | TYP. | MAX.                     | Units |

|---------------------------------------|--------|---------|-------------------------------------------------------------------------------------|------------|------|--------------------------|-------|

| High level input voltage              | ViH    | ViH     |                                                                                     | 2.2        |      | V <sub>DDP</sub><br>+0.3 | V     |

| Low level input voltage               | VIL    | VIL     |                                                                                     | -0.3       |      | 0.8                      | ٧     |

| Input leakage current                 | ILIP   | lu      | 0 ≤ V1 ≤ VDDP                                                                       |            |      | 10                       | μА    |

| High level output voltage             | Vон    | Vон     | loн = -1.0 mA                                                                       | Vpp-1      |      |                          | ٧     |

| Low level output voltage              | Vol    | Vol     | lot = 2.0 mA                                                                        |            |      | 0.45                     | V     |

| Output leakage current                | ILO    | -       | 0 ≤ Vo ≤ VDDP, OE = VIH                                                             |            |      | 10                       | μΑ    |

| PROG pin high voltage input current   | lip    | -       |                                                                                     |            |      | ±10                      | μА    |

| V <sub>DDP</sub> power supply voltage | VDDP   | Voo     | Program memory write mode                                                           | 5.75       | 6.0  | 6.25                     | ٧     |

| Voor power supply voitage             | ₩ DOF  | 400     | Program memory read mode                                                            | 4.5        | 5.0  | 5.5                      | V     |

| V <sub>PP</sub> power supply voltage  | VPP    | Vpp     | Program memory write mode                                                           | 12.2       | 12.5 | 12.8                     | V     |

| VPP power supply vortage              | VPP    | VPP     | Program memory read mode                                                            | VPP = VDDP |      | ٧                        |       |

|                                       | 1      | lpp     | Program memory write mode                                                           |            | 10   | 30                       | mA    |

| V <sub>DDP</sub> power supply current | loo    | 1DD _   | Program memory read mode<br>CE = V <sub>IL</sub> , V <sub>I</sub> = V <sub>IH</sub> |            | 10   | 30                       | mA    |

| V <sub>PP</sub> power supply current  | Ірр    | Ірр     | Program memory write mode                                                           |            | 10   | 30                       | mA    |

|                                       |        | -       | Program memory read mode                                                            |            | 1    | 100                      | μА    |

<sup>\*:</sup> Corresponding symbols in the  $\mu$ PD27C256A.

# AC Programming Characteristics (Ta = 25 $\pm 5^{\circ}$ C, V<sub>IP</sub> = 12.0 $\pm 0.5$ V, Vss = 0 V)

| ltem                                                           | Symbol | Symbol* | Conditions | MIN. | TYP. | MAX.  | Units |

|----------------------------------------------------------------|--------|---------|------------|------|------|-------|-------|

| Address set up time_<br>(vs. CE ↓)                             | tsac   | tas     |            | 2    |      |       | μs    |

| Data → OE ↓ delay time                                         | topoo  | toes    |            | 2    |      |       | μs    |

| Input data set up time<br>(vs. CE 1)                           | tsioc  | tos     |            | 2    |      |       | μs    |

| Address hold time<br>(vs. CE ↑)                                | THCA   | tah     |            | 2    |      |       | με    |

| Input data hold time<br>(vs. CE ↑)                             | thcid  | tон     |            | 2    |      | -     | μs    |

| Output data hold ti <u>me</u><br>(vs. OE ↑)                    | tноор  | tor     |            | 0    |      | 130   | ns    |

| V <sub>PP</sub> set up time<br>(vs. CE ↓)                      | tsvrc  | tvps    |            | 2    |      |       | μs    |

| V <sub>DOP</sub> set up time<br>(vs. $\overline{\text{CE}}$ ↓) | tsvoc  | tvos    |            | 2    |      |       | μs    |

| Initial program<br>pulse width                                 | twL1   | tpw     |            | 0.95 | 1.0  | 1.05  | ms    |

| Additional program pulse width                                 | twL2   | topw    |            | 2.85 |      | 78.75 | ms    |

| PROG high voltage<br>input set up time<br>(vs. CE ↓)           | tspc   | -       |            | 2    |      |       | μs    |

| Address → Data output<br>time                                  | toaoo  | tacc    | ŌĒ = VIL   |      |      | 2     | μs    |

| OE ↓ → Data output time                                        | tpoop  | toe     |            |      |      | 1     | με    |

| Data hold time<br>(vs. OE ↑)                                   | tнсор  | tor     |            | 0    |      | 130   | ns    |

| Data hold time<br>(vs. Address)                                | THAOD  | tон     | OE = Vil   | 0    |      |       | ns    |

<sup>•:</sup> Corresponding symbols in the  $\mu$ PD27C256A.

## **PROM Write Mode Timing**

- Notes 1: VDDP must applied before VPP is applied, must be removed after VPP is removed.

- 2: Vm must not exceed +13 V, including overshoot voltage.

## **PROM Read Mode Timing**

## 5. EXTERNAL DIMENSIONS

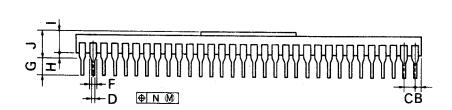

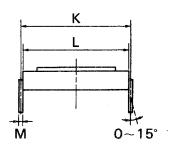

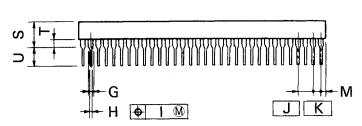

# 64PIN PLASTIC SHRINK DIP (750 mil)

P64C-70-750A,C

## **NOTES**

- Each lead centerline is located within 0.17 mm (0.007 inch) of its true position (T.P.) at maximum material condition.

- 2) Item "K" to center of leads when formed parallel.

| ITEM | MILLIMETERS           | INCHES                  |

|------|-----------------------|-------------------------|

| Α    | 58.68 MAX.            | 2.311 MAX.              |

| В    | 1.78 MAX.             | 0.070 MAX.              |

| С    | 1.778 (T.P.)          | 0.070 (T.P.)            |

| D    | 0.50 <sup>±0:10</sup> | 0.020-0.005             |

| F    | 0.9 MIN.              | 0.035 MIN.              |

| G    | 3.2 <sup>±0:3</sup>   | 0.126 <sup>±0.012</sup> |

| Н    | 0.51 MIN.             | 0.020 MIN.              |

| ı    | 4.31 MAX.             | 0.170 MAX.              |

| J    | 5.08 MAX.             | 0.200 MAX.              |

| К    | 19.05 (T.P.)          | 0.750 (T.P.)            |

| L    | 17.0                  | 0.669                   |

| М    | 0.25 -0.05            | 0.010 +0.004            |

| N    | 0.17                  | 0.007                   |

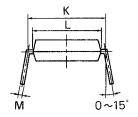

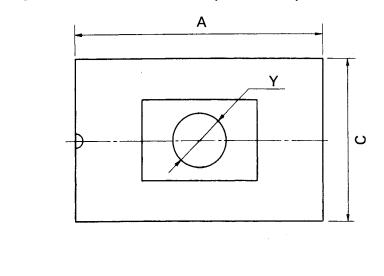

# 64 PIN PLASTIC QFP (14×20)

## NOTE

Each lead centerline is located within 0.20 mm (0.008 inch) of its true position (T.P.) at maximum material condition.

| P64GF-100-3B8,3BE,3BR-                 |                                                                                                                                               |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| MILLIMETERS                            | INCHES                                                                                                                                        |

| 23.6±0.4                               | 0.929±0.016                                                                                                                                   |

| 20.0±0.2                               | 0.795+0.009                                                                                                                                   |

| 14.0±0.2                               | 0.551+0.009                                                                                                                                   |

| 17.6±0.4                               | 0.693±0.016                                                                                                                                   |

| 1.0                                    | 0.039                                                                                                                                         |

| 1.0                                    | 0.039                                                                                                                                         |

| 0.40±0.10                              | 0.016+0.004                                                                                                                                   |

| 0.20                                   | 0.008                                                                                                                                         |

| 1.0 (T.P.)                             | 0.039 (T.P.)                                                                                                                                  |

| 1.8±0.2                                | 0.071+0.008                                                                                                                                   |

| 0.8±0.2                                | 0.031+0.009                                                                                                                                   |

| 0.15 <sup>+0.10</sup> <sub>-0.05</sub> | 0.006+0.004                                                                                                                                   |

| 0.12                                   | 0.005                                                                                                                                         |

| 2.7                                    | 0.106                                                                                                                                         |

| 0.1±0.1                                | 0.004±0.004                                                                                                                                   |

| 3.0 MAX.                               | 0.119 MAX.                                                                                                                                    |

|                                        | MILLIMETERS  23.6±0.4  20.0±0.2  14.0±0.2  17.6±0.4  1.0  1.0  0.40±0.10  0.20  1.0 (T.P.)  1.8±0.2  0.15 <sup>+0.10</sup> 0.12  2.7  0.1±0.1 |

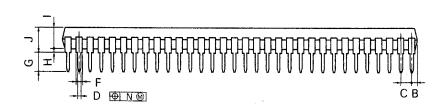

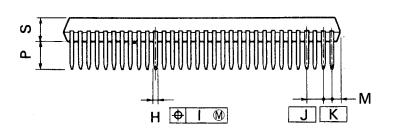

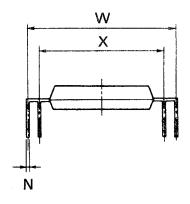

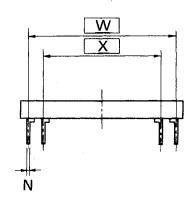

# **64 PIN PLASTIC QUIP**

P64GQ-100-36

## NOTE

Each lead centerline is located within 0.25 mm (0.010 inch) of its true position (T.P.) at maximum material condition.

| ITEM | MILLIMETERS            | INCHES                  |

|------|------------------------|-------------------------|

| Α    | 41.5 <sup>+8.3</sup>   | 1.634 <sup>±8.808</sup> |

| С    | 16.5                   | 0.650                   |

| н    | 0.50 <sup>±0.10</sup>  | 0.020 <sup>±8.886</sup> |

| ١.,  | 0.25                   | 0.010                   |

| J    | 2.54 (T.P.)            | 0.100 (T.P.)            |

| К    | 1.27 (T.P.)            | 0.050 (T.P.)            |

| М    | 1.1 +0.25              | 0.043 <sup>+8.801</sup> |

| N    | 0.25 ± 8.38            | 0.010 + 8.883           |

| Р    | 4.0 <sup>±0.3</sup>    | 0.157 + 0.013           |

| s    | 3.6 <sup>±0.1</sup>    | 0.142 <sup>+8.884</sup> |

| W    | 24.13 <sup>±1.05</sup> | 0.950 <sup>±0.042</sup> |

| Х    | 19.05 <sup>±1.05</sup> | 0.750 <sup>±0.042</sup> |

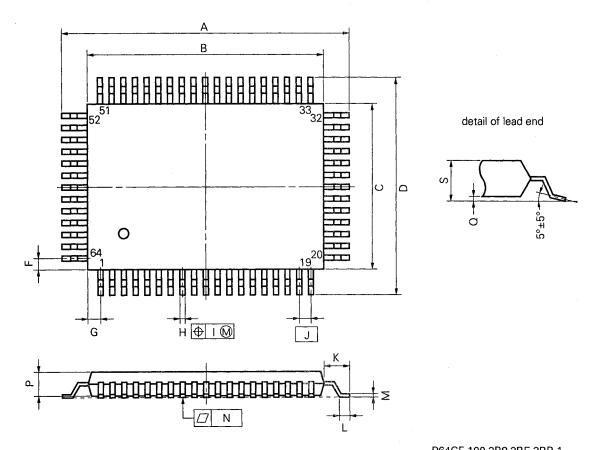

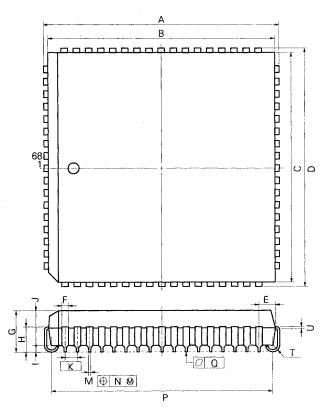

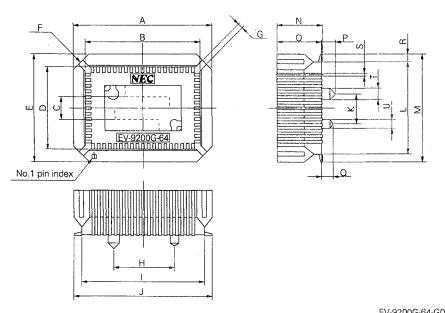

# 68 PIN PLASTIC QFJ (□950 mil)

NOTE

Each lead centerline is located within 0.12 mm (0.005 inch) of its true position (T.P.) at maximum material condition.

| •    |             | P68L-50A1-2  |

|------|-------------|--------------|

| ITEM | MILLIMETERS | INCHES       |

| Α    | 25.2±0.2    | 0.992±0.008  |

| В    | 24.20       | 0.953        |

| С    | 24.20       | 0.953        |

| D    | 25.2±0.2    | 0.992±0.008  |

| E    | 1.94±0.15   | 0.076+0.007  |

| F    | 0.6         | 0.024        |

| G    | 4.4±0.2     | 0.173+0.009  |

| Η    | 2.8±0.2     | 0.110+0.009  |

| 1    | 0.9 MIN.    | 0.035 MIN.   |

| J    | 3.4         | 0.134        |

| K    | 1.27 (T.P.) | 0.050 (T.P.) |

| М    | 0.40±1.0    | 0.016+0.004  |

| N    | 0.12        | 0.005        |

| Р    | 23.12±0.20  | 0.910+0.009  |

| Q    | 0.15        | 0.006        |

| Т    | R 0.8       | R 0.031      |

| U    | 0.20+0.10   | 0.008+0.004  |

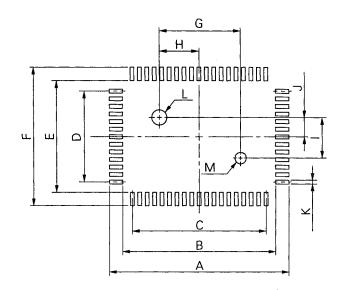

# 64PIN CERAMIC SHRINK DIP (750 mil)

P64DW-70-750A

## **NOTES**

- Each lead centerline is located within 0.25 mm (0.01 inch) of its true position (T.P.) at maximum material condition.

- 2) Item "K" to center of leads when formed parallel.

| ITEM | MILLIMETERS           | INCHES         |

|------|-----------------------|----------------|

| Α    | 58.68 MAX.            | 2.310 MAX.     |

| В    | 1.78 MAX.             | 0.070 MAX.     |

| С    | 1.778 (T.P.)          | 0.070 (T.P.)   |

| D    | 0.46 ±0.05            | 0.018 ±0.002   |

| F    | 0.8 MIN.              | 0.031 MIN.     |

| G    | 3.5 <sup>±0.3</sup>   | 0.138 ±0.012   |

| Н    | 1.0 MIN.              | 0.039 MIN.     |

| ı    | 3.0                   | 0.118          |

| J    | 5.08 MAX.             | 0.200 MAX.     |

| К    | 19.05 (T.P.)          | 0.750 (T.P.)   |

| L    | 18.8                  | 0.740          |