DATA SHEET

# μ**PD17704, 17705, 17707, 17708, 17709**

# 4-BIT SINGLE-CHIP MICROCONTROLLERS WITH DEDICATED HARDWARE FOR DIGITAL TUNING SYSTEM

The  $\mu$ PD17704, 17705, 17707, 17708, and 17709 are 4-bit single-chip CMOS microcontrollers containing hardware for digital tuning systems.

Provided with a wealth of hardware, these microcontrollers are available in many variations of ROM and RAM capacities to support various applications.

Therefore, a high-performance, multi-function digital tuning system can be configured with only one chip.

In addition, a one-time PROM model,  $\mu$ PD17P709, which can be written only once and therefore is ideal for program evaluation and small-scale production of a  $\mu$ PD17704, 17705, 17707, 17708, or 17709 system, is also available.

## FEATURES

NEC

★

|                                      | μPD17704                         | μPD17705                       | μPD17707             | μPD17708                          | μPD17709             |

|--------------------------------------|----------------------------------|--------------------------------|----------------------|-----------------------------------|----------------------|

| Program memory (ROM)                 | 16K bytes (8192 $	imes$ 16 bits) | 24K bytes<br>(12288 × 16 bits) |                      | 32K bytes (16384 $	imes$ 16 bits) |                      |

| General Purpose data<br>memory (RAM) | $672 \times 4$ bits              |                                | $1120 \times 4$ bits |                                   | $1776 \times 4$ bits |

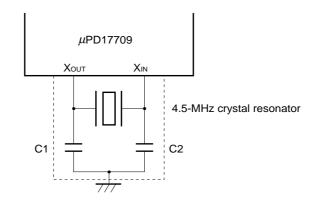

- Instruction execution time

1.78 μs (with fx = 4.5-MHz crystal oscillator)

- PLL frequency synthesizer Dual modulus prescaler (130 MHz MAX.), programmable divider, phase comparator, charge pump

- Abundant peripheral hardware units General-purpose I/O ports, serial interfaces, A/D converter, D/A converter (PWM output), BEEP output, frequency counter

- Many interrupts

- External : 6 sources Internal : 6 sources

- Power-ON reset, CE reset, and power failure detection circuit

- Supply voltage:  $V_{DD} = 5 V \pm 10 \%$

Unless otherwise specified, the  $\mu$ PD17709 is treated as the representative model in this document.

The information in this document is subject to change without notice.

# ORDERING INFORMATION

| Part Number                     | Package                                                                              |

|---------------------------------|--------------------------------------------------------------------------------------|

| μPD17704GC-×××-3B9              | 80-pin plastic QFP (14 $\times$ 14 mm, 0.65 mm pitch)                                |

| µPD17705GC-×××-3B9              | 80-pin plastic QFP (14 $	imes$ 14 mm, 0.65 mm pitch)                                 |

| µPD17707GC-×××-3B9              | 80-pin plastic QFP (14 $	imes$ 14 mm, 0.65 mm pitch)                                 |

| µPD17708GC-×××-3B9              | 80-pin plastic QFP (14 $	imes$ 14 mm, 0.65 mm pitch)                                 |

| $\mu$ PD17709GC- $\times$ ×-3B9 | 80-pin plastic QFP (14 $	imes$ 14 mm, 0.65 mm pitch)                                 |

|                                 | μPD17704GC-xxx-3B9<br>μPD17705GC-xxx-3B9<br>μPD17707GC-xxx-3B9<br>μPD17708GC-xxx-3B9 |

**Remark** ××× indicates a ROM code number.

#### FUNCTIONAL OUTLINE

| Item                      | Part Number         | μPD17704                                                                                                                                                                                                                                                                                                                         | μPD17705         | μPD17707             | μPD17708                            | μPD17709     |  |  |  |  |

|---------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------|-------------------------------------|--------------|--|--|--|--|

| Program mem               | ory (ROM)           | 16K bytes         24K bytes (12288 × 16 bits)         32K bytes (16384 × 16 bits)           (8192 × 16 bits)         24K bytes (16384 × 16 bits)         32K bytes (16384 × 16 bits)                                                                                                                                             |                  |                      | 384 × 16 bits)                      |              |  |  |  |  |

| General-purpos            | e data memory (RAM) | $672 \times 4$ bits                                                                                                                                                                                                                                                                                                              |                  | $1120 \times 4$ bits |                                     | 1176 × 4 bit |  |  |  |  |

| Instruction exe           | ecution time        | 1.78 $\mu$ s (with fx                                                                                                                                                                                                                                                                                                            | = 4.5-MHz cryst  | al oscillator)       |                                     |              |  |  |  |  |

| General-purpo             | ose port            | <ul> <li>I/O port : 46 pins</li> <li>Input port : 12 pins</li> <li>Output port: 4 pins</li> </ul>                                                                                                                                                                                                                                |                  |                      |                                     |              |  |  |  |  |

| Stack level               |                     | <ul> <li>Address stack: 15 levels</li> <li>Interrupt stack: 4 levels</li> <li>DBF stack : 4 levels (can be manipulated via software)</li> </ul>                                                                                                                                                                                  |                  |                      |                                     |              |  |  |  |  |

| Interrupt                 |                     | <ul> <li>External: 6 sources (falling edge of CE pin, INT0 through INT4)</li> <li>Internal: 6 sources (timers 0 through 3, serial interfaces 0 and 1)</li> </ul>                                                                                                                                                                 |                  |                      |                                     |              |  |  |  |  |

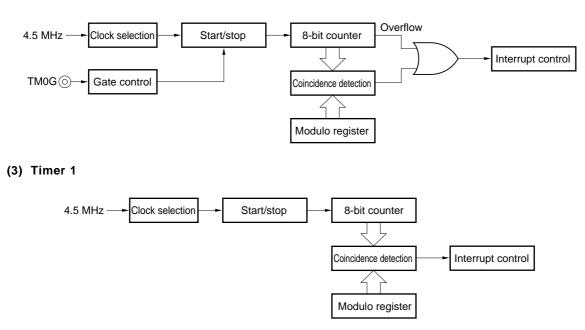

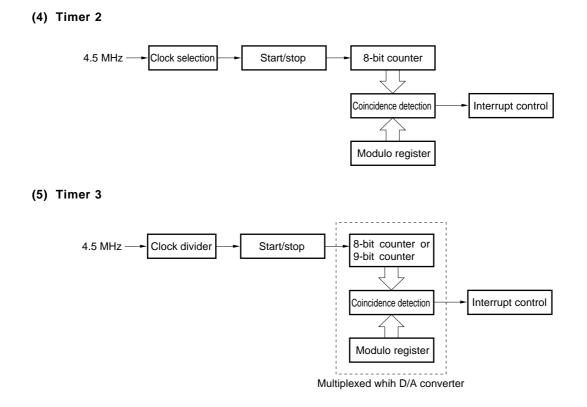

| Timer                     |                     | <ul> <li>5 channels</li> <li>Basic timer (clock: 10, 20, 50, 100 Hz) : 1 channel</li> <li>8-bit timer with gate counter (clock: 1 k, 2 k, 10 k, 100 kHz): 1 channel</li> <li>8-bit timer (clock: 1 k, 2 k, 10 k, 100 kHz) : 2 channels</li> <li>8-bit timer multiplexed with PWM (clock: 440 Hz, 4.4 kHz) : 1 channel</li> </ul> |                  |                      |                                     |              |  |  |  |  |

| A/D converter             |                     | 8 bits $\times$ 6 channels (hardware mode and software mode selectable)                                                                                                                                                                                                                                                          |                  |                      |                                     |              |  |  |  |  |

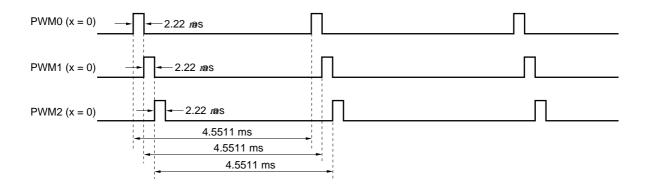

| D/A converter             | (PWM)               | 3 channels (8-bit or 9-bit resolution selectable by software)<br>Output frequency: 4.4 kHz, 440 Hz (with 8-bit PWM selected)<br>2.2 kHz, 220 Hz (with 9-bit PWM selected)                                                                                                                                                        |                  |                      |                                     |              |  |  |  |  |

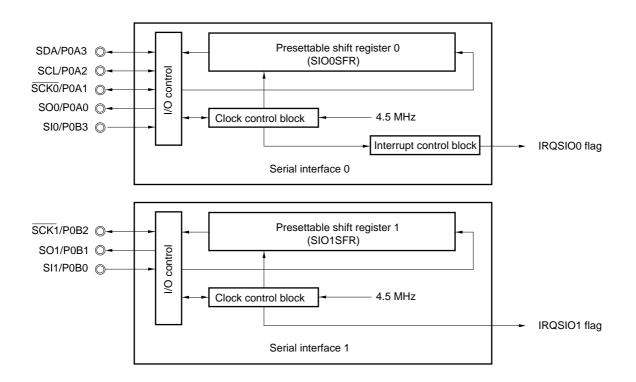

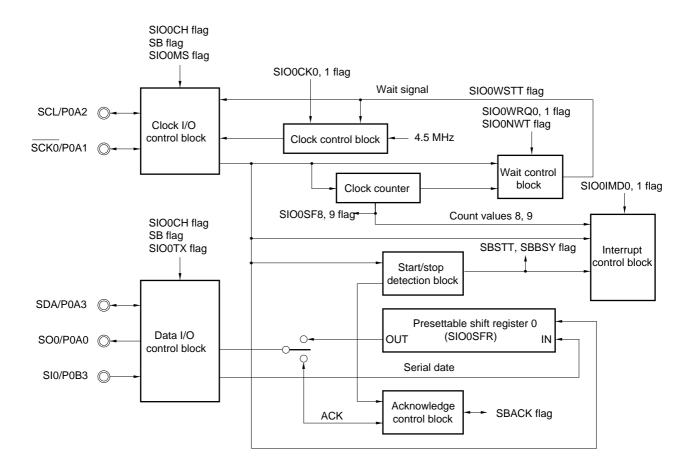

| Serial interfac           | e                   | 2 units (3 channels)<br>• 3-wire serial I/O : 2 channels<br>• 2-wire serial I/O/I <sup>2</sup> C bus: 1 channel                                                                                                                                                                                                                  |                  |                      |                                     |              |  |  |  |  |

| PLL frequency synthesizer | Division mode       | <ul> <li>Direct division mode (VCOL pin (MF mode) : 0.5 to 3 MHz)</li> <li>Pulse swallow mode (VCOL pin (HF mode) : 10 to 40 MHz)<br/>(VCOH pin (VHF mode): 60 to 130 MHz)</li> </ul>                                                                                                                                            |                  |                      |                                     |              |  |  |  |  |

|                           | Reference frequency | 13 types selectable (1, 1.25, 2.5, 3, 5, 6.25, 9, 10, 12.5, 18, 20, 25, 50 kHz)                                                                                                                                                                                                                                                  |                  |                      |                                     |              |  |  |  |  |

|                           | Charge pump         | Two error-out output pins (EO0, EO1)                                                                                                                                                                                                                                                                                             |                  |                      |                                     |              |  |  |  |  |

|                           | Phase comparator    | Unlock status d                                                                                                                                                                                                                                                                                                                  | etectable by pro | gram                 | Unlock status detectable by program |              |  |  |  |  |

NEC

| Part Number       | μPD17704                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | μPD17705                                                         | μPD17707       | μPD17708 | μPD17709       |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|----------------|----------|----------------|--|

| Frequency counter | <ul> <li>Intermediate frequency (IF) measurement<br/>P1C0/FMIFC pin: in FMIF mode 10 to 11 MHz<br/>in AMIF mode 0.4 to 0.5 MHz<br/>P1C1/AMIFC pin: in AMIF mode 0.4 to 0.5 MHz</li> <li>External gate width measurement<br/>P2A1/FCG1, P2A0/FCG0 pin</li> </ul>                                                                                                                                                                                                                             |                                                                  |                |          |                |  |

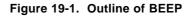

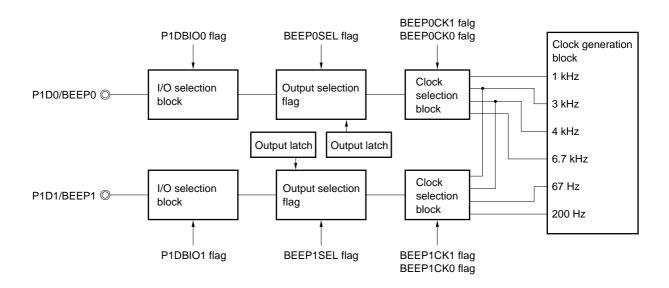

| BEEP output       | 2 pins<br>Output frequency: 1 kHz, 3 kHz, 4 kHz, 6.7 kHz (BEEP0 pin)<br>67 Hz, 200 Hz, 3 kHz, 4 kHz (BEEP1 pin)                                                                                                                                                                                                                                                                                                                                                                             |                                                                  |                |          |                |  |

| Reset             | <ul> <li>Power-ON reset (on power application)</li> <li>Reset by RESET pin</li> <li>Watchdog timer reset         Can be set only once on power application: 65536 instruction, 131072             instruction, or no-use selectable</li> <li>Stack pointer overflow/underflow reset         Can be set only once on power application: interrupt stack or address stack         selectable</li> <li>CE reset (CE pin low → high level)         CE reset delay timing can be set.</li> </ul> |                                                                  |                |          | use selectable |  |

| Standby           | <ul> <li>Power failure detection function</li> <li>Clock stop mode (STOP)</li> <li>Halt mode (HALT)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                              |                                                                  |                |          |                |  |

| Supply voltage    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | n: V <sub>DD</sub> = 4.5 to 5.<br>on: V <sub>DD</sub> = 3.5 to 5 |                |          |                |  |

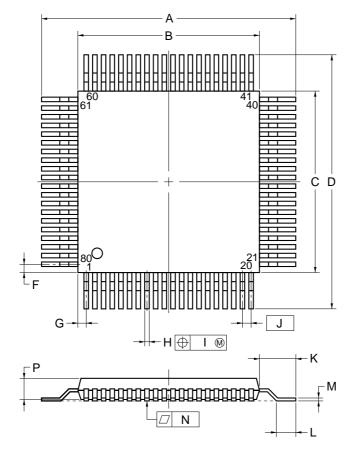

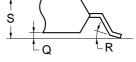

| Package           | 80-pin plastic (                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | QFP (14 $	imes$ 14 mm,                                           | 0.65 mm pitch) |          |                |  |

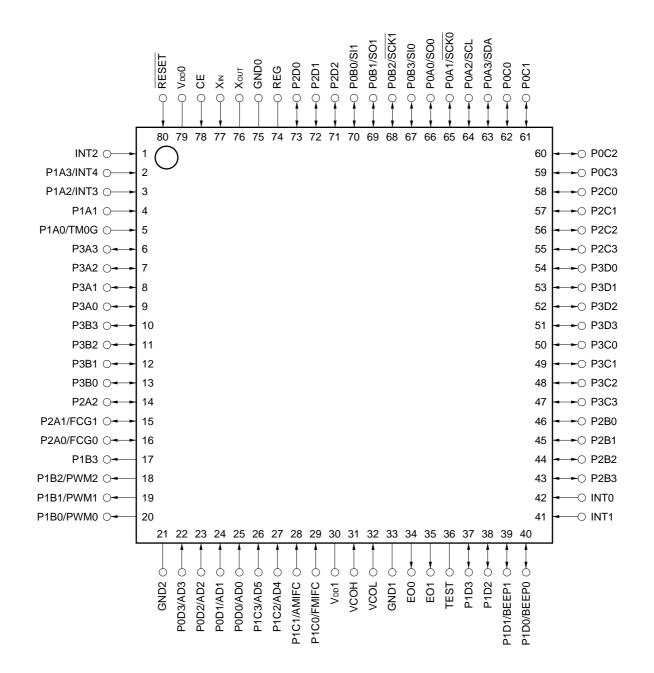

#### **PIN CONFIGURATION (Top View)**

80-pin plastic QFP (14  $\times$  14 mm, 0.65 mm pitch)

- ★ μPD17704GC-×××-3B9

★ μPD17705GC-×××-3B9

- μPD17707GC-×××-3B9 μPD17708GC-×××-3B9

- $\mu$ PD17709GC- $\times$ ×-3B9

# PIN NAME

| AD0-AD5     | : A/D converter input          | P2C0-P2C3  | : Port 2C                      |

|-------------|--------------------------------|------------|--------------------------------|

| AMIFC       | : AM frequency counter input   | P2D0-P2D2  | : Port 2D                      |

| BEEP0, BEEP | 1 : BEEP output                | P3A0-P3A3  | : Port 3A                      |

| CE          | : Chip enable                  | P3B0-P3B3  | : Port 3B                      |

| EO0, EO1    | : Error-out output             | P3C0-P3C3  | : Port 3C                      |

| FCG0, FGC1  | : Frequency counter gate input | P3D0-P3D3  | : Port 3D                      |

| FMIFC       | : FM frequency counter input   | REG        | : CPU regulator                |

| GND0-GND2   | : Ground 0 to 2                | RESET      | : Reset input                  |

| INT0-INT4   | : External interrupt input     | SCK0, SCK1 | : 3-wire serial clock I/O      |

| PWM0-PWM2   | : D/A converter output         | SCL        | : 2-wire serial clock I/O      |

| P0A0-P0A3   | : Port 0A                      | SDA        | : 2-wire serial data I/O       |

| P0B0-P0B3   | : Port 0B                      | SI0, SI1   | : 3-wire serial data input     |

| P0C0-P0C3   | : Port 0C                      | SO0, SO1   | : 3-wire serial data output    |

| P0D0-P0D3   | : Port 0D                      | TEST       | : Test input                   |

| P1A0-P1A3   | : Port 1A                      | TM0G       | : Timer 0 gate input           |

| P1B0-P1B3   | : Port 1B                      | VCOH       | : Local oscillation high input |

| P1C0-P1C3   | : Port 1C                      | VCOL       | : Local oscillation low input  |

| P1D0-P1D3   | : Port 1D                      | Vdd0, Vdd1 | : Power supply                 |

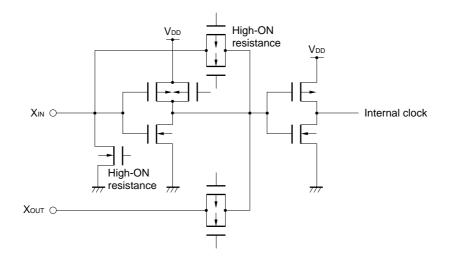

| P2A0-P2A2   | : Port 2A                      | Xin, Xout  | : Main clock oscillation       |

| P2B0-P2B3   | : Port 2B                      |            |                                |

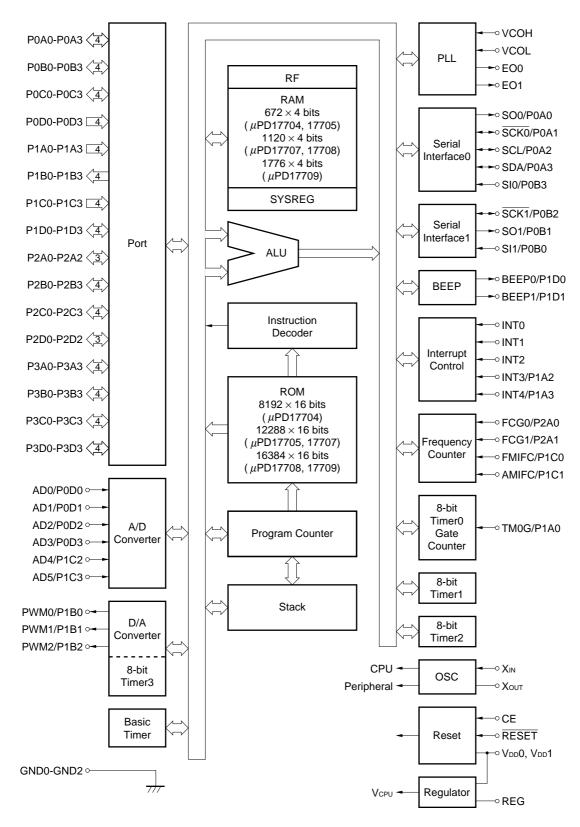

#### **BLOCK DIAGRAM**

# TABLE OF CONTESNTS

| 1. | PIN F | UNCTIONS                                                                     | 11 |

|----|-------|------------------------------------------------------------------------------|----|

|    | 1.1   | Pin Function List                                                            | 11 |

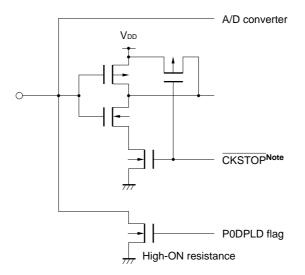

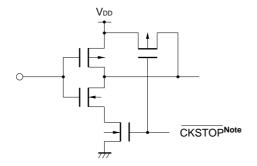

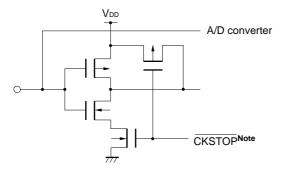

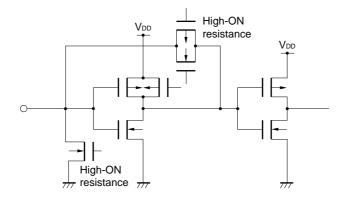

|    | 1.2   | Equivalent Circuits of Pins                                                  | 16 |

|    | 1.3   | Connections of Unused Pins                                                   |    |

|    | 1.4   | Cautions on Using CE, INT0 through INT4, and RESET Pins                      | 23 |

|    | 1.5   | Cautions on Using TEST Pin                                                   | 23 |

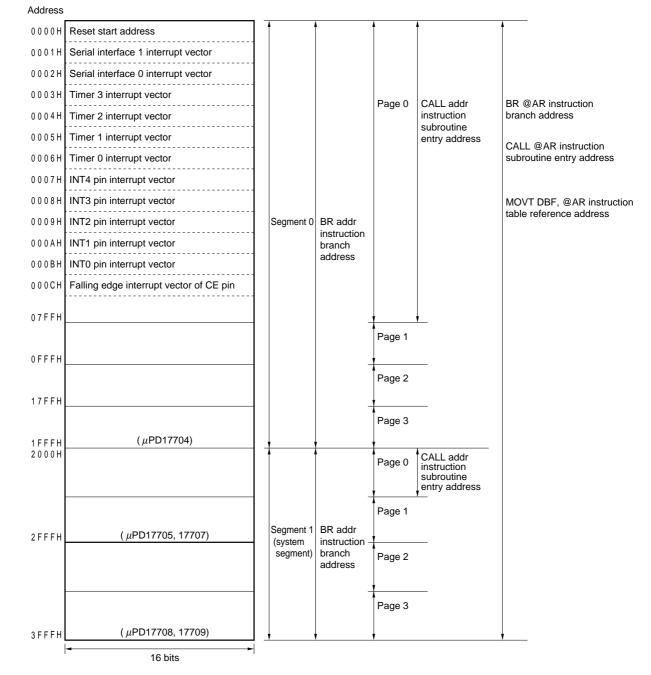

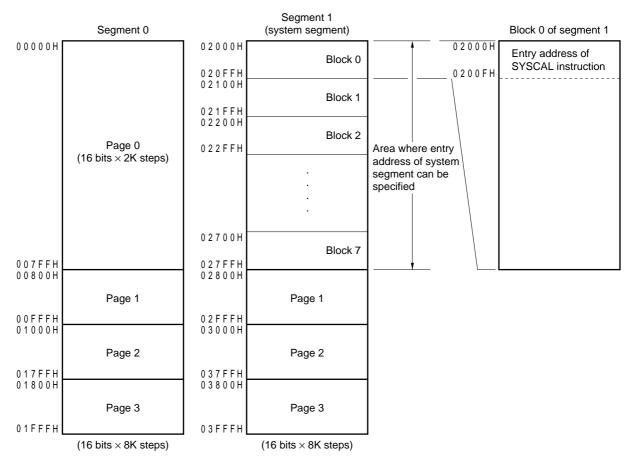

| 2. | PRO   | GRAM MEMORY (ROM)                                                            | 24 |

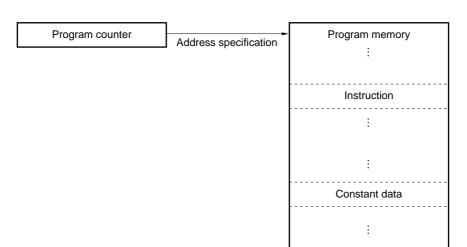

|    | 2.1   | Outline of Program Memory                                                    |    |

|    | 2.2   | Program Memory                                                               | 25 |

|    | 2.3   | Program Counter                                                              |    |

|    | 2.4   | Flow of Program                                                              |    |

|    | 2.5   | Cautions on Using Program Memory                                             |    |

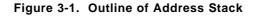

| 3. | ADD   | RESS STACK (ASK)                                                             | 30 |

|    | 3.1   | Outline of Address Stack                                                     | 30 |

|    | 3.2   | Address Stack Register (ASR)                                                 | 30 |

|    | 3.3   | Stack Pointer (SP)                                                           |    |

|    | 3.4   | Operation of Address Stack                                                   |    |

|    | 3.5   | Cautions on Using Address Stack                                              |    |

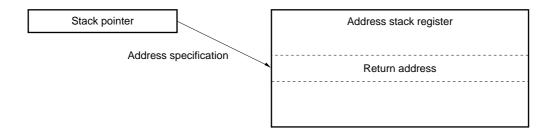

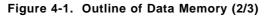

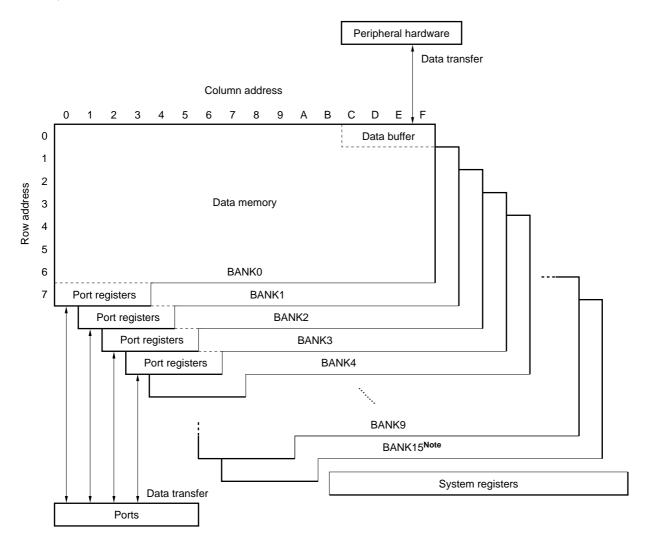

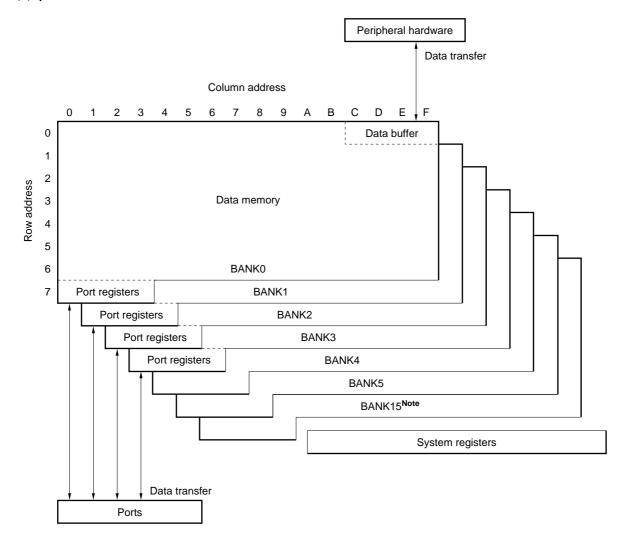

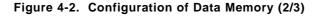

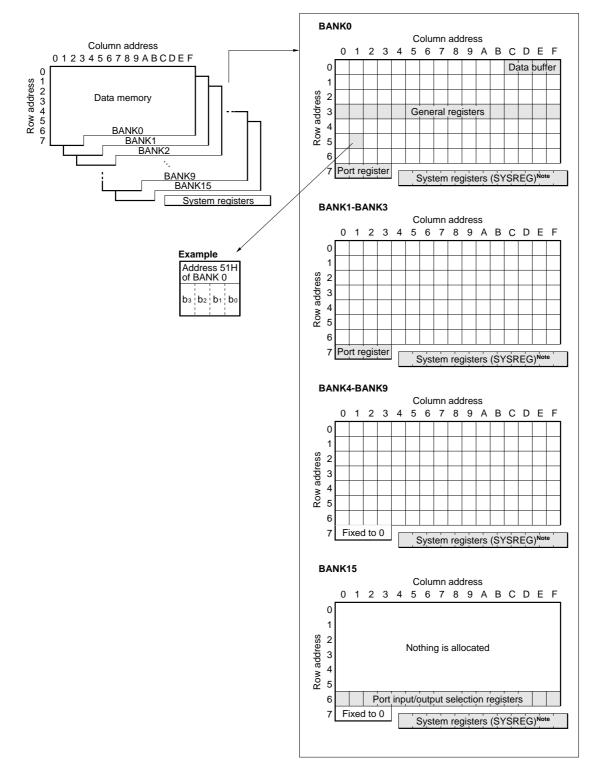

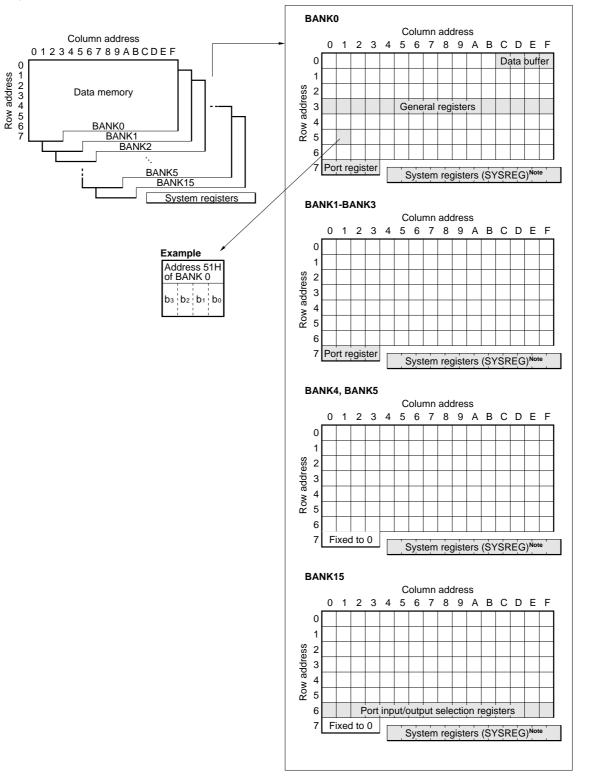

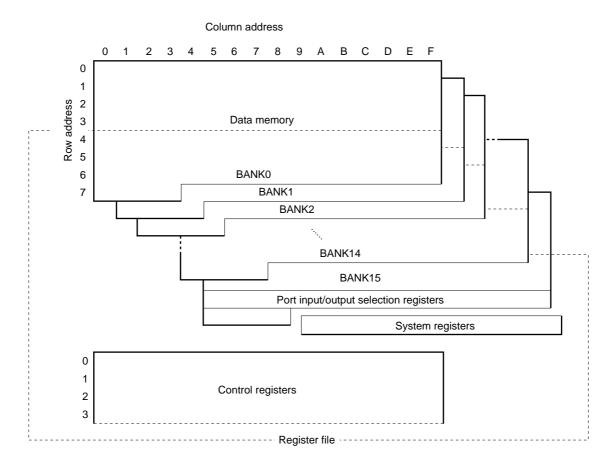

| 4. | DATA  | MEMORY (RAM)                                                                 | 35 |

|    | 4.1   | Outline of Data Memory                                                       |    |

|    | 4.2   | Configuration and Function of Data Memory                                    | 38 |

|    | 4.3   | Data Memory Addressing                                                       |    |

|    | 4.4   | Cautions on Using Data Memory                                                |    |

| 5. | SYST  | EM REGISTERS (SYSREG)                                                        | 44 |

|    | 5.1   | Outline of System Registers                                                  | 44 |

|    | 5.2   | System Register List                                                         | 45 |

|    | 5.3   | Address Register (AR)                                                        |    |

|    | 5.4   | Window Register (WR)                                                         |    |

|    | 5.5   | Bank Register (BANK)                                                         | 49 |

|    | 5.6   | Index Register (IX) and Data Memory Row Address Pointer (MP: memory pointer) | 50 |

|    | 5.7   | General Register Pointer (RP)                                                | 52 |

|    | 5.8   | Program Status Word (PSWORD)                                                 | 54 |

| 6. | GENE  | ERAL REGISTER (GR)                                                           | 56 |

|    | 6.1   | Outline of General Register                                                  |    |

|    | 6.2   | General Register                                                             |    |

|    | 6.3   | Generating Address of General Register by Each Instruction                   | 57 |

|    | 6.4   | Cautions on Using General Register                                           | 57 |

|    |       |                                                                              |    |

# NEC

| 7.  | ALU ( | Arithmetic Logic Unit) BLOCK                                                          | 58  |

|-----|-------|---------------------------------------------------------------------------------------|-----|

|     | 7.1   | Outline of ALU Block                                                                  | 58  |

|     | 7.2   | Configuration and Function of Each Block                                              | 59  |

|     | 7.3   | ALU Processing Instruction List                                                       | 59  |

|     | 7.4   | Cautions on Using ALU                                                                 | 63  |

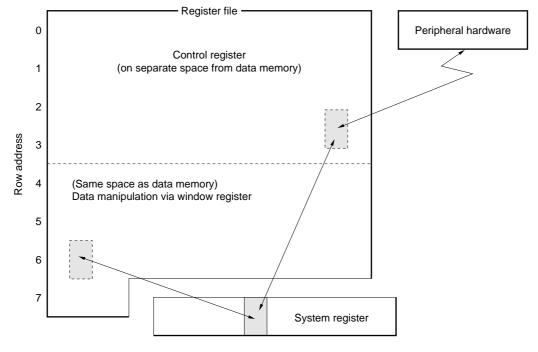

| 8.  | REGIS | TER FILE (RF)                                                                         | 64  |

|     | 8.1   | Outline of Register File                                                              | 64  |

|     | 8.2   | Configuration and Function of Register File                                           | 65  |

|     | 8.3   | Control Registers                                                                     | 66  |

|     | 8.4   | Port Input/Output Selection Registers                                                 | 78  |

|     | 8.5   | Cautions on Using Register File                                                       |     |

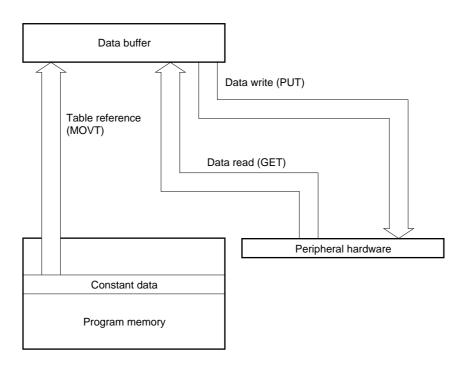

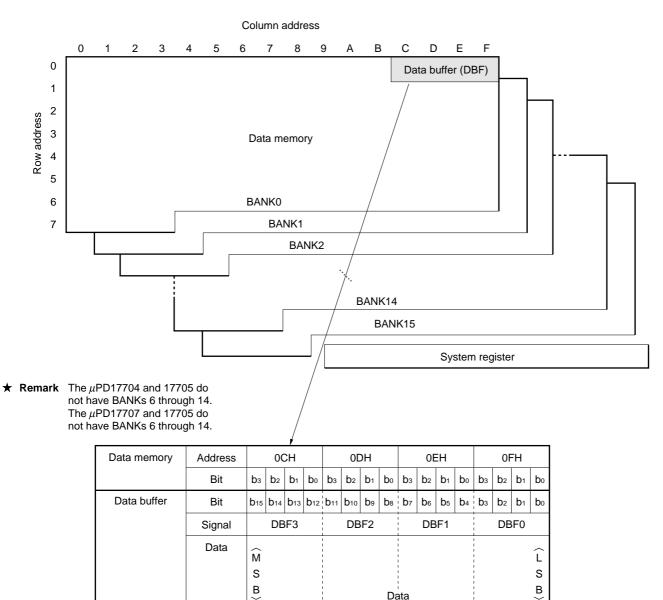

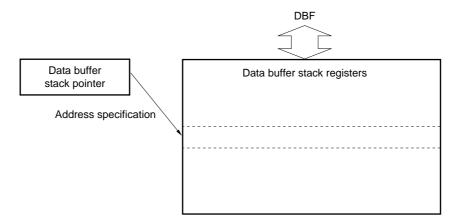

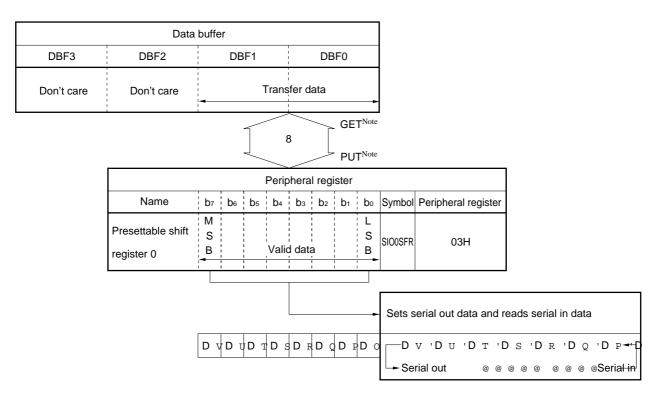

| 9.  | DATA  | BUFFER (DBF)                                                                          | 85  |

| •   | 9.1   | Outline of Data Buffer                                                                |     |

|     | 9.2   | Data Buffer                                                                           |     |

|     | 9.3   | Relationships between Peripheral Hardware and Data Buffer                             |     |

|     | 9.4   | Cautions on Using Data Buffer                                                         |     |

|     |       |                                                                                       |     |

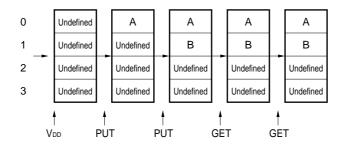

| 10. |       | BUFFER STACK                                                                          |     |

|     | 10.1  | Outline of Data Buffer Stack                                                          |     |

|     | 10.2  | Data Buffer Stack Register                                                            |     |

|     | 10.3  | Data Buffer Stack Pointer                                                             |     |

|     | 10.4  | Operation of Data Buffer Stack                                                        |     |

|     | 10.5  | Using Data Buffer Stack                                                               |     |

|     | 10.6  | Cautions on Using Data Buffer Stack                                                   | 95  |

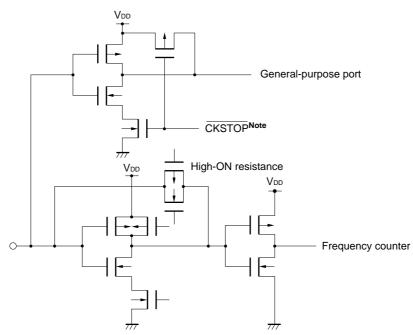

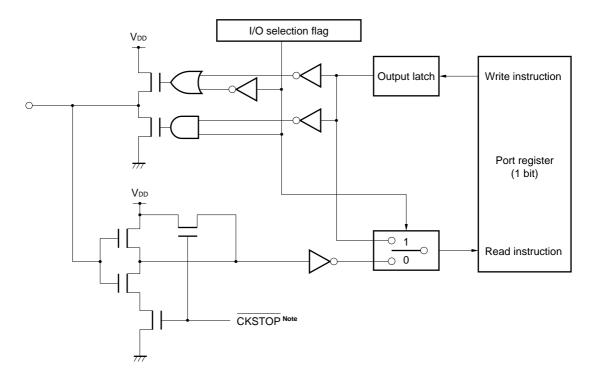

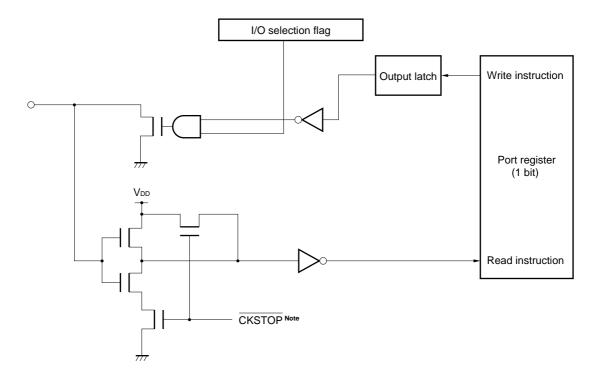

| 11. | GENE  | RAL-PURPOSE PORT                                                                      | 96  |

|     | 11.1  | Outline of General-purpose Port                                                       | 96  |

|     | 11.2  | General-Purpose I/O Port (P0A, P0B, P0C, P1D, P2A, P2B, P2C, P2D, P3A, P3B, P3C, P3D) | 99  |

|     | 11.3  | General-Purpose Input Port (P0D, P1A, P1C)                                            |     |

|     |       | General-Purpose Output Port (P1B)                                                     |     |

|     |       |                                                                                       |     |

| 12. |       | RRUPT                                                                                 |     |

|     | 12.1  | Outline of Interrupt Block                                                            |     |

|     | 12.2  | Interrupt Control Block                                                               |     |

|     | 12.3  | Interrupt Stack Register                                                              |     |

|     | 12.4  | Stack Pointer, Address Stack Registers, and Program Counter                           |     |

|     | 12.5  | Interrupt Enable Flip-Flop (INTE)                                                     |     |

|     | 12.6  | Accepting Interrupt                                                                   |     |

|     | 12.7  | Operations after Interrupt Has Been Accepted                                          |     |

|     | 12.8  | Returning from Interrupt Routine                                                      |     |

|     | 12.9  | External Interrupts (CE and INT0 through INT4 pins)                                   |     |

|     | 12.10 | Internal Interrupts                                                                   | 147 |

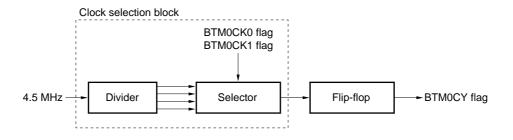

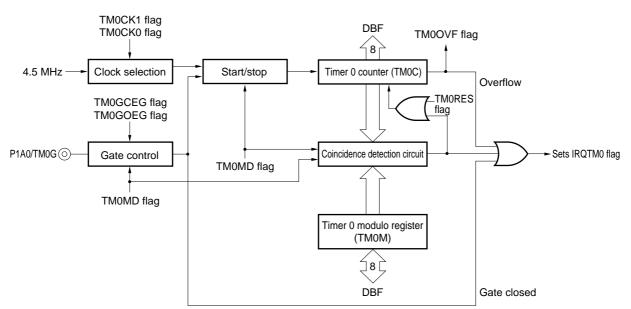

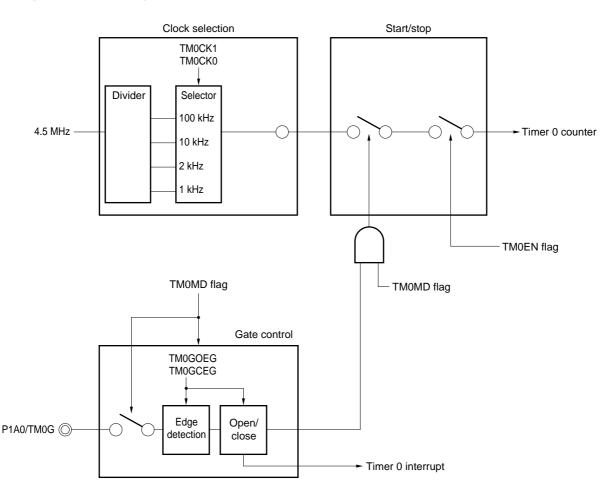

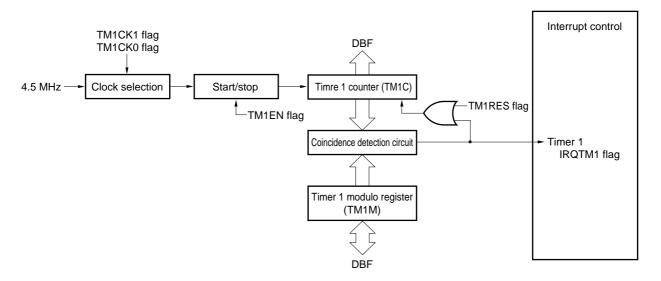

| 13  | TIME  | RS                                                                                    | 148 |

|     | 13.1  | Outline of Timers                                                                     |     |

|     |       |                                                                                       |     |

|     | 13.2  | Basic Timer 0                                            | 150 |

|-----|-------|----------------------------------------------------------|-----|

|     | 13.3  | Timer 0                                                  | 163 |

|     | 13.4  | Timer 1                                                  | 172 |

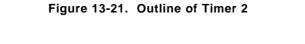

|     | 13.5  | Timer 2                                                  | 179 |

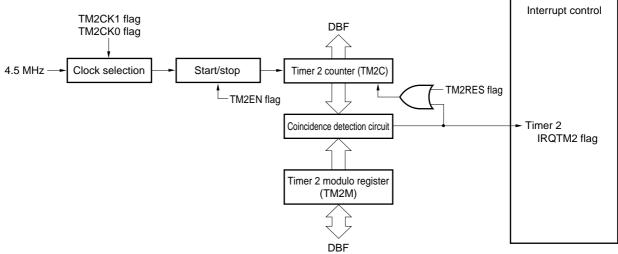

|     | 13.6  | Timer 3                                                  | 186 |

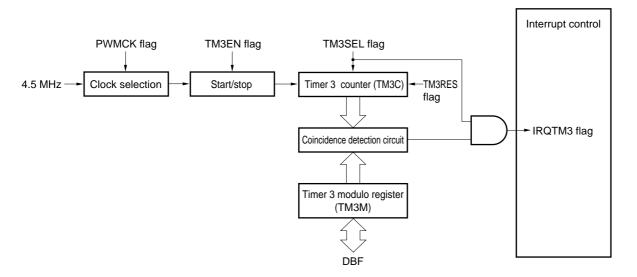

| 11  |       | ONVERTER                                                 | 102 |

|     | 14.1  | Outline of A/D Converter                                 |     |

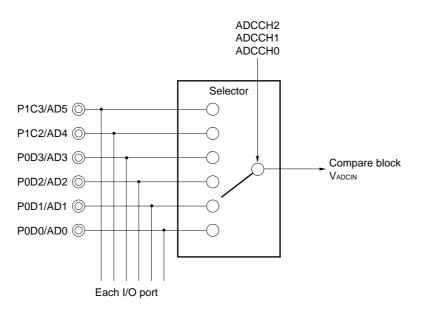

|     | 14.2  | Input Selection Block                                    |     |

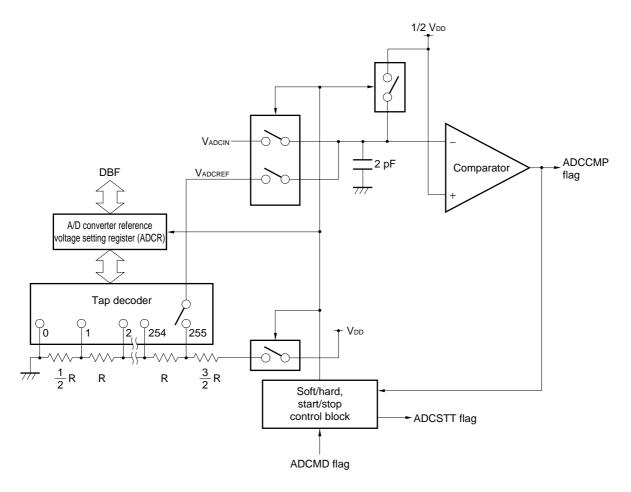

|     | 14.3  | Compare Voltage Generation and Compare Blocks            |     |

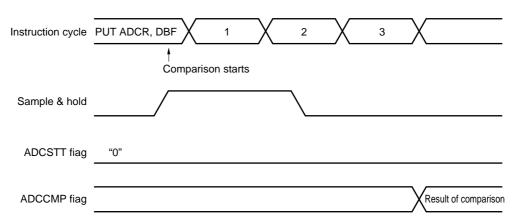

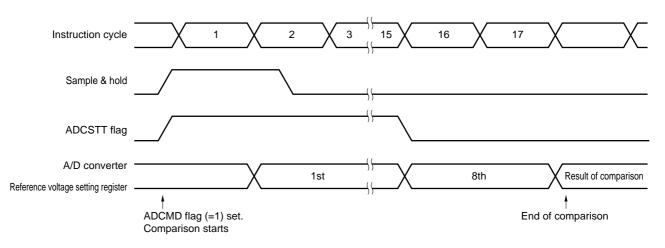

|     | 14.4  | Comparison Timing Chart                                  |     |

|     | 14.5  | Using A/D Converter                                      |     |

|     | 14.6  | Cautions on Using A/D Converter                          |     |

|     | 14.7  | Status at Reset                                          |     |

|     |       |                                                          |     |

| 15. |       | CONVERTER (PWM mode)                                     |     |

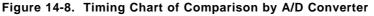

|     | 15.1  | Outline of D/A Converter                                 |     |

|     | 15.2  | PWM Clock Selection Register                             |     |

|     | 15.3  | PWM Output Selection Block                               |     |

|     | 15.4  | Duty Setting Block                                       |     |

|     | 15.5  | Clock Generation Block                                   |     |

|     | 15.6  | D/A Converter Output Wave                                |     |

|     | 15.7  | Example of Using D/A Converter                           |     |

|     | 15.8  | Status at Reset                                          | 215 |

| 16. | SERI  | AL INTERFACES                                            | 216 |

|     | 16.1  | Outline of Serial Interfaces                             | 216 |

|     | 16.2  | Serial Interface 0                                       | 217 |

|     | 16.3  | Serial Interface 1                                       | 245 |

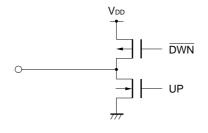

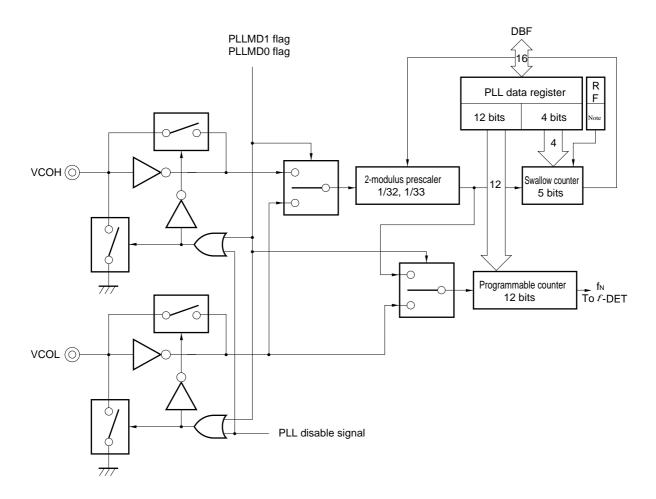

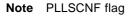

| 17. | PLL F | REQUENCY SYNTHESIZER                                     | 255 |

|     | 17.1  | Outline of PLL Frequency Synthesizer                     | 255 |

|     | 17.2  | Input Selection Block and Programmable Divider           | 256 |

|     | 17.3  | Reference Frequency Generator                            | 260 |

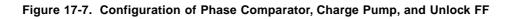

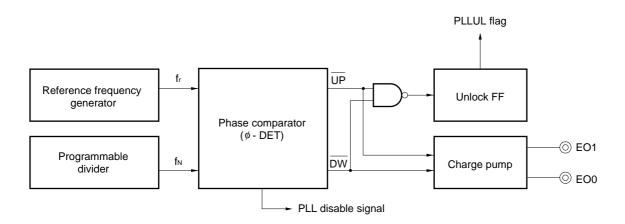

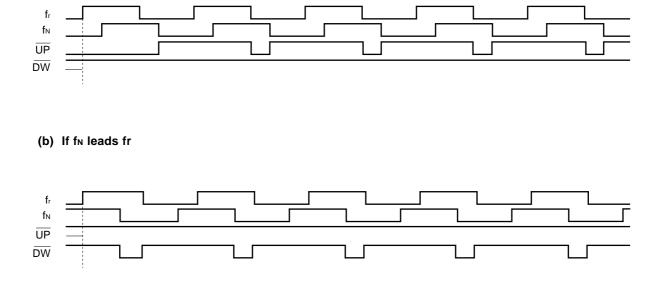

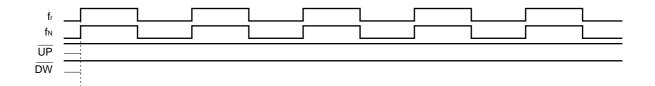

|     | 17.4  | Phase Comparator (¢-DET), Charge Pump, and Unlock FF     | 262 |

|     | 17.5  | PLL Disabled Status                                      | 266 |

|     | 17.6  | Using PLL Frequency Synthesizer                          | 267 |

|     | 17.7  | Status at Reset                                          | 271 |

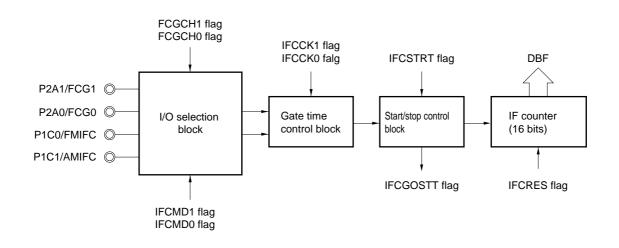

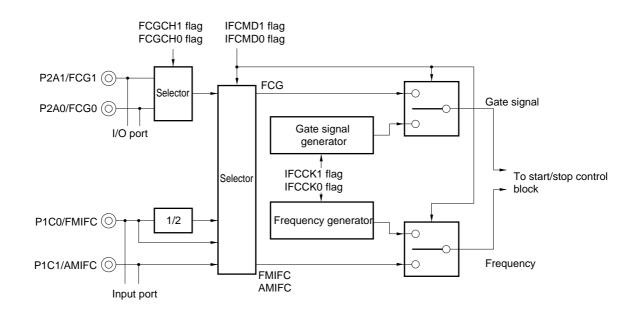

| 10  | EDEC  |                                                          | 272 |

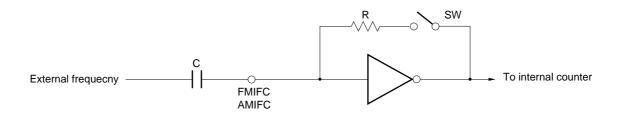

| 10. | 18.1  | Outline of Frequency Counter                             |     |

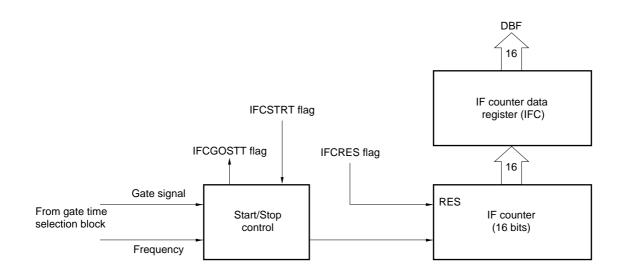

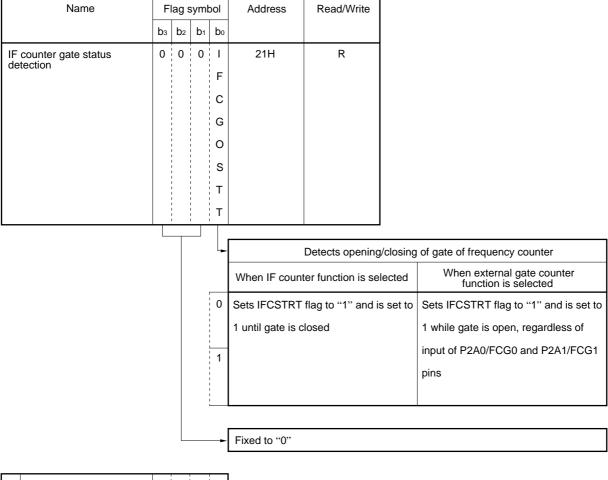

|     | 18.2  | Input/Output Selection Block and Gate Time Control Block |     |

|     | 18.3  | Start/Stop Control Block and IF Counter                  |     |

|     | 18.4  | Using IF Counter                                         |     |

|     | 18.5  | Using External Gate Counter                              |     |

|     | 18.6  | Status at Reset                                          |     |

|     | 0.01  | טומוש מו הכסכו                                           | 200 |

# NEC

| 19.         | BEEP  |                                                                  | 287 |

|-------------|-------|------------------------------------------------------------------|-----|

|             | 19.1  | Outline of BEEP                                                  | 287 |

|             | 19.2  | I/O Selection Block and Output Selection Block                   | 288 |

|             | 19.3  | Clock Selection Block and Clock Generation Block                 | 290 |

|             | 19.4  | Output Waveform of BEEP                                          | 291 |

|             | 19.5  | Status at Reset                                                  | 291 |

|             |       |                                                                  |     |

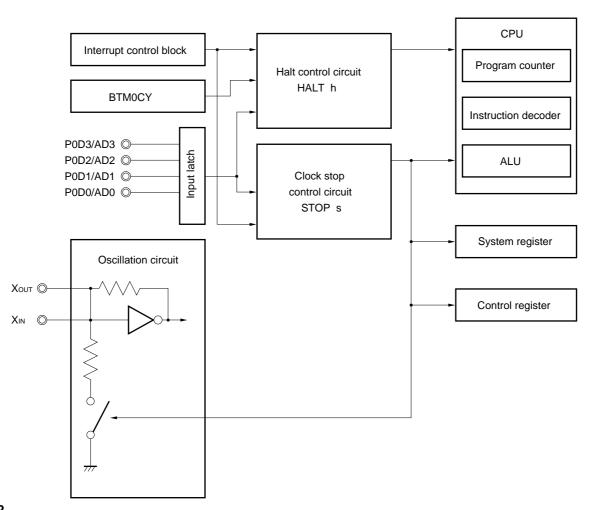

| 20.         | STAN  | DBY                                                              |     |

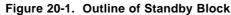

|             | 20.1  | Outline of Standby Function                                      | 292 |

|             | 20.2  | Halt Function                                                    | 293 |

|             | 20.3  | Clock Stop Function                                              |     |

|             | 20.4  | Device Operation in Halt and Clock Stop Status                   | 301 |

|             | 20.5  | Cautions on Processing of Each Pin in Halt and Clock Stop Status | 301 |

|             | 20.6  | Device Operation Control Function of CE Pin                      | 303 |

|             |       |                                                                  |     |

| 21.         |       | Т                                                                |     |

|             | 21.1  | Outline of Reset                                                 |     |

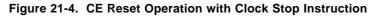

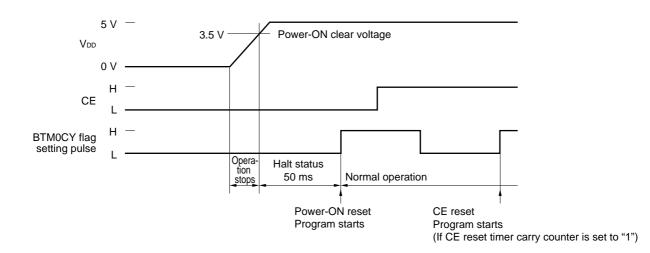

|             | 21.2  | CE Reset                                                         |     |

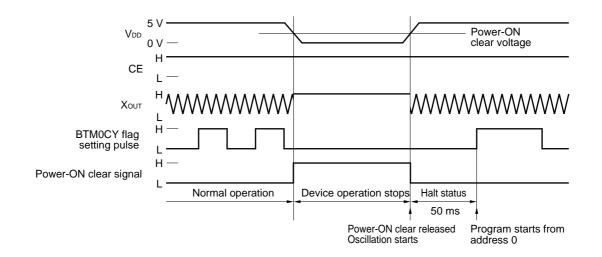

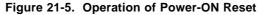

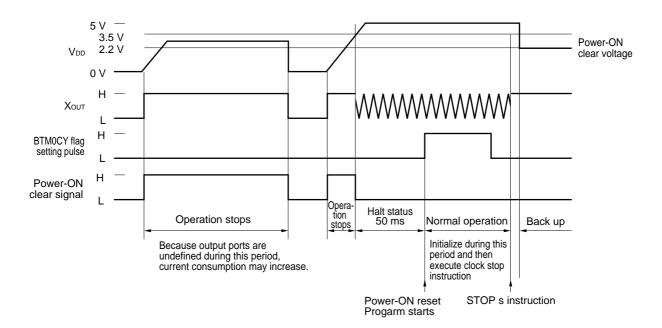

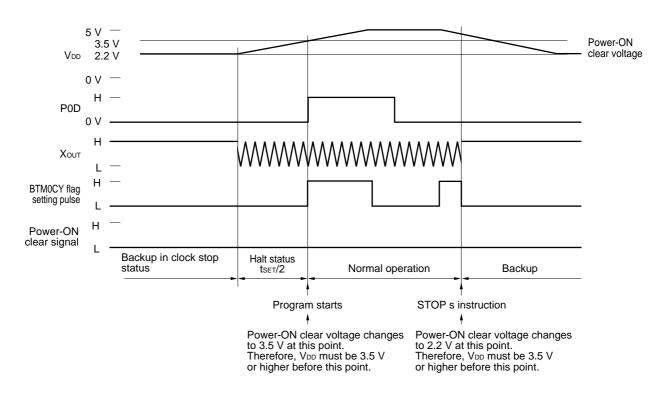

|             | 21.3  | Power-ON Reset                                                   |     |

|             | 21.4  | Relationship between CE Reset and Power-ON Reset                 |     |

|             | 21.5  | Reset by RESET Pin                                               | 320 |

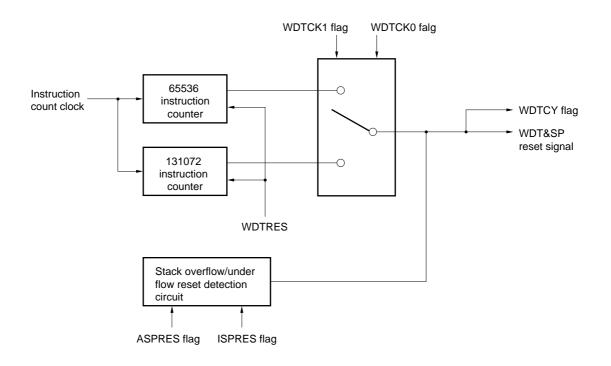

|             | 21.6  | WDT&SP Reset                                                     |     |

|             | 21.7  | Power Failure Detection                                          | 327 |

| 22          | INCTO |                                                                  | 222 |

| <b>ZZ</b> . | 22.1  | Outline of Instruction Set                                       |     |

|             | 22.1  | Legend                                                           |     |

|             | 22.2  | Instruction List                                                 |     |

|             | 22.3  | Assembler (RA17K) Embedded Macro Instruction                     |     |

|             | 22.7  |                                                                  | 550 |

| 23.         | RESE  | RVED SYMBOLS                                                     | 337 |

|             | 23.1  | Data Buffer (DBF)                                                | 337 |

|             | 23.2  | System Registers (SYSREG)                                        | 337 |

|             | 23.3  | Port Registers                                                   |     |

|             | 23.4  | Register File (Control Registers)                                | 340 |

|             | 23.5  | Peripheral Hardware Registers                                    |     |

|             | 23.6  | Others                                                           |     |

| ~ 4         |       |                                                                  | 240 |

| 24.         | ELEC  | TRICAL CHARACTERISTICS                                           | 340 |

| 25.         | PACK  | AGE DRAWING                                                      | 349 |

| 26          | RECO  | MMENDED SOLDERING CONDITIONS                                     | 350 |

| 20.         |       |                                                                  | 500 |

| API         | PENDI | X A. CAUTIONS ON CONNECTING CRYSTAL RESONATOR                    | 351 |

| API         | PENDI | X B. DEVELOPMENT TOOLS                                           | 352 |

## **1. PIN FUNCTIONS**

## 1.1 Pin Function List

| Pin No.          | Symbol                                      |                                                                                                       | Functio                      | n                               |                                 | Output Form       |

|------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------|------------------------------|---------------------------------|---------------------------------|-------------------|

| 1<br>41<br>42    | INT2<br>INT1<br>INT0                        | Edge-detectable ve<br>specified.                                                                      | lling edge can be            | _                               |                                 |                   |

| 2<br>3<br>4<br>5 | P1A3/INT4<br>P1A2/INT3<br>P1A1<br>P1A0/TM0G | 1A2/INT3signal input pins.1A1• P1A3 through P1A0                                                      |                              |                                 |                                 |                   |

|                  |                                             |                                                                                                       | At reset                     |                                 | With clock stopped              |                   |

|                  |                                             | Power-ON reset                                                                                        | WDT&SP reset                 | CE reset                        | -                               |                   |

|                  |                                             | Input<br>(P1A3 through P1A0)                                                                          | Input<br>(P1A3 through P1A0) | Retained                        | Retained                        |                   |

| 6<br>            | P3A3<br> <br>P3A0                           | 4-bit I/O port.<br>Can be set in input or output mode in 4-bit units.                                 |                              |                                 |                                 |                   |

| 9                |                                             |                                                                                                       | At reset                     | With clock stopped              |                                 |                   |

|                  |                                             | Power-ON reset                                                                                        | WDT&SP reset                 | CE reset                        |                                 |                   |

|                  |                                             | Input                                                                                                 | Input                        | Retained                        | Retained                        |                   |

| 10<br>           | P3B3<br>                                    | 4-bit I/O port.<br>Can be set in input or output mode in 4-bit units.                                 |                              |                                 |                                 |                   |

| 13               | P3B0                                        |                                                                                                       | At reset                     |                                 |                                 |                   |

|                  |                                             | Power-ON reset                                                                                        | WDT&SP reset                 | CE reset                        |                                 |                   |

|                  |                                             | Input                                                                                                 | Input                        | Retained                        | Retained                        |                   |

| 14<br>15<br>16   | P2A2<br>P2A1/FCG1<br>P2A0/FCG0              | <ul> <li>P2A2 through P</li> <li>3-bit I/O port</li> <li>Can be set in</li> <li>FCG1, FCG0</li> </ul> | input or output mod          |                                 |                                 | CMOS<br>push-pull |

|                  |                                             | Input for external gate counter      At reset     With clock stopped                                  |                              |                                 |                                 |                   |

|                  |                                             | Power-ON reset                                                                                        | WDT&SP reset                 | CE reset                        |                                 |                   |

|                  |                                             | Input<br>(P2A2 through P2A0)                                                                          | Input<br>(P2A2 through P2A0) | Retained<br>(P2A2 through P2A0) | Retained<br>(P2A2 through P2A0) |                   |

# NEC

| Pin No.              | Symbol                                           |                                                                                                                                                                                                                                                                                                            | Functio                                                 | n                                                                                                                      |                                                                                                                        | Output Form |

|----------------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-------------|

| 17<br>18<br> <br>20  | P1B3<br>P1B2/PWM2<br> <br>P1B0/PWM0              | Port 1B multiplexed<br>P1B3 through P <sup>2</sup><br>4-bit output po<br>PWM2 through F<br>8- or 9-bit D/A                                                                                                                                                                                                 | N-ch<br>open-drain<br>(12 V)                            |                                                                                                                        |                                                                                                                        |             |

|                      |                                                  |                                                                                                                                                                                                                                                                                                            | At reset                                                |                                                                                                                        | With clock stopped                                                                                                     |             |

|                      |                                                  | Power-ON reset                                                                                                                                                                                                                                                                                             | WDT&SP reset                                            | CE reset                                                                                                               | -                                                                                                                      |             |

|                      |                                                  | Outputs low level<br>(P1B3 through P1B0)                                                                                                                                                                                                                                                                   | Outputs low level<br>(P1B3 through P1B0)                | Retained                                                                                                               | Retained<br>(P1B3 through P1B0)                                                                                        |             |

| 21<br>33<br>75       | GND2<br>GND1<br>GND0                             | Ground                                                                                                                                                                                                                                                                                                     |                                                         |                                                                                                                        |                                                                                                                        | -           |

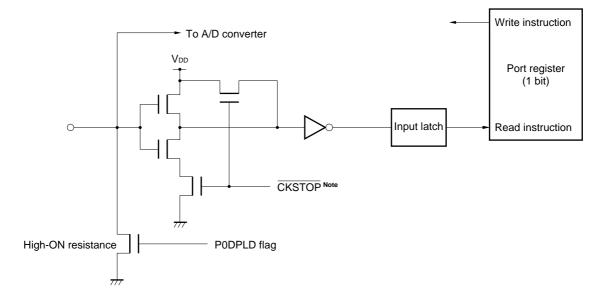

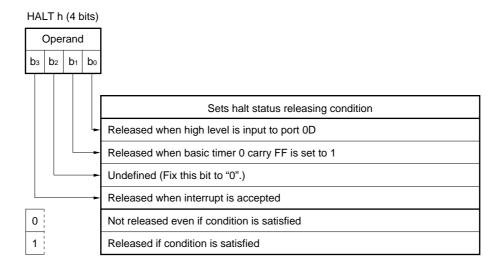

| 22<br> <br>25        | P0D3/AD3<br> <br>P0D0/AD0                        | <ul> <li>Port 0D multiplexed with A/D converter input pins</li> <li>P0D3 through P0D0 <ul> <li>4-bit input port</li> <li>Can be connected with pull-down resistor in 1-bit units.</li> </ul> </li> <li>AD3 through AD0 <ul> <li>Analog input of A/D converter with 8-bit resolution</li> </ul> </li> </ul> |                                                         |                                                                                                                        |                                                                                                                        | _           |

|                      |                                                  |                                                                                                                                                                                                                                                                                                            | At reset                                                |                                                                                                                        | With clock stopped                                                                                                     |             |

|                      |                                                  | Power-ON reset                                                                                                                                                                                                                                                                                             | WDT&SP reset                                            | CE reset                                                                                                               | -                                                                                                                      |             |

|                      |                                                  | Input with pull-down<br>resistor<br>(P0D3 through P0D0)                                                                                                                                                                                                                                                    | Input with pull-down<br>resistor<br>(P0D3 through P0D0) | Retained                                                                                                               | Retained                                                                                                               |             |

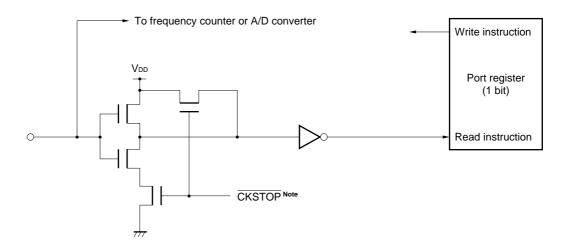

| 26<br>27<br>28<br>29 | P1C3/AD5<br>P1C2/AD4<br>P1C1/AMIFC<br>P1C0/FMIFC | <ul> <li>P1C3 through P</li> <li>4-bit input por</li> <li>AD5, AD4</li> </ul>                                                                                                                                                                                                                              | t<br>o A/D converter with                               |                                                                                                                        | er input pins.                                                                                                         | _           |

|                      |                                                  |                                                                                                                                                                                                                                                                                                            | At reset                                                |                                                                                                                        | With clock stopped                                                                                                     |             |

|                      |                                                  | Power-ON reset                                                                                                                                                                                                                                                                                             | WDT&SP reset                                            | CE reset                                                                                                               |                                                                                                                        |             |

|                      |                                                  | Input<br>(P1C3 through P1C0)                                                                                                                                                                                                                                                                               | Input<br>(P1C3 through P1C0)                            | <ul> <li>P1C3/AD5,<br/>P1C2/AD4<br/>retained</li> <li>P1C1/AMIFC,<br/>P1C0/FMIFC<br/>input<br/>(P1C1, P1C0)</li> </ul> | <ul> <li>P1C3/AD5,<br/>P1C2/AD4<br/>retained</li> <li>P1C1/AMIFC,<br/>P1C0/FMIFC<br/>input<br/>(P1C1, P1C0)</li> </ul> |             |

| Pin No.              | Symbol                                   |                                                                                                                                                                                                                                | Functio                                                                                                                                                   | n                                                                    |                                 | Output Form       |  |  |

|----------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|---------------------------------|-------------------|--|--|

| 30<br>79             | Vdd1<br>Vdd0                             |                                                                                                                                                                                                                                | erating                                                                                                                                                   | ye to these pins.<br>operating: 4.5 to 5<br>: 3.5 to 5<br>: 2.2 to 5 | .5 V                            | _                 |  |  |

| 31<br>32             | VCOH<br>VCOL                             | <ul> <li>VCOH</li> <li>Active with VH</li> <li>VCOL</li> <li>Active with HF</li> <li>Because the input</li> </ul>                                                                                                              | <ul> <li>PLL local oscillation (VCO) frequency input.</li> <li>VCOH</li> <li>Active with VHF mode selected by program; otherwise, pulled down.</li> </ul> |                                                                      |                                 |                   |  |  |

| 34<br>35             | EO0<br>EO1                               |                                                                                                                                                                                                                                | oscillation and the r                                                                                                                                     | ency synthesizer. C<br>esult of comparison                           | •                               | CMOS<br>3-state   |  |  |

|                      |                                          | Power-ON reset                                                                                                                                                                                                                 | At reset<br>WDT&SP reset                                                                                                                                  | CE reset                                                             | With clock stopped              |                   |  |  |

|                      |                                          | High-impedance<br>output                                                                                                                                                                                                       | High-impedance<br>output                                                                                                                                  | High-impendance<br>output                                            | High-impedance<br>output        |                   |  |  |

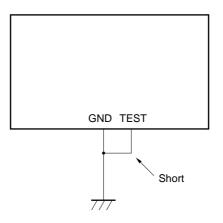

| 36                   | TEST                                     | Test input pin.<br>Be sure to connect                                                                                                                                                                                          | Test input pin.<br>Be sure to connect this pin to GND.                                                                                                    |                                                                      |                                 |                   |  |  |

| 37<br>38<br>39<br>40 | P1D3<br>P1D2<br>P1D1/BEEP1<br>P1D0/BEEP0 | <ul> <li>Port 1D and BEEP output.</li> <li>P1D3 through P1D0 <ul> <li>4-bit I/O port</li> <li>Can be set in input or output mode in 1-bit units.</li> </ul> </li> <li>BEEP1, BEEP0 <ul> <li>BEEP output</li> </ul> </li> </ul> |                                                                                                                                                           |                                                                      |                                 |                   |  |  |

|                      |                                          |                                                                                                                                                                                                                                | At reset                                                                                                                                                  |                                                                      | With clock stopped              |                   |  |  |

|                      |                                          | Power-ON reset                                                                                                                                                                                                                 | WDT&SP reset                                                                                                                                              | CE reset                                                             |                                 |                   |  |  |

|                      |                                          | Input<br>(P1D3 through P1D0)                                                                                                                                                                                                   | Input<br>(P1D3 through P1D0)                                                                                                                              | Retained<br>(P1D3 through P1D0)                                      | Retained<br>(P1D3 through P1D0) |                   |  |  |

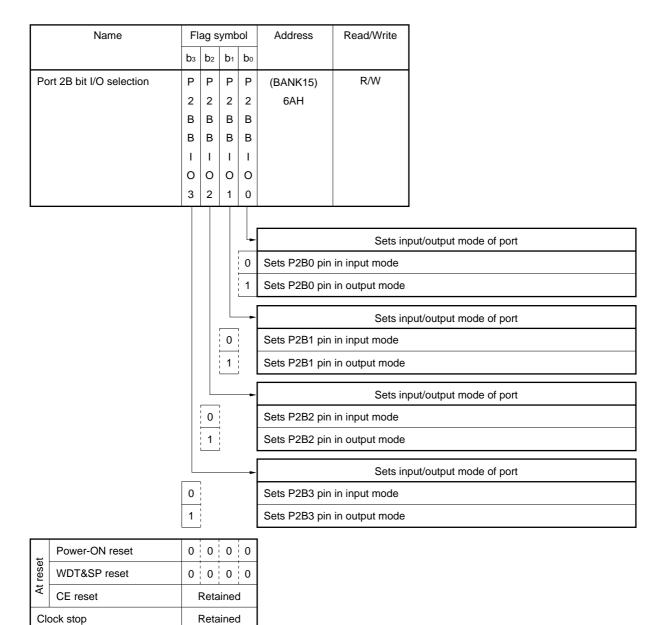

| 43<br>               | P2B3<br>                                 | 4-bit I/O Port.<br>Can be set in inpu                                                                                                                                                                                          | t or output mode in                                                                                                                                       | 1-bit units.                                                         |                                 | CMOS<br>push-pull |  |  |

| 46                   | P2B0                                     |                                                                                                                                                                                                                                | At reset                                                                                                                                                  | 1                                                                    | With clock stopped              |                   |  |  |

|                      |                                          | Power-ON reset                                                                                                                                                                                                                 | WDT&SP reset                                                                                                                                              | CE reset                                                             |                                 |                   |  |  |

|                      |                                          | Input                                                                                                                                                                                                                          | Input                                                                                                                                                     | Retained                                                             | Retained                        |                   |  |  |

| 47<br>               | P3C3<br>                                 | 4-bit I/O Port.<br>Can be set in input or output mode in 4-bit units.                                                                                                                                                          |                                                                                                                                                           |                                                                      |                                 |                   |  |  |

| 50                   | P3C0                                     |                                                                                                                                                                                                                                | At reset                                                                                                                                                  |                                                                      | With clock stopped              |                   |  |  |

|                      |                                          | Power-ON reset                                                                                                                                                                                                                 | WDT&SP reset                                                                                                                                              | CE reset                                                             |                                 |                   |  |  |

|                      |                                          | Input                                                                                                                                                                                                                          | Input                                                                                                                                                     | Retained                                                             | Retained                        |                   |  |  |

| Pin No.                                      | Symbol                                                                                         |                                                                                                                                                                                                                                                                                                                                 | Functio                                                                                                                                                      | n                                                                                         |                                                                        | Output Form                             |

|----------------------------------------------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------|-----------------------------------------|

| 51<br>                                       | P3D3<br>                                                                                       | 4-bit I/O Port.<br>Can be set in inpu                                                                                                                                                                                                                                                                                           | t or output mode in 4                                                                                                                                        | 1-bit units.                                                                              |                                                                        | CMOS<br>push-pull                       |

| 54                                           | P3D0                                                                                           |                                                                                                                                                                                                                                                                                                                                 | With clock stopped                                                                                                                                           |                                                                                           |                                                                        |                                         |

|                                              |                                                                                                | Power-ON reset                                                                                                                                                                                                                                                                                                                  | WDT&SP reset                                                                                                                                                 |                                                                                           |                                                                        |                                         |

|                                              |                                                                                                | Input                                                                                                                                                                                                                                                                                                                           | Input                                                                                                                                                        | Retained                                                                                  |                                                                        |                                         |

| 55<br>                                       | P2C3                                                                                           | 4-bit I/O Port.<br>Can be set in inpu                                                                                                                                                                                                                                                                                           | t or output mode in 4                                                                                                                                        | 1-bit units.                                                                              |                                                                        | CMOS<br>push-pull                       |

| 58                                           | P2C0                                                                                           |                                                                                                                                                                                                                                                                                                                                 | At reset                                                                                                                                                     |                                                                                           | With clock stopped                                                     |                                         |

|                                              |                                                                                                | Power-ON reset                                                                                                                                                                                                                                                                                                                  | WDT&SP reset                                                                                                                                                 | CE reset                                                                                  |                                                                        |                                         |

|                                              |                                                                                                | Input                                                                                                                                                                                                                                                                                                                           | Input                                                                                                                                                        | Retained                                                                                  | Retained                                                               |                                         |

| 59<br>                                       | P0C3                                                                                           | 4-bit I/O Port.<br>Can be set in inpu                                                                                                                                                                                                                                                                                           | t or output mode in 4                                                                                                                                        | 1-bit units.                                                                              |                                                                        | CMOS<br>push-pull                       |

| 62                                           | P0C0                                                                                           |                                                                                                                                                                                                                                                                                                                                 | At reset                                                                                                                                                     |                                                                                           | With clock stopped                                                     |                                         |

|                                              |                                                                                                | Power-ON reset                                                                                                                                                                                                                                                                                                                  | WDT&SP reset                                                                                                                                                 | CE reset                                                                                  |                                                                        |                                         |

|                                              |                                                                                                | Input                                                                                                                                                                                                                                                                                                                           | Input                                                                                                                                                        | Retained                                                                                  | Retained                                                               |                                         |

| 63<br>64<br>65<br>66<br>67<br>68<br>69<br>70 | P0A3/DSA<br>P0A2/SCL<br>P0A1/SCK0<br>P0A0/S00<br>P0B3/SI0<br>P0B2/SCK1<br>P0B1/S01<br>P0B0/SI1 | <ul> <li>P0A3 through P0</li> <li>4-bit I/O port</li> <li>Can be set in</li> <li>P0B3 through P0</li> <li>4-bit I/O port</li> <li>Can be set in</li> <li>SDA, SCL</li> <li>Serial data an I<sup>2</sup>C bus mode</li> <li>SCK0, SO0, SI0</li> <li>Serial clock I/0</li> <li>0 in 3-wire set</li> <li>SCK1, SO1, SI1</li> </ul> | input or output mod<br>0B0<br>input or output mod<br>d serial clock I/O of<br>O, serial data output<br>rial I/O mode<br>O, serial data output<br>al I/O mode | e in 1-bit units.<br>e in 1-bit units.<br>serial interface 0 in<br>, and serial data inpu | 2-wire serial I/O or<br>ut of serial interface<br>f serial interface 1 | N-ch<br>open-drain<br>CMOS<br>push-pull |

|                                              |                                                                                                |                                                                                                                                                                                                                                                                                                                                 | At reset                                                                                                                                                     |                                                                                           | With clock stopped                                                     |                                         |

|                                              |                                                                                                | Power-ON reset                                                                                                                                                                                                                                                                                                                  | WDT&SP reset                                                                                                                                                 | CE reset                                                                                  |                                                                        |                                         |

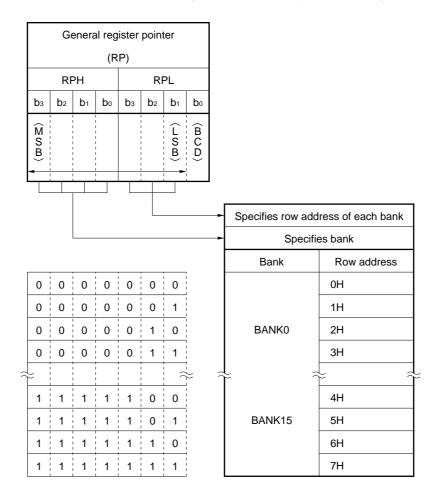

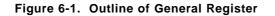

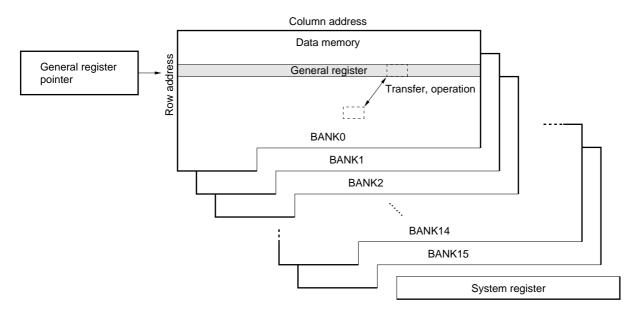

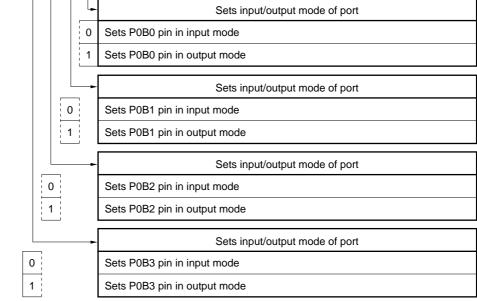

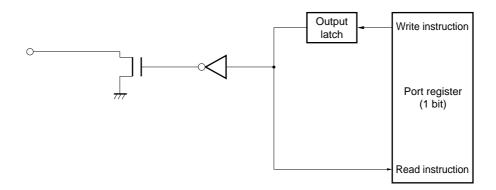

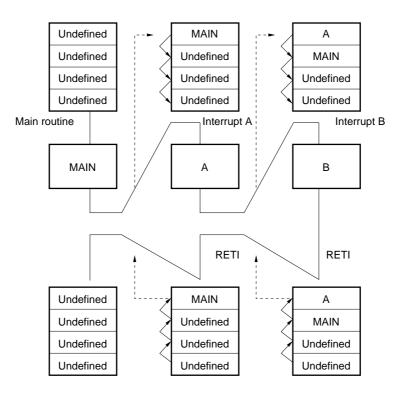

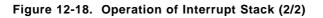

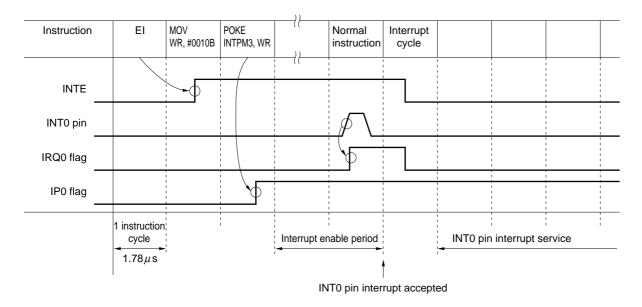

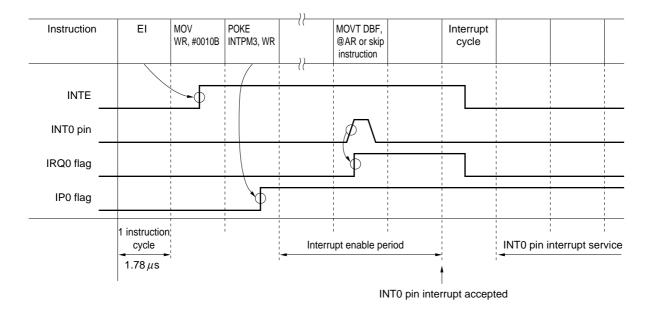

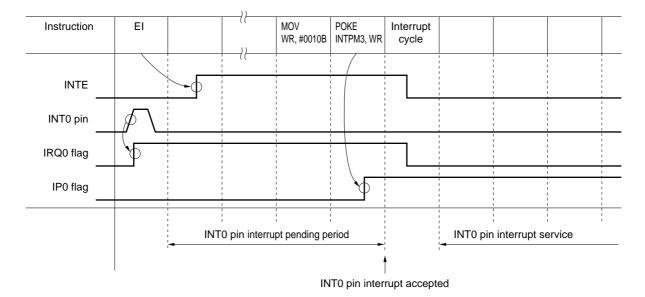

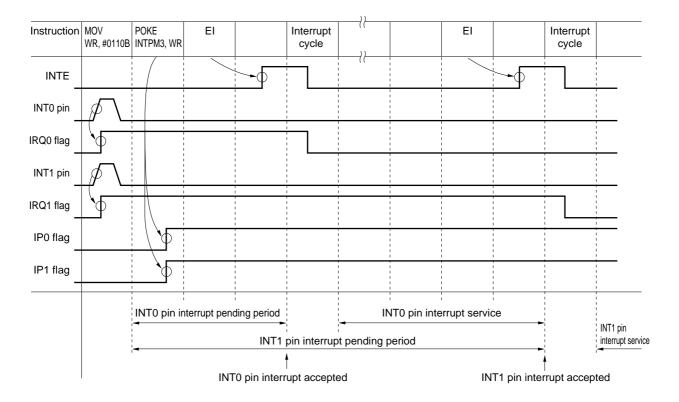

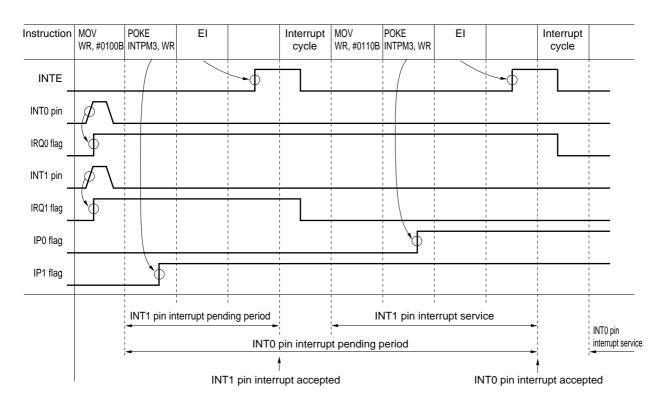

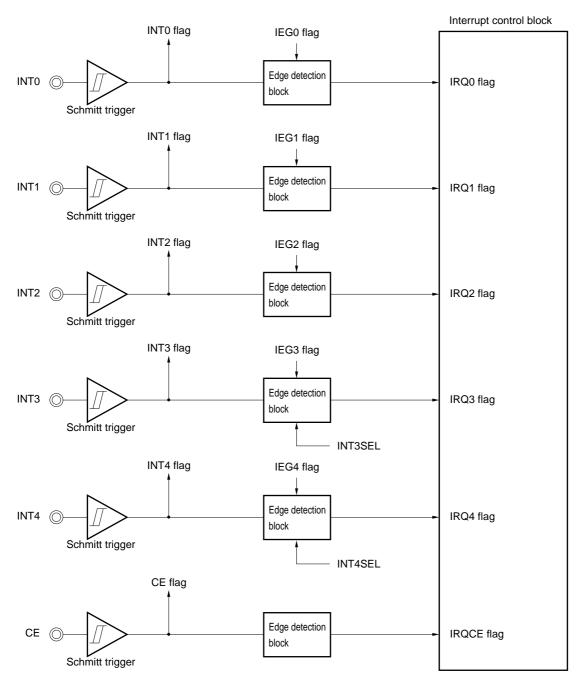

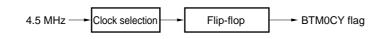

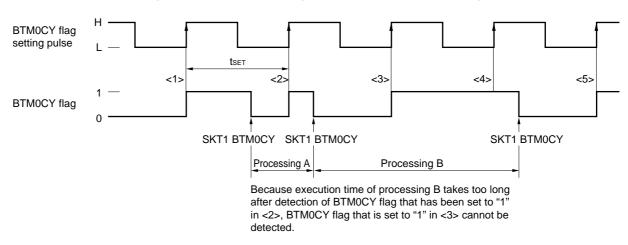

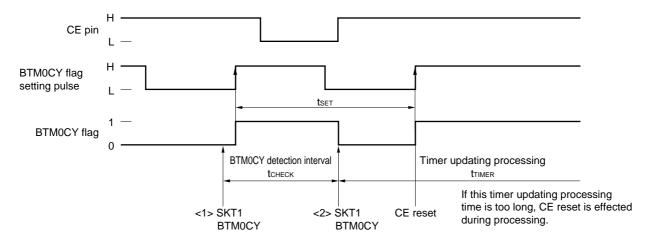

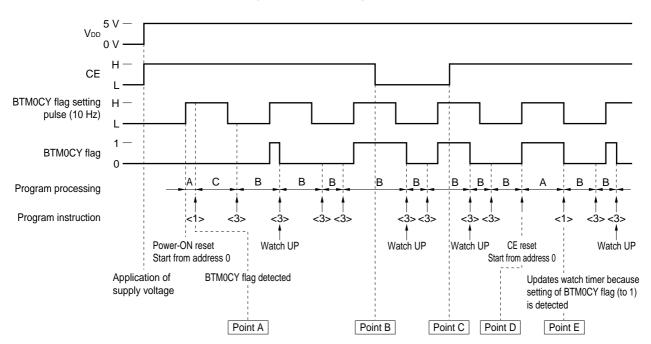

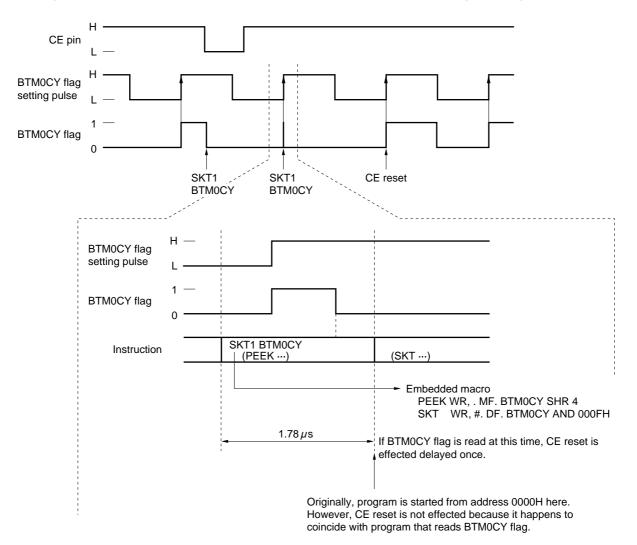

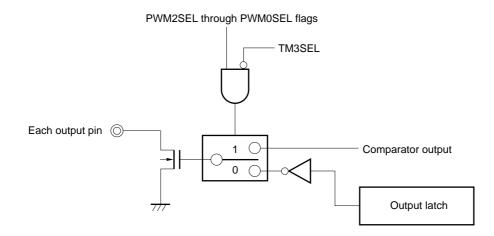

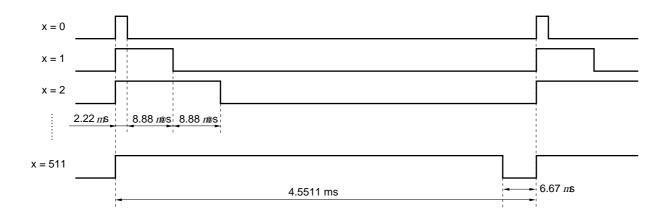

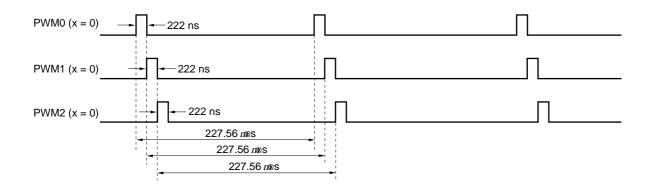

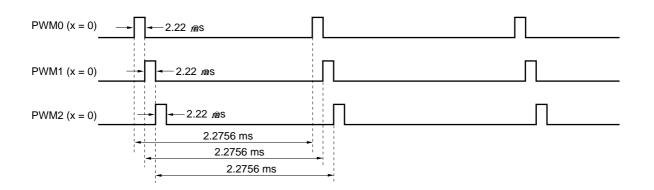

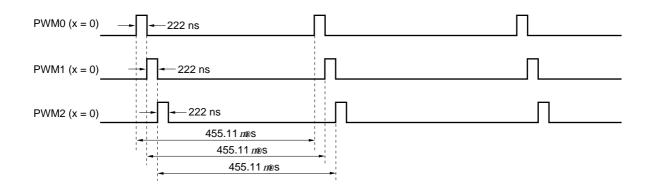

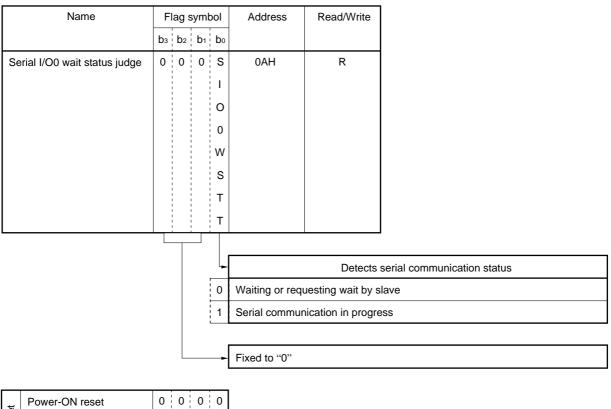

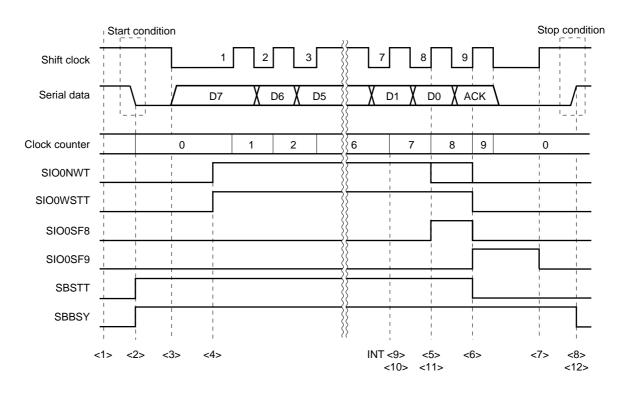

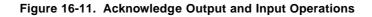

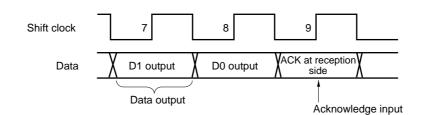

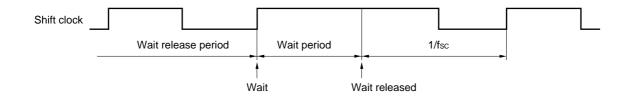

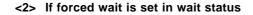

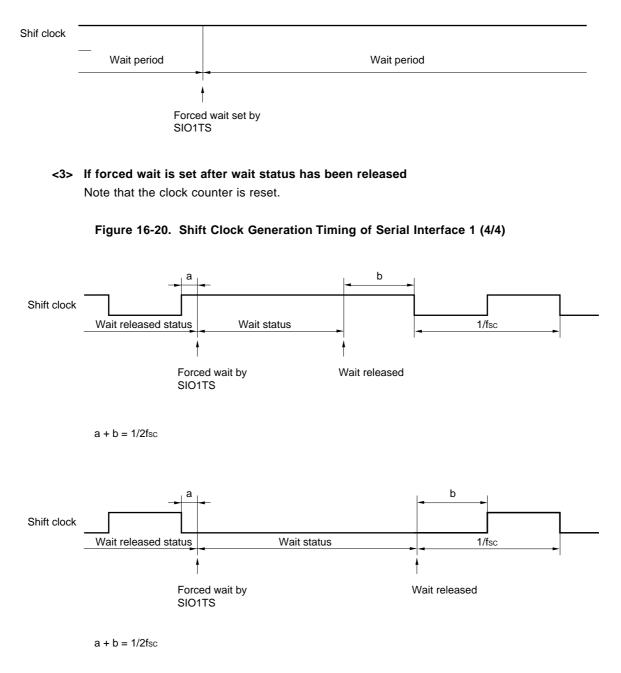

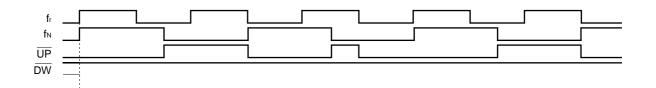

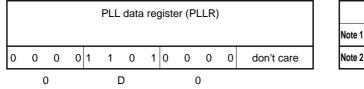

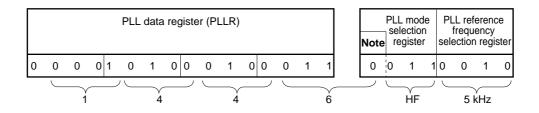

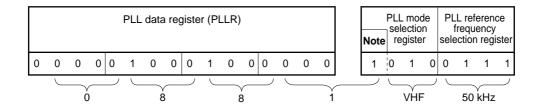

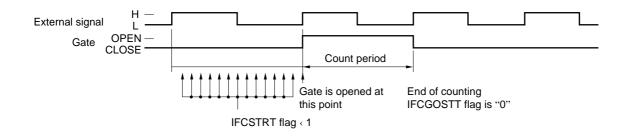

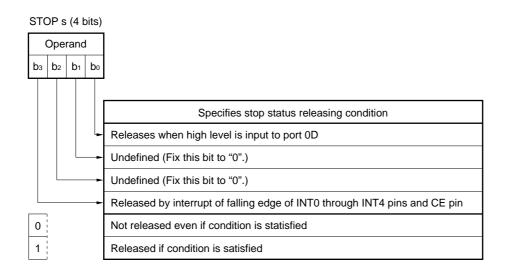

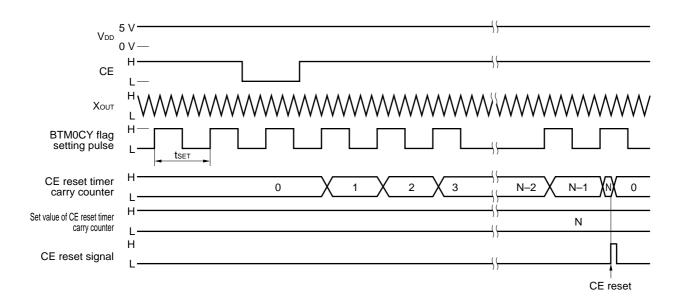

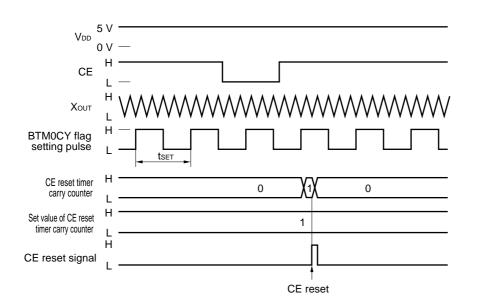

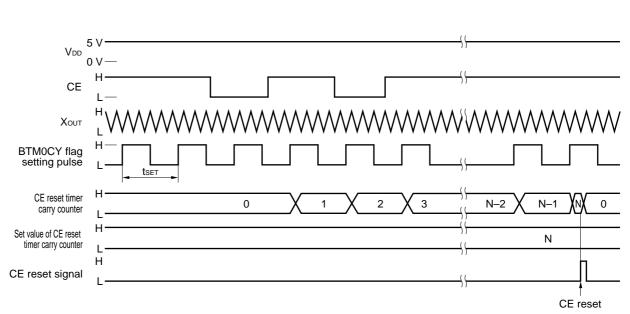

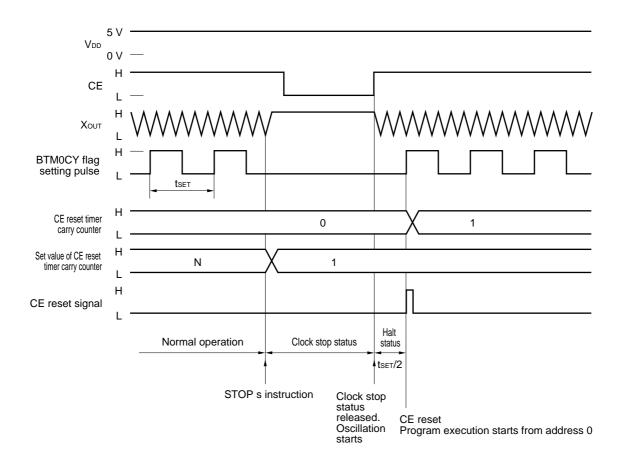

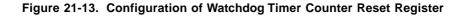

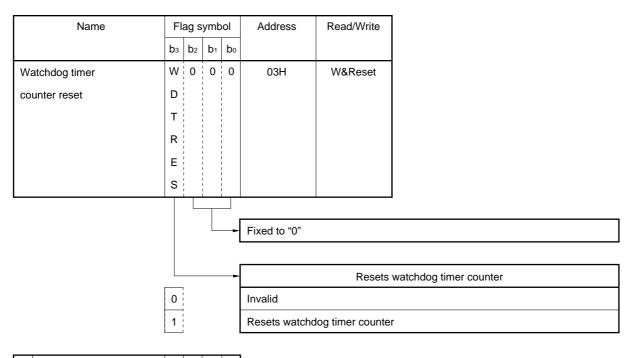

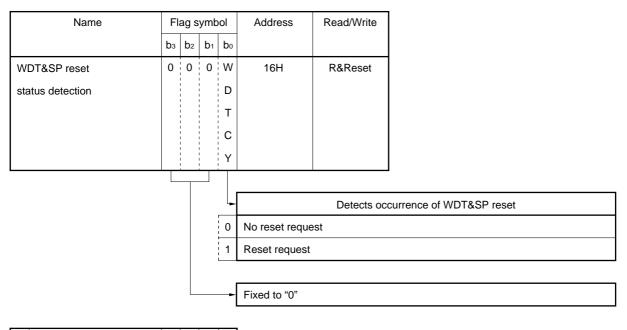

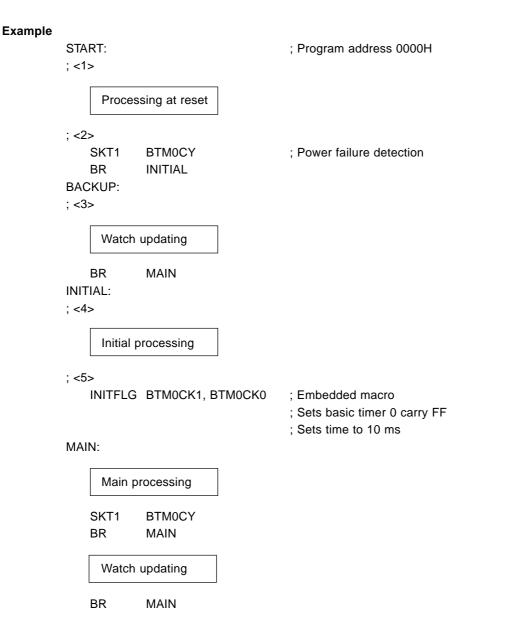

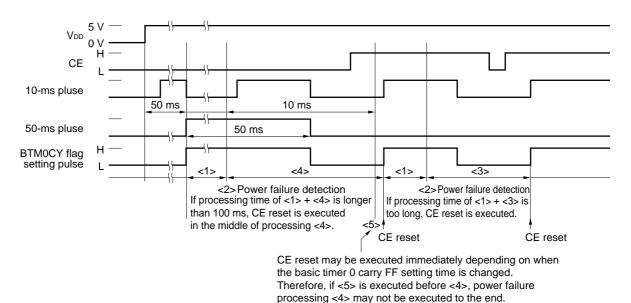

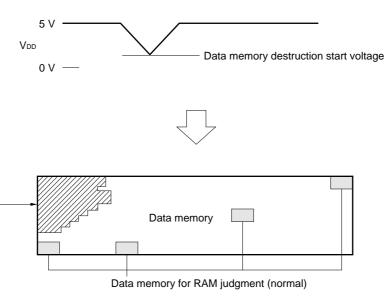

|                                              |                                                                                                | Retained<br>(P0A3 through P0A0,<br>P0B3 through P0B0)                                                                                                                                                                                                                                                                           |                                                                                                                                                              |                                                                                           |                                                                        |                                         |