# UAA4002

# CONTROL CIRCUIT FOR FAST SWITCHING TRANSISTORS

- DIRECT DRIVE OF THE SWITCHING TRANS-ISTOR

- SELF REGULATED POSITIVE BASE CUR-RENT (1 A max)

- NEGATIVE BASE CURRENT ENSURING FAST TURN-OFF (3 A max)

- THE OUTPÙT CURRENT CAN BE INCREA-SED BY MEANS OF ONE (or more) EXTERNAL TRANSISTOR(S)

- MINIMUM CONDUCTING TIME (or no conduction) TO ALLOW THE DISCHARGE OF A RDC NETWORK

- PROTECTION AGAINST SATURATION FAI-LURE OF THE POWER TRANSISTOR DURING CONDUCTING PERIOD, WITH ADJUSTABLE DETECTION THRESHOLD

- INSTANTANEOUS-COLLECTOR CURRENT LIMITATION

- POSITIVE SUPPLY (Vcc) MONITORING

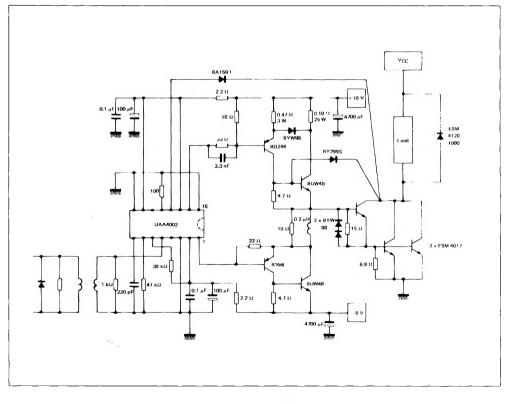

Figure 1: Block Diagram

NEGATIVE SUPPLY MONITORING WITH AD-JUSTABLE THRESHOLD

- ON-CHIP THERMAL PROTECTION

- PROGRAMMABLE MAXIMUM ON TIME

- TTL AND CMOS COMPATIBLE INPUT

- CAN BE DRIVEN WITH ALTERNATE PULSES

- ADJUSTABLE DELAY BETWEEN THE RISING EDGE OF THE INPUT SIGNAL AND THE BE-GINNING OF THE POSITIVE BASE DRIVE

## **ABSOLUTE MAXIMUM RATINGS**

| Symbol              | Parameter                                                      | Value         | Unit |

|---------------------|----------------------------------------------------------------|---------------|------|

| Vcc                 | Supply Voltage                                                 | + 15          | V    |

| V <sup>+</sup>      | Positive Supply Voltage (power stage)                          | + 15          | V    |

| V-                  | Negative Supply Voltage (power stage)                          | - 10          | V    |

| $V^{\star} - V^{-}$ | Voltage between Pins 15 and 2                                  | + 18          | V    |

| I <sub>B1</sub>     | Positive Output Current                                        | + 1.5         | A    |

| I <sub>B2</sub>     | Negative Output Current                                        | - 3.5         | A    |

| Ιc                  | Current into Input I <sub>C</sub> (internal protection diodes) | ± 5           | mA   |

| -                   | Minimum Value of Resistors Rt and RD                           | 5             | kΩ   |

| -                   | Voltage between Input and V <sup>-</sup>                       | + 18          | V    |

| Тj                  | Junction Temperature Range                                     | - 40 to + 150 | °C   |

| T <sub>stg</sub>    | Storage Temperature Range                                      | - 40 to + 150 | °C   |

Note: 1. Pin 2 (V-) should not be left open.

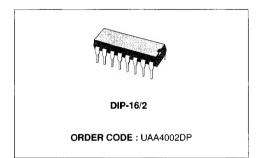

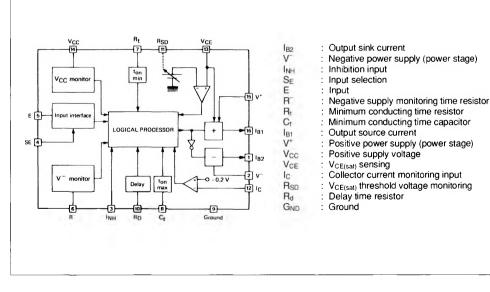

# **PIN CONNECTION** (top view)

#### THERMAL DATA

| R <sub>th(j-a)</sub> | Maximum Junction-ambient Thermal Resistance | 80 | °C/W | l |

|----------------------|---------------------------------------------|----|------|---|

|----------------------|---------------------------------------------|----|------|---|

# ELECTRICAL CHARACTERISTICS

$T_{amb}$  = + 25 °C,  $V_{CC}$  = + 10 V,  $V^-$  = - 5 V (unless otherwise specified)

| Symbol                | Parameter                                                                                        | Min.                                                | Тур.      | Max.            | Unit     |

|-----------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----------|-----------------|----------|

| Vcc                   | Supply Voltage                                                                                   | 7                                                   | _         | 14              | V        |

| -                     | Positive Supply Voltage Monitoring Threshold<br>Supply Current                                   |                                                     | 7         | -               | V        |

| Icc                   |                                                                                                  |                                                     | 12        | -               | mA       |

| V*                    | Positive Supply Voltage (power stage)                                                            | 4                                                   | _         | 14              | V        |

| <b>V</b> <sup>-</sup> | Negative Supply Voltage (power stage)                                                            | - 1                                                 | -         | - 9             | V        |

| V1                    | Threshold of Input I <sub>C</sub>                                                                | 0.160                                               | 0.2       | 0.240           | V        |

| I <sub>1</sub>        | Current into Input I <sub>C</sub>                                                                | -                                                   | 5         | 20              | μA       |

| Rt                    | Value of Resistor Rt (Rt between pin 7 and ground)                                               | 10                                                  | 47        | 200             | kΩ       |

| RD                    | Value of Resistor R <sub>D</sub> (R <sub>D</sub> between pin 10 and ground)                      | 20                                                  | -         | 200             | kΩ       |

| I <sub>B1</sub>       | Positive Output Current $(V_{(15)} - V_{(16)} = + 2 V)$                                          | 0.5                                                 | _         | -               | Α        |

| I <sub>B1(peak)</sub> | Positive Output Current (peak value)                                                             | 1                                                   | _         | -               | Α        |

| I <sub>B2</sub>       | Negative Output Current $(V_{(1)} - V_{(2)} = + 4 V)$                                            | 3                                                   | -         | -               | Α        |

| V <sub>SD</sub>       | Comparator V <sub>CE</sub> Threshold Voltage                                                     | 1                                                   | _         | 5.6             | V        |

| -                     | High Level on Input E ( $V_{(5)} - V^- < + 18 V$ )                                               | 2                                                   | -         | V <sub>cc</sub> | v        |

| -                     | Low Level on Input E (input SE not connected)                                                    | V <sup></sup>                                       | -         | 0.8             | V        |

| -                     | Low Level on Input E ( $ V^-  > 2.5 V$ , input SE tied to ground)                                | V-                                                  | _         | - 2             | V        |

| -                     | Current into Input E (V <sub>(5)</sub> = 0 V)<br>Input SE Left Open<br>Input SE Grounded         | - 0 -                                               | 10<br>0.2 | 50<br>0.3       | μA<br>mA |

| -                     | Low Level on Input I <sub>NH</sub>                                                               | 0                                                   | _         | 0.8             | v        |

| _                     | High Level on Input I <sub>NH</sub>                                                              | 2                                                   | _         | Vcc             | V        |

| t <sub>on(min)</sub>  | Time Constant ton min (Rt between pin 7 and ground)                                              | 0.06 R <sub>1</sub> (kΩ)                            |           | μs              |          |

| t <sub>d</sub>        | Delay between Input Pulse and Rise of Output Current ( $R_{\text{D}}$ between pin 10 and ground) | 0.05 R <sub>D</sub> (kΩ)                            |           | μs              |          |

| -                     | Propagation between Input Pulse and Rise of Output Current                                       |                                                     | 0.3       |                 | μs       |

| V <sub>SD</sub>       | Desaturation Threshold ( $R_{SD}$ between pin 11 and ground)                                     | $10 \times \frac{R_{SD}}{R_t}$                      |           | V               |          |

| R⁻                    | $V^-$ min Detection Resistor Value (R^ between pin 6 and $V^-)$                                  | $\frac{R_t}{2} \left(1 + \frac{V^- \min}{5}\right)$ |           | Ω               |          |

| t <sub>on(max)</sub>  | Time Constant ton max (Ct between pin 8 and ground)                                              | 2RtCt                                               |           | s               |          |

| _                     | Thermal Shut Down                                                                                |                                                     | 150       |                 | °C       |

#### **APPLICATION INFORMATION**

The coexistence of a power circuit handling high voltages and currents, and a control circuit carrying low amplitude signals, does not represent any special difficulty provided that a few simple rules are observed.

Positive and negative supply voltages of the integrated circuit must be carefully filtered by means of capacitors located very close to the device.

The device itself must by situated close to the power transistor, using short connections. The control circuit ground (pin 9) and the power circuit ground (emitter of the power transistor) must be linked by a single connection, as short as possible and of adequate cross-section.

A ground plane on the printed circuit board may be favourable in noisy environments. With regards to upper switches of a bridge configuration, the auxiliary supplies of the integrated circuit must have a low parasitic capacitor with respect to the ground potentiel. In the same way, the isolated components

driving the UAA4002 (optocoupler or pulse transformer) must have also a low parasitic capacitor in order to reduce dv/t phenomenons and to avoid risks of reswitching or conduction cut-off.

If a free-wheel diode is connected in parallel with the power transistor (witch is generally the case in

#### CIRCUIT DESCRIPTION (see block diagram figure 1)

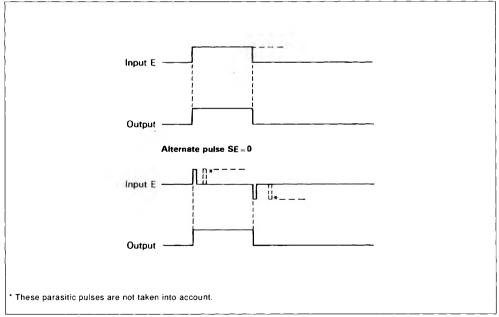

#### INPUT INTERFACE E AND SE INPUT

It translates the input signal into the logic levels required by the internal processor.

It also includes a RS flip-flop for the pulse mode operation.

#### FAULT DETECTORS

Power transistor collector current limiting (Ic input)

The collector current of the power transistor is measured by means of a shunt connected in the negative return of the power supply. As a result the current rather than the emitter current, since the base

Figure 2 : Level Mode SE = 1.

bridge systems), a diode (1N4148) must be connected between pin 13 and ground (cathode on pin 13 and anode on ground) in order to limit the negative voltage applied to this pin during the conduction of the free-wheel diode.

current of the switching does not flow through the shunt.

A voltage below - 0.2 V on input  $I_{\rm C}$  causes comparator to change state. This information is transmitted to the logic unit, which blocks the output pulses from the circuit until the next positive transition of the input signal.

If the voltage across the measuring shunt exceeds 0.2 V for the required limiting current value, a voltage divider bridge may be used (see application note NA031A).

If input Ic not used, it must be connected directly to ground.

Note : Pulse duration > 100ns.

Figure 3 : Switching Transistor Collector Current Measurement.

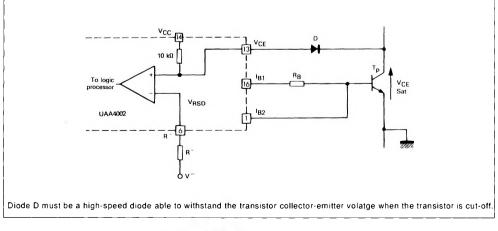

Protection against desaturation of the power transistor.

A comparator monitors continuously during the conduction that the collector voltage on the switching transistor remains lower than the preset value.

The preset value  $V_{RSD}$  (see figure 4) is given by :

$$R_{SD} = 5 V \times 2 \frac{H_{SD}}{Rt}$$

Current I set by external resistor Rt is :

$$I(mA) = \frac{5(V)}{B_t(k)}$$

Figure 4 : VCEsat Voltage Monitoring.

Without resistor  $R_{SD}$ , the threshold is set internally at + 5.6 V.

In case of overstep, the information is transmitted to the logic unit, which turns the output off until the next positive edge of the input signal.

To enable the switching transistor collector emitter voltage to fall when conduction begins, the protection function against desaturation is disabled during  $t_{on}$  min (see application note NA031A).

This protection is disabled by connecting pin  $R_{SD}\,directly$  to  $V_{\cdot}$

(FOR THRESHOLD EXCEEDING 5.5 V SEE NA031EA).

#### SUPPLY DEFECT

Negative supply (R input, see figure 4).

It is possible to disable the output pulses if the negative supply voltage V is insufficient to guarantee the switching of the power transistor (optional).

#### (FOR USING WITHOUT NEGATIVE POWER SUP-PLY SEE NA031A)

For this a resistor R is tied between pin 6 and the negative supply.

A current 2 I flows into it, and the threshold of the detector is + 5 V on pin 6.

Thus giving the relationship :

| 5 + V- min | 5   | Rt       | V– min |

|------------|-----|----------|--------|

| = 2        | 2 x | R-= (1 + | +)     |

| R-         | Rt  | 2        | 5      |

This function can be disabled ty tying pin 6 to ground.

Positive supply (V<sub>CC</sub> input)

An internal comparator ensures that there is no output voltage if positive supply  $V_{CC}$  is less than + 7 V. This threshold is not adjustable.

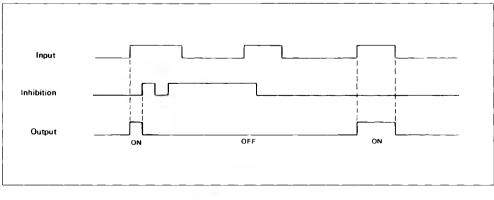

Inhibition (I<sub>NH</sub> input)

The action of the inhibition input is shown in the diagram below.

This input is CMOS and TTL compatible. If not used, it must be connected directly to ground.

Thermal protection

The UAA4002 is protected against excessive overheating by a thermal cut-out which automatically cuts off the output pulses if the chip temperature exceeds + 150 °C. The interruption is stored for a complete conduction period, but the output pulses reappear as soon as the chip temperature falls below the limiting temperature value.

#### TIME CONSTANTS

Minimum conducting time (Rt input)

To enable the capacitor of the switching aid network associated with power transistor to discharge completely, the logic processor ensures that the integrated circuit output pulse has a minimum duration ton min. To be effective, this must be at least four times the time constant of the RDC network.

The value of ton min is programmed by a resistor Rt

Typically  $t_{on} \min(s) = 0.06 \times R_t(k)$

The usable range of values for  $t_{on}$  min is between 1 and 12 s.

Resistor  $R_t$  has a key role in the operation of the UAA4002 integrated circuit. It sets the value of a bias current internal to the circuit :

$$f(\mathbf{mA}) = \frac{5}{\mathbf{R}_1(\mathbf{k})}$$

$t_{on}$  min embodies a priority function : no other security function can stop the conduction during  $t_{on}$  min.

The ton min function cannot be disabled.

Maximum conducting time (Rt and Ct inputs)

At the start of each conduction period the capacitor  $C_t$  is loaded by a constant current 1/2, where I is the current through resistor  $R_t$  (I = 5/ $R_t$ ). When the voltage across  $C_t$  reaches + 5 V the conduction is stopped. The value of  $t_{on}$  max is thus given by the equation :

$t_{on} max (s) = 2 \times R_t (k) \times C_t (nF)$

If the  $t_{on}$  max function is not to be used, it is only necessary to replace capacitor  $C_t$  with a short-circuit.

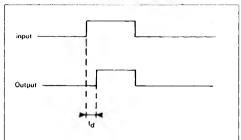

Time delay function

A constant time delay may be implemented between the rising edge of the control pulse and the begin-

Figure 5.

ning of the conduction pulse at the circuit output = (1 to 20  $\mu s$  by using resistor R<sub>D</sub>, t<sub>d</sub> ( $\mu s$ ) = 0.05 R<sub>D</sub> (kΩ).

#### LOGIC PROCESSOR

A logic unit processes the information coming from the fault detectors, and ensures that the output signal fulfils two conditions :

#### Figure 6.

- No double pulsing within a period : the occurence of a defect is memorized until the end of the period.

- To allow the discharge of a snubber network, the minimum output pulse width is set at a given value ton min.

#### OUTPUT STAGE : V<sup>+</sup>, V-, IB1, IB2, INPUTS

Introduction

The highly sophisticated output stage of the UAA4002 offers high performance is terms of switching transistor control.

Its principal features are as follows :

- the switching transistor is direct driven

- the transistor remains in a quasi-saturated state, whence reduced storage time

- control power is limited to the strict minimum

- it is easy to use

This stage is in fact in two parts, a positive driver stage which turns on the transistor and a negative driver stage which turns off the transistor.

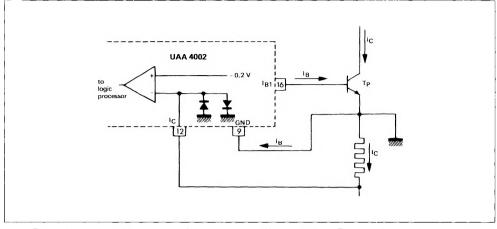

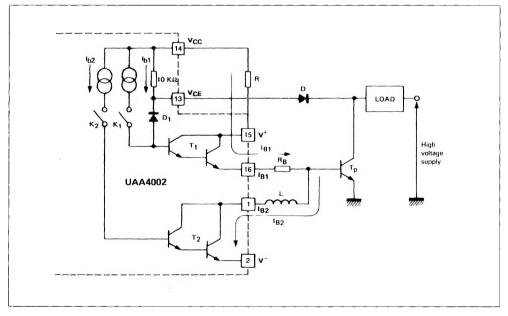

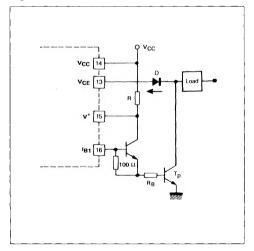

Power transistor conduction

The maximum value of the positive base current is determined by the limitation resistor R (I<sub>B1</sub> 1 A). A regulation loop is used to keep  $T_p$  in a quasi-saturation mode : the more  $T_p$  becomes saturated, the more diode D will shunt an important part of the drive current I<sub>B1</sub>, through diode D<sub>1</sub>. R<sub>B</sub> is a low value resistor (about 1) which helps to stabilize the regulation loop.

Voltage VCE across transistor Q is :

$V_{CE}(V) = V_{BE}(V) + R_B() I_{B1}(A)$

If the required drive current is greater than 0.5 A, one external NPN transistor may be added.

In this case :

$V_{CE}(V) = 2 V_{BE}(V) + R_B().I_B(A)$

Turn-off switching of power transistors

The closing of contact  $K_2$  (figure 10) causes Darlington  $T_2$  to conduct. The negative supply voltage is applied to the base of transistor  $T_P$  and a high negative base current  $I_{B2}$  flows, permitting the rapid evacuation of charges stored in the base-emitter junction of transistor  $T_P$ .

#### Figure 8.

A low-value inductor L may be required between the base of transistor  $T_P$  and the  $I_{B2}$  output of the UAA4002, so as to limit the gradient  $dI_{B2}/dt$  (see "The Power Transistor in its Environment" published by the Discrete Semiconductors Division of Thomson-CSF). In many cases, this inductor is not required.

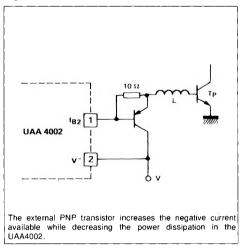

The Darlington  $T_2$  can carry a maximum current of 3 A. The corresponding saturation voltage is typically 3 V. Like the positive stage, this stage is designed for easy augmentation of the available output current by the addition of one or more external transistors.

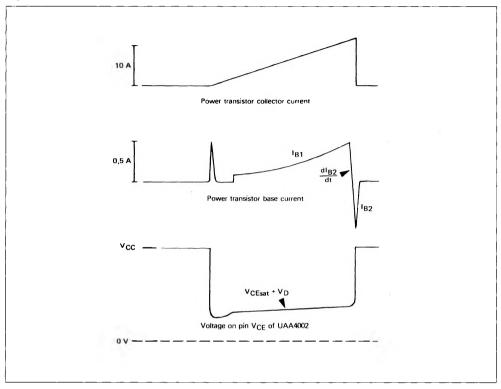

Typical inductive load waveforms

When conduction begins, the base current assumes a high value briefly and then reverts to zero. This base current spike permits rapid switching on of the power transistor. The base current value is then that required for quasi-saturation of the transistor. The base current curve is generally curved upwardy, due to the decreased gain of the power transistor with increased collector current.

#### Figure 10.

#### CONTROL OF MOS POWER TRANSISTORS

Ideally,MOS power transistors should be voltagecontrolled. In practice, in order to benefit from the high speed typical of this type of transistor it is necessary to charge and discharge the spurious input capacitance at high speed, so that high currents flow. By virtue of the high current capability of its output stages, the UAA4002 is particularly suitable for controlling MOS power transistors.

The output of the positive stage is connected directly to the gate of the MOS transistor, to switch it into conduction very fast. The negative stage controls the turning off of the MOS transistor, by discharging the gate capacitance of the transistor. There is no need for a high negative supply voltage, and the arrangement described in the previous section is therefore used.

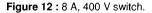

In this circuit the UAA4002 is used in a completely conventional manner, in "level" control mode.

The time constant t<sub>on</sub> min is set at 2.8 s, which is four times the time constant of the snubber network associated with the BUV37 transistor. The positive output stage of the UAA4002 is connected to the V<sub>CC</sub> rail through a 15 resistor. The maximum base current is approximately 0.45 A. The collector current is measured using a 0.10 shunt, and is limited to 10 A. The BUV37 Darlington for which the specified value of I<sub>Csat</sub> is 12 A, is thus operated with a considerable safety margin.

# **UAA4002**

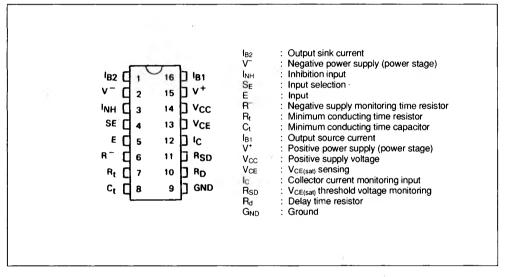

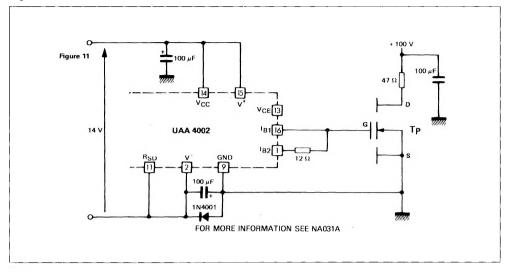

# Figure 11.

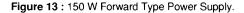

# TYPICAL APPLICATIONS

Switching aid network.

- 2. Polypropylene capacitor.

- 3. With heatsink,  $R_{HT} < 3.5$  °/W.

#### Performance

Output voltage stability :

For an input voltage varying from 190 to 245 V, the maximum relative variation in the output voltage is 0.7 % at nominal operating conditions.

$(V_{OUT} = 25 V, I_{OUT} = 6 A).$

For a variation in the load from 0 to 100 % the relative variation in the output voltage is 1.3 %.

For a variation in the load from 10 to 100 % ( $I_{OUT}$  = 0.6 to 6 A), the relative variation in the output voltage is 0.4 %.

Efficiency 80 % under nominal operating conditions.

Behaviour on overload :

The power supply is fully protected against overloads and short-circuits, the output current being limited to 7 A.

# **UAA4002**

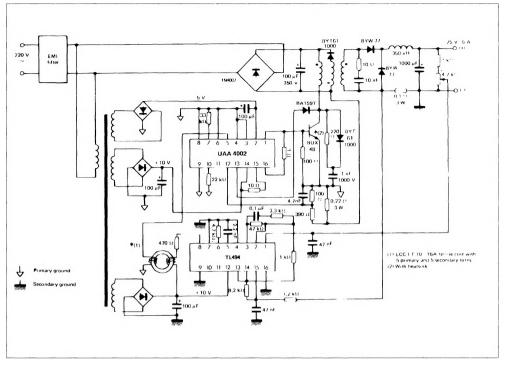

Figure 14 : Capacitor Type Half Bridge Symmetrical Converter.

Figure 15 : 200 A, 700 V Switch.