# TS75C25

# V.22 BIS, V.22, BELL 212, V.21 V.23, BELL 103 MODEM CHIP SET

#### **ADVANCE DATA**

- CCITT V.22 BIS COMPATIBLE MODEM CHIP SET

- CCITT V.21, V.22 AND V.23 COMPATIBLE MO-DEM CHIP SET

- BELL 103 AND 212 COMPATIBLE MODEM CHIP SET

- DIGITAL SIGNAL PROCESSING (TS75C250)

AND ANALOG FRONT-END (TS7542) IMPLE-MENTATION

- QAM, DPSK AND FSK MODULATION AND DE-MODULATION

- DATA TRANSMISSION SPEED:

- 2400BPS IN QAM

- 1200 OR 600BPS IN DPSK

- 1200 OR 300 OR 75BPS IN FSK

- ADAPTIVE EQUALIZATION

- TRANSMIT AND RECEIVE FILTERING

- SHARP ADJACENT CHANNEL REJECTION

- PROGRAMMABLE TRANSMIT OUTPUT LE-VELS

- ON-CHIP 4/2-WIRE HYBRID CAPABILITY

- ANSWER TONE DETECTION AND GENERA-TION FOR CCITT (2100Hz), BELL (2225Hz), AND TRANSPAC (1650Hz) RECOMMENDA-TIONS

- 550Hz AND 1800Hz GUARD TONE GENERA-TION

- DTMF TONE GENERATION

- CALL PROGRESS TONE DETECTION

- SELECTABLE SCRAMBLER AND DESCRAMBLER

- DYNAMIC RECEIVE RANGE 0 TO 48dBm

- TYPICAL 10<sup>-4</sup> B.E.R. ACHIEVED WITH A 13dB S/N RATIO (V.22 BIS)

- ± 10Hz FREQUENCY OFFSET CAPABILITY

- SUPPLY VOLTAGE: ± 5V

- POWER CONSUMPTION 0.7W

- CMOS TECHNOLOGY

- SOFTWARE LICENSE AND DEVELOPMENT TOOLS AVAILABLE FOR EASY CUSTOMIZA-TION

#### DESCRIPTION

The SGS THOMSON Microelectronics multi-standard V.22 bis chip set is a high performance modem engine, which can operate up to 2400bps in full duplex over public switched telephone network or leased lines. The TS75C25 also allows implementation

of modems complying with CCITT V.21, V.22, V.23, and BELL 103, 212 recommendations. The modem hardware consists of a DSP chip and an analog front end (TS7542). The modem signal processing functions are implemented on a ST18930 CMOS programmable digital signal processor, namely TS75C250. In the DSP, internal program memory is available allowing easy customization.

# TABLE OF CONTENTS

|    |                                                 | Page |

|----|-------------------------------------------------|------|

| 1. | PIN DESCRIPTION                                 |      |

|    | 1.1. SYSTEM INTERFACE                           | 5    |

|    | 1.2. ANALOG INTERFACE                           | 5    |

|    | 1.3. CLOCK INTERFACE                            | 5    |

| 2. | FUNCTIONAL DESCRIPTION                          |      |

|    | 2.1. SYSTEM ARCHITECTURE                        | 6    |

|    | 2.2. PROCESSOR AND ANALOG FRONT END ARRANGEMENT | 7    |

|    | 2.3. OPERATION                                  | 8    |

|    | 2.3.1. ANALOG FRONT END DESCRIPTION             | 8    |

|    | 2.3.2. OPERATING MODES                          | 9    |

|    | 2.3.3. TRANSMIT                                 | 9    |

|    | 2.3.4. RECEIVE                                  | 10   |

|    | 2.4. TS75C25 ANALOG INTERFACE                   | 10   |

|    | 2.4.1. TS75C25 ANALOG INTERFACE                 | 10   |

|    | 2.4.2. TS75C25 DIGITAL INTERFACE                | 10   |

|    | 2.4.3. MAILBOX DESCRIPTION                      | 12   |

| 3. | USER INTERFACE                                  |      |

|    | 3.1. COMMAND AND STATUS WORDS                   | 13   |

|    | 3.2. TRANSMIT AND RECEIVE COMMAND WORDS         | 13   |

|    | 3.2.1. TRANSMIT COMMAND WORD                    |      |

|    | DTMF MODE                                       |      |

|    | ANSWER TONE GENERATION                          |      |

|    | 3.2.2. RECEIVE COMMAND WORD                     |      |

|    | 3.3. TRANSMIT AND RECEIVE STATUS WORDS          |      |

|    | 3.3.1. TRANSMIT STATUS WORD                     |      |

|    | 3.3.2. RECEIVE STATUS WORD                      |      |

# TABLE OF CONTENTS

| 4. ELECTRICAL SPECIFICATION                               |    |

|-----------------------------------------------------------|----|

| 4.1. MAXIMUM RATINGS                                      | 21 |

| 4.2. DC ELECTRICAL CHARACTERISTICS                        | 22 |

| 4.3. AC ELECTRICAL SPECIFICATIONS                         |    |

| 4.3.1. CLOCK AND CONTROL PINS TIMING                      | 23 |

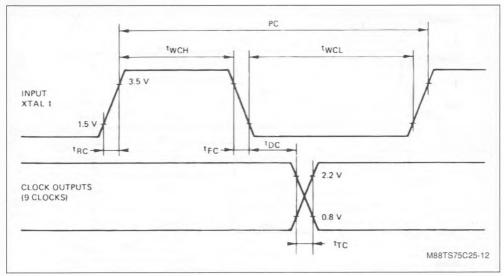

| 4.3.2. CLOCK GENERATOR                                    | 25 |

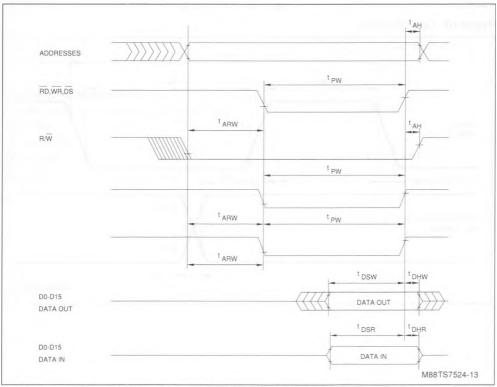

| 4.3.3. LOCAL BUS TIMING (TS75C250 and TS7542)             | 26 |

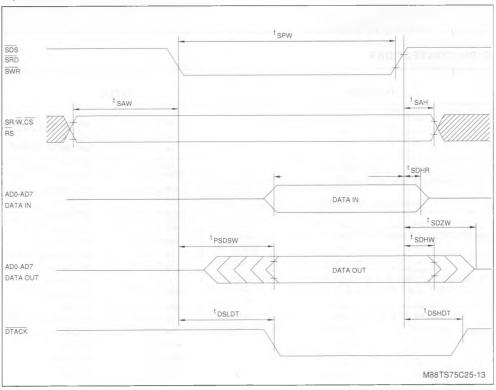

| 4.3.4. SYSTEM BUS TIMING (TS75C250 and control processor) | 27 |

| 4.3.5. DAA INTERFACE (DAA and TS7542)                     | 28 |

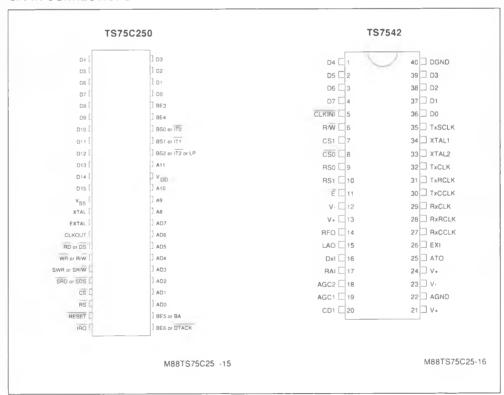

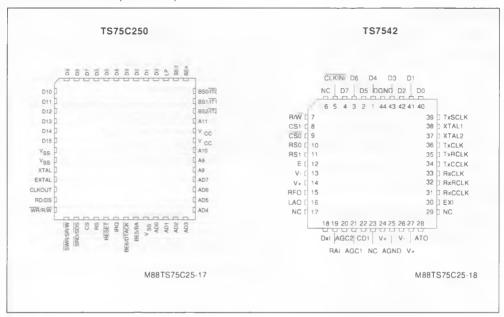

| 5. PIN CONNECTIONS                                        | 28 |

| 6. ORDERING INFORMATION                                   | 33 |

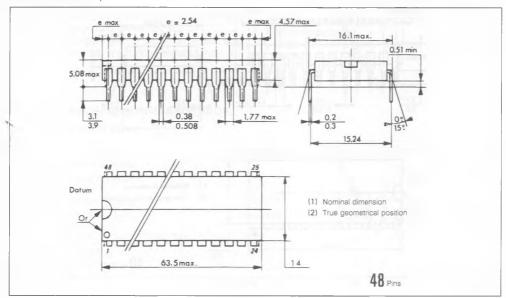

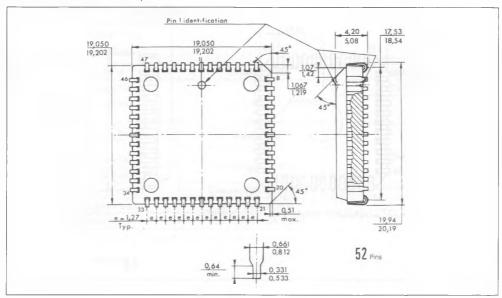

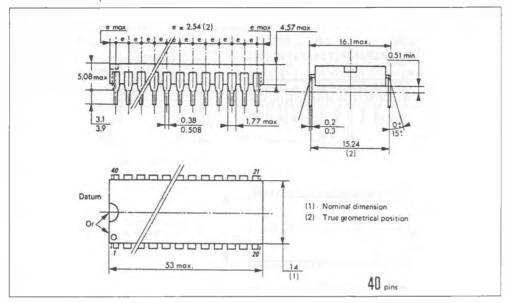

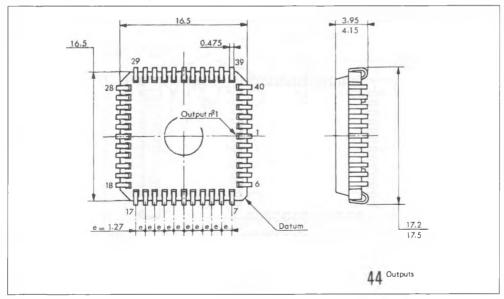

| 7. PACKAGE MECHANICAL DATA                                | 34 |

|                                                           |    |

| TABLE OF APPENDICES                                       |    |

| A. TRANSMIT/RECEIVE COMMAND WORDS PROGRAMMING MODEL       | 36 |

| B. TRANSMIT/RECEIVE STATUS WORDS PROGRAMMING MODEL        | 36 |

| C. TS75C25 CHIP SET                                       | 37 |

# LIST OF ILLUSTRATIONS

| Figure | Title                                           | Page |

|--------|-------------------------------------------------|------|

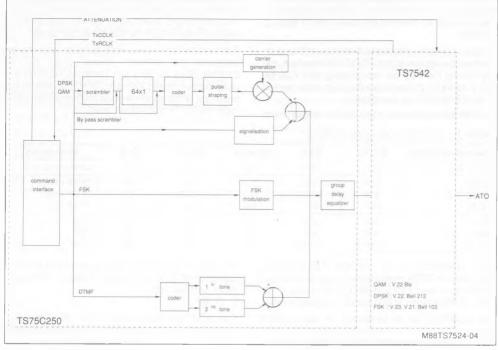

| 1      | TS75C25 BLOCK DIAGRAM                           | 6    |

| 2      | INTERCONNECTION BETWEEN ANALOG FRONT END AND DI |      |

| 3      | 7542 BLOCK DIAGRAM                              | 8    |

| 4      | TRANSMIT BLOCK DIAGRAM                          | 10   |

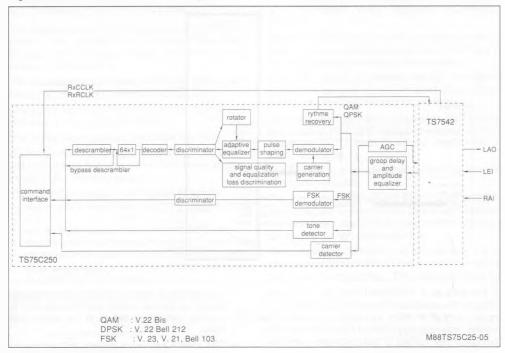

| 5      | RECEIVE BLOCK DIAGRAM                           | 11   |

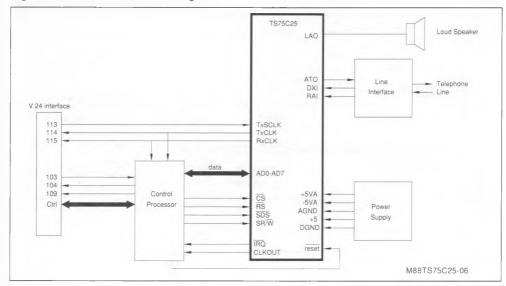

| 6      | FUNCTIONAL INTERCONNECT DIAGRAM                 | 12   |

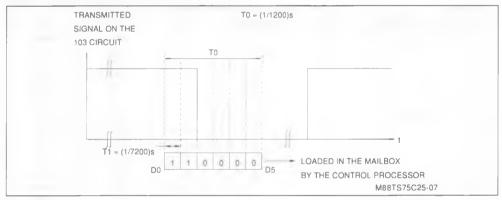

| 7      | FSK TRANSMIT MODE                               | 15   |

| 8      | FSK RECEIVE MODE                                | 20   |

| 9      | CLOCK AND CONTROL PINS TIMING                   | 23   |

| 10     | CLOCK GENERATOR                                 | 25   |

| 11     | LOCAL BUS TIMING DIAGRAM                        | 26   |

| 12     | SYSTEM BUS TIMING DIAGRAM                       | 27   |

| 13     | TYPICAL STAND-ALONE APPLICATION                 | 35   |

|        |                                                 |      |

# LIST OF TABLES

| Table | Title                                              | Page |

|-------|----------------------------------------------------|------|

| 1     | TS75C25 OPERATING MODES                            | 9    |

| 2     | DIGITAL INTERFACE SIGNALS                          | 11   |

| 3     | TRANSMIT COMMAND WORD FORMAT                       | 13   |

| 4     | DTMF (dual or single tone programmation)           | 16   |

| 5     | TONE ENCODING                                      | 16   |

| 6     | ANSWER TONE GENERATION                             | 17   |

| 7     | RECEIVE COMMAND WORD FORMAT                        | 17   |

| 8     | TRANSMIT STATUS WORD FORMAT                        | 18   |

| 9     | RECEIVE STATUS WORD FORMAT                         | 19   |

| 10    | CALL PROCESS AND ANSWER TONE DETECTION PROGRAMMING |      |

# 1. PIN DESCRIPTION

# 1.1. SYSTEM INTERFACE

# TS75C250 (DSP)

| Name    | Type | Description                                                                                                               |

|---------|------|---------------------------------------------------------------------------------------------------------------------------|

| AD0.AD7 | 1/0  | System Data Bus: these lines are used for transfer between the TS75C25 mailbox and the control processor.                 |

| CS      | l    | Chip Select: this input is asserted when the TS75C25 is to be accessed by the control processor.                          |

| RS      | 1    | Register Select: this signal is used to control the data transfers between the control processor and the TS75C25 mailbox. |

| SDS     | 1    | System Data Strobe : synchronizes the transfer between the TS75C25 mailbox and the control processor.                     |

| SR/W    | 1    | System Read/Write: Control Signal for the TS75C25 Mailbox Operation                                                       |

| IRQ     | 0    | Interrupt Request : signal sent to the control processsor to access the TS75C25 mailbox.                                  |

| RESET   | 1    | Reset of the TS75C25. Must be maintened for a minimum of five clocks cycles.                                              |

## 1.2. ANALOG INTERFACE

# TS7542 (analog transmit and Receive parts)

| Name | Type | Description                                                |

|------|------|------------------------------------------------------------|

| ATO  | 0    | Analog Transmit Output                                     |

| LAO  | 0    | Line Monitoring Output for Loud Speaker                    |

| RAI  | 1    | Receive Analog Input                                       |

| DXI  | 1    | Duplexer Input. This signal is subtracted from signal RAI. |

# 1.3. CLOCK INTERFACE

# TS7542 (clock part)

| Name    | Type | Description                                                                                                                            |

|---------|------|----------------------------------------------------------------------------------------------------------------------------------------|

| TxCLK   | 0    | Transmit Bit Clock                                                                                                                     |

| TxRCLK  | 0    | Additional Transmit Clock                                                                                                              |

| TxCCLK  | 0    | Transmit Conversion Clock                                                                                                              |

| RxCLK   | 0    | Receive Bit Clock                                                                                                                      |

| RxRCLK  | 0    | Additional Receive Clock                                                                                                               |

| RxRCCLK | 0    | Receive Conversion Clock                                                                                                               |

| TxSCLK  | ı    | Transmit Synchro Clock: can be used to synchronize the transmitter on an external bit clock provided by the RS232C (or V 24) junction. |

#### 2. FUNCTIONAL DESCRIPTION

## 2.1. SYSTEM ARCHITECTURE

The SGS-THOMSON V.22 bis chip set is a highly integrated modem engine which provides the functionality and performance requirements for full-duplex 2400bps modem solutions at a low cost with excellent performance due to digital signal processing technology. On top of the V.22 bis, the TS75C25 chip set also implements the CCITT V.21, V.22, V.23 and BELL 103, 212 requirements.

The TS75C250 is a programmable digital signal processor which implements the complete signal processing functions required to send and receive data according to the standard requirement and utilities such as call progress tone detection, auto-answer tone detection and tone generation.

The TS7542 (modem analog front end) is designed to meet the requirements of the whole range of voiceband modems.

The TS7542 incorporates all the required programmable gain control and clock circuitry, and signal filtering (band-limiting, anti-aliasing and smoothing filters).

Interfacing the TS75C25 chip set to a control processor is very straightforward and requires no external interface circuitry.

The TS75C25 chip set along with a data access arrangement (DAA), a control processor and a V.24/RS232 interface and/or an UART, is particularly well-suited for high-performance modem.

The modem supervision is insured by a control processor which implements the handshake monitoring, the auto/manual answer and dialing modes, the test modes and fall back capability and the async/sync and sync/async conversion.

Figure 1: TS75C25 Block Diagram.

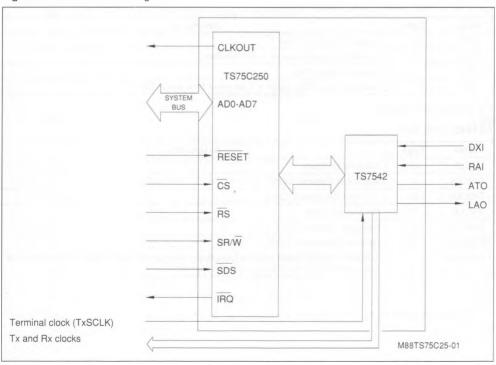

# 2.2. PROCESSOR AND MAFE CHIPS ARRANGEMENT

The TS75C25 is connected to the analog front end chip through its local bus where D8 through D15 are the 8-bit data bus and A8 through A11 are four address lines used to address directly the analog front end chip.

Data-Strobe (DS) is used to synchronize the transfer of data. Read/write (R/W) indicates the direction of data. Two Branch-on-External-Condition signals (BE5 to BE6) are connected to the different clock signals issued from the TS7542 clock generator part. They are used by the TS75C250 to perform its real-time task scheduling.

Figure 2: Interconnections between the Analog Front End Chip and the Digital Signal Processor TS75C250.

#### 2.3. OPERATION

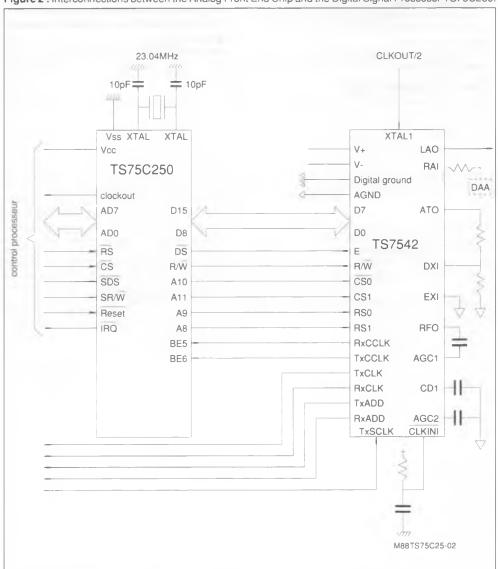

2.3.1. ANALOG FRONT END DESCRIPTION. The TS7542 is a modem analog front end which performs the following functions controlled by the TS75C250 digital signal processor according to the selected modem standard.

# Transmit Analog Part:

- 12-bit D/A converter synchronized with the sampling transmit clock

- Low-pass and smoothing continuous-time filters

- 0 to 22dB (or infinite) programmable attenuation

#### Receive analog Part:

- 12-bit A/D converter synchronized with the sampling receive clock.

- Figure 3: TS7542 Block Diagram.

- Band-pass programmable filter

- · Back channel rejection filter

- · Smoothing filter

- 0 to 46.5dB gain amplifier

#### Clock Generation Part:

- Transmit time base with programmable synchronization on data terminal equipment clock or extracted receive clock.

- Programmable receive time base DPLL

- Programmable plesiochronous transmit and receive clocks (sampling, bit and additional clocks).

## Loudspeaker Part:

Loudspeaker with programmable level line output

2.3.2. OPERATING MODES. The modem implementation is fully compatible with different CCITT and BELL recommendations as listed in table 1. It may operate at different bit rates, from 75bps to 2400bps.

In case of switching from any mode to another, a reset must be applied to the TS75C250 reset pin, except during the V.22 bis handshaking (the V.22 bis and V.22/BELL 212 software modules implemented in the TS75C250 are compatible).

A DTMF tone generator is provided to output one of

16 standard dual tones coded by a combination of two frequencies. For specific applications where single tone is required, the DTMF generator provides the possibility to select either the high frequency or the low frequency of the standard dual tones.

A tone detector and a carrier detector respectively recognize the different answer tones (CCITT 2100Hz, BELL 2225Hz and Transpac 1650Hz) and call progress tones (300Hz to 700Hz), as well as the presence or the absence of the on-line carrier signal (both for PSTN and leased lines).

Table 1: TS75C25 Operating Modes.

| Recommendation             | Bauds                 | BPS                   | Duplex               | Answer            | Orig              | Modulation                           |

|----------------------------|-----------------------|-----------------------|----------------------|-------------------|-------------------|--------------------------------------|

| V. 22 BIS                  | 600                   | 2400                  | Full                 | Yes               | Yes               | QAM (quadribit)                      |

| V. 22<br>BELL 212<br>V. 22 | 600<br>600            | 1200<br>1200<br>600   | Full<br>Full<br>Full | Yes<br>Yes<br>Yes | Yes<br>Yes<br>Yes | DPSK (dibit) DPSK (dibit) DPSK (bit) |

| V. 21<br>BELL 103<br>V. 23 | 300<br>300<br>1200/75 | 300<br>300<br>75/1200 | Full<br>Full<br>Full | Yes<br>Yes<br>Yes | Yes<br>Yes<br>Yes | FSK<br>FSK<br>FSK                    |

2.3.3. TRANSMIT (fig. 4): *V.22 bis, V.22 and BELL 212.* QAM or DPSK modulation is used to send four (V.22 bis) or two (V.22 and BELL 212) or one (V.22) bit(s) of information at 600 bauds modulation rate.

The scrambler can be bypassed, as user's option usually during the handshake procedure. After coding. a raised cosine filter (roll-off factor 0.75) performs pulse shaping and provides a 45dB rejection between the channels so as to comply with V.22 bis, V.22 and BELL 212 standard requirements. When required, a 1800Hz or 550Hz guard tone can be added to the transmitted signal.

- V.23. V.21 and BELL 103

The FSK modulation is used to send one bit of information at 1200 or 75 baud (V.23) or 300 bauds (V.21 and Bell 103).

\_ DTMF

The DTMF generator outputs one of 16 standard dual tones synthetized by the TS75C250 and selected by a 4-bit binary value as described later. Each tone is coded by a combination of two frequencies. The DTMF generator may be programmed to generate one tone at a time.

The transmit attenuation level is programmable over a 23dB dynamic range by 1dB steps.

Figure 4: TS75C25 Transmit Block Diagram.

## 2.3.4. RECEIVE (fig. 5):

V.22 bis. V.22 and BELL 212.

QAM or DPSK demodulation is used to receive four (V.22 bis) or two (V.22 and BELL 212) or one (V.22) bit(s) of information at 600 bauds.

- V.23, V.21 and BELL 103

The FSK demodulation is used to receive one bit of information at 1200 or 75 bauds (V.23) or 300 bauds (V.21 and BELL 103).

Tone Detection

The TS75C25 recognizes the following tones:

- 2100Hz and 2225Hz answer tone detection

- 1650Hz V.21 Transpac answer tone detection

- 300 to 700Hz call progress tone detection

Adaptive equalization, DPLL and AGC compensate for line impaiments, frequency offset, group delay and amplitude distorsions.

Efficient rythm recovery algorithms provides accurate sampling on the receive signal with a variation up to  $\pm\,2.10^{-4}$

Decoded data are provided in scrambled or descrambled format

# 2.4. TS75C25 INTERFACE (fig. 6)

2.4.1. TS75C25 ANALOG INTERFACE. The transmit signal at the line interface (output ATO) is programmable over a 23dB dynamic range by 1dB steps through the TS75C250 mailbox.

The receive signal at the line interface (input RAI) can have a dynamic range from 0 to - 48dBm.

With a simple circuit using a minimum of external components, the TS75C25 can transmit with a level of - 12dBm on line and provide the adequate rejection of the transmit signal on the receive channel.

2.4.2. TS75C25 DIGITAL INTERFACE. The interface between the TS75C25 chip set and the control processor is managed by the TS75C250 via its system bus and internal mailbox. The mailbox allows the control processor to read/write three consecutive data-bytes through AD0-AD7 bus. The mailbox exchanges follows the protocol described in fig. 2.4.3.

The TS75C250 digital interface signals, and their definition are listed in table 2.

Figure 5: TS75C25: Receive Block Diagram.

Table 2 : Digital Interface Signals.

| Interface<br>Signals | Input/output<br>I/O | Signal Definition         |  |  |

|----------------------|---------------------|---------------------------|--|--|

| AD0                  | 1/0                 | Data-Bus (LSB)            |  |  |

| AD1                  | 1/0                 | Data-Bus                  |  |  |

| AD2                  | I/O                 | Data-Bus                  |  |  |

| AD3                  | 1/0                 | Data-Bus                  |  |  |

| AD4                  | 1/0                 | Data-Bus                  |  |  |

| AD5                  | 1/0                 | Data-Bus                  |  |  |

| AD6                  | 1/0                 | Data-Bus                  |  |  |

| AD7                  | 1/0                 | Data-Bus (MSB)            |  |  |

| SR/W                 | 1                   | Read/write Signal         |  |  |

| SDS                  | 1                   | Data Strobe               |  |  |

| IRQ                  | 0                   | Mailbox Handshake         |  |  |

| CS<br>RS             |                     | TS75C250 Chip Select      |  |  |

| RS                   | 1                   | Register Select           |  |  |

| Reset                | 1                   | TS75C250 Reset            |  |  |

| TxCLK                | 0                   | Additional Transmit Clock |  |  |

| RxCLK                | 0                   | Additional Receive Clock  |  |  |

| TxSCLK               |                     | Transmit Terminal Clock   |  |  |

These additional clocks may be used for specific applications.

Figure 6: Functional Interconnect Diagram.

2.4.3. MAILBOX DESCRIPTION. The TS75C250 requires the attention of the control processor at regular intervals in order to perform properly. The control processor must interact with the modem chip set in a timely manner to avoid improper operation.

To initialize communication exchanges between the TS75C25 and the control processor, the TS75C25 RESET pin must be maintained in its active (low) state during at least 870ns (5 clock cycles) by the microprocessor. At the end of reset, the TS75C250 gives the mailbox control to the processor.

It is also recommended to maintain the RESET in its active state until the exchanges can start.

Following a reset the status word read from the mailbox is not significant, and the content of the command word is ignored. So, the first mailbox exchange is a dummy exchange.

The mailbox located internally to the TS75C250 DSP contains 3-bytes input and 3-bytes output shift registers. The TS75C250 has an internal flag which indicates whether the TS75C250 or the control processor has access to the mailbox. The TS75C250 can relinquish its accessability to the mailbox by setting this internal flag, but it can no longer regain access to the mailbox as the flag is reset only after the control processor relinquishes its accessability to the mailbox.

The access protocol and system bus transfers are controlled by an internal I/O sequencer within the TS75C250 which operates as follows:

- 1/ The mailbox is made available to the control processor by the TS75C250 which drives the IRQ mailbox handshake signal to the active (low) state.

- 2/ The control processor detects RQ active and dummy reads the mailbox by forcing the TS75C250 chip select (CS) and register select (RS) low along with the write signal (SRW) high. The activated data strobe signal (SDS = 0) validates the above signals.

- 3/ The TS75C250 detects the dummy read of its mailbox via the control signals mentioned in step 2 and negates IRQ mailbox handshake signal after  $1\mu S$  (at least 5 clock cycles).

- 4/ The control processor detects the negation of IRQ indicating that the TS75C250 mailbox is available for data transfers. The control processor reads three bytes (one status word) and then writes three bytes (one command word) in the mailbox. If the status word is a transmit status word is a transmit status word, then a transmit command word must be written into the mailbox. Else, a receive command word must be written into the mailbox.

- 5/ The control processor ends the exchange protocol performing a dummy read of the mailbox as in step 2 but with RS in the high state.

The TS75C250 then owns the mailbox and can make it available again to the control processor as in step 1.

#### 3. USER INTERFACE

## 3.1. COMMAND AND STATUS WORDS

The TS75C25 chip set functionalities and status reporting are managed by the control processor through the TS75C250 mailbox, according to the protocol outlined earlier.

The command words are issued by the control processor and received by the TS75C250.

The status words are issued by the TS75C250 and delivered to the control processor.

The status words provide the status reporting.

Each command and status word of both the transmit and receive part comprises three bytes as described in the following sections.

The control processor must be able to handle :

- one mailbox transfer per transmit baud period and.

- · one mailbox transfer per receive baud period

- these transfers are plesiochronous. (Tx and Rx clocks have the same nominal frequency but can shift of ± 1.10<sup>-4</sup>, so the phase relation between Tx and Rx is time varying).

3.2. TRANSMIT AND RECEIVE COMMAND WORDS

Both the transmit and receive command words are built on the same programming model, but have to be programmed completely independently.

3.2.1. TRANSMIT COMMAND WORD. The table 3 shows the transmit command word (three bytes) programmation and transmit functionalities.

The first byte of the transmit command word permits the choice of the DTMF mode or the selection of the requested CCITT (with or without guard tone) or BELL standards.

The second byte contains the transmit parameters information register.

The third byte is the transmit data register of DTMF tone selection register. In this byte is also included the transmit enable bit which instructs the TS75C25 to transmit (or not) data to the line.

To manage the TS75C25 in an efficient way, it is recommended to work with a table stored in the control processor memory space. This table will reflect the

Table 3: Transmit Command Word Format.

| BIT | First Byte                                                          | Second Byte                                     |                 | Т      | hird B       | yte    |        |  |  |  |

|-----|---------------------------------------------------------------------|-------------------------------------------------|-----------------|--------|--------------|--------|--------|--|--|--|

| 0   | Transmit Mode Selection                                             | ansmit Mode Selection                           |                 |        | Transmit (0) |        |        |  |  |  |

| 1   | 0000 : Modem Disabled<br>0001 : V.22 Bis<br>0010 : V.22 0011 : B212 | Transmit                                        | DO              | D<br>P |              |        |        |  |  |  |

| 2   | 0100 : V.23 0101 : V.21<br>0110 : Bell 103                          | Attenuation                                     | D1              | S<br>K | Q            |        | D<br>T |  |  |  |

| 3   | 0111 : D.T.M.F.                                                     |                                                 | D2              | 0      | М            | F      | M<br>F |  |  |  |

| 4   | Transmit Signalling 00 : Signalling Disabled                        |                                                 | D3              | 0      |              | S<br>K |        |  |  |  |

| 5   | 01 : 550Hz<br>11 : 1800Hz                                           | Scrambler (ON/OFF)                              | D4              | 0      | 0            |        | 0      |  |  |  |

| 6   | Reserved                                                            | 64 x 1 (ON/OFF)                                 | D5              | 0      | 0            |        | 0      |  |  |  |

| 7   | ANSW/ORIG or DTMF1                                                  | V.22 Binary Rate Select<br>or DTMF <sup>2</sup> | Transmit Enable |        |              |        |        |  |  |  |

Notes: All the "RESERVED" bits must be cleared to "0" by the user.

1. DTMF: Higher/lower tone selection

2. DTMF : DUAL/single tone.

three bytes of the transmit command word and will be sent from the control processor to the TS75C25 at each transmit baud. In this table, the different fields could be programmed according to the CCITT or BELL standard needed taking into account the transmit parameters. Once the contents of the first and second byte have been determined for the whole transmission, only the transmit data field in the third byte has to be updated in the table. So, at each transmit baud, the TS75C250 will receive the complete three bytes, will check them and send the data.

## FIRST BYTE:

Bit 3, 2, 1 and 0: Transmit mode selection

These bits select the standard to use or the DTMF mode

0000 : Modem disabled

0001 to 0110: Transmit mode selection

0111

: DTMF. In this mode, the number which may be dialed is given by the proper binary combination of bits 4, 3, 2 and 1 in the third byte. Refer to paragraph "DTMF mode" for detailed information.

Other bit codes are reserved.

Bit 5 and 4: Transmit Signalling

These bits represent the tone to send regarding the requested functionalities.

00

: Signalling disabled

01 or 11

: Guard tone 550Hz or 1800Hz added

to the modulated signal.

10 : Reserved

Bit 6: Reserved

#### Bit 7: ANSWER/ORIGINATE or DTMF

This bit has two main functions. Its first function is to select the answer or originate mode. The second function is used in DTMF mode as explained in details in paragraph "DTMF mode".

In ANSWER/ORIGINATE mode, the bit 7 cleared to zero selects the answer mode (transmit in high channel). The bit 7 set to one selects the originate mode (transmit in low channel).

## SECOND BYTE:

Bit 4, 3, 2, 1, and 0: Transmit attenuation

The transmit levels without attenuation at the transmit interface output (ATO) on  $600\Omega$  are as follows:

- in FSK modes (V.23, V.21 and BELL 103)

- 0dBm

- in QAM (V.22 bis) and DPSK (V.22 and BELL 212) modes

- 5dBm when transmission on low channel

- 4dBm when transmission on high channel with guard tone composed by ;

- 5dBm (signal)

- 12dBm (guard tone)

- 5dBm when transmission on high channel without guard tone

- 4dBm in DTMF mode composed by

- 5dBm (high frequency)

- 7dBm (low frequency)

These are maximum levels which can be decreased by programming the transmit attenuation, with attenuation levels falling within 0dB (00000) and 23dB (10111) range, selectable in 1dB steps.

Selection within 11000 to 11111 correspond to an infinite attenuation.

At power-on, or after a reset applied on the reset pin of the TS75C250, an infinite attenuation is automatically programmed.

Bit 5 : Scrambler

The TS75C25 incorporates an auto-synchronized scrambler/descrambler in accordance with CCITT V.22 bis and V.22 and BELL 212 recommendation.

The scrambler is enabled (1) or disabled (0) by programming the bit 5.

When the scrambler is enabled, the input data is scrambled by dividing the data by a generating polynomial as defined in the V.22 bis and V.22 recommendations.

When the scrambler is disabled, the input data is routed around the scrambler in the transmit path.

Bit 6:64 x 1 Counter: The 64 x 1 counter is enabled (1) or disabled (0) by programming the bit 6.

When the  $64 \times 1$  counter is enabled, if 64 consecutive bits "1" are outputed by the scrambler, the next scrambler input bit is one's complemented. When the  $64 \times 1$  counter is disabled, the input data is routed around the  $64 \times 1$  counter in the transmit path.

Bit 7: V.22 binary rate selection or DTMF

This bit has two main functions. Its first function allows the possibility to select the lowest binary rate (V.22 at 600bps) when set to one, or the highest binary rate (V.22 at 1200bps) when cleared to zero.

The second function is used in DTMF mode as explained in details in paragraph "DTMF mode".

# THIRD BYTE:

Bit 0 : Transmit

This bit indicates the nature of the command word. It must be cleared to zero by the control processor to indicate to the TS75C25 that the command word

is a transmit command word, and that the 3-bytes written in the mailbox contain transmit information.

Bit 6 Thru 1: Transmitted data or DTMF tone selection. These bits have two main functions. The first function is to represent the data which will be sent according to the appropriate mode. The second function, used in DTMF mode, is to select by programming the bits 4, 3, 2, and 1 the generated tone which will be used to dial the proper number as shown in paragraph "DTMF mode" in table 5.

In QAM (V.22 bis) or DPSK (V.22 or BELL 212) modes, the bits 4, 3, 2, and 1 represent the data sent by the TS75C25. According to the selected mode, up to 4 bits will be used:

- In V.22 bis, each symbol (baud) is coded by 4 bits (quadribit)

- In V.22 at 1200bps and BELL 212 modes, each symbol is coded by 2 bits (dibit)

In V.22 at 600bps, each symbol is coded by only one bit.

In these modes, the mailbox exchanges are executed at the rate of 600 exchanges per second.

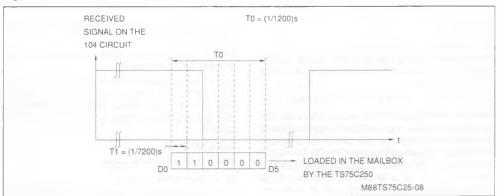

In FSK modes (V.21, V.23, and BELL 103) all the 6 bits (bit 6 thru 1) are used to represent the binary value of six samples of the transmitted signal. In these modes, the mailbox exchanges are executed at the rate of 1200 exchanges per second. Consequently, to perform a serial to parallel conversion the control processor has to sample the 103 circuit of the V.24/RS232 junction at 7.2kHz which is the sampling clock frequency (TxCCLK).

The bit 1 (which correspond to D0) is the first sample of the signal transmitted over the line as shown in figure 7.

Bit 7: transmit enable

This bit low instructs the TS75C25 to send data

Figure 7: FSK Mode.

#### DTMF MODE

The DTMF generator outputs one of 16 standard dual-tones. For specific applications where single tone is required, the DTMF generator provides the possibility to select either the high frequency or the low frequency of the standard dual tones.

All the bytes used to program the DTMF mode and mentioned in this section are those of the transmit command word.

The DTMF mode is selected by programming bits 3 to 0 in the first byte.

Choosing the dual-tone mode, which is the normal operating mode, is done with bit 7 in the second byte cleared to zero. The DTMF generator then outputs one of the sixteen standard dual tones selected

through bits 4 to 1 in the third byte as shown in table 5.

The single-tone mode is selected by setting to 1 the bit 7 in the second byte. This mode is used in specific cases where one frequency is to be generated. After one frequency pair is selected through bits 4 to 1 in the third byte as shown in table 5, the choice of the higher or lower frequency is made through bit 7 of the first byte. When bit 7 is set to 1 (respectively 0), the lower (respectively higher) frequency is generated.

In DTMF mode, the mailbox exchanges are executed at the rate of 1200 exchanges per second.

The programming of DTMF mode is summarized in table 4.

Table 4: DTMF (dual or single tone) Programmation.

| DTMF                       |   | First Byte s 3, 2, 1, 0       | 2nd Byte<br>Bit 7 | Third Byte<br>Bits 4, 3, 2, 1                              |

|----------------------------|---|-------------------------------|-------------------|------------------------------------------------------------|

| Dual-tone                  |   | 0111                          | 0                 | 4-bit Binary Value<br>Coding one of 16<br>Dual Tone        |

| Sinule-tone                |   | First Byte<br>Bits 3, 2, 1, 0 | 2nd Byte<br>Bit 7 | Third Byte<br>Bits 4, 3, 2, 1                              |

| High Frequency<br>Selected | 0 | 0111                          | 1                 | 4-bit Binary Value<br>Coding one of 16<br>Dual Tone (high) |

| Low Frequency<br>Selected  | 1 | 0111                          | 1                 | 4-bit Binary Value<br>Coding one of 16<br>Dual Tone (low)  |

In DTMF mode the transmit levels at the analog transmit interface output (ATO) are respectively - 5dBm for the high group frequencies, and - 7dBm

for the low group frequencies. These are maximum levels and can be decreased by programming the transmit attenuation in the second byte.

Table 5: Tone Encoding.

| Number  |      | DTMF Code in Third Byte Generated Tone |      |      |     |   |      |

|---------|------|----------------------------------------|------|------|-----|---|------|

| to Dial | Bit4 | Bit3                                   | Bit2 | Bit1 | Low |   | High |

| 0       | 0    | 0                                      | 0    | 0    | 941 | & | 1336 |

| 1       | 0    | 0                                      | 0    | 1    | 697 | & | 1209 |

| 2       | 0    | 0                                      | 1    | 0    | 697 | & | 1336 |

| 3       | 0    | 0                                      | 1    | 1    | 697 | & | 1477 |

| 4       | 0    | 1                                      | 0    | 0    | 770 | & | 1209 |

| 5       | 0    | 1                                      | 0    | 1    | 770 | & | 1336 |

| 6       | 0    | 1                                      | 1    | 0    | 770 | & | 1477 |

| 7       | 0    | 1                                      | 1    | 1    | 852 | & | 1209 |

| 8       | 1    | 0                                      | 0    | 0    | 852 | & | 1336 |

| 9       | 1    | 0                                      | 0    | 1    | 852 | & | 1477 |

| A       | 1    | 0                                      | 1    | 0    | 697 | & | 1633 |

| В       | 1    | 0                                      | 1    | 1    | 770 | & | 1633 |

| С       | 1    | 1                                      | 0    | 0    | 852 | & | 1633 |

| D       | 1    | 1                                      | 0    | 1    | 941 | & | 1633 |

|         | 1    | 1                                      | 1    | 0    | 941 | & | 1209 |

| #       | 1    | 1                                      | 1    | 1 1  | 941 | & | 1477 |

The accuracy of the frequencies is  $\pm 10^{-4}$ . The harmonic rejection level is at -65dB.

#### ANSWER TONE GENERATION

The TS75C25 chip set may generate four different standard frequencies which represent the usual auto answer tones.

- □ 1300Hz: V.23 Automatic connection tone

- 1650Hz: V.21 Transpac specific answer tone

- 2100Hz : CCITT V.22 bis, V.22, V.23 and V.21 answer tone

- 2225Hz: BELL 212 and BELL 103 answer tone

For answer tone generation, mailbox exchanges are executed at the rate of 1200 exchanges/second.

Table 6: Answer Tone Generation

| Tone   | FSK Mode<br>to Use | Bit 7 | First Byte<br>Bits 3, 2, 1, 0 | Third Byte<br>Bits 6, 5, 4, 3, 2, 1 |

|--------|--------------------|-------|-------------------------------|-------------------------------------|

| 1300Hz | V. 23 Answer       | 0     | 0100                          | 111 111                             |

| 1650Hz | V. 21 Answer       | 0     | 0101                          | 111 111                             |

| 2100Hz | V. 23 Answer       | 0     | 0100                          | 000 000                             |

| 2225Hz | B103 Answer        | 0     | 0110                          | 111 111                             |

3.2.2. RECEIVE COMMAND WORD. In the receive command word, the first byte permits the choice of the call progress and answer tone detection modes or the selection of the requested CCITT or BELL standards

The second byte defines additional receive parame-

The third byte informs the TS75C25 that the command word is a receive command word.

To manage the TS75C25 in an efficient way, it is re-

commended to work with a table stored in the control. processor memory space. This table will reflect the three bytes of the receive command word and will be sent from the memory by the control processor to the TS75C25 at each receive baud. In this table. the different fields could be programmed according to the CCITT or BELL standard needed taking into account the receive parameters. At each receive baud, the TS75C250 will receive and processes the complete three bytes.

Table 7: Receive Command Word Format.

| BIT | First Byte                                         | Second Byte             | Third Byte  |

|-----|----------------------------------------------------|-------------------------|-------------|

| 0   | Receive Mode Selection                             |                         | Receive (1) |

| 1   | 0000 : Modem Disabled<br>0001 : V.22 Bis           | Line Output Level       |             |

| 2   | 0010 : V.22 0011 : B212<br>0100 : V.23 0101 : V.21 | Reserved                |             |

| 3   | 0110 : Bell 103<br>0111 : Call Progress Tone       | Additional Clocks       | Reserved    |

| 4   | Answer Tone Selection                              |                         |             |

| 5   | Tx Synchronization                                 | Descrambler (ON/OFF)    |             |

| 6   | Carrier Detect Level                               | 64 x 1 (ON/OFF)         |             |

| 7   | Answer/originate                                   | V.22 Binary Rate Select |             |

Note: All the "RESERVED" bits must be cleared to "0" by the user.

## FIRST BYTE:

Bit 3, 2, 1, and 0: Receive mode selection

These bits select the standard to use or the call progress and answer tone detection mode.

: Modem disabled 0000

0001 to 0110: Receive mode selection

0111 : Call progress and answer tone detection mode. In this mode the TS75C25 recognizes different tones as explained in paragraph "call progress and answer tone detection"

Other bit codes are reserved.

Bit 4: Answer tone selection

This bit defines the answer tone to be detected. It selects either 1650Hz (Transpac) or 2100/2225Hz answer tone. When high, the detect answer tone is 1650Hz. When low, the detect answer tone is 2100/2225Hz.

Bit 5: Tx synchronization signal programming

This bit allows synchronization of all transmit clocks on a selected source. When bit 5 is set to 1, all the TS75C25 transmit clocks (TxCLK, TxCCLK, TxRCLK) are synchronized on TxSCLK input (typically a terminal clock signal coming from the V.24/RS232 interface). This avoids overspeed and maintains a complete synchronization during the transmission. If there is no signal on TxSCLK coming from the terminal clock, the transmit clocks are free-running at their nominal frequencies.

When the bit 5 is set to 0, the TS75C25 transmit clocks are synchronized on the receive clocks. This possibility may be used for remote digital loopback.

#### Bit 6: Carrier detection level

The TS75C25 can be used both on the public switched telephone network (PSTN) and with leased lines

When the bit 6 is set to 0, the carrier detection threshold are:

# - 43 and - 48dBm (PSTN)

When the bit 6 is set to 1, the carrier detection threshold are:

- 33 and - 38dBm (leased lines).

#### Bit 7: Answer / originate

The bit 7 cleared to zero selects the answer mode (receive in low channel). The bit 7 set to one selects the originate mode (receive in high channel).

#### SECOND BYTE:

The signal level applied to the loud speaker will be as follow:

Bit 1 and 0: Line Output Programmable Level.

| B1 B0 | Attenuation Level | Unit |

|-------|-------------------|------|

| 00    | 00                | dB   |

| 01    | 0                 | dB   |

| 10    | 6                 | dB   |

| 11    | 12                | dB   |

Bit 2 · Reserved

Bit 4 and 3: Additional Clocks

| B4 B3 | Clock Frequency | Unit |

|-------|-----------------|------|

| 00    | 2400            | Hz   |

| 01    | 1600            | Hz   |

| 10    | 1200            | Hz   |

| 11    | 600             | Hz   |

Both Tx and Rx clocks are programmed with the same frequency according to B4 and B3. These clocks are not obligatory for the functionning of the TS75C25, but may be useful for specific application.

### Bit 5 : Descrambler

The TS75C25 incorporates an auto-synchronized scrambler/descrambler in accordance with CCITT V.22 bis and V.22 and BELL 212 recommendation.

The descrambler is enabled when bit 5 is set to 1, or disabled when bit 5 is set to 0.

When the descrambler is enabled, the data stream is multiplied by the same polynomial that divided the data at the scrambler in the transmission path.

When the descrambler is disabled, the data stream is routed around the descrambler in the receive path.

Bit 6: 64 x 1 Counter. When the 64 x 1 counter is enabled, if 64 consecutive bits "1" are decoded, the next descrambler input bit is one's complemented. When the 64 x 1 counter is disabled, the output data is routed around the 64 x 1 counter in the receive part. The 64 x 1 counter is enabled when bit 6 is set to 1, or disabled when bit 6 is set to 0.

## Bit 7: V.22 binary rate select

This bit allows the possibility to select the lowest binary rate (V.22 at 600bps) when set to one, or the highest binary rate (V.22 at 1200bps) when set to zero.

### THIRD BYTE:

# Bit 0 : Receive

This bit indicates the nature of the command word. It must be set to one to indicate to the TS75C25 that the command word is a receive command word. This involves that the 3-bytes written in the mailbox by the control processor to the TS75C25 contain receive command information.

Bit 7 Thru 1: Reserved (must be cleared to 0)

#### 3.3 TRANSMIT AND RECEIVE STATUS WORD

The status words are issued by the TS75C250 and provide the status reporting to the control processor.

#### 3.3.1. TRANSMIT STATUS WORD

Table 8: Transmit Status Word Format.

| BIT | First Byte   | Second Byte | Third Byte |

|-----|--------------|-------------|------------|

| 0   | Transmit (0) |             |            |

| 1   |              |             |            |

| 2   |              |             |            |

| 3   |              | _           |            |

| 4   | Reserved     | Reserved    | Reserved   |

| 5   |              |             |            |

| 6   |              |             |            |

| 7   |              |             |            |

#### FIRST BYTE:

Bit 0 : Transmit

This bit when low informs the control processor that the status word issued by the TS75C25 is a transmit status word.

Bit 7 Thru 1 : Reserved

SECOND BYTE:

Bit 7 Thru 0: Reserved

THIRD BYTE:

Bit 7 Thru 0: Reserved

### 3.3.2. RECEIVE STATUS WORD

Table 9: Receive Status Word Format.

| BIT |    | First Byte                                  | Second Byte         | Third Byte |             |        |          |

|-----|----|---------------------------------------------|---------------------|------------|-------------|--------|----------|

| 0   |    | Receive (1)                                 |                     |            | Res         | erved  |          |

| 1   | D0 | Data Before                                 | Reserved            | D0         | Data        | DO     |          |

| 2   | D1 | Descrambling                                |                     | D1         | After       | D1     |          |

| 3   | D2 | (Q.A.M. , D.P.S.K.)                         |                     | D2         | Descr.      | D2     | Data     |

| 4   | D3 | (2                                          | Equalization Status | D3         | (Q.A.M.,    | D3     | (F.S.K.) |

| 5   |    | Reserved                                    | Signal Quality      | 1          | D.P.S.K.)   | D4     |          |

| 6   |    | S1 Sequence                                 | Carrier Detect      | 1          | D.1 .0.1(.) | D5     |          |

| 7   | Ĉ  | S1 Sequence or Call Progress Tone Detection | Reserved            |            | Answer To   | ne Det | ection   |

Note: In QAM and DPSK modes, both for the data after and before descrambling, the unused bits are set to "1" by the TS75C25.

#### FIRST BYTE:

Bit 0: Receive

This bit set to one by the TS75C25 indicates to the control processor that the current status word is a receive status word.

Bit 4. 3, 2, and 1: Data before descrambling

Used only in QAM and DPSK modes, these four bits represent the data received before descrambling, i.e., after the demodulator and before the descrambler. Data is coded on four bits (D3, D2, D1, D0) in V.22 bis, on two bits (D1, D0) in V.22 at 1200bps and BELL 212, on only one bit (D0) in V.22 at 600bps. The unused bits are set to 1 by the TS75C25.

The mailbox exchange rate between the TS75C250 and the control processor is done at 600 exchanges per second. Both for QAM and DPSK modes, D0 (which correspond to the bit 1) is the first bit received

Bit 5: Reserved

Bit 7 and 6 : S1 handshake sequence (V.22 bis) mode

During the V.22 bis handshake sequence, these two bits indicate the presence or the absence of the "S1" sequence detected by the TS75C25. If the TS75C25 gives an alternance (at each baud period in reception) of values "10" and "01" on bit 7 and 6,

the "S1" sequence is present in reception. Else, this means its absence.

Bit 7: Call progress tone detection (call progress/answer tone mode).

This bit low indicates detection of energy in the band 300 - 700Hz with a detection threshold of - 43dBm. This bit high means there is no energy detected. (see paragraph call progress and answer tone detection).

SECOND BYTE:

Bits 3, 2, 1, and 0: Reserved

Bit 4: Equalization status

This bit will go high (1) in case of equalization loss (retrain sequence initialization or fallback mode).

Bit 5: Signal quality

This bit will go high (1) when the quality of the received signal is too low for a good transmission.

Bit 6: Carrier detect

This bit indicates the presence or the absence of the on-line signal as follows:

- This bit will go low (0) if the signal level is higher than -43dBm on PSTN or - 33dBm on leased lines

- This bit will go high (1) if the signal level is lower than -48dBm on PSTN or - 38dBm on leased lines.

The minimum hysteresis level is 2dB.

The information on the on-line signal may be used by the control processor to manage the 109 signal of the V.24 junction.

Bit 7: Reserved

THIRD BYTE:

Bit 0: Reserved

Bit 6 Thru 1 : Data received or data after descrambling.

These six bits contain the received data and have to be processed by the control processor according to the selected standards:

In QAM and DPSK modes, bit 4 thru 1 represent the data received after descrambling, if the descrambler is enabled. Otherwise, they represent the data received without descrambling.

The data is encoded on four bits (D3, D2, D1, D0) in V.22 bis, on two bits (D1, D0), in V.22

at 1200bps and Bell 212, on only one bit (D0) in V.22 at 600bps. The unused bits are set to one by the TS75C25.

The mailbox exchange rate between the TS75C250 and the control processor is done at 600 exchanges per second. For both QAM and DPSK modes, D0 (which correspond to bit 1) is the first bit received.

In FSK modes (V.21, V.23, and BELL 103) all the six bits are used to represent the digital value of six samples of the received signal. In these modes, the mailbox exchange must be executed at the rate of 1200 exchanges per second. Consequently to perform a parallel to serial conversion the control processor has to resend these bits on the 104 circuit of the V.24/RS232 junction at 7.2kHz.

Bit 1 (which correspond to D0) is the first sample of the incoming signal received over the line as shown in figure 8.

Figure 8: FSK Receive Mode.

Bit 7: Answer tone detection

Used in answer tone detection mode, this bit when low (0), indicates the presence of the answer tone (CCITT 2100Hz, BELL 2225Hz or Transpac

1650Hz) sent by the far-end modem. When high (1), it means no detection of answer tone. Refer to paragraph "call progress and answer tone detection" for further details.

## CALL PROGRESS AND ANSWER TONE DETECTION

The TS75C25 call progress detection part is activated by detection of energy in the 300 to 700Hz call progress tone bandwidth. The call progress mode must be selected in the first byte (bit 3 thru 0) of the receive command word

Then the bit 7 of the first byte of the receive status word indicates to the control processor that the call progress tone is detected (bit 7 = 0) or not (Bit 7 = 1).

In answer tone mode, the TS75C25 may recognize three different standard frequencies which represent the usual answer tones sent by the far-end modern as described hereunder.

2100Hz: CCITT modes answer tone V.21 and V.23 - 2225Hz: BELL answer tones

- 1650Hz: Transpac V.21 answer tone

The answer tone mode must be selected in the first byte (bit 3 thru 0) of the receive command word and the answer tone selection (1650Hz or 2100/2225Hz) with the bit 4.

Then bit 7 in the third byte of the receive status word indicates to the control processor that the answer tone is detected (bit 7 = 0) or not (bit 7 = 1).

The table 10 shows the programmation of the receive command word, and the status reporting contained in the receive status word.

DTMF mode and transmit enable = 1 must be selected in the transmit command word.

Table 10: Call Progress and Answer Tone Detection Programming Model.

|                                                       | Receive Command               | d Word | Re                  | ceive Status Word                                                                           |

|-------------------------------------------------------|-------------------------------|--------|---------------------|---------------------------------------------------------------------------------------------|

|                                                       | First Byte<br>Bit 3, 2, 1, 0, | Bit 4  | First Byte<br>Bit 7 | Third Byte<br>Bit 7                                                                         |

| Call Progress<br>Mode and<br>2100/2225<br>Answer Tone | 0111                          | 0      |                     | Progress Tone Detected<br>of Call Progress Tone<br>0 2100/2225Hz Detected<br>1 No Detection |

| Call Progress<br>Mode and<br>1650Hz<br>Answer Tone    | 0111                          | 1      |                     | Progress Tone Detected<br>of Call Progress Tone<br>0 1650HZ Detected<br>1 No Detection      |

# 4. ELECTRICAL SPECIFICATIONS

#### 4.1. MAXIMUM RATINGS

## TS75240

| Symbol            | Parameter                   | Value        | Unit |

|-------------------|-----------------------------|--------------|------|

| V <sub>CC</sub> * | Supply Voltage              | - 0.3 to 7.0 | V    |

| V <sub>in</sub> * | Input Voltage               | - 0.3 to 7.0 | V    |

| TA                | Operating Temperature Range | 0 to 70      | °C   |

| T <sub>stg</sub>  | Storage Temperature Range   | - 55 to 150  | °C   |

<sup>\*</sup> With respect to Vss.

Stresses above those hereby listed may cause permanent damage to the device. The ratings are stress ones only and functional operation of the device at these or any conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability. Standard MOS circuits handling procedure should be used to avoid possible damage to the device

# TS7542

| Symbol           | Parameter                                   | Value                                    | Unit |

|------------------|---------------------------------------------|------------------------------------------|------|

|                  | Supply Voltage between V * and AGND or DGND | - 0.3 to + 7                             | V    |

|                  | Supply Voltage between V and AGND or DGND   | - 7 to + 0.3                             | V    |

|                  | Voltage between AGND and DGND               | - 0.3 to + 0.3                           | V    |

|                  | Digital Input Voltage                       | DGND - 0.3 to V <sub>CC</sub> * + 0.3    | V    |

|                  | Digital Output Voltage                      | DGND - 0.3 to V <sub>CC</sub> * + 0.3    | V    |

|                  | Digital Output Current                      | - 20 to + 20                             | mA   |

|                  | Analog Input Voltage                        | $V_{CC}^ 0.3 \text{ to } V_{CC}^+ + 0.3$ | V    |

|                  | Analog Output Voltage                       | $V_{CC}^ 0.3 \text{ to } V_{CC}^+ + 0.3$ | V    |

|                  | Analog Output Current                       | - 10 to + 10                             | mA   |

|                  | Power Dissipation                           | 500                                      | mW   |

| Toper            | Operating Temperature Range                 | 0 to + 70                                | °C   |

| T <sub>stg</sub> | Storage Temperature                         | - 65 to + 150                            | °C   |

# 4.2. DC ELECTRICAL CHARACTERISTICS DGND = AGND = 0 V

Digital Supply  $V_{CC} = 5.0 \text{ V} \pm 10 \%$ ,  $V_{SS} = 0$ ,  $T_A = 0 \text{ to } + 70 \,^{\circ}\text{C}$  (unless otherwise specified)

| Symbol          | Parameter                                          | Min.  | Typ. | Max. | Unit |

|-----------------|----------------------------------------------------|-------|------|------|------|

| Vcc             | Supply Voltage                                     | 4.5   | 5    | 5.5  | V    |

| VIL             | Input Low Voltage                                  | - 0.3 |      | 0.8  | ٧    |

| V <sub>IH</sub> | Input High Voltage                                 | 2.4   |      | Vcc  | V    |

| lin             | Input Leakage Current                              | - 10  |      | + 10 | μΑ   |

| VoH             | Output High Voltage (I <sub>io ad</sub> = - 300μA) | 2.7   |      |      | V    |

| Vol             | Output Low Voltage (I <sub>io ad</sub> = 2mA)      |       |      | 0.5  | V    |

| PD              | Total Power Dissipation                            |       | 0.5  |      | W    |

| Cin             | Input Capacitance                                  |       | 10   |      | ρF   |

| ITSI            | Three State (off state) Input Current              | - 20  |      | + 20 | μА   |

# **Analog Supply**

| Symbol | Parameter                                           | Min.   | Тур. | Max.   | Unit |

|--------|-----------------------------------------------------|--------|------|--------|------|

| V*     | Positive Power Supply                               | 4.75   |      | 5.25   | V    |

| V-     | Negative Power Supply                               | - 5.25 |      | - 4.75 | V    |

| 1+     | Positive Supply Current (receive signal level 0dbm) |        |      | 30     | mA   |

| 1-     | Negative Supply Current (receive signal level 0dBm) | - 25   |      |        | mA   |

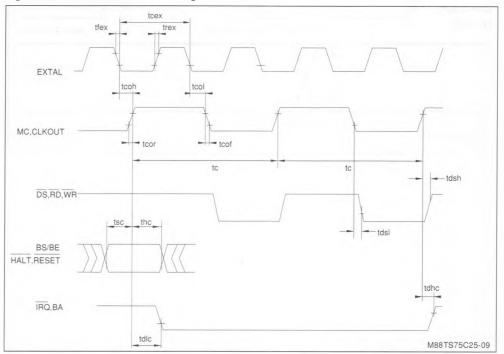

# AC ELECTRICAL SPECIFICATIONS - CLOCK AND CONTROL PINS TIMING

$5V_{CC} = 5.0V \pm 10\%$ .  $T_A = 0$  to  $70^{\circ}C$ , see figure 9.1.) OUTPUT LOAD = 50 pF . DC characteristics I load

REFERENCE LEVELS  $V_{IL} = 0.8V$   $V_{IH} = 2.4V$   $V_{OL} = 0.8V$   $V_{OH} = 2.4V$

tr, tf ≤ 5ns for Input Signals

| Symbol | Parameter                                           | Min. | Тур. | Max. | Unit |

|--------|-----------------------------------------------------|------|------|------|------|

| tcex   | External Clock Cycle Time (tc = 2 x tcex)           | 50   |      | 200  | ns   |

| tcex   | External Clock Cycle Time (tc = 4 x tcex)           | 25   |      | 100  | ns   |

| tfex   | External Clock Fall Time                            |      |      | 5    | ns   |

| trex   | External Clock Rise Time                            |      |      | 5    | ns   |

| tcoh   | EXTAL to CLKOUT High Delay                          |      | 25   |      | ns   |

| tcol   | EXTAL to CLKOUT Low Delay                           |      | 25   |      | ns   |

| tcor   | CLKOUT Rise Time                                    |      |      | 10   | ns   |

| tcof   | CLKOUT Fall Time                                    |      |      | 10   | ns   |

| tdsl   | CLKOUT to DS, RD, WR Low                            |      | 5    |      | ns   |

| tdsh   | CLKOUT to DS. RD, WR High                           |      | 5    |      | ns   |

| tsc    | Control Input Set-up Time (BS/IT, BE, Reset)        | 20   |      |      | ns   |

| thc    | Control Input Hold Time (BS0, BS2, BE3, BE6, Reset) | 10   |      |      | ns   |

| tdlc   | CLKOUT to Control Output Low (RQ. BA)               |      |      | 30   | ns   |

| tdhc   | CLKOUT to Control Output High (BA, IRQ)             |      |      | 30   | ns   |

Figure 9: Clock and Control Pins Timing.

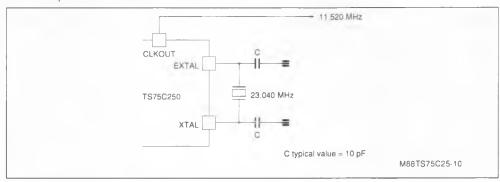

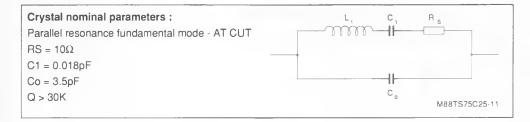

# INTERNAL CLOCK OPTION

A crystal oscillator can be connected across XTAL and EXTAL. The frequency of CLKOUT is half the crystal fundamental frequency, and can be used by the control processor.

Then the 5.76MHz required by the Analog Front End can be easily obtained.

# 4.3.2. TS7542 : CLOCK GENERATOR

# **CLOCK WAVE FORMS**

| Symbol | Parameter                    | Test Conditions             | Min. | Typ.  | Max. | Unit |

|--------|------------------------------|-----------------------------|------|-------|------|------|

| PC     | Main Clock Period            | XTAL1 Input                 | 150  | 173.6 |      | ns   |

| twcL   | Main Clock Low Level Width   | XTAL1 Input                 | 50   |       |      | ns   |

| twch   | Main Clock High Level Width  | XTAL1 Input                 | 50   |       |      | ns   |

| tac    | Main Clock Rise Time         | XTAL1 Input                 |      |       | 50   | ns   |

| tFC    | Main Clock Fall Time         | XTAL1 Input                 |      |       | 50   | ns   |

| toc    | Clock Output Delay Time      | All Clock Outputs CL = 50pF |      |       | 500  | ns   |

| tro    | Clock Output Transition Time | All Clock Outputs CL = 50pF |      |       | 100  | ns   |

Unless otherwise noted, electrical characteristics are specified over the operating range. Typical values are given for  $V^* = 5.0V$  and  $T_{amb} = 25$  C.

Figure 10: Clock Generator.

# 4.3.3. LOCAL BUS TIMING (TS75C250 and TS7542) ( $V_{CC}$ = 5.0V $\pm$ 10%, $T_A$ = 0° to + 70°C, see figure 11)

| Symbol           | Parameter                       | Min.        | Max.   | Unit |

|------------------|---------------------------------|-------------|--------|------|

| tpw              | RD, WR. AS Pulse Width          | 1/2 tc - 10 | 1/2 tc | ns   |

| tarw             | Address Valid to WR, AS, RD Low | 1/2 tc - 25 |        | ns   |

| tah              | Address Hold Time               | 5           |        | ns   |

| t <sub>DSW</sub> | Data Set-up Time, Write Cycle   | 1/2 tc - 25 |        | ns   |

| t <sub>DHW</sub> | Data Hold Time, Write Cycle     | 5           |        | ns   |

| tosa             | Data Set-up Time, Read Cycle    | 15          |        | ns   |

| t <sub>DHR</sub> | Data Hold Time, Read Cycle      | 5           |        | ns   |

Figure 11: Local Bus Timing Diagram.

Note: In multicycle exchanges, tpw, tdsw, duration is extended by 1, 2 or 3 machine cycle lenghts (tc).

# 4.3.4. SYSTEM BUS TIMING (TS75C250 and control processor) (V $_{CC}$ = 5.0V $\pm$ 10%, T $_{A}$ = 0° to + 70°C)

| Symbol | Parameter                        | Min. | Max. | Unit |

|--------|----------------------------------|------|------|------|

| tspw   | SDS Pulse Width                  | 50   |      | ns   |

| tsaw   | SR/W. CS, RS Set-up Time         | 20   |      | ns   |

| tsah   | SR/W. CS. RS Hold after SDS High | 5    |      | ns   |

| tsosa  | Data Set-up Time. Read Cycle     | 20   |      | ns   |

| tsDHR  | Data Hold Time, Read Cycle       | 5    |      | ns   |

| tspsw  | Data Set-up Time, Write Cycle    |      | 30   | ns   |

| tsphw  | Data Hold Time, Write Cycle      | 5    | 30   | ns   |

| toslot | SDS Low to DTACK Low             |      | 30   | ns   |

| toshot | SDS High to DTACK High           |      | 40   | ns   |

<sup>\*</sup> DTACK is an open drain output test load include  $R_L$  = 820  $\Omega$  at  $V_{CC}$

Figure 12: System Bus Timing Diagram.

# 4.3.5. DAA INTERFACE (DAA and TS7542)

Analog Transmit Output (ATO)

$V^*=5\bar{V}\pm5\%,~0^{\circ}C\leq T_{amb}\leq +~70^{\circ}C~V^-=-5V\pm5\%,~0^{\circ}C\leq T_{amb}\leq +~70^{\circ}C$  (unless otherwise specified)

| Symbol | Parameter                                              | Min.  | Тур. | Max.  | Unit |

|--------|--------------------------------------------------------|-------|------|-------|------|

| Vos    | Output DC Offset                                       | - 250 |      | + 250 | mV   |

| CL     | Load Capacitance                                       |       |      | 50    | pF   |

| RL     | Load Resistance                                        | 1.2   |      |       | kΩ   |

| Vout   | Output Voltage Swing $(R_L > 1.2k\Omega \ C_L < 50pF)$ | - 2.5 |      | + 2.5 | ٧    |

| Rout   | Output Resistance (read cycle)                         |       |      | 5     | Ω    |

# Receive Analog Input (RAI).

| Symbol | Parameter                   | Min.  | Typ. | Max.  | Unit |

|--------|-----------------------------|-------|------|-------|------|

| Vin    | Input Voltage               | - 2.5 |      | + 2.5 | V    |

| lin    | Input Current (write cycle) | - 1   |      | + 1   | μА   |

#### 5. PIN CONNECTIONS

## PIN CONNECTIONS (continued)

## TS75C250

# TS7542 Interface

| Name         | Pin | Function                       | Description                                                                                                                                       |  |  |

|--------------|-----|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| D0 thru D15  | I/O | Local Data Bus                 | Only D8 thru D15 lines are used for data transfer between the TS75C250 and TS7542.  D0 thru D7 are not used and are left unconnected.             |  |  |

| A8 thru A11  | 0   | Local Address Bus              | Address Lines to the TS7542                                                                                                                       |  |  |

| DS           | 0   | Data Strobe                    | This signal synchronizes the transfer between the TS75C250 and the TS7542.                                                                        |  |  |

| R/W          | 0   | Read/Write                     | Indicates the current bus cycle state.                                                                                                            |  |  |

| CLKOUT       | 0   | Clock Output                   | This signal generated by the TS75240 is at half the frequency of the crystal. It can be divided by 2 to provide the 5.76MHz clock for the TS7542. |  |  |

| BE3 thru BE6 | 1   | Receive and<br>Transmit Clocks | These two inputs are connected to the receive and transmit clocks generated by the TS7542.                                                        |  |  |

# TS75C250

# System Interface.

| Name Pin Function        |                   | Function           | Description                                                                                                      |  |  |  |

|--------------------------|-------------------|--------------------|------------------------------------------------------------------------------------------------------------------|--|--|--|

| AD0 thru AD7             | I/O               | System Data Bus    | These bi-directional lines are used for data transfer between the TS75C250 mailbox and a control processor.      |  |  |  |

| cs                       | 1                 | Chip Select        | This active low input is asserted when the TS75C250 is to be accessed by the control processor.                  |  |  |  |

| RS                       | l Register Select |                    | This signal is used with CS to control the data transfer between the control processor and the TS75C250 mailbox. |  |  |  |

| SDS                      | - 1               | System Data Strobe | Synchronizes the transfer on the system bus.                                                                     |  |  |  |

| SR/W I System Read/Write |                   | System Read/Write  | Indicates the current system bus cycle state.                                                                    |  |  |  |

| IRQ O Interrupt Request  |                   | Interrupt Request  | Handshake signal sent to the master to gain access to the mailbox.                                               |  |  |  |

# Others Pins.

| Name          | Pin    | Function        | Description                                                                 |

|---------------|--------|-----------------|-----------------------------------------------------------------------------|

| BS0 thru BS2  | 1      | Branch on State | These three inputs are not used and must be grounded.                       |

| EXTAL I Clock |        | Clock           | Crystal Input for Internal Oscillator or Input Pin for External Oscillator. |

| XTAL          | 1      | Clock           | Together with EXTAL this pin is used for the external 23.040MHz crystal.    |

| Vcc           | Supply | Power Supply    |                                                                             |

| Vss           | Supply | Ground          |                                                                             |

| RESET         | 1      | Reset           |                                                                             |

| BE3 thru BE4  | ī      | Branch on Edge  | These two inputs are not used and must be grounded.                         |

# PIN DESCRIPTION TS7542

| N°    | Name           | Description                                                                                                                                                                                                                                                          |  |

|-------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1-4   | D4-D7          | Bidirectional Data Bus.                                                                                                                                                                                                                                              |  |

| 5     | CLKINI         | Clock Initialization Input. Must be tied to V* during normal operation.                                                                                                                                                                                              |  |

| 6     | R/W            | Read/Write Selection Input. This input indicates whether the current bus cycle is a read (high) or write (low) cycle.                                                                                                                                                |  |

| 7-8   | CS1-CS0        | Chip Select Input. The chip is selected when CS0 = 0 and CS1= 1.                                                                                                                                                                                                     |  |

| 9-10  | RS0-RS1        | Register Select Input. Select the register involved in a read or write operation.                                                                                                                                                                                    |  |

| 11    | Ē              | Enable Input. Enables Selection Inputs Active on a low level for read operation. Active on a positive-going edge for write operation.                                                                                                                                |  |

| 12    | V <sup>-</sup> | Negative Supply Voltage. $V^- = -5V \pm 5\%$                                                                                                                                                                                                                         |  |

| 13    | V <sup>+</sup> | Positive Supply Voltage. V* = + 5V ± 5%                                                                                                                                                                                                                              |  |

| 14    | RFO            | Receive Filter Analog Output. Designed to be connected to AGC1 input through a 1 $\mu\text{F}$ non polarized capacitor.                                                                                                                                              |  |

| 15    | LAO            | Line Attenuator Output. Duplexer analog output usefull for line monitoring during call progress.                                                                                                                                                                     |  |

| 16    | DxI            | Duplexer Input. Analog input subtracted from the receive anti-aliasing filter output to implement duplexer function.                                                                                                                                                 |  |

| 17    | RAI            | Receive Analog Input. Analog input tied to the transmission line.                                                                                                                                                                                                    |  |

| 18    | AGC2           | This pin must be connected to the analog ground through a 1 $\mu$ F non polarized capacitor, in order to cancel the offset voltage of the AGC amplifier.                                                                                                             |  |

| 19    | AGC1           | Analog input of the AGC amplifier and of the carrier level detector.                                                                                                                                                                                                 |  |

| 20    | CD1            | This pin must be connected to the analog ground through a $1\mu F$ non polarized capacitor, in order to remove the offset voltage of the carrier level detector amplifier.                                                                                           |  |

| 21    | V+             | Positive Power Supply Voltage                                                                                                                                                                                                                                        |  |

| 22    | AGND           | Analog Ground. All analog signals are referenced to this pin.                                                                                                                                                                                                        |  |

| 23    | V-             | Negative Supply Voltage                                                                                                                                                                                                                                              |  |

| 24    | V+             | Positive Supply Voltage                                                                                                                                                                                                                                              |  |

| 25    | ATO            | Analog Transmit Output. Capable of driving $1200\Omega$ load with 5V peak to peak amplitude.                                                                                                                                                                         |  |

| 26    | EXI            | External Transmit Input. Can be programmmed to be connected to the transmit filter or to the transmit attenuator input.                                                                                                                                              |  |

| 27    | RxCCLK         | Receive Conversion Clock Output                                                                                                                                                                                                                                      |  |

| 28    | RxRCLK         | Receive Baud Rate Clock Output                                                                                                                                                                                                                                       |  |

| 29    | RxCLK          | Receive Bit Rate Clock Output                                                                                                                                                                                                                                        |  |