# MODEM RECEIVE ANALOG INTERFACE

- TWO CHANNEL 12-BIT ANALOG TO DIGITAL CONVERTER FOR RECEPTION OF DIGITAL DATA FROM THE TELEPHONE LINE AND ECHO CANCELLATION (with asynchronous multiplexing of 2 plesiochronous channels)

- PROGRAMMABLE SWITCHED CAPACITOR BAND-PASS FILTER

- PROGRAMMABLE GAIN AMPLIFIER FROM 0 TO 46.5 dB WITH 1.5 dB STEPS

- PROGRAMMABLE BACK CHANNEL REJEC-TION AND RECONSTRUCTION FILTER

- CARRIER LEVEL DETECTOR WITH PRO-GRAMMABLE THRESHOLD

- DIRECT INTERFACE WITH STANDARD MPU 8-BIT BUS

- LOW POWER CMOS TECHNOLOGY

- AVAILABLE IN DIL OR SURFACE MOUNT PACKAGE

# DESCRIPTION

The TS68951 is a Receive (Rx) Analog Front-End circuit designed to implement the analog to digital conversion and filtering required by high-speed voice-band modems or speech coding applications using digital signal processing technology.

The TS68951 meets all the CCITT recommendations from V.22 to V.33 including full-duplex recommendations with echo-cancellation (V.32) thanks to its multiplexed 2nd channel.

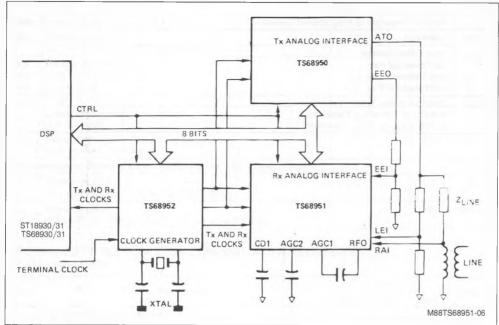

Used in conjunction with the TS68950 Transmit (Tx) Analog Front-End circuit and the TS68952 clock generator\*, it provides a very cheap and efficient interface to digital signal processing functions in high speed modems or telephony applications.

\*The interconnection between the 3 chips of the Modern Analog Front End (MAFE) is decribed p16/30.

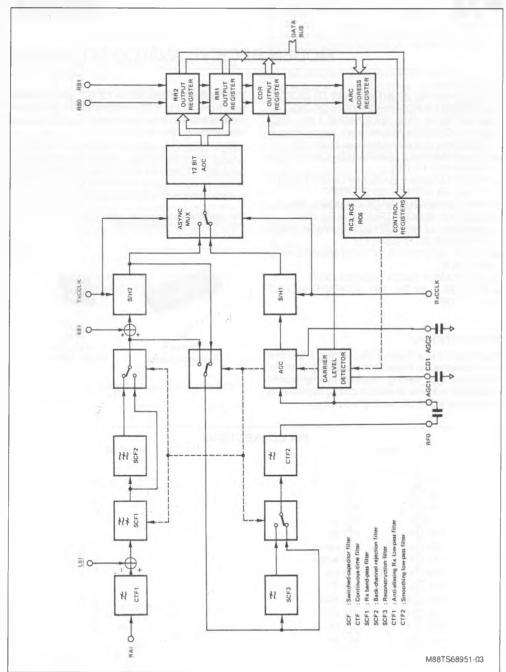

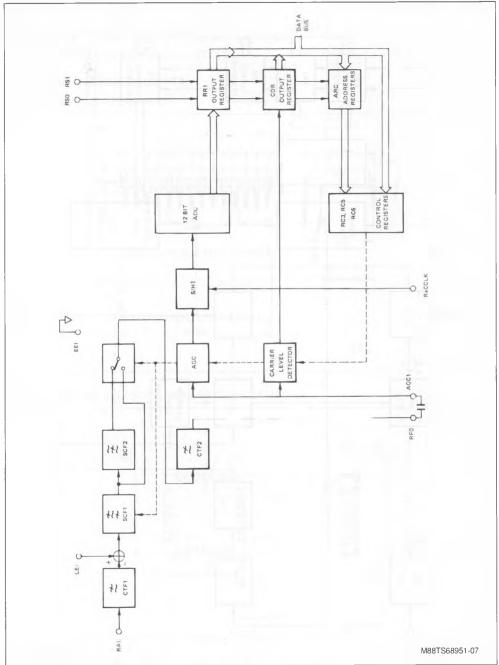

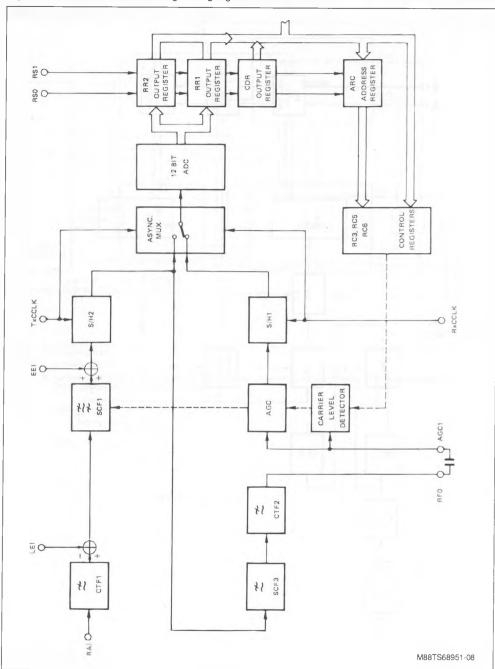

# **BLOCK DIAGRAM**

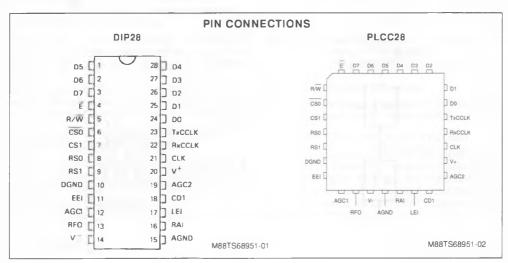

### PIN DESCRIPTION

| Name           | Description                                                                                                                                                            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D5-D7          | Data Bus                                                                                                                                                               |

| Ē              | Enable Input. Enables Selection Inputs. Active On a Low Level for Read Operation. Active On a Positive Edge for Write Operation.                                       |

| R/W            | Read/write Selection Input. Read operation is selected on a high level. Write operation is selected on a low level.                                                    |

| CSO-CS1        | Chip Select Inputs. The chip set is selected when $\overline{\text{CSO}} = 0$ and $\overline{\text{CS1}} = 1$ .                                                        |

| RSO-RS1        | Register Select Inputs. Select the register involved in a read or write operation.                                                                                     |

| DGND           | Digital Ground. All digital signals are referenced to this pin.                                                                                                        |

| EEI            | Estimated Echo Input. When operating in echo cancelling mode, this signal is added to the reception bandpass filter output.                                            |

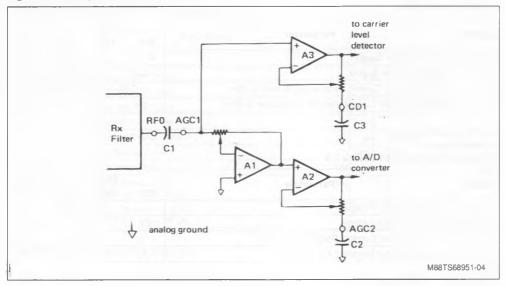

| AGC1           | Analog input of the automatic gain control amplifier and of the carrier level detector.                                                                                |

| RFO            | Reception Filter Analog Output. Designed to be connected to AGC1 input through a 1 μF nor polarised capacitor.                                                         |

| V-             | Negative Power Supply. $V^- = -5 V \pm 5 \%$ .                                                                                                                         |

| AGND           | Analog Ground. All analog signals are referenced to this pin.                                                                                                          |

| RAI            | Receive Analog Input. Analog input tied to the transmission line.                                                                                                      |

| LEI            | Local Echo Input. Analog input substracted from the receive anti-aliasing filter output.                                                                               |

| CD1            | This pin must be connected to the analog ground through a 1 µF non polarised capacitor, in order to cancel the offset voltage of the carrier level detector amplifier. |

| AGC2           | This pin must be connected to the analog ground through a 1 µF non polarised capacitor, in order to cancel the offset voltage of the AGC amplifier.                    |

| V <sup>+</sup> | Positive Power Supply $V^* = +5 V \pm 5 \%$ .                                                                                                                          |

| CLK            | Master Clock Input. Nominal Frequency 1.44 MHz.                                                                                                                        |

| RxCCLK         | Receive Conversion Clock.                                                                                                                                              |

| TxCCLK         | Transmit Conversion Clock.                                                                                                                                             |

| D0-D4          | Data Bus.                                                                                                                                                              |

### **FUNCTIONAL DESCRIPTION**

The TS68951 is a received analog interface for voice-band MODEM. It is able to perform the receive interface function for three types of synchronous MODEM:

- Four-wire or two-wire half duplex MODEM

- Two-wire full duplex band-split MODEM

- Two-wire full duplex echo cancelling MODEM

# FOUR/TWO WIRE HALF DUPLEX MODEM TWO WIRE BAND SPLIT MODEM

In these modes of operation, EEI input must be tied to the analog ground. The analog signal treatment of receive input is shown in figure 3 p17/30.

Programming requirements:

Band-pass filter cut-off frequencies

- Back channel rejection filter (presence or absence according to the application)

- SCF1 or SCF2 output as input of CTF2

- AGC gain

- Carrier level detector threshold

The receive samples are coded at RxCCLK rate and can be read from receive register (RR1)

### TWO WIRE ECHO CANCELLING MODEM

This mode of operation uses the full capabilities of the TS68951. The analog treatment of receive input is shown in figure 4 p18/30. The echo cancelling operation is achieved by means of subtraction of the LEI signal from the output of CTF1 duplexer and addition of the EEI signal to the output of SC1.

After the local echo reduction by the duplexer the resultant signal consists of the receive signal plus the echo signal generated by the transmission line mismatch: this undesirable signal is then cancelled at the output of the Rx band-pass filter.

Programming requirements:

- Band-pass filter cut-off frequencies

- SCF1 output as input of S/H2

- Output of S/H2 as input of SCF3 and output of SCF3 as input of CTF2.

- AGC gain

# Carrier level detector threshold

Residual signal samples from S/H2 output are coded at TxCCLK rate and can be read from receive register 2 (RR2), hence the signal processor may correlate them with the transmit samples to update the coefficients of the filter that generates the estimated echo.

The receive signal samples are coded at RxCCLK rate and can be read from receive register 1 (RR1).

### **FUNCTIONAL SPECIFICATIONS**

### **BUS AND REGISTERS CONTROL**

For any operation involving bus and registers, the chip select bits CS0 and CS1 must be active (CS0 = 0 and CS1 = 1)

The seven internal registers are divided into four write only registers and three read-only registers

### WRITE OPERATION

There are three control registers (RC3, RC5, RC6) and one address register (ARC) which can be written; but only ARC can be directly addressed.

The control registers are indirectly addressed by the word contained in ARC according to table 1.

Table 1.

| Addressed Control Register |    | Word Contained in ARC |    |    |    |    |    |    |  |  |  |

|----------------------------|----|-----------------------|----|----|----|----|----|----|--|--|--|

| Addressed Control Register | D7 | D6                    | D5 | D4 | D3 | D2 | D1 | D0 |  |  |  |

| RC3                        | 0  | 1                     | 0  | X  | Х  | X  | X  | Х  |  |  |  |

| RC5                        | 1  | 0                     | 0  | X  | Х  | Х  | Х  | Х  |  |  |  |

| RC6                        | 1  | 0                     | 1  | X  | Х  | Х  | Х  | X  |  |  |  |

X: don't care.

When a write operation is selected (refer to table 3) the data present on the bus are strobed on a positive edge of E and the content of ARC is incremented

Note: Addresses of RC3 and RC5 are separated by two increments

### READ OPERATION

There are two 12-bit receive registers (RR1, RR2) and a 1-bit carrier detector register (CDR)

RR2 contains the coded samples of the residual signal and RR1 the coded samples of the receive signal

The active bit of CDR is D7:D0 to D6 are forced to 0

When the RMS value of CTF2 output is greater than the programmed threshold, bit 7 of CDR is set. The nominal response time of the carrier detector to a signal settlement or removal is 1.78 ms.

When a read operation is selected (refer to table 3) the data are sent to the bus on a low level of  $\overline{E}$ ; a high level on  $\overline{E}$  sets the output bus drivers in a high impedance state

As the data bus has only 8 bits, the contents of RR1 or RR2 must be read in two cycles. The four less significant bits are transferred in the first cycle and the eight most significant bits are transferred in the second cycle according to the format, table 2.

Table 2.

|              | D7    | D6    | D5   | D4   | D3   | D2   | D1   | D0   |

|--------------|-------|-------|------|------|------|------|------|------|

| First Cycle  | RRx3  | RRx2  | RRx1 | RRx0 | 0    | 0    | 0    | 0    |

| Second Cycle | RRx11 | RRx10 | RRx9 | RRx8 | RRx7 | RRx6 | RRx5 | RRx4 |

An internal latch selects the first or the second byte and is automatically incremented on a positive edge of E when one of the receive registers is addressed. This latch is not reset at power-on, so it needs to be reset before the first read operation: reset occurs on any positive edge of E for any operation, provided none of the receive registers is addressed; the first byte is selected when reset.

### RR1 AND RR2 OUTPUT CODE:

The output code is a 2's complement delivering values from -2048 up to +2047. Since the converter codes voltage between - V <sub>ref</sub> and + V <sub>ref</sub>, the theo-

retical decision voltage corresponding to code C can be computed as follows :

$$V_C = \frac{2C + 1}{4095} V_{ref}$$

where  $V_{\text{ref}}$  is the reference voltage of the A/D converter,  $V_{\text{ref}}$  nominal value is 2.5 V and C is the algebraic value of code C.

### Example:

Assume the output code is the hexadecimal value \$8B1; the algebraic value of this code C=-1871 therefore  $V_C=-2.283$  V.

Table 3.

| R/W | RSO | RS1 | Operation                                              |

|-----|-----|-----|--------------------------------------------------------|

| 0   | 1   | 1   | Write Control Register Addressed by ARC                |

| 0   | 1   | 0   | Write Address Register (ARC)                           |

| 1   | 0   | 1   | Read Receive Register 2 (RR2) (residual signal sample) |

| 1   | 0   | 0   | Read Receive Register 1 (RR1) (receive signal sample)  |

| 1   | 1   | 0   | Read Carrier Detector Register (CDR)                   |

### CONTROL REGISTERS DESCRIPTION

### POWER-ON

The control registers are not initialised at power-on; they must be initialised before reading any word from the output registers.

#### REGISTER RC3

The contents of RC3 sets the -3 dB cut-off frequencies of SCF1 receive band-pass filter, determines the presence or the absence of SCF2 back channel rejection filter and of SCF3 reconstruction filter, and selects receive signal path to the second filtering section; without echo-cancelling the output of SCF1

or SCF2 is selected; with echo-cancelling the output of S/H2 is selected.

The band-pass filter consists of a 5th-order elliptic low-pass filter and of a 2nd order high-pass filter whose cut-off frequencies can be programmed by (LP1, LP2) and (HP1, HP2) respectively, (refer table 4).

The rejection filter is present when REJ bit is high.

The reconstruction filter is present when REC bit is high.

S/H2 output is selected when S/A bit is high.

Table 4.

| D7<br>HP2 | D6<br>HP1 | D5<br>LP2 | D4<br>LP1 | D3<br>REJ | D2<br>S/A | D1<br>REC | D0     |                                | RC3 R        | egister             |                           |

|-----------|-----------|-----------|-----------|-----------|-----------|-----------|--------|--------------------------------|--------------|---------------------|---------------------------|

|           |           |           |           |           |           |           |        |                                | Low-pa:      | ss Filter           |                           |

|           |           |           |           |           |           |           |        | Sampling Frequency Fs<br>(kHz) |              | - 3 dB (            | Cut-off Frequency<br>(Hz) |

|           |           | 0         | 0         |           |           |           | х      | 72                             |              |                     | 800                       |

|           |           | 0         | 1         |           |           |           | x      | 144                            |              |                     | 1600                      |

|           |           | 1         | 0         |           |           |           | x      | 288                            |              |                     | 3200                      |

|           |           | 1         | 1         |           |           |           | x      | 288                            |              |                     | 3200                      |

|           |           |           |           |           |           |           |        |                                | High-pa:     | ss Filter           |                           |

|           |           |           |           |           |           |           |        | Sampling Freque<br>(kHz)       | ency Fs      | - 3 dB (            | Cut-off Frequency<br>(Hz) |

| 0         | х         |           |           | 0         |           |           | х      | 36                             |              |                     | 250                       |

| 1         | 0         |           |           | 0         |           |           | x      | 72                             |              |                     | 500                       |

| 1         | 1         |           |           | 0         |           |           | х      | 144                            |              |                     | 1600                      |

|           |           |           |           |           |           |           |        | High                           | pass and     | Rejection           | Filter                    |

|           |           |           |           |           |           |           |        | Sampling<br>Frequency<br>(kHz) |              | Cut-off<br>ncy (Hz) | Rejected Band<br>(Hz)     |

| 1         | 0         |           |           | 1         |           |           | х      | 72                             | 80           | 00                  | 370-470                   |

| 1         | 1         |           |           | 1         |           |           | х      | 144                            | 22           | 00                  | 800-1600                  |

|           |           |           |           |           |           |           |        |                                | S/H2 Se      | lection             |                           |

|           |           |           |           |           | 0         |           | х      | Deselected                     | _            |                     |                           |

|           |           |           |           |           | 1         |           | х      | Selected                       |              |                     |                           |

|           |           |           |           |           |           |           |        | Recor                          | struction    | Filter Sele         | ction                     |

|           |           |           |           |           |           | 0         | x<br>x | Deselected<br>Selected (san    | npling frequ | ency Fs = :         | 288 kHz)                  |

X: don't care.

# **REGISTER RC5**

The content of RC5 sets the gain of the AGC amplifier between 0 dB and 46.5 dB with 1.5 dB steps.

**Note**: The AGC loop control is performed by the signal processor.

Table 5.

| 7 | D 6 | D 5 | D4 | D3 | D2 | D1 | D0 | RC5           |

|---|-----|-----|----|----|----|----|----|---------------|

|   |     |     |    |    |    |    |    | AGC Gain (dB) |

| 0 | 0   | 0   | 0  | 0  | х  | х  | х  | 0             |

| 0 | 0   | 0   | 0  | 1  | х  | ×  | х  | 1.5           |

| 0 | 0   | 0   | 1  | 0  | х  | ×  | х  | 3             |

| 0 | 0   | 0   | 1  | 1  | х  | х  | х  | 4.5           |

| 0 | 0   | 1   | 0  | 0  | х  | х  | х  | 6             |

| 0 | 0   | 1   | 0  | 1  | х  | ×  | x  | 7.5           |

| 0 | 0   | 1   | 1  | 0  | ×  | х  | х  | 9             |

| 0 | 0   | 1   | 1  | 1  | x  | ×  | х  | 10.5          |

| ) | 1   | 0   | 0  | 0  | x  | ×  | x  | 12            |

| 0 | 1   | 0   | 0  | 1  | х  | х  | x  | 13.5          |

| 0 | 1   | 0   | 1  | 0  | х  | х  | x  | 15            |

| 0 | 1   | 0   | 1  | 1  | x  | ×  | x  | 16.5          |

| 0 | 1   | 1   | 0  | 0  | х  | х  | x  | 18            |

| 0 | 1   | 1   | 0  | 1  | х  | х  | х  | 19.5          |

| ) | 1   | 1   | 1  | 0  | х  | х  | X  | 21            |

| ) | 1   | 1   | 1  | 1  | x  | х  | X  | 22.5          |

| 1 | 0   | 0   | 0  | 0  | x  | х  | x  | 24            |

| 1 | 0   | 0   | 0  | 1  | x  | ×  | х  | 25.5          |

| 1 | 0   | 0   | 1  | 0  | x  | x  | х  | 27            |

| 1 | 0   | 0   | 1  | 1  | x  | x  | x  | 28.5          |

| 1 | 0   | 1   | 0  | 0  | x  | x  | x  | 30            |

| 1 | 0   | 1   | 0  | 1  | x  | ×  | x  | 31.5          |

| 1 | 0   | 1   | 1  | 0  | x  | х  | х  | 33            |

| 1 | 0   | 1   | 1  | 1  | ×  | ×  | х  | 34.5          |

| 1 | 1   | 0   | 0  | 0  | х  | ×  | x  | 36            |

| 1 | 1   | 0   | 0  | 1  | х  | х  | х  | 37.5          |

| 1 | 1   | 0   | 1  | 0  | х  | х  | х  | 39            |

| 1 | 1   | 0   | 1  | 1  | ×  | х  | x  | 40.5          |

| 1 | 1   | 1   | 0  | 0  | х  | х  | х  | 42            |

| 1 | 1   | 1   | 0  | 1  | х  | ×  | х  | 43.5          |

| 1 | 1   | 1   | 1  | 0  | x  | ×  | х  | 45            |

| 1 | 1   | 1   | 1  | 1  | х  | х  | x  | 46.5          |

X: don't care.

### REGISTER RC6

The content of RC6 sets the carrier level detector threshold. (Refer to table 6).

The threshold values are grouped by pair; values belonging to each pair have 2.5 dB separation which allows the signal processor to perform software hysteresis

Table 6.

| D7 | D6 | D 5 | D4 | D3 | D2 | D1 | D0 | RC6             |

|----|----|-----|----|----|----|----|----|-----------------|

|    |    |     |    |    |    |    |    | Threshold (dBm) |

| 0  | 0  | 0   | х  | х  | х  | х  | х  | - 29.85         |

| 0  | 0  | 1   | x  | х  | х  | х  | х  | - 27.35         |

| 0  | 1  | 0   | х  | х  | х  | х  | х  | - 36.65         |

| 0  | 1  | 1   | х  | х  | х  | х  | х  | - 34.15         |

| 1  | 0  | 0   | х  | х  | х  | х  | х  | - 46.75         |

| 1  | 0  | 1   | х  | х  | х  | х  | х  | - 44.25         |

| 1  | 1  | 0   | х  | х  | х  | х  | х  | - 46.75         |

| 1  | 1  | 1   | х  | х  | х  | х  | х  | - 44.25         |

X: don't care.

### **CLOCK**

The master clock CLK, the receive conversion clock (RxCCLK) and the transmit conversion clock (TxCCLK) are generated in the TS68952 clock generator. There are three possible frequencies for the conversion clocks: 7.2 kHz, 8 kHz and 9.6 kHz.

The nominal values of the RxCCLK and TxCCLK clocks must be identicals (these clocks are plesiochronous and real values within  $\pm$  100 ppm according to CCITT recommandations).

The frequency of RxCCLK and TxCCLK is controlled by two independant Digital Phase Locked Loops (DPLL). TxCCLK can be synchronised on an external Terminal Clock (TxSCLK) or on the Rx bit rate clock; in these cases 350 ns discrete phase shifts occurs on CLK and TxCCLK synchronously with TxCCLK negative edge with a repetition rate of 600 Hz, 800 Hz or 1 000 Hz according to the programmation of RC1 control register in the TS68952.

### A/D CONVERSION

The A/D converter is a 12 bit resolution, 8 bit minimum integral linearity, monotonic converter. The in-

put voltage ranges from – 2.5 V to + 2.5 V ; and the conversion time is better than 50  $\mu s.$

### ASYNCHRONOUS MULTIPLEXING

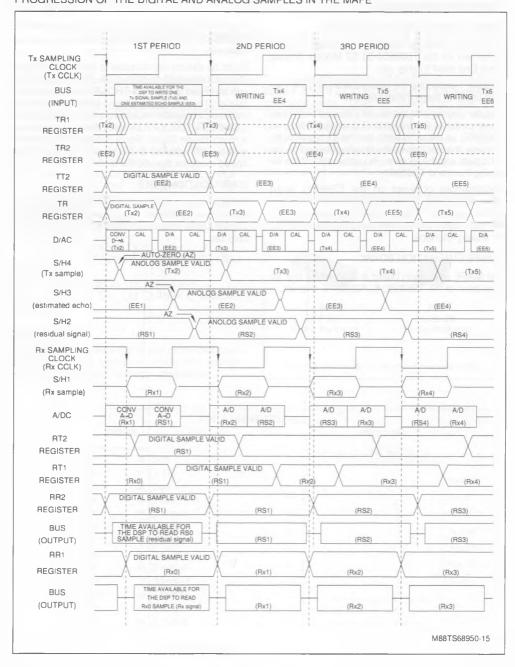

Samples on the output of S/H1 and S/H2 are converted respectively at RxCCLK frequency and TxCCLK frequency. Since RxCCLK and TxCCLK are plesiochronous, the order of conversion is determined by an asynchronous logic. The output register RR1 and RR2 are respectively loaded on the negative edge of RxCCLK and TxCCLK.

### AGC AND CLD AMPLIFIERS.

The AGC consists of two cascaded amplifiers A1 and A2 (see fig.1) AC coupling is obtained from C1 and C2 external capacitors. C2 can be used as an auxiliary input for performing an analog loop located after echo cancellation. The carrier level detector (CLD) amplifier A3 also needs an external capacitor C3.

Figure 1: Rx Amplifiers Schematic.

# **ELECTRICAL SPECIFICATIONS**

The electrical specifications are given for operating temperature range (0 °C, 70 °C).

### ABSOLUTE MAXIMUM RATINGS

| Symbol           | Parameter                                   | Value                  | Unit |

|------------------|---------------------------------------------|------------------------|------|

|                  | Supply Voltage between V * and AGND or DGND | - 0.3 to + 7           | ٧    |

|                  | Supply Voltage between V and AGND or DGND   | - 7 to + 0.3           | ٧    |

|                  | Voltage between AGND and DGND               | - 0.3 to + 0.3         | V    |

|                  | Digital Input Voltage                       | DGND - 0.3 to V* + 0.3 | V    |

|                  | Digital Output Voltage                      | DGND - 0.3 to V* + 0.3 | ٧    |

|                  | Digital Output Current                      | - 20 to + 20           | mA   |

| 4                | Analog Input Voltage                        | V 0.3 to V + + 0.3     | ٧    |

|                  | Analog Output Voltage                       | V 0.3 to V + 0.3       | V    |

|                  | Analog Output Current                       | - 10 to + 10           | mA   |

|                  | Power Dissipation                           | 500                    | mW   |

| Toper            | Operating Temperature                       | 0 to + 70              | °C   |

| T <sub>stq</sub> | Storage Temperature                         | - 65 to + 150          | °€   |

### POWER SUPPLIES DGND = AGND = 0 V

| Symbol | Parameter                                            |        | Value |        |      |  |  |

|--------|------------------------------------------------------|--------|-------|--------|------|--|--|

| Symbol |                                                      | Min.   | Тур.  | Max.   | Unit |  |  |

| ٧٠     | Positive Power Supply                                | 4.75   |       | 5.25   | V    |  |  |

| V -    | Negative Power Supply                                | - 5.25 |       | - 4.75 | V    |  |  |

| 1+     | Positive Supply Current (receive signal level 0 dBm) |        |       | 20     | mA   |  |  |

| -      | Negative Supply Current (receive signal level 0 dBm) | - 20   |       |        | mA   |  |  |

# DIGITAL INTERFACE

Control Inputs.

Voltages Referenced to DGND = 0 V

| Symbol           | Parameter                                                        |      | Value |      |      |  |  |

|------------------|------------------------------------------------------------------|------|-------|------|------|--|--|

| Symbol           |                                                                  | Min. | Тур.  | Max. | Unit |  |  |

| V <sub>1</sub> L | Low Level Input Voltage                                          |      |       | 0.8  | V    |  |  |

| V <sub>IH</sub>  | High Level Input Voltage                                         | 2.2  |       |      | V    |  |  |

| V <sub>IL</sub>  | Low Level Input Current DGND < V <sub>1</sub> < 0.8 V            | - 10 |       | 10   | μА   |  |  |

| V <sub>IH</sub>  | High Level Input Current 2.2 V < V <sub>I</sub> < V <sup>+</sup> | - 10 |       | 10   | μА   |  |  |

# DATA BUS

Voltages Referenced to DGND = 0 V

| Symbol          | Parameter                                                                      |      | Value |      |      |  |  |

|-----------------|--------------------------------------------------------------------------------|------|-------|------|------|--|--|

| Syllibol        | rarameter                                                                      | Min. | Тур.  | Max. | Unit |  |  |

| VIL             | Low Level Input Voltage                                                        |      |       | 0.8  | V    |  |  |

| V <sub>IH</sub> | High Level Input Voltage                                                       | 2.2  |       |      | V    |  |  |

| VoL             | Low Level Output Voltage (I <sub>OL</sub> = 2.5 mA)                            |      |       | 0.4  | V    |  |  |

| V <sub>OH</sub> | High Level Output Voltage (I <sub>OL</sub> = 2.5 mA)                           | 2.4  |       |      | V    |  |  |

| loz             | High Impedance Output Current (when E is high and DGND < V <sub>I</sub> < V *) | - 50 |       | 50   | μА   |  |  |

# ANALOG INTERFACE

All Voltages Referenced to AGND = 0 V

| Symbol | Parameter                                           |       | 11-:4 |      |      |

|--------|-----------------------------------------------------|-------|-------|------|------|

| Symbol | ratameter                                           | Min.  | Тур.  | Max. | Unit |

| Vin    | Input Voltage EEI, LEI, RAI                         | - 2.5 |       | 2.5  | V    |

| lin    | Input Current EEI, LEI, RAI (- 2.5 V < Vin < 2.5 V) | - 1   |       | 1    | μΑ   |

| Rin    | Input Resistance AGC1, AGC2                         | 1.5   |       |      | kΩ   |

| Rin    | Input Resistance CD1                                | 0.7   |       |      | kΩ   |

| Vout   | Output Voltage RFO CL = 50 pF, RL = 1 k $\Omega$    | - 2.5 |       | 2.5  | V    |

| Rout   | Output Resistance RFO                               |       |       | 2    | Ω    |

| RL     | Load Resistance RFO                                 | 1     |       |      | kΩ   |

| CL     | Load Capacitance RFO                                |       |       | 50   | pF   |

# BUS TIMING CHARACTERISTICS

(see foot notes 1 and 2 on timing diagrams)

| Cumbal                          | Banamatan                                                       |      | Hania |      |      |      |

|---------------------------------|-----------------------------------------------------------------|------|-------|------|------|------|

| Symbol                          | Parameter                                                       |      | Min.  | Тур. | Max. | Unit |

| toyo                            | Cycle Time                                                      | (1)  | 320   |      |      | ns   |

| tweL                            | Pulse Width E Low Level                                         | (2)  | 180   |      |      | ns   |

| twen                            | Pulse Width E High Level                                        | (3)  | 100   |      |      | ns   |

| t <sub>r</sub> , t <sub>f</sub> | Clock Rise and Fall Time                                        | (4)  |       |      | 20   | ns   |

| tHCE                            | Control Signal Hold Time                                        | (5)  | 10    |      |      | ns   |

| tsce                            | Control Signal Set-up Time                                      | (6)  | 40    |      |      | ns   |

| tsDI                            | Input Data Set-up Time                                          | (7)  | 120   |      |      | ns   |

| t <sub>HDI</sub>                | Input Data Hold Time                                            | (8)  | 1     |      |      | ns   |

| t <sub>SDO</sub>                | Output Data Set-up Time<br>(1 TTL load and CL = 50 pF)          | (9)  |       |      | 150  | ns   |

| t <sub>DZ</sub>                 | Output High Impedance Delay Time<br>(1 TTL load and CL = 50 pF) | (10) |       |      | 80   | ns   |

# RECEPTION CHARACTERISTICS

PERFORMANCE OF THE WHOLE RECEPTION CHAIN (input RAI or LEI, output RR1)

| Cumbal | Devemater                                                                                                                      |       | I I m i A |       |      |

|--------|--------------------------------------------------------------------------------------------------------------------------------|-------|-----------|-------|------|

| Symbol | Parameter                                                                                                                      | Min.  | Typ.      | Max.  | Unit |

| G      | Gain (AGC gain = 0 dB, RxCCLK = 9600 Hz, $V_{in}$ = 775 m $V_{eff}$ , $f$ = 2000 Hz)                                           | - 0.5 |           | - 0.5 | dB   |

| TD     | Total Non Harmonic Distortion<br>(AGC gain = 0 dB, RxCCLK = 9600 Hz, V <sub>in</sub> = 775 mV <sub>eff</sub> ,<br>f = 2000 Hz) |       |           | - 58  | dB   |

# PERFORMANCE OF THE RECEPTION SUB-CHAIN (from RAI input to S/H2 input)

| Symbol | Total Distortion                                                              |      | Unit |              |      |

|--------|-------------------------------------------------------------------------------|------|------|--------------|------|

| Symbol | ratameter                                                                     | Min. | Тур. | p. Max. – 72 | Unit |

| TD     | Total Distortion (RxCCLK = 9600 Hz, $V_{in}$ = 1.6 $V_{eff}$ , $f$ = 2000 Hz) |      |      | - 72         | dB   |

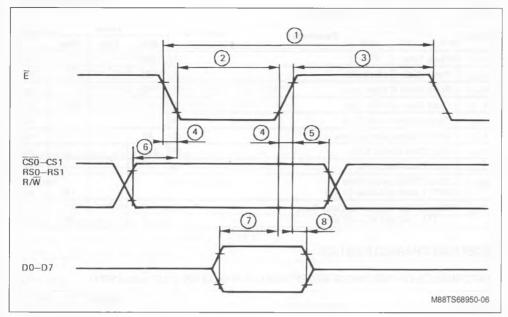

# WRITE OPERATION

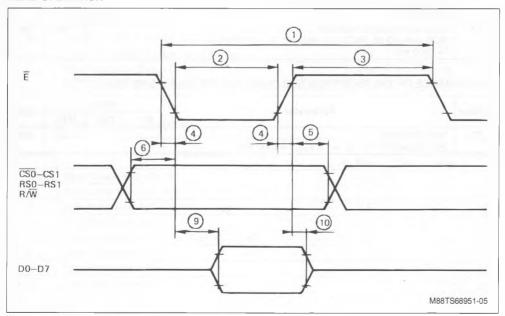

### **READ OPERATION**

Notes: 1. Voltage levels shown are V<sub>IL</sub> < 0.4 V, V<sub>IH</sub> > 2.4 V, unless otherwise specified 2. Measurement points shown are 0.8 V and 2.2 V, unless otherwise specified

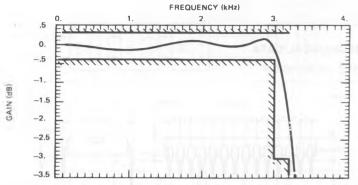

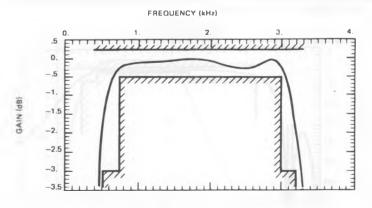

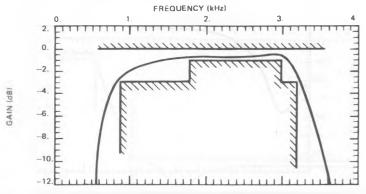

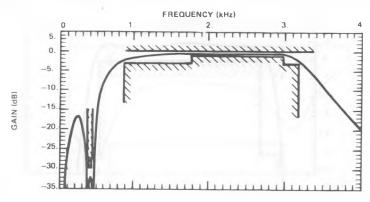

# RECEIVE BAND-PASS FILTER AND REJECTION FILTER (input RAI, output RFO)

| Symbol           | Parameter                                                                                                       |              | Value |                                   |                      |  |

|------------------|-----------------------------------------------------------------------------------------------------------------|--------------|-------|-----------------------------------|----------------------|--|

| Oymbo.           | T a l'alliete                                                                                                   | Min.         | Тур.  | Max.                              | Unit                 |  |

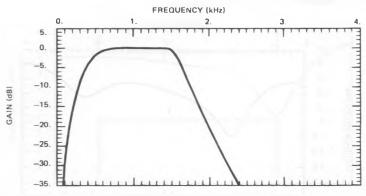

| Low-pa           | ss Filter (Fs = 288 kHz)                                                                                        |              |       |                                   |                      |  |

| Gref             | Reference Gain $(V_{in} = 775 \text{ mV}_{eff}, f = 1800 \text{ Hz})$                                           | - 0.5        |       | 0.5                               | dB                   |  |

| G <sub>rel</sub> | Relative Gain to $G_{ref}$<br>0 Hz < f < 3000 Hz<br>f = 3200 Hz<br>f > 6250 Hz                                  | - 0.4<br>- 3 |       | 0.3<br>0.3<br>- 60                | dB<br>dB<br>dB       |  |

| T <sub>gp</sub>  | Group Propagation Delay Time<br>(f = 1800 Hz)                                                                   |              |       | 300                               | μs                   |  |

| T <sub>gpd</sub> | Group Propagation Delay Time Distortion (600 Hz < f < 3000 Hz)                                                  |              |       | 360                               | μs                   |  |

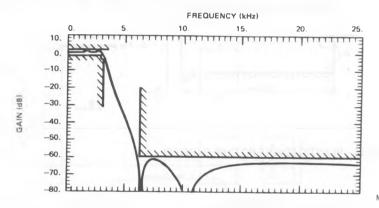

| High-pa          | ss Filter (Fs = 72 kHz)                                                                                         | ,            |       |                                   |                      |  |

| Gref             | Reference Gain<br>(V <sub>in</sub> = 775 mV <sub>eff</sub> , f = 1800 Hz)                                       | - 0.5        |       | 0.5                               | dB                   |  |

| G <sub>rel</sub> | Relative Gain to $G_{ref}$<br>500 Hz < f $\leq$ 3000 Hz<br>f = 500 Hz<br>f < 100 Hz                             | - 0.4<br>- 3 |       | 0.3<br>0.5<br>– 25                | dB<br>dB<br>dB       |  |

| Tgp              | Group Propagation Delay Time<br>(f = 1800 Hz)                                                                   |              |       | 50                                | μs                   |  |

| T <sub>gpd</sub> | Group Propagation Delay Time Distortion (600 Hz < f < 3000 Hz)                                                  |              |       | 450                               | μs                   |  |

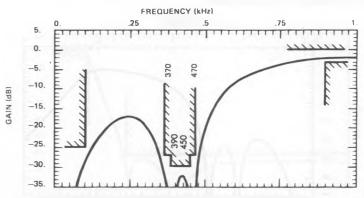

| High-pa          | ss Filter and Rejection Filter (Fs = 72 kHz)                                                                    |              |       |                                   |                      |  |

| Gret             | Reference Gain<br>(V <sub>in</sub> = 775 mV <sub>eff</sub> , f = 1800 Hz)                                       | - 1          |       | 0                                 | dB                   |  |

| Grel             | Relative Gain to $G_{ref}$<br>f = 100  Hz<br>f = 370  Hz<br>390  Hz < f < 450  Hz<br>f = 470  Hz<br>f = 900  Hz |              |       | - 25<br>- 27<br>- 30<br>- 27<br>0 | dB<br>dB<br>dB<br>dB |  |

| Tgp              | Group Propagation Delay Time<br>(f = 1800 Hz)                                                                   |              |       | 75                                | μS                   |  |

| T <sub>gpd</sub> | Group Propagation Delay Time Distortion (600 Hz < f < 3000 Hz)                                                  |              |       | 1400                              | μs                   |  |

Note: The measurement frequencies are integer sub-multiples of filters sampling frequencies.

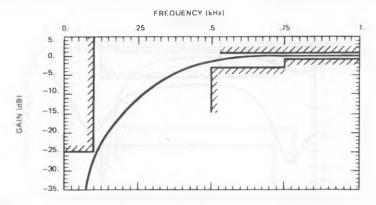

### RECONSTRUCTION FILTER

| Symbol           | Parameter                                                                             |              | Unit |                    |                   |  |

|------------------|---------------------------------------------------------------------------------------|--------------|------|--------------------|-------------------|--|

| ,                |                                                                                       | Min.         | Typ. | Max.               |                   |  |

| Recons           | truction Filter (Fs = 288 kHz)                                                        |              |      |                    |                   |  |

| Gref             | Reference Gain<br>(V <sub>in</sub> = 775 mV <sub>eff</sub> , f = 2000 Hz)             | - 0.3        |      | 0.3                | dB                |  |

| Grei             | Relative Gain to $G_{Tef}$<br>0 Hz < f < 2900 Hz<br>f = 3100 Hz<br>f > 6000 Hz        | - 0.4<br>- 3 |      | 0.3<br>0.3<br>- 60 | dB<br>dB<br>dB    |  |

| Тдр              | Group Propagation Delay Time<br>(f = 1800 Hz)                                         |              |      | 300                | μs                |  |

| T <sub>gpd</sub> | Group Propagation Delay Time Distortion<br>(600 Hz < f < 3000 Hz)                     |              |      | 440                | μs                |  |

| Whole F          | Reception Filtering Chain (input RAI or LEI, output RFO)                              |              |      |                    |                   |  |

| Gref             | Reference Gain<br>(V <sub>in</sub> = 775 mV <sub>eff</sub> , f = 2000 Hz, RC3 = \$AO) | - 0.5        |      | 0.5                | dB                |  |

| N <sub>rfo</sub> | Noise on RFO<br>(RAI, LEI, EEI tied to AGND 250 Hz < f < 3200 Hz)                     |              |      | 350                | μV <sub>eff</sub> |  |

# PERFORMANCE OF RESIDUAL SIGNAL CHANNEL AND A/D CONVERTER (input EEI, output RR2)

| Symbol | Parameter                    |       | Value |      |      |  |  |

|--------|------------------------------|-------|-------|------|------|--|--|

| Symbol | raiailletei                  | Min.  | Тур.  | Max. | Unit |  |  |

| Vin    | Input Voltage (peak to peak) |       |       | 5    | V    |  |  |

| Resh   | A/D Converter Resolution     |       |       | 12   | Bit  |  |  |

| LSB    | Analog Increment             |       | 1.2   |      | mV   |  |  |

| Eil    | Integral Linearity Error     | - 16  |       | 16   | LSB  |  |  |

| Edl    | Differential Linearity Error | - 0.7 |       | 0.7  | LSB  |  |  |

| Vos    | Offset Voltage               | - 100 |       | 100  | LSB  |  |  |

# AGC AMPLIFIER AND A/D CONVERTER (input AGC1, output RR1)

| Symbol   | Parameter                                                                                                                                 |              | 11-:4 |      |                   |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------|------|-------------------|

| Oyiiib0i |                                                                                                                                           | Min.         | Typ.  | Max. | Unit              |

| Grel     | Relative Gain to Programmed Gain $0 \text{ dB} \leq \text{AGC} \leq 24 \text{ dB}$ $25.5 \text{ dB} \leq \text{AGC} \leq 46.5 \text{ dB}$ | - 0.5<br>- 1 |       | 0.5  | dB<br>dB          |

| Vos      | Offset Voltage                                                                                                                            | - 70         |       | 70   | LSB               |

| N        | Equivalent RMS Noise<br>(AGC gain = 0 dB, RAI, LEI, EEI tied to AGND)                                                                     |              |       | 1.2  | mV <sub>eff</sub> |

# CARRIER LEVEL DETECTOR (input AGC1, output CDR)

| Cumbal          | D                                                                                                                                      |                   | Value |             |                |  |  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------|-------------|----------------|--|--|

| Symbol          | Parameter                                                                                                                              | Min.              | Тур.  | Max.        | Unit           |  |  |

| Trel            | Relative Threshold to Programmed Threshold                                                                                             | -1                |       | 1           | dB             |  |  |

| Hyst            | Hysteresis                                                                                                                             | 2                 |       | 3           | dB             |  |  |

| Vos             | Input Offset Voltage<br>1st Threshold Pair<br>2nd Threshold pair<br>3rd Threshold Pair                                                 | - 1<br>- 2<br>- 3 |       | 1<br>2<br>3 | mV<br>mV<br>mV |  |  |

| T <sub>dd</sub> | Detection Delay Time 0 mV <sub>eff</sub> to 775 mV <sub>eff</sub> Transition or 775 mV <sub>eff</sub> to 0 V <sub>eff</sub> Transition | 1                 |       | 3           | ms             |  |  |

### **APPLICATIONS INFORMATIONS**

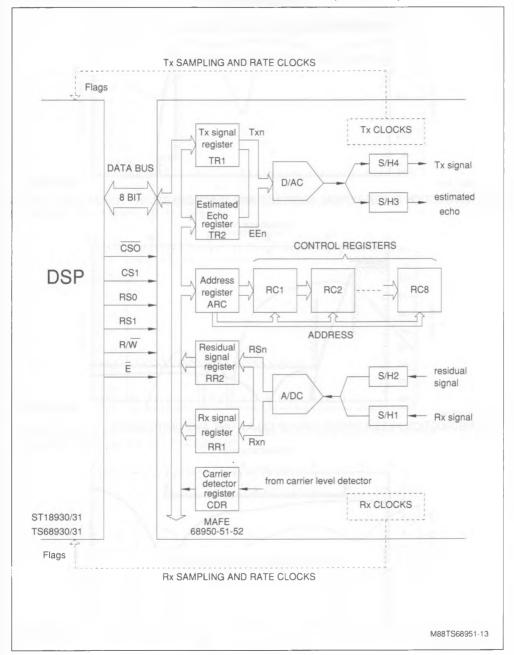

Figure 2: Modem Analog Front-end Chip Set.

Notes: 1...... Digital ground.

... Analog ground

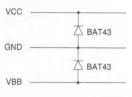

In some cases, external-user circuitry may induces power-up sequency latch-up problems that can be efficiently avoided by using BAT43 schottky small signal diodes as follow:

Figure 3: Four-wire or Two-wire Half Duplex and Two-wire Band-split Analog Signal Treatment.

Figure 4: Two-wire Echo Cancelling Analog Signal Treatment.

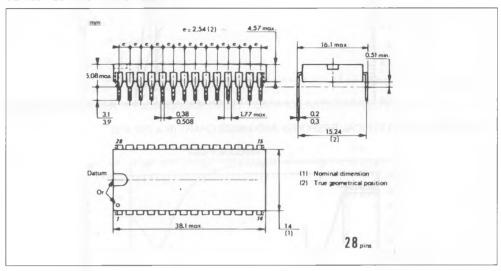

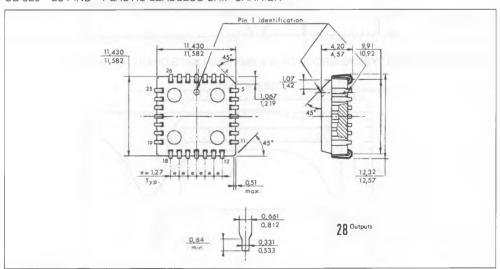

### ORDERING INFORMATION

| Part Number | Temperature<br>Range | Package |

|-------------|----------------------|---------|

| TS68951CP   | 0 to + 70 °C         | DIP 28  |

| TS68951CFN  | 0 to + 70 °C         | PLCC 28 |

### PACKAGE MECHANICAL DATA

CB-132 - 28 PINS - PLASTIC DIP

### CB-520 - 28 PINS - PLASTIC LEADLESS CHIP CARRIER

Rx LOW-PASS FILTER TYPICAL RESPONSE AND LIMITS CHART (fs = 288 kHz).

M88TS68951-09

Rx LOW-PASS FILTER TYPICAL RESPONSE AND LIMITS CHART (fs = 288 kHz).

M88TS68951-10

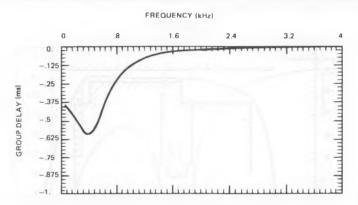

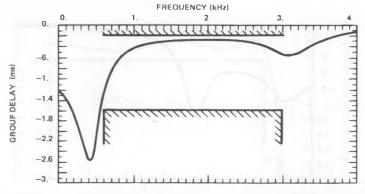

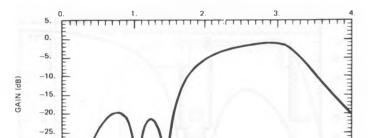

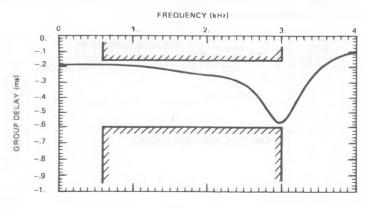

Rx LOW-PASS FILTER TYPICAL GROUP DELAY TIME AND LIMITS CHART (fs = 288 kHz).

Rx HIGH-PASS FILTER TYPICAL RESPONSE AND LIMITS CHART (Fs = 72 kHz).

M88TS68951-12

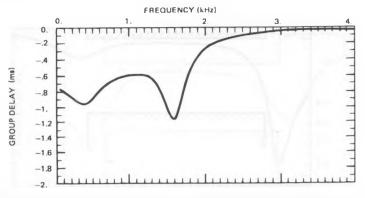

Rx HIGH-PASS FILTER TYPICAL GROUP DELAY TIME AND LIMITS CHART (Fs = 72 kHz).

M88TS68951-13

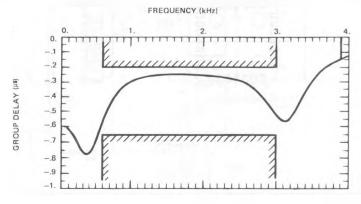

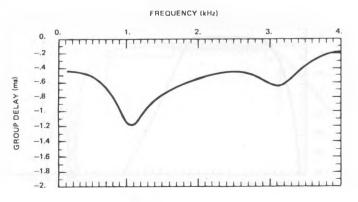

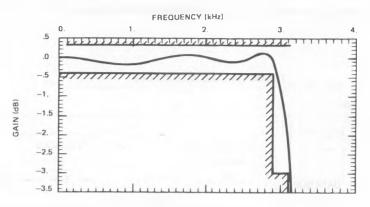

Rx BAND-PASS FILTER TYPICAL RESPONSE AND LIMITS CHART (HP: Fs = 72 kHz, LP: Fs = 288 kHz).

Rx BAND-PASS FILTER TYPICAL GROUP DELAY TIME AND LIMITS CHART (HP: Fs = 72 kHz, LP: Fs = 288 kHz).

FREQUENCY (kHz)

0. 1. 2. 3. 4.

-.1 -.2 -.3 -.4 -.4 -.5 -.6 -.6 -.7 -.8 -.9 -.1

M88TS68951-15

Rx BAND-PASS AND REJECTION FILTER TYPICAL RESPONSE AND LIMITS CHART (HP and REJ. : Fs = 72 kHz, LP : Fs = 288 kHz).

M88TS68951-16

Rx BAND-PASS AND REJECTION FILTER TYPICAL RESPONSE AND LIMITS CHART (HP and REJ. : Fs = 72 kHz, LP : Fs = 288 kHz).

Rx BAND-PASS AND REJECTION FILTER TYPICAL GROUP DELAY TIME AND LIMITS CHART (HP and REJ. : Fs = 72 kHz, LP : Fs = 288 kHz).

M88TS68951-18

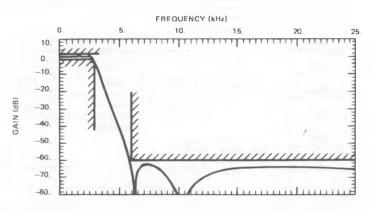

Rx HIGH-PASS AND REJECTION FILTER TYPICAL RESPONSE AND LIMITS CHART (Fs = 72 kHz).

M88TS68951-19

Rx BAND-PASS FILTER TYPICAL RESPONSE FOR V22 MODE (Low Channel) (HP : Fs = 72 kHz, LP : Fs = 144 kHz).

Rx BAND-PASS FILTER TYPICAL GROUP DELAY TIME FOR V.22 MODE (Low Channel) (HP: Fs = 72 kHz, LP: Fs = 144 kHz).

M88TS68951-21

Rx BAND-PASS FILTER TYPICAL RESPONSE FOR V.22 MODE (High Channel) (HP and REJ. : fs = 144 kHz, LP : fs = 288 kHz).

FREQUENCY (kHz)

M88TS68951-22

Rx BAND-PASS FILTER TYPICAL GROUP DELAY TIME FOR V.22 MODE (High Channel) (HP and REJ. : Fs = 144 kHz, LP : Fs = 288 kHz).

-30. -35.

RECONSTRUCTION FILTER TYPICAL RESPONSE AND LIMITS CHART.

M88TS68951-24

RECONSTRUCTION FILTER TYPICAL RESPONSE AND LIMITS CHART.

M88TS68951-25

RECONSTRUCTION FILTER TYPICAL GROUP DELAY TIME AND LIMITS CHART.

APPENDIX 2

INTERFACE BETWEEN DSP AND MODEM ANALOG FRONT-END (TS68950/1/2)

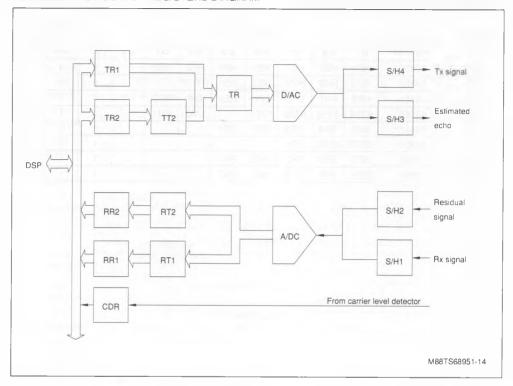

### DETAILED INPUT/OUTPUT REGISTERS DIAGRAM

|          | R/W | RS0 | RS1 | Register Accessed                 |

|----------|-----|-----|-----|-----------------------------------|

|          | 0   | 0   | 0   | TR1                               |

| Writing  | 0   | 0   | 1   | TR2                               |

| vvriting | 0   | 1   | 0   | ARC                               |

|          | 0   | 1   | 1   | Control Register Addressed by ARC |

|          | 1   | 0   | 0   | RR1                               |

| Reading  | 1   | 0   | 1   | RR2                               |

| ricading | 1   | 1   | 0   | CDR                               |

|          | 1   | 1   | 1   | Not Used                          |

# CONTROL REGISTERS PROGRAMMING

| Register<br>Name | Circuit<br>Including this | Register Content |      |      |      |      |      |     |    | Arc Content<br>(register address) |    |     |

|------------------|---------------------------|------------------|------|------|------|------|------|-----|----|-----------------------------------|----|-----|

|                  | Register                  | D7               | D6   | D5   | D4   | D3   | D2   | D1  | D0 | D7                                | D6 | D 5 |

| RC1              | 68952                     | HB4              | НВ3  | HB2  | HB1  | HR3  | HR2  | HR1 |    | 0                                 | 0  | 0   |

| RC2              | 68952                     | НМ3              | HM2  | HM1  | HS2  | HS1  | HTHR |     |    | 0                                 | 0  | 1   |

| RC3              | 68051                     | HP2              | HP1  | LP2  | LP1  | REJ  | S/A  | REC |    | 0                                 | 1  | 0   |

| RC4              | 68950                     | ATE4             | ATE3 | ATE2 | ATE1 |      | EM2  | EM1 |    | 0                                 | 1  | 1   |

| RC5              | 68951                     | GR5              | GR4  | GR3  | GR2  | GR1  |      |     |    | 1                                 | 0  | 0   |

| RC6              | 68951                     | GDS2             | GDS1 | HDS  |      |      |      |     |    | 1                                 | 0  | 1   |

| RC7              | 68952                     | SP5              | SP4  | SP3  | SP2  | SP1  |      |     |    | 1_                                | 1  | 0   |

| RC8              | 68952                     | MPE              | SPR  | AVRE | VAL  | INIT |      |     |    | 1                                 | 1  | 1   |

APPENDIX 5

PROGRESSION OF THE DIGITAL AND ANALOG SAMPLES IN THE MAFE

### **FURTHER REFERENCES**

### 1/MAFE CHARACTERIZATION REPORT

This report gives the results of the measurements performed on the TS68950-51-52 Modem Analog Front-End (MAFE) chip set.

Chapter 1 describes the configuration and the method used for these measurements.

Chapter 2 comments the results obtained on the two signal paths of the transmit (Tx) analog front-end TS68950. i.e the echo path and the Tx signal path. Similarly chapter 3 gives the results obtained on the echo path and the receive (Rx) signal path of the Rx analog front-end TS68951.

Performances obtained on the TS68951 when using plesiochronous clocks are given in chapter 4. In this case, the TS68952 clock generator delivers the main clock and the two sampling clocks to the Rx analog interface.

### 2/MAFE EVALUATION BOARD

The MAFE evaluation board is a complete unit for evaluation of the TS68950/51/52 MAFE chip set.

The MAFE evaluation board is equipped with the TS68950/51/52 chip set and a phone line interface facilities.

It can be directly connectable to an external Digital Signal Processor through a 50-pins connector or can be linked to the SGS-THOMSON family of digital signal processors emulation-evaluation tools. In this case, along with the software tools (MACROAS-SEMBLER, SIMULATOR and LINKER), it provides a ready-to-use Digital Signal Processor System Interface well adapted to the analog word and high speed modems development.

### 3/APPLICATION NOTE

This application note describes the development of Real-Time Algorithms using the SGS-THOMSON Digital Signal Processor TS68930 and the MAFE chip set.