# TS27C64AFN TS27C64AP

# 64K (8K×8) CMOS ONE TIME PROGRAMMABLE ROM

- COMPATIBLE TO TS27C64A EPROM (ELECTRICAL PARAMETERS, PROGRAMMING)

- PROGRAMMING VOLTAGE 12.5V

- HIGH SPEED PROGRAMMING

- 28-PIN JEDEC APPROVED PIN-OUT

- 32-PIN JEDEC APPROVED PIN-OUT (PLCC)

- IDEAL FOR AUTOMATIC INSERTION

#### DESCRIPTION

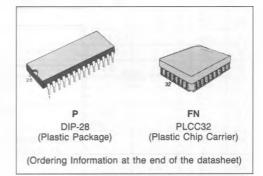

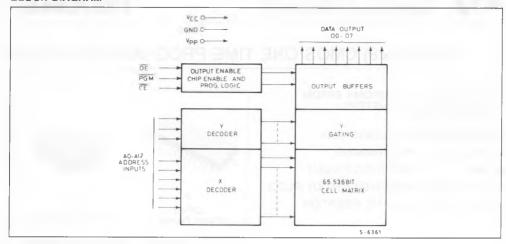

The TS27C64AP and TS27C64AFN are high speed 65,536-bit One Time Programmable (OTP) CMOS ROM ideally suited for applications where fast turnaround is an important requirement.

The TS27C64AP is packaged in a 28-pin dual-inline plastic package, the TS27C64AFN in a 32-pin PLCC plastic package and therefore can not be rewritten. Programming is performed according to standard SGS-THOMSON 64K EPROM procedure.

### PIN NAMES

| A0—A12                         | ADDRESS       |

|--------------------------------|---------------|

| CE                             | CHIP ENABLE   |

| ŌĒ                             | OUTPUT ENABLE |

| O <sub>0</sub> -O <sub>7</sub> | OUTPUTS       |

| PGM                            | PROGRAM       |

| NC                             | NON CONNECTED |

| DU                             | DO NOT USE    |

#### **BLOCK DIAGRAM**

#### ABSOLUTE MAXIMUM RATINGS(1)

| Symbol                         | Parameter                                                             | Value                                                                          | Unit |

|--------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------|------|

| T <sub>amb</sub>               | Operating temperature range<br>TS27C64A-C<br>TS27C64A-V<br>TS27C64A-T | T <sub>L</sub> to T <sub>H</sub><br>0 to + 70<br>- 40 to + 85<br>- 40 to + 105 | °C   |

| T <sub>stg</sub>               | Storage temperature range                                             | - 65 to + 125                                                                  | °C   |

| V <sub>PP</sub> <sup>(2)</sup> | Supply voltage                                                        | -0.6 to +14                                                                    | V    |

| V <sub>IN</sub> <sup>(2)</sup> | Input voltages A9 Except V <sub>PP</sub> , A9                         | - 0.6 to + 13.5<br>- 0.6 to + 6.25                                             | ٧    |

| PD                             | Max power dissipation                                                 | 1.5                                                                            | W    |

|                                | Lead temperature<br>(Soldering: 10 seconds)                           | + 300                                                                          | °C   |

Notes: 1. "Maximum ratings" are those values beyond which the safety of the device cannot be guaranteed. Except for "Operating temperature range" they are not meant to imply that the devices should be operated at these limits. The table of "Electrical characteristics" provides conditions for actual device operation.

2. With respect to GND.

#### **OPERATING MODES**

| MODE                    | CE              | ŌĒ              | A9                | PGM             | V <sub>PP</sub> | v <sub>cc</sub> | OUTPUTS          |

|-------------------------|-----------------|-----------------|-------------------|-----------------|-----------------|-----------------|------------------|

| READ                    | V <sub>IL</sub> | V <sub>IL</sub> | Х                 | V <sub>IH</sub> | V <sub>CC</sub> | Vcc             | D <sub>OUT</sub> |

| OUTPUT DISABLE          | VIL             | V <sub>IH</sub> | Х                 | V <sub>IH</sub> | Vcc             | Vcc             | Hi-Z             |

| STANDBY                 | V <sub>IH</sub> | Х               | X                 | Х               | Vcc             | Vcc             | Hi-Z             |

| HIGH SPEED PROGRAMMING  | V <sub>IL</sub> | V <sub>IH</sub> | Х                 | VIL             | V <sub>PP</sub> | V <sub>CC</sub> | D <sub>IN</sub>  |

| PROGRAM VERIFY          | $V_{IL}$        | V <sub>IL</sub> | Х                 | V <sub>IH</sub> | V <sub>PP</sub> | V <sub>CC</sub> | D <sub>OUT</sub> |

| PROGRAM INHIBIT         | V <sub>IH</sub> | Х               | Х                 | Х               | V <sub>PP</sub> | V <sub>CC</sub> | Hi-Z             |

| ELECTRONIC SIGNATURE(3) | VIL             | V <sub>IL</sub> | VH <sup>(2)</sup> | V <sub>IH</sub> | VCC             | V <sub>CC</sub> | CODE             |

Notes: 1. X can be either  $V_{IL}$  or  $V_{IH}$  — 2.  $V_{H}$  = 12 0V ± 0.5V 3. All address lines at  $V_{IL}$  except A9 and A0 that is toggled from  $V_{IL}$  (manufacturer code: 9B) to  $V_{IH}$  (type code: 08).

#### **READ OPERATION**

# DC CHARACTERISTICS ( $T_{amb} = T_L$ to $T_H$ , $V_{CC} = 5V \pm 10\%$ , GND = 0V; Unless otherwise specified)

|                    |                                                     | T                                                                                                |                              | Values  |                    | 11-14 |

|--------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------|---------|--------------------|-------|

| Symbol             | Parameter                                           | Test Conditions                                                                                  | Min.                         | Тур.(1) | Max.               | Unit  |

| ILI                | Input Load Current                                  | V <sub>IN</sub> = V <sub>CC</sub> or GND                                                         |                              |         | 10                 | μΑ    |

| ILO                | Output Leakage Current                              | V <sub>OUT</sub> = V <sub>CC</sub> or GND,<br>CE = V <sub>IH</sub>                               |                              |         | 10                 | μА    |

| V <sub>PP</sub>    | V <sub>PP</sub> Read Voltage                        |                                                                                                  | V <sub>CC</sub> - 0.7        |         | Vcc                | V     |

| V <sub>IL</sub>    | Input Low Voltage                                   |                                                                                                  | -0.1                         |         | 0.8                | V     |

| V <sub>IH</sub>    | Input High Voltage                                  |                                                                                                  | 2.0                          |         | V <sub>CC</sub> +1 | V     |

| V <sub>OL</sub>    | Output Low Voltage                                  | I <sub>OL</sub> = 2.1 mA<br>I <sub>OL</sub> = 0 μA                                               |                              |         | 0.45<br>0.1        | V     |

| V <sub>OH</sub>    | Output High Voltage                                 | I <sub>OH</sub> = - 400 μA<br>I <sub>OH</sub> = 0 μA                                             | 2.4<br>V <sub>CC</sub> - 0.1 |         |                    | ٧     |

| I <sub>CC2</sub>   | V <sub>CC</sub> Supply Active Current<br>TTL Levels | $\overline{CE} = \overline{OE} = V_{ L}$ , Inputs = $V_{ H}$ or $V_{ L}$ , f = 5 MHz, I/O = 0 mA |                              | 10      | 30                 | mA    |

| I <sub>CCSB1</sub> | V <sub>CC</sub> Supply Standby Current              | CE = V <sub>IH</sub>                                                                             |                              | 0.5     | 1                  | mA    |

| I <sub>CCSB2</sub> | V <sub>CC</sub> Supply Standby Current              | CE = V <sub>CC</sub>                                                                             |                              | 10      | 100                | μΑ    |

| I <sub>PP1</sub>   | V <sub>PP</sub> Read Current                        | $V_{PP} = V_{CC} = 5.5V$                                                                         |                              |         | 100                | μA    |

Note: 1. Typical conditions are for operation at: Tamb = +25°C, VCC = 5V, VPP = VCC, and VSS = 0V

# AC CHARACTERISTICS(1)(Tamb = TI to TH)

| Symbol                | Parameter                                                    | Test Conditions           | 27C64A<br>-15 |     | 27C64A<br>-20 |     | 27C64A<br>-25 |     | 27C64A<br>-30 |     | Unit |

|-----------------------|--------------------------------------------------------------|---------------------------|---------------|-----|---------------|-----|---------------|-----|---------------|-----|------|

|                       |                                                              |                           | Min           | Max | Min           | Max | Min           | Max | Min           | Max |      |

| tACC                  | Address to Output Delay                                      | CE = OE = VIL             |               | 150 |               | 200 |               | 250 |               | 300 | ns   |

| t <sub>CE</sub>       | CE to Output Delay                                           | OE = V <sub>IL</sub>      |               | 150 |               | 200 |               | 250 |               | 300 | ns   |

| tOE                   | Output Enable to<br>Output Delay                             | CE = V <sub>IL</sub>      |               | 75  |               | 80  |               | 100 |               | 120 | ns   |

| t <sub>DF</sub> (2,4) | OE or CE High to                                             | CE = V <sub>IL</sub>      | 0             | 50  | 0             | 50  | 0             | 60  | 0             | 105 | ns   |

| tон                   | Output Hold from addresses, CE or OE whichever occured first | CE = OE = V <sub>IL</sub> | 0             |     | 0             |     | 0             |     | 0             |     | ns   |

# CAPACITANCE Tamb = +25°C, f = 1 MHz (Note 3)

|        | 641116             | · ·                   |      |      |      |      |

|--------|--------------------|-----------------------|------|------|------|------|

| Symbol | Parameter          | Test Conditions       | Min. | Тур. | Max. | Unit |

| Cin    | Input Capacitance  | V <sub>IN</sub> = 0V  |      | 4    | 6    | pF   |

| Cout   | Output Capacitance | V <sub>OUT</sub> = 0V |      | 8    | 12   | pF   |

Notes: 1. V<sub>CC</sub> must be applied at the same time or before Vpp and removed after or at the same time as Vpp+Vpp may be connected to V<sub>CC</sub> except during program.

2. The tpc compare level is determined as follows:

High to THREE-STATE, the measured V<sub>OH</sub>(DC) = 0.1V

Low to THREE-STATE the measured VOL(DC) +0.1V

3. Capacitance is guaranteed By periodic testing. T<sub>amb</sub> = +25°C, f=1MHz.

4. T<sub>DF</sub>, is specified from OE or CE whichever occurs first. This parameter is only sampled and not 100% tested.

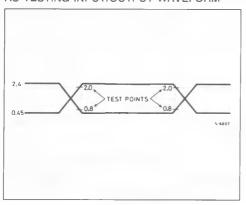

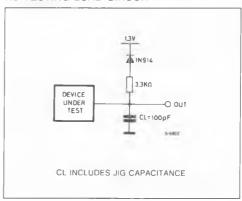

#### **AC TEST CONDITIONS**

Output Load: 1 TTL gate and CL = 100 pF Input Rise and Fall Times Input pulse levels: 0.45V to 2.4V

Timing Measurement Reference Level

Inputs, Outputs 0.8V and 2V

#### AC TESTING INPUT/OUTPUT WAVEFORM

#### AC TESTING LOAD CIRCUIT

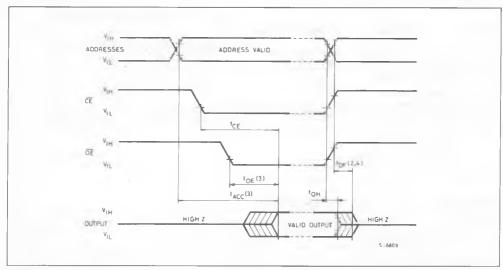

### AC WAVEFORMS

#### Notes:

- 1. Typical values are for T<sub>amb</sub> = 25°C and nominal supply voltage

2. This parameter is only sampled and not 100% tested.

3. OE may be delayed up to tacc tog after the falling edge CE without impact on tacc

4. togsis specified form OE or CE whichever occurs first.

#### **DEVICE OPERATION**

The seven modes of operation of the TS27C64A are listed in the Operating Modes table. A single 5V power supply is required in the read mode. All inputs are TTL levels except for V<sub>DD</sub>.

#### READ MODE

The TS27C64A has two control functions, both of wich must be logically active in order to obtain data at the outputs. Chip Enable (CE) is the power control and should be used for device selection. Output Enable (OE) is the output control and should be used to gate data to the output pins, independent of device selection. Assuming that addresses are stable, address access time (t<sub>ACC</sub>) is equal to the delay from CE to Output (t<sub>CE</sub>). Data is available at the outputs after a delay of t<sub>OE</sub> from the falling edge of OE, assuming that CE has been low and addresses have been stable for at least t<sub>ACC</sub>-t<sub>OE</sub>.

#### STANDBY MODE

The TS27C64A has a standby mode which reduces the maximum power dissipation to 5.5 mW. The TS27C64A is placed in the standby mode by applying a TTL high signal to the CE input. When in standby mode, the outputs are in a high impedance state, independent of the OE input.

#### **OUTPUT OR-TYING**

Because OTPs are usually used in larger memory arrays, we have provided two control lines which accomodate this multiple memory connection. The two control lines allow for:

- a) the lowest possible memory power dissipation, and

- b) complete assurance that output bus contention will not occur.

To use these control lines most efficiently, CE should be decoded and used as the primary device selecting function, while OE should be made a common connection to all devices in the array and connected to the READ line from the system control bus. This assures that all deselected memory devices are in their low power standby modes and that the output pins are active only when data is desired from a particular memory device.

#### **PROGRAMMING**

Caution: Exceeding 14V on  $V_{pp}$  pin will damage the TS27C64A.

Initially, all bits of the TS27C64A are in the "1" state. Data is introduced by selectively programming "0s" into the desired bit locations. Although only "0s" will be programmed, both "1s" and "0s" can be presented in the data word.

The TS27C64A is in the programming mode when the  $V_{pp}$  input is at 12.5 V and  $\overline{CE}$  and  $\overline{PGM}$  are both at TTL Low. It is required that a 0.1  $\mu F$  capacitor be placed across  $V_{pp}$ ,  $V_{CC}$  and ground to suppress spurious voltage transients which may damage the device. The data to be programmed is applied 8 bits in parallel to the data output pins. The levels required for the address and data inputs are TTL.

Programming of multiple TS27C64As in parallel with the same data can be easily accomplished due to the simplicity of the programming requirements. Like inputs of the parallel TS27C64As may be connected together when they are programmed with the same data. A low level TTL pulse applied to the PGM input programs the paralleled TS27C64As.

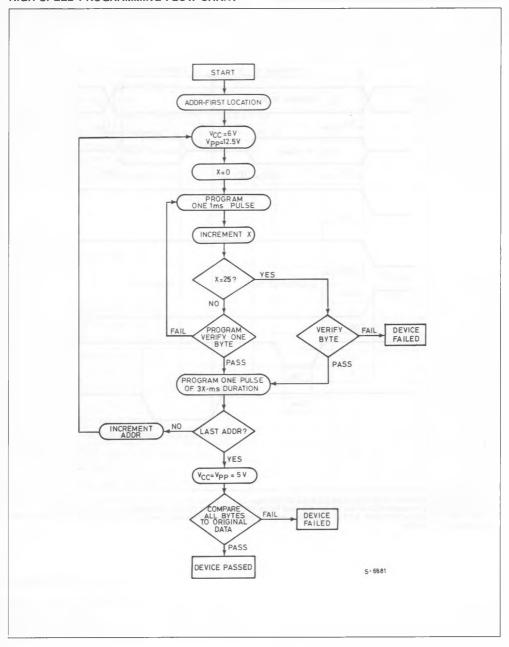

#### HIGH SPEED PROGRAMMING

The high speed programming algorithm described in the flow chart rapidly programs TS27C64A using an efficient and reliable method particularly suited to the production programming environment. Typical programming times for individual devices are on the order of 1 minute.

#### PROGRAM INHIBIT

Programming of multiple TS27C64As in parallel with different data is also easily accomplished by using the program inhibit mode. A high level on CE or PGM inputs inhibits the other TS27C64As from from being programmed. Except for CE, all like inputs (including OE) of the parallel TS27C64As may be common. A TTL low-level pulse applied to a TS27C64A CE and PGM inputs with Vpp at 12.5 V will program that TS27C64A.

#### PROGRAM VERIFY

A verify may be performed on the programmed bits to determine that they were correctly programmed.  $\frac{\text{The verify is performed with CE}}{\text{PGM at V}_{\text{IH}}} \text{ and V}_{\text{DD}} \text{ at 12.5 V}.$

### **ELECTRONIC SIGNATURE MODE**

Electronic signature mode allows the reading out of a binary code that will indentify the EPROM manufacturer and type. This mode is intended for use by programming equipment for the purpose of automatically matching the device to be programmed with its corresponding programming algorithm. This mode is functional in the  $25^{\circ}\text{C} \pm 5^{\circ}\text{C}$  ambient temperature range that is required when programming the TS27C64A. To activate this mode the programming equipment must force 11.5V to 12.5V on address line A9 of the TS27C64A. Two bytes may then be sequenced from the device outputs by toggling address line A0 from VIL to VIH. All other address lines must be held at VIL during electonic signature mode.

## **PROGRAMMING OPERATIONS**(1)( $T_{amb} = 25 \pm 5^{\circ}C$ , $V_{CC} = 6.0V \pm 0.25V$ , $V_{PP} = 12.5V \pm 0.3V$ )

#### DC AND OPERATING CHARACTERISTICS

| Symbol           | Parameter                                            | Test Conditions                                     |       | Unit |                    |      |

|------------------|------------------------------------------------------|-----------------------------------------------------|-------|------|--------------------|------|

|                  |                                                      | rest Conditions                                     | Min.  | Тур. | Max.               | Unit |

| I <sub>I</sub>   | Input Current (all inputs)                           | V <sub>I</sub> = V <sub>IL</sub> or V <sub>IH</sub> |       |      | 10                 | μА   |

| $V_{IL}$         | Input Low Level (all inputs)                         |                                                     | - 0.1 |      | 0.8                | V    |

| $V_{IH}$         | Input High Level                                     |                                                     | 2.0   |      | V <sub>CC</sub> +1 | V    |

| V <sub>OL</sub>  | Output low voltage during verify                     | I <sub>OL</sub> = 2.1 mA                            |       |      | 0.45               | V    |

| V <sub>OH</sub>  | Output high voltage during verify                    | $I_{OH} = -400 \ \mu A$                             | 2.4   |      |                    | V    |

| ICC3             | V <sub>CC</sub> Supply current<br>(Program & Verify) |                                                     |       |      | 30                 | mA   |

| I <sub>PP2</sub> | V <sub>PP</sub> supply current (Program)             | CE = V <sub>IL</sub> = PGM                          | -     |      | 30                 | mA   |

#### AC CHARACTERISTICS

| Symbol              | Parameter                           | Test Conditions |      | 11-:4 |       |      |

|---------------------|-------------------------------------|-----------------|------|-------|-------|------|

| Symbol              | Parameter                           | rest Conditions | Min. | Тур.  | Max.  | Unit |

| t <sub>AS</sub>     | Address Set-up Time                 |                 | 2    |       |       | μS   |

| toes                | OE Set-up Time                      |                 | 2    |       |       | μS   |

| t <sub>DS</sub>     | Data Set-up Time                    |                 | 2    |       |       | μS   |

| t <sub>AH</sub>     | Address Hold Time                   |                 | 0    |       |       | μS   |

| t <sub>DH</sub>     | Data Hold Time                      |                 | 2    |       |       | μS   |

| t <sub>DFP</sub>    | Output enable to output float delay |                 | 0    |       | 130   | ns   |

| t <sub>VPS</sub>    | V <sub>PP</sub> set-up time         |                 | 2    |       |       | μS   |

| t <sub>VCS</sub>    | V <sub>CC</sub> set-up time         |                 | 2    |       |       | μS   |

| tpw                 | PGM initial program pulse width     |                 | 0.95 | 1.0   | 1.05  | ms   |

| topw <sup>(2)</sup> | PGM overprogram pulse width         |                 | 2.85 |       | 78.75 | ms   |

| tCES                | CE set-up time                      |                 | 2    |       |       | μS   |

| toE                 | Data valid from OE                  |                 |      |       | 150   | ns   |

Notes: 1.  $V_{CC}$  must be applied simultaneously or before  $V_{PP}$  and removed simultaneously or after  $V_{PP}$ . 2.  $t_{OPW}$  is defined in flow chart.

#### **AC TEST CONDITIONS**

Input rise and fall times (10% to 90%) 20ns

Input pulse levels 0.45V to 2.4V

Input timing reference level 0.8V and 2.0V

Output timing reference level 0.8V and 2.0V

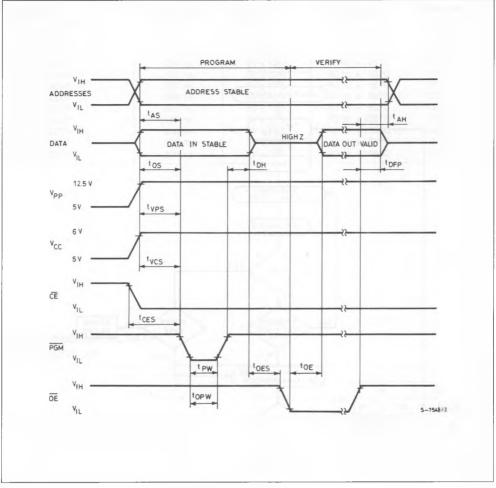

#### HIGH SPEED PROGRAMMING WAVEFORMS

The input timing reference level is 0.8V for V<sub>IL</sub> and 2.0V for V<sub>IH</sub>.

top and topp are characteristics of the device but must be be accommodated by the programmer

When programming the TS27C64A, a 0.1 µF capacitor is required across Vpp and ground to suppress spurious voltage transiens which can damage the device.

#### HIGH SPEED PROGRAMMING FLOW CHART

### **ORDERING INFORMATION (TS27C64AP)**

| Part Number   | Access Time | Supply Voltage | Temp. Range     | Package |  |

|---------------|-------------|----------------|-----------------|---------|--|

| TS27C64A-15CP | 150 ns      | 5V ± 10%       | 0 to + 70°C     | DIP-28  |  |

| TS27C64A-20CP | 200 ns      | 5V ± 10%       | 0 to + 70°C     | DIP-28  |  |

| TS27C64A-25CP | 250 ns      | 5V ± 10%       | 0 to + 70°C     | DIP-28  |  |

| TS27C64A-30CP | 300 ns      | 5V ± 10%       | 0 to + 70°C     | DIP-28  |  |

| TS27C64A-15VP | 150 ns      | 5V ± 10%       | -40 to + 85°C   | DIP-28  |  |

| TS27C64A-20VP | 200 ns      | 5V ± 10%       | -40 to + 85°C   | DIP-28  |  |

| TS27C64A-25VP | 250 ns      | 5V ± 10%       | -40 to + 85°C   | DIP-28  |  |

| TS27C64A-30VP | 300 ns      | 5V ± 10%       | -40 to + 85°C   | DIP-28  |  |

| TS27C64A-15TP | 150 ns      | 5V ± 10%       | -40 to +105°C   | DIP-28  |  |

| TS27C64A-20TP | 200 ns      | 5V ± 10%       | -40 to +105°C   | DIP-28  |  |

| TS27C64A-25TP | 250 ns      | 5V ± 10%       | -40 to +105°C   | DIP-28  |  |

| TS27C64A-30TP | 300 ns      | 5V ± 10%       | - 40 to + 105°C | DIP-28  |  |

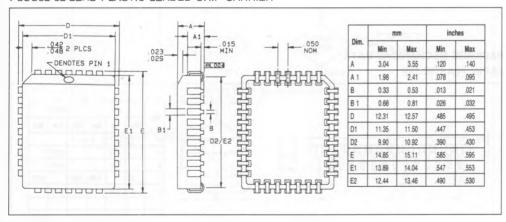

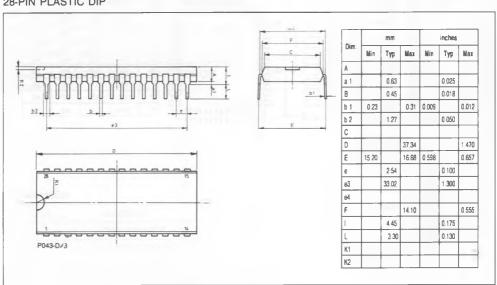

## PACKAGE MECHANICAL DATA

28-PIN PLASTIC DIP

### **ORDERING INFORMATION (TS27C64AFN)**

| Part Number    | Access Time | Supply Voltage | Temp. Range     | Package |  |

|----------------|-------------|----------------|-----------------|---------|--|

| TS27C64A-15CFN | 150 ns      | 5V ± 10%       | 0 to + 70°C     | PLCC32  |  |

| TS27C64A-20CFN | 200 ns      | 5V ± 10%       | 0 to + 70°C     | PLCC32  |  |

| TS27C64A-25CFN | 250 ns      | 5V ± 10%       | 0 to + 70°C     | PLCC32  |  |

| TS27C64A-30CFN | 300 ns      | 5V ± 10%       | 0 to + 70°C     | PLCC32  |  |

| TS27C64A-15VFN | 150 ns      | 5V ± 10%       | -40 to + 85°C   | PLCC32  |  |

| TS27C64A-20VFN | 200 ns      | 5V ± 10%       | -40 to + 85°C   | PLCC32  |  |

| TS27C64A-25VFN | 250 ns      | 5V ± 10%       | -40 to + 85°C   | PLCC32  |  |

| TS27C64A-30VFN | 300 ns      | 5V ± 10%       | -40 to + 85°C   | PLCC32  |  |

| TS27C64A-15TFN | 150 ns      | 5V ± 10%       | - 40 to + 105°C | PLCC32  |  |

| TS27C64A-20TFN | 200 ns      | 5V ± 10%       | - 40 to + 105°C | PLCC32  |  |

| TS27C64A-25TFN | 250 ns      | 5V ± 10%       | - 40 to + 105°C | PLCC32  |  |

| TS27C64A-30TFN | 300 ns      | 5V ± 10%       | - 40 to + 105°C | PLCC32  |  |

#### PACKAGE MECHANICAL DATA

PLCC32 32-LEAD PLASTIC LEADED CHIP CARRIER