# Signetics

# TDA1541A Dual 16-Bit Digital-to-Analog Converter

**Product Specification**

### Linear Products

### DESCRIPTION

The TDA1541A is a monolithic integrated dual 16-bit digital-to-analog converter (DAC) designed for use in hi-fi digital audio equipment such as compact disc players, digital tape, or cassette recorders.

### **FEATURES**

- Selectable input format: offset binary or two's complement

- Internal timing and control circuit

- TTL-compatible digital inputs

- High maximum input bit rate and fast settling time

- 6Mbits/s data rate

- Low linearity error (½ LSB typ.)

- Fast settling (1μs typ.)

# **APPLICATIONS**

- Compact disc players

- Digital audio tape, and cassette recorders and players

- Waveform generation

# ORDERING INFORMATION

| DESCRIPTION        | TEMPERATURE RANGE | ORDER CODE |

|--------------------|-------------------|------------|

| 28-Pin Plastic DIP | -20°C to +70°C    | TDA1541AN  |

# ABSOLUTE MAXIMUM RATINGS

| SYMBOL           | PARAMETER                           | RATING         | UNIT |

|------------------|-------------------------------------|----------------|------|

|                  | Supply voltage ranges               |                |      |

| V <sub>DD</sub>  | Pin 28                              | + 7            | V    |

| V <sub>DD1</sub> | Pin 26                              | -7             | V    |

| $V_{DD2}$        | Pin 15                              | -17            | V    |

| TJ               | Junction temperature range          | -55 to +150    | °C   |

| T <sub>STG</sub> | Storage temperature range           | -65 to +150    | °C   |

| TA               | Operating ambient temperature range | -40 to +85     | °C   |

| V <sub>ES</sub>  | Electrostatic handling <sup>1</sup> | -1000 to +1000 | ٧    |

### NOTE:

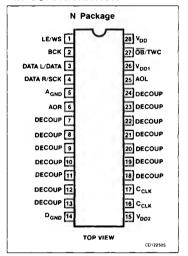

### PIN CONFIGURATION

<sup>1.</sup> Discharging a 250pF capacitor through a  $1k\Omega$  series resistor.

# **TDA1541A**

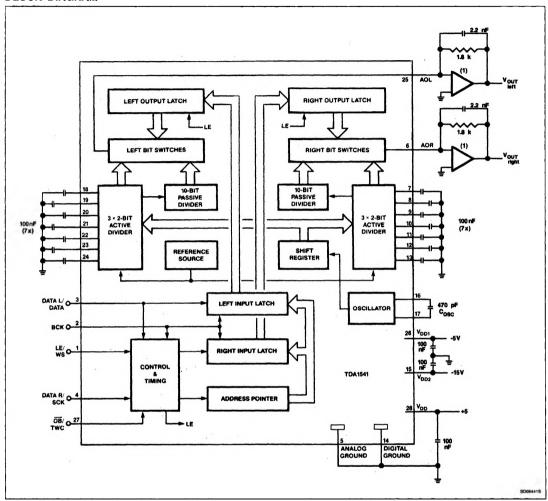

# **BLOCK DIAGRAM**

TDA1541A

DC AND AC ELECTRICAL CHARACTERISTICS  $V_{DD} = +5V$ ;  $V_{DD1} = -5V$ ;  $V_{DD2} = -15V$ ;  $T_A = +25$ °C; measured in Figure 1, unless otherwise specified.

|                         |                                                                                | LIMITS   |                          |      |        |

|-------------------------|--------------------------------------------------------------------------------|----------|--------------------------|------|--------|

| SYMBOL                  | PARAMETER                                                                      | Min      | Тур                      | Max  | UNIT   |

| Supply                  |                                                                                |          |                          |      |        |

|                         | Supply voltage ranges                                                          |          |                          |      | 1      |

| $V_{DD}$                | Pin 28                                                                         | 4.5      | 5.0                      | 5.5  | \ \ \  |

| -V <sub>DD1</sub>       | Pin 26                                                                         | 4.5      | 5.0                      | 5.5  | V      |

| -V <sub>DD2</sub>       | Pin 15                                                                         | 14       | 15                       | 16   | V      |

|                         | Supply currents                                                                | 1        |                          |      |        |

| IDD                     | Pin 28                                                                         | - 1      | 27                       | 40   | mA.    |

| - JDD1                  | Pin 26                                                                         | 1        | 37                       | 50   | mA     |

| ~1DD2                   | Pin 15                                                                         |          | 25                       | 35   | mA     |

|                         | Resolution                                                                     |          | 16                       |      | bits   |

|                         | Voltage difference between analog and digital ground                           | ~0.3     |                          | +0.3 | V      |

| Inputs                  |                                                                                |          |                          |      |        |

|                         | Input current (Pins 1, 2, 3 and 4)                                             |          |                          |      |        |

| h.                      | digital inputs LOW ( < 0.8V)                                                   |          |                          | 0.4  | mA     |

| ин                      | digital inputs HIGH ( > 2.0V)                                                  |          |                          | 20   | μΑ     |

| 11 00 (Turol            | Digital input current (Pin 27)                                                 |          |                          |      | ١      |

| OB/TWC                  | +5V                                                                            |          |                          | 1    | μΑ     |

| OB/TWC <br>   OB/TWC    | 0V                                                                             |          |                          | 20   | μΑ     |

| II OB/TWC               | -5V                                                                            |          |                          | 40   | μΑ     |

| face                    | Input frequency at clock input (Pin 2)                                         |          |                          | 0.4  | MHz    |

| f <sub>BCK</sub>        | at data inputs (Pin 3 and Pin 4)                                               |          | ì                        | 0.4  | MHz    |

| f <sub>DAT</sub><br>fws | at word select input (Pin 1)                                                   |          | -                        | 200  | kHz    |

| fLE                     | at latch enable Pin 1                                                          | ľ        |                          | 200  | kHz    |

| Cı                      | Input capacitance of digital inputs                                            |          | 12                       |      | pF     |

| Oscillator              | <u> </u>                                                                       |          |                          |      |        |

| fosc                    | Oscillator frequency C <sub>OSC</sub> = 470pF                                  | 150      | 200                      | 275  | kHz    |

|                         | ts (AOL; AOR)                                                                  | <u> </u> | L                        |      | L      |

| V <sub>OC</sub>         | Output voltage compliance                                                      |          |                          |      | mV     |

| l <sub>FS</sub>         | Full-scale current                                                             | 3.4      | 4.0                      | 4.6  | mA     |

| ± Izs                   | Zero-scale current                                                             | -        | 25                       | 50   | mA     |

| TC <sub>FS</sub>        | Full-scale temperature coefficient $T_A = -20 \text{ to } +85^{\circ}\text{C}$ |          | ± 200 × 10 <sup>-6</sup> |      | ppm/°( |

|                         | Linearity error integral                                                       | -        |                          |      | 1      |

| EL                      | at T <sub>A</sub> = 25°C                                                       |          | 0.5                      | 1.0  | LSB    |

| EL                      | at $T_A = -20 \text{ to } +85^{\circ}\text{C}$                                 |          |                          | 1.0  | LSB    |

|                         | Linearity error differential                                                   |          |                          |      |        |

| E <sub>DL</sub>         | at T <sub>A</sub> = 25°C                                                       | 1        | 0.5                      | 1.0  | LSB    |

| EDL                     | at T <sub>A</sub> = -20 to +85°C                                               |          |                          | 1.0  | LSB    |

| THD                     | Total harmonic distortion                                                      |          | -100                     |      | dB     |

| S/N                     | Signal-to-noise ratio + THD <sup>2</sup>                                       | 90       | 95                       |      | dB     |

| tcs                     | Settling time to ± 1 LSB                                                       |          | 0.5                      |      | μs     |

**TDA1541A**

DC AND AC ELECTRICAL CHARACTERISTICS (Continued) V<sub>DD</sub> = +5V; V<sub>DD1</sub> = -5V; V<sub>DD2</sub> = -15V; T<sub>A</sub> = +25°C; measured in Figure 1, unless otherwise specified.

| SYMBOL               |                                                                                              |     | LIMITS            |     |                |

|----------------------|----------------------------------------------------------------------------------------------|-----|-------------------|-----|----------------|

|                      | PARAMETER                                                                                    | Min | Тур               | Max | UNIT           |

| α                    | Channel separation                                                                           | 80  | 98                |     | dB             |

| $\Delta I_{FS}$      | Unbalance between outputs                                                                    |     | 0.1               | 0.3 | dB             |

| t <sub>D</sub>       | Time delay between outputs                                                                   |     |                   | 0.2 | μs             |

| SVRR<br>SVRR<br>SVRR | Supply voltage ripple rejection <sup>3</sup> $V_{DD} = +5V$ $V_{DD1} = -5V$ $V_{DD2} = -15V$ |     | -76<br>-84<br>-58 |     | dB<br>dB<br>dB |

| S/N                  | Signal-to-noise ratio<br>at bipolar zero<br>at full scale                                    | 98  | 110<br>104        |     | dB<br>dB       |

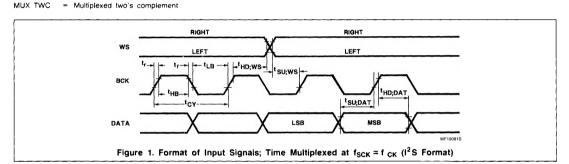

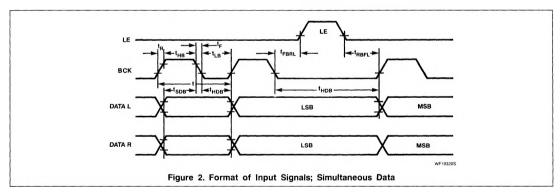

| Timing (see Fi       | gures 2, 3, and 4)                                                                           |     |                   |     |                |

| t <sub>R</sub>       | Rise time                                                                                    |     |                   | 32  | ns             |

| t <sub>F</sub>       | Fall time                                                                                    |     |                   | 32  | ns             |

| t <sub>CY</sub>      | Bit clock cycle time                                                                         | 156 |                   |     | ns             |

| t <sub>HB</sub>      | Bit clock High time                                                                          | 46  |                   |     | ns             |

| t <sub>LB</sub>      | Bit clock Low time                                                                           | 46  |                   |     | ns             |

| t <sub>FBRL</sub>    | Bit clock fall time to latch rise time                                                       | 0   |                   |     | ns             |

| t <sub>RBFL</sub>    | Bit clock rise time to latch fall time                                                       | 0   |                   |     | ns             |

| t <sub>SDB</sub>     | Data setup time to bit clock                                                                 | 32  |                   |     | ns             |

| t <sub>HDB</sub>     | Data hold time to bit clock                                                                  | 0   |                   |     | ns             |

| t <sub>SDS</sub>     | Data setup time to system clock                                                              | 32  |                   |     | ns             |

| t <sub>HWS</sub>     | Word select hold time to system clock                                                        | 0   |                   |     | ns             |

| tsws                 | Word select setup time to system clock                                                       | 32  |                   |     | ns             |

## NOTES:

- To ensure no performance losses, permitted output voltage compliance is ± 25mV maximum.

- 2. Signal-to-noise ratio + THD with 1kHz full-scale sine wave generated at a sampling rate of 176.4kHz.

- 3. VRIPPLE = 100mV and fRIPPLE = 100Hz.

# **FUNCTIONAL DESCRIPTION**

The TDA1541A accepts input sample formats in time multiplexed mode or simultaneous mode with any bit length. The most significant bit (MSB) must always be first. This flexible input data format allows easy interfacing with signal processing chips such as interpolation filters, error correction circuits, pulse code modulation adaptors and audio signal processors (ASP).

The high maximum input bit rate and fast settling time facilitates application in  $4\times$  oversampling systems (44.1kHz to 176.4kHz or 48kHz to 192kHz) with the associated simple

analog filtering function (low-order, linear phase filter).

# Input Data Selection

# (See also Table 1)

With input OB/TWC connected to ground, data input (offset binary format) must be in time multiplexed mode. It is accompanied with a word select (WS) and a bit clock input (BCK) signal. A separate system clock input (SCK) is provided for accurate, jitter-free timing of the analog outputs AOL and AOR.

With  $\overline{\text{OB}}/\text{TWC}$  connected to  $V_{DD}$ , the mode is the same, but data format must be in two's complement.

When input  $\overline{OB}/TWC$  is connected to  $(V_{DD1})$  the two channels of data (L/R) are input simultaneously via  $(DATA\ L)$  and  $(DATA\ R)$ , accompanied by BCK and a latch-enable input (LE). With this mode selected, the data must be in offset binary.

The format of data input signals is shown in Figures 2, 3, and 4.

True 16-bit performance is achieved by each channel using three 2-bit active dividers, operating on the dynamic element matching principle, in combination with a 10-bit passive current-divider, based on emitter scaling. All digital inputs are TTL-compatible.

TDA1541A

Table 1. Input Data Selection

| OB/TWC | MODE         | PIN 1 | PIN 2 | PIN 3    | PIN 4    |

|--------|--------------|-------|-------|----------|----------|

| -5V    | Simultaneous | LE    | BCK   | DATA L   | DATA R   |

| 0V     | Time MUX OB  | ws    | BCK   | DATA OB  | NOT USED |

| +5V    | Time MUX TWC | ws    | BCK   | DATA TWC | NOT USED |

Where:

LE = Latch enable ws = Word select вск Bit clock DATA L Data left DATA R Data right DATA OB Data offset binary DATA TWC Data two's complement Multiplexed offset binary MUX OB