TOSHIBA TC90A13N/F

TOSHIBA CMOS DIGITAL INTEGRATED CIRCUIT SILICON MONOLITHIC

# TC90A13N, TC90A13F

# 3 LINE DIGITAL Y/C SEPARATION IC

The TC90A13N and TC90A13F separate luminance (Y) and chrominance (C) signals from an NTSC composite video signal. It employs the Toshiba original logical comb filter to realize high performance Y/C separation at low cost.

## **FEATURES**

- NTSC system

- PLL 4X multiplication circuit

- Sync. tip clampping circuit

- 8bit A/D converter

- 8bit D/A converters (2ch)

- 2H line memory

- Dynamic comb filter

- 1 line dot correction circuit

- Vertical enhancer

- Color killer mode (Y/C separation OFF)

- Chrominance wide band output mode

- SDIP28/SOP28 package

- 5V single power supply

Weight SDIP28-P-400-1.78 : 1.7g (Typ.) SOP28-P-450-1.27 : 0.8g (Typ.)

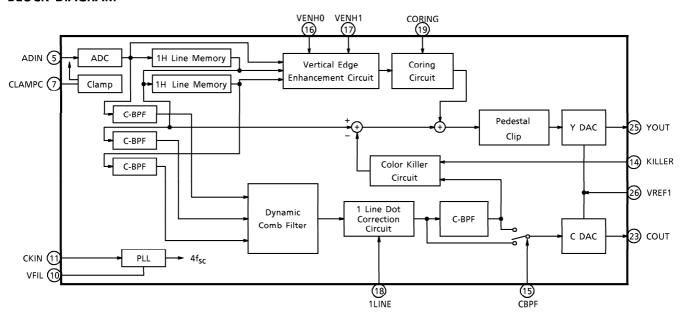

## **BLOCK DIAGRAM**

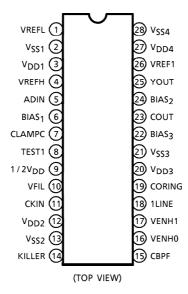

## **TERMINAL CONNECTION DIAGRAM**

# **TERMINAL FUNCTION**

| PIN<br>No. | NAME               | FUNCTION                | PIN<br>No. | NAME              | FUNCTION                                                      |

|------------|--------------------|-------------------------|------------|-------------------|---------------------------------------------------------------|

| 1          | VREFL              | Bias for ADC            | 15         | CBPF              | L : C-BPF = WIDE, H : NARROW                                  |

| 2          | V <sub>SS1</sub>   | GND for ADC             | 16         | VENH0             | Vertical edge enhanced level<br>(VENH0, VENH1) = (L, L) = OFF |

| 3          | V <sub>DD1</sub>   | V <sub>DD</sub> for ADC | 17         | VENH1             | (H, L) = Low (L, H) = MID,<br>(H, H) = High                   |

| 4          | VREFH              | Bias for ADC            | 18         | 1LINE             | L : 1 line color ON<br>H : 1 line color OFF                   |

| 5          | ADIN               | Video input             | 19         | CORING            | L : Coring ON<br>H : Coring OFF                               |

| 6          | BIAS <sub>1</sub>  | Bias for ADC            | 20         | $V_{DD3}$         | V <sub>DD</sub> for digital                                   |

| 7          | CLAMPC             | Clamp filter            | 21         | V <sub>SS3</sub>  | GND for digital                                               |

| 8          | TEST1              | Test terminal           | 22         | BIAS <sub>3</sub> | Bias for DAC                                                  |

| 9          | 1/2V <sub>DD</sub> | Bias for line memory    | 23         | COUT              | C output                                                      |

| 10         | VFIL               | VCO filter              | 24         | BIAS <sub>2</sub> | Bias for DAC                                                  |

| 11         | CKIN               | Clock input             | 25         | YOUT              | Y output                                                      |

| 12         | $V_{DD2}$          | V <sub>DD</sub> for PLL | 26         | VREF1             | Bias for DAC                                                  |

| 13         | $V_{SS2}$          | GND for PLL             | 27         | $V_{DD4}$         | V <sub>DD</sub> for DAC                                       |

| 14         | KILLER             | L:Color, H:B/W mode     | 28         | V <sub>SS4</sub>  | GND for DAC                                                   |

(Note) Pin 9 and Pin 26 require external bias

#### **FUNCTION BLOCK DESCRIPTIONS**

## 1. Input clamp (CLAMP)

This block performs sync tip clamping of the composite video signal. It provides a feedback signal for clamping A/D-converted minimum data at Y/C separation to the internal DC bias level.

#### 2. A/D converter (ADC)

This block comprises a high-speed series-parallel 8bit A/D converter that accepts an input video signal of  $1.5V_{D-D}$  (from sync level to 100% white level).

## 3. 1H memory

This block consists of DRAM resident line memory for 1H delay. The 3-line comb filter is configured from two pairs of line memory.

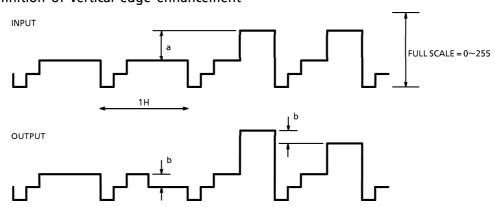

# 4. Vertical edge enhancement circuit (VENH)

This block enhances the uncorrelated components among the three lines of the luminance signal following coring. There are three enhancement level selections of HIGH (1.9dB), MID (1.0dB) and LOW 0.5dB). The luminance signal, obtained by subtracting the chrominance signal from the composite video signal, is added to the vertical edge enhancement component and output through the D/A converter. However, this output signal is limited to the pedestal level (fixed internally) by the pedestal clipping circuit (except for the sync tip level).

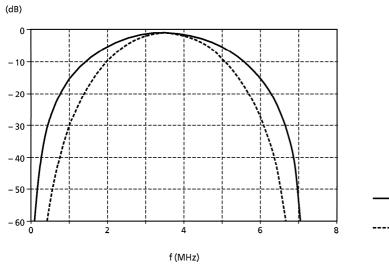

## 5. Horizontal band-pass filter (BPF)

In this block, with fsc as the center frequency of the BPF, the chrominance signal is extracted from the 0H, 1H and 2H delayed composite video signal. Since the BPF for the chrominance signal output can be controlled (ON or OFF), the chrominance output can therefore be switched between a narrow band width and a wide band width.

## 6. Vertical dynamic comb filter (DCF)

This block comprises a band-pass filter that extracts the vertical component of the chrominance signal. Using Toshiba original logic, a correlation of the three lines is sought for. The absence of correlation is taken as an indication of a luminance signal, at which time chrominance signal output is suppressed.

### 7. 1-line dot correction circuit

Previously, a 1-line-only chrominance signal was processed as a luminance signal resulting in dot crawl. This circuit prevents this problem by extracting the 1-line dot component and adding it to the dynamic comb filter output. This circuit block can be set ON or OFF.

## 8. Clock and memory timing generator (RTIM)

This block supplies a 4 fsc (PLL 4X multiplied) buffered signal to the other circuit blocks, and also generates a timing signal for the memory.

#### 9. D/A converter (DAC)

This block comprises a high-speed 8bit D/A converter. It provides Y output at approximately  $1.5V_{p-p}$  and burst-level C output at approximately  $572mV_{p-p}$ .

# **MODE TABLE**

| PIN 14<br>KILLER | PIN 15<br>CBPF | PIN 16<br>VENH0 | PIN 17<br>VENH1 | PIN 18<br>1 LINE | PIN 19<br>CORING | MODE                                                  | ACTION                                                  |

|------------------|----------------|-----------------|-----------------|------------------|------------------|-------------------------------------------------------|---------------------------------------------------------|

| L                | _              | _               | _               | _                | _                | Y/C separation ON                                     | Color mode                                              |

| Н                |                |                 |                 | _                | _                | Y/C separation OFF                                    | B/W mode (Killer)                                       |

| _                | L              | 1               | ı               | 1                | _                | Chrominance signal<br>horizontal band width<br>WIDE   | Passes through BPF for chrominance signal output        |

|                  | I              | 1               | 1               |                  |                  | Chrominance signal<br>horizontal band width<br>NARROW | Does not pass through BPF for chrominance signal output |

| _                | _              | L               | L               | _                | _                | Vertical enhance OFF                                  | No vertical enhancement                                 |

| _                |                | Н               | L               | _                | _                | Vertical enhance level MID                            | Vertical enhancement level 0.5dB                        |

| _                |                | L               | Н               | _                | _                | Vertical enhance level LOW                            | Vertical enhancement level 1.0dB                        |

|                  |                | Н               | Н               | _                | _                | Vertical enhance level<br>HIGH                        | Vertical enhancement level<br>1.9dB                     |

| _                |                | _               |                 | L                | _                | 1 line color ON                                       | 1 line dot correction circuit ON                        |

| _                |                | _               |                 | Н                | _                | 1 line color OFF                                      | 1 line dot correction circuit OFF                       |

| _                | _              | _               | _               |                  | L                | Coring ON                                             | Coring circuit ON                                       |

| _                |                |                 | _               |                  | Н                | Coring OFF                                            | Coring circuit OFF                                      |

# **RATINGS AND CHARACTERISTICS**

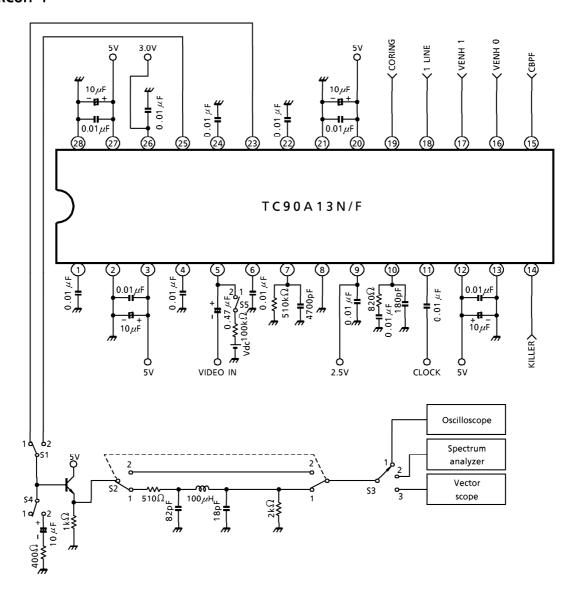

The following specifications were obtained in part from the test circuit shown on page 8.

# **MAXIMUM RATINGS** (Ta = $25^{\circ}$ C)

| CHARACTER          | CHARACTERISTIC |                       | CHARACTERISTIC            |       | RATING | UNIT |

|--------------------|----------------|-----------------------|---------------------------|-------|--------|------|

| Power Supply Volt  | age            | $V_{DD}$              | V55~V55 + 6.0             | V     |        |      |

| Input Voltage      |                | $v_{IN}$              | -0.3~V <sub>DD</sub> +0.3 | ٧     |        |      |

| Power Dissipation  | TC90A13N       | P <sub>D</sub> (Note) | 900                       | mW    |        |      |

| l ower bissipation | TC90A13F       | TD (Note)             | 600                       | 11100 |        |      |

| Storage Temperatu  | ire            | T <sub>stg</sub>      | <b>-</b> 55∼125           | °C    |        |      |

(Note)  $Ta = 75^{\circ}C$

# **RECOMMENDED OPERATING CONDITIONS**

| CHARACTERISTIC        | SYMBOL           | TEST CONDITION | MIN. | TYP. | MAX.     | UNIT |

|-----------------------|------------------|----------------|------|------|----------|------|

| Power Supply Voltage  | $V_{DD}$         | _              | 4.75 | 5.0  | 5.25     | V    |

| Input Voltage         | VIN              | _              | 0    | _    | $V_{DD}$ | V    |

| Operating Temperature | T <sub>opr</sub> | 1              | - 10 |      | 75       | °C   |

# **ELECTRICAL CHARACTERISTICS**

DC CHARACTERISTICS (Ta = 25°C,  $V_{DD} = 5V$ )

| CHARACT                    | ERISTIC    | SYMBOL            | TEST<br>CIR-<br>CUIT | TEST CONDITION                                                                                     | MIN. | TYP. | MAX. | UNIT     |

|----------------------------|------------|-------------------|----------------------|----------------------------------------------------------------------------------------------------|------|------|------|----------|

| Power Supply \             | /oltage    | $V_{DD}$          | 1                    |                                                                                                    | 4.75 | 5.0  | 5.25 | <b>V</b> |

| Supply Current             |            | $I_{DD}$          | 1                    |                                                                                                    | 40   | 60   | 80   | mΑ       |

| Output Voltage Level       |            | Yout              | 1                    |                                                                                                    | 3.0  | 3.15 | 3.3  | v        |

|                            |            | COUT              | '                    |                                                                                                    | 3.9  | 4.0  | 4.1  | V        |

|                            |            | VREFL             |                      |                                                                                                    | 1.4  | 1.5  | 1.6  |          |

|                            |            | VREFH             |                      | $CLOCK = 3.579545MHz$ $500mV_{p-p}$ $VREF1 = 3.0V$ $1/2V_{DD} = 2.5V$ $V_{IN} = No input (Note 2)$ | 3.4  | 3.5  | 3.6  | V        |

|                            |            | ADIN              |                      |                                                                                                    | 1.5  | 1.6  | 1.8  |          |

|                            |            | BIAS <sub>1</sub> |                      |                                                                                                    | 0.8  | 1.4  | 2.4  |          |

| Pin Voltage Lev            | /el        | BIAS <sub>2</sub> | 1                    |                                                                                                    | 0.8  | 1.6  | 2.6  |          |

|                            |            | BIAS <sub>3</sub> |                      |                                                                                                    | 2.4  | 3.4  | 4.4  |          |

|                            |            | CLAMPC            | 1                    |                                                                                                    | 2.0  | 3.0  | 4.0  |          |

|                            |            | VFIL              |                      |                                                                                                    | 0.9  | 1.9  | 2.9  |          |

|                            |            |                   |                      |                                                                                                    | 1.5  | 2.2  | 3.0  |          |

| Input Voltage              | High Level | V <sub>IH</sub>   | 1                    |                                                                                                    | 4    | _    | _    | .,       |

| input voitage              | Low Level  | V <sub>IL</sub>   | 1                    |                                                                                                    | _    | _    | 1    | V        |

| ADIN Pin Input Capacitance |            | CIN               | 1                    |                                                                                                    | _    | 50   | _    | рF       |

| Pull Down Resi             | stance     | R <sub>PD</sub>   | 1                    |                                                                                                    | 25   | 50   | 100  | kΩ       |

(Note 1) External bias must be applied at Pin 9 and Pin 26.

(Note 2)  $I_{DD}$  is  $V_{IN} = modulated lamp wave.$

AC CHARACTERISTICS Y output ( $Ta = 25^{\circ}C$ ,  $V_{DD} = 5V$ , Clock frequency 3.579545MHz, 0.5Vp-p, S1 = 2,  $V_{REF1} = 3.0V$ )

| CHARACTERISTIC                                         | SYMBOL          | TEST<br>CIR-<br>CUIT | TEST CONDITION                                                                                                                  |                   | MIN.  | TYP.  | MAX.  | UNIT              |

|--------------------------------------------------------|-----------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------|-------|-------|-------|-------------------|

| Input Level                                            | V <sub>IN</sub> | 1                    | 0~140IRE                                                                                                                        |                   | _     | 1.5   | 1.6   | V <sub>p-p</sub>  |

| Low Frequency Gain                                     | GV              | 1                    | S2 = 2, S3 = 2, S4 = 1<br>V <sub>IN</sub> = 15.734kHz, 1.5<br>Vdc = 2.5V                                                        |                   | - 0.5 | 0.0   | 0.5   | dB                |

| Eroquangu Basnansa                                     | MTF1            | 1                    | S2 = 2, S3 = 2,<br>S4 = 1, S5 = 2                                                                                               | f2/f1             | - 2.0 | - 1.2 | - 0.5 | dB                |

| Frequency Response                                     | MTF2            | 1                    | V <sub>IN</sub> = 1.5V <sub>p-p</sub><br>Vdc = 2.5V                                                                             | f4/f1             | - 3.0 | - 2.0 | - 1.5 | αв                |

| Comb Characteristics                                   | Comb            | 1                    | S2 = 2, $S3 = 2$ ,<br>S4 = 1, $S5 = 2V_{IN} = 1.5V_{p-p}Vdc = 2.5V$                                                             | f2/f3             | 40    | 45    | _     | dB                |

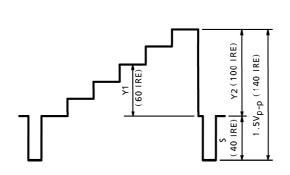

| Linearity (Fig. 4)                                     | L <sub>S</sub>  | 1                    | S2 = 1, S3 = 1,<br>S4 = 1, S5 = 2                                                                                               | Y1/Y2             | 35    | 40    | 43    | 0/                |

| Linearity (Fig.1)                                      | L <sub>y</sub>  | 1                    | $V_{IN} = 5$ step signal,<br>1.5 $V_{p-p}$ (Fig.2)                                                                              | S/Y2              | 57    | 60    | 63    | %                 |

| Output Impedance                                       | z <sub>o</sub>  | 1                    | S2 = 1, S3 = 1, S5 = 2<br>$V_{IN}$ = 15.734kHz, 1.5<br>Vdc = 2.5V<br>$Z_{O}$ = $\frac{V1 - V2}{V2}$ × 40<br>V1 : S4 = 1, V2 : 5 | 5V <sub>p-p</sub> | 250   | 400   | 700   | Ω                 |

| Clock Leakage<br>(4f <sub>sC</sub> Components)         | L <sub>ck</sub> | 1                    | S2 = 2, S3 = 2, S4 = 1<br>V <sub>IN</sub> = No input                                                                            |                   | _     | 5.0   | 20    | mV <sub>rms</sub> |

| Fundamental Clock Leakage (f <sub>SC</sub> Components) | L <sub>sc</sub> | 1                    | S2 = 2, S3 = 2, S4 = 1<br>V <sub>IN</sub> = No input                                                                            | , S5 = 1          | _     | 1.0   | 2.0   | mV <sub>rms</sub> |

C output (Ta = 25°C,  $V_{DD}$  = 5V, Clock frequency 3.579545MHz, 0.5 $V_{p-p}$ , S1 = 1, VREF1 = 3.0V)

| CHARACTERISTIC                                   |        | SYMBOL          | TEST<br>CIR-<br>CUIT | TEST CONDITION                                                                                                                                                                   | MIN.  | TYP.  | MAX.  | UNIT              |

|--------------------------------------------------|--------|-----------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------------------|

| BPF<br>Characteristics                           | WIDE   | BWCW            | 1                    | S2 = 2, $S3 = 2$ , $S4 = 1$ , $S5 = 2Difference of amplitudebetween 1f_{SC} and 1f_{SC} - 503496HzV_{IN} = 1.5V_{p-p}, Vdc = 2.5V$                                               | -0.5  | -0.2  |       | dB                |

|                                                  | NARROW | BWCN            | 1                    | S2 = 2, $S3 = 2$ , $S4 = 1$ , $S5 = 2Difference of amplitudebetween 1f_{SC} and 1f_{SC} - 503496HzV_{IN} = 1.5V_{p-p}, Vdc = 2.5V$                                               | - 1.0 | - 0.5 | _     | uв                |

| Gain                                             |        | CV              | 1                    | S2 = 2, $S3 = 2$ , $S4 = 1$ , $S5 = 1V_{IN} = f_{SC}, 430 \text{mV}_{p-p}$                                                                                                       | - 2.0 | - 0.9 | - 0.6 | dB                |

| Comb Characteristics                             |        | Comb            | 1                    | S2 = 2, $S3 = 2$ ,<br>S4 = 1, $S5 = 2V_{IN} = 430 \text{mV}_{p-p},Vdc = 2.5 V$                                                                                                   | 30    | 35    | _     | dB                |

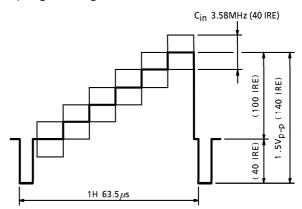

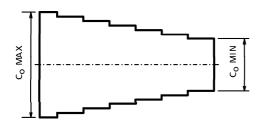

| Differential Gain                                |        | DG              | 1                    | S2 = 2, $S3 = 3$ , $S4 = 1$ , $S5 = 1V_{IN} = 5 step signal,Y = 140IRE = 1.5V_{p-p}$                                                                                             | 0     | 2     | 5     | %                 |

| Differential Phase                               |        | DP              | 1                    | C = 40IRE (Fig.2) DG = (Comax – Comin) / Comax (Fig.3)                                                                                                                           | 0     | 2     | 5     | o                 |

| Output Impedance                                 |        | Z <sub>O</sub>  | 1                    | S2 = 2, S3 = 2, S5 = 2<br>$V_{IN}$ = 15.734kHz, 1.5 $V_{p-p}$<br>$V_{dc}$ = 2.5 $V_{dc}$<br>$V_{dc}$ = $\frac{V_{1} - V_{2}}{V_{2}}$ × 400<br>$V_{1}$ : S4 = 1, $V_{2}$ : S4 = 2 | 250   | 400   | 700   | Ω                 |

| Clock Leak<br>(4f <sub>sc</sub> Components)      |        | L <sub>ck</sub> | 1                    | S2 = 2, S3 = 2, S4 = 1, S5 = 1<br>V <sub>IN</sub> = No input                                                                                                                     | -     | 5.0   | 20    | mV <sub>rms</sub> |

| Fundamental Cloc<br>(f <sub>sc</sub> Components) |        | L <sub>sc</sub> | 1                    | S2 = 2, $S3 = 2$ , $S4 = 1$ , $S5 = 1V_{IN} = No input$                                                                                                                          | _     | 0.3   | 1.0   | mV <sub>rms</sub> |

f1 = 15.734kHz, f2 = 3.587412MHz, f3 = 3.595279MHz, f4 = 4.783216MHz

# PLL CIRCUIT CHARACTERISTICS

| CHARACTERISTIC                               | SYMBOL | TEST<br>CIR-<br>CUIT | TEST CONDITION | MIN. | TYP. | MAX. | UNIT             |

|----------------------------------------------|--------|----------------------|----------------|------|------|------|------------------|

| Pull-in Frequency Range                      | fck    | 1                    | _              | 3.57 | 3.58 | 3.59 | MHz              |

| Input Amplitude (f <sub>sc</sub> Components) | Vck    | 1                    | _              | 0.4  | 0.5  | _    | V <sub>p-p</sub> |

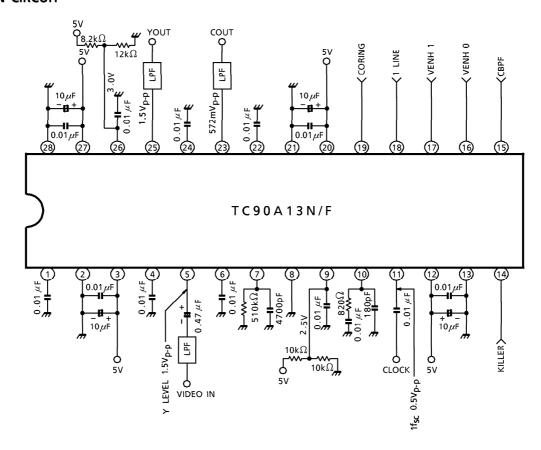

# **TEST CIRCUIT 1**

Linearity test (Fig.1)

5 Step signal (Fig.2)

Chroma differential gain (Fig.3)

# **REFERENCE DATA**

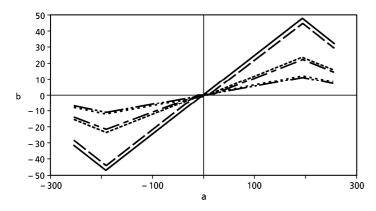

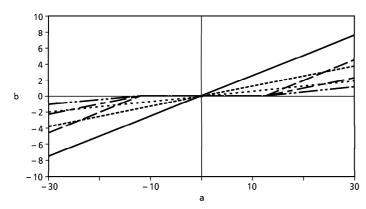

(Fig.4-a) Definition of vertical edge enhancement

(Note) The output signal, to which the vertical edge enhancement component is added, is limited to pedestal level by the pedestal clip circuit.

(Fig.4-b) Vertical edge enhancement characteristic

(Fig.4-c) Vertical edge enhancement characteristic (detail)

The relation between a and b. (refer to Fig.4-a)

- a: The difference in luminance level is in the enhanced part of the edge.

- b: The component of vertical edge enhancement that is added to the luminance signal.

Both are expressed as digital values.

- (A) Enhance Value HIGH ----- (B) MID ---- (C) LOW

- − − (D) Enhance value HIGH −− − (E) MID −−− ⋅ (F) LOW

A, B, C : Coring = OFF D, E, F : Coring = ON

(Fig.5) Frequency characteristics of chroma output

- Wide band width

---- Narrow band width

# **APPLICATION CIRCUIT**

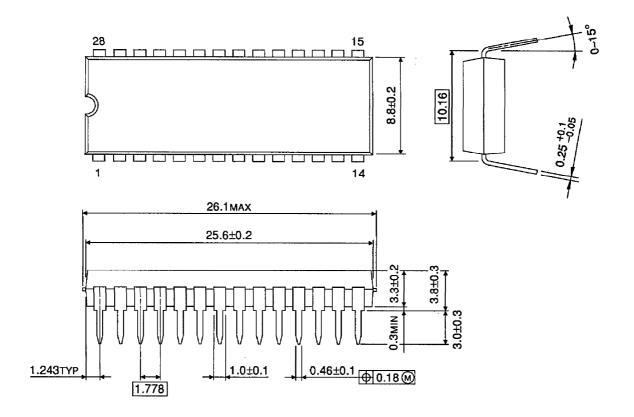

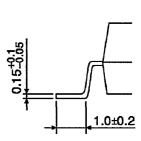

# **PACKAGE DIMENSIONS**

SDIP28-P-400-1.78 Unit: mm

Weight: 1.7g (Typ.)

Unit: mm

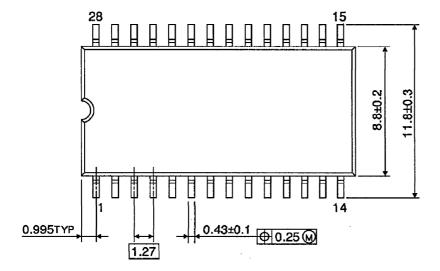

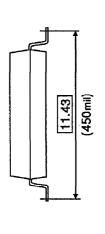

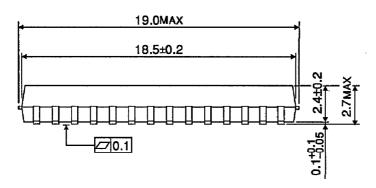

# **PACKAGE DIMENSIONS**

SOP28-P-450-1.27

Weight: 0.8g (Typ.)

## RESTRICTIONS ON PRODUCT USE

000707EBA

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

- The products described in this document are subject to the foreign exchange and foreign trade laws.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

- The information contained herein is subject to change without notice.