TOSHIBA Bipolar Linear IC Silicon Monolithic

## **TA2170FL**

#### Low Current Consumption Headphone Amplifier (Built-in input selector)

The TA2170FL is a stereo headphone amplifier built in the selector switch of 3 inputs.

The mute switch is built in each 3 input, and an output can choose 1 output or a mixer output.

#### **Features**

• Low current consumption

$V_{CC} = 3 \text{ V}, \text{ f} = 1 \text{ kHz}, \text{ RL} = 32 \Omega, \text{ typ}.$

• No signal mode

$I_{CCQ} = 0.9 \text{ mA} (1 \text{ input mode})$

ICCQ = 1.0 mA (2 inputs mode)

$I_{CCQ} = 1.1 \text{ mA} (3 \text{ inputs mode})$

•  $0.1 \text{ mW} \times 2 \text{ ch}$

ICC = 2.2 mA (1 input mode)

$I_{CC} = 2.3 \text{ mA} (2 \text{ inputs mode})$

ICC = 2.4 mA (3 inputs mode)

•  $0.5 \text{ mW} \times 2 \text{ ch}$

$I_{CC} = 4.1 \text{ mA} (1 \text{ input mode})$

ICC = 4.2 mA (2 inputs mode)

ICC = 4.3 mA (3 inputs mode)

- GV = -0.3dB (1 input mode, typ.)

- Built-in signal level adjustment circuit, so that a 1 output or a mixer output doesn't change a feeling of volume either.

- Built-in power switch

- Built-in all mute switch

- Built-in mute switch at each buffer amplifier.

- ullet Built-in one side mute switch at buffer amplifier 1.

- Operating supply voltage range (Ta = 25°C):  $V_{\rm CC1~(opr)}$  = 1.8 to 4.5 V

VCC2 (opr) = 0.9 to 4.5 V

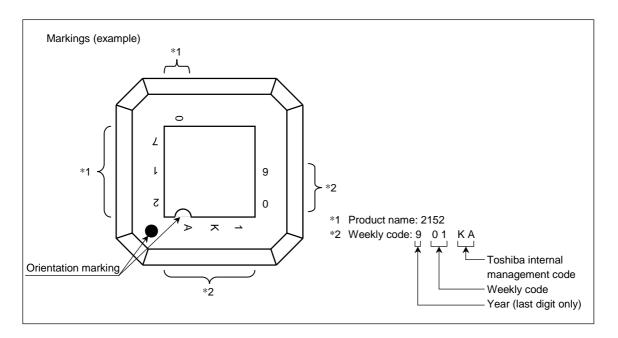

Weight: 0.05 g (typ.)

Marking: 2170

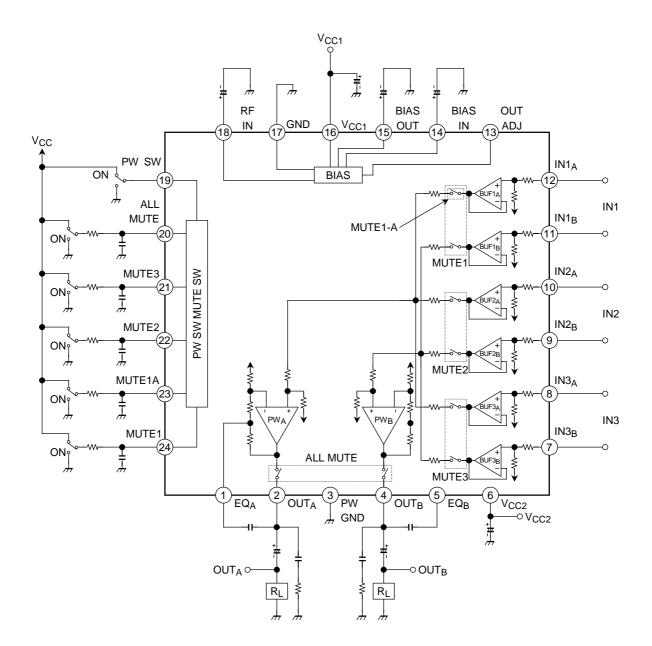

## **Block Diagram**

## **Pin Descriptions**

Pin Voltage: Typical Pin voltage for test circuit when no input signal is applied, VCC1 = VCC2 = 3 V, Ta = 25°C

|    | No. and Name        | Pin voltage for test circuit when  Function | Internal Circuit        |      |  |  |  |

|----|---------------------|---------------------------------------------|-------------------------|------|--|--|--|

| 1  | EQ <sub>A</sub>     | - Low-pass Compensation pins                | 2                       | 1.15 |  |  |  |

| 5  | 5 EQ <sub>B</sub>   | - Low-pass Compensation pins                | C 15 kΩ 43 kΩ  BIAS OUT | 1.15 |  |  |  |

| 2  | OUTA                | Outputs from power amplifier                | → 6 → ∨cc2              | 1.15 |  |  |  |

| 4  | OUTB                | Outputs from power amplifier                |                         | 1.15 |  |  |  |

| 3  | PW GND              | GND for power drive stage                   | 2                       | 0    |  |  |  |

| 6  | V <sub>CC2</sub>    | V <sub>CC</sub> for power drive stage       | <b>1</b>                | 3    |  |  |  |

| 7  | IN3 <sub>B</sub>    | landa ta huffar annilifian O                |                         | 4.45 |  |  |  |

| 8  | B IN3 <sub>A</sub>  | Inputs to buffer amplifier 3                |                         | 1.15 |  |  |  |

| 9  | IN2 <sub>B</sub>    | Inputs to buffer amplifier 2                | 10 kΩ                   | 1.15 |  |  |  |

| 10 | 10 IN2 <sub>A</sub> | Timputo to builer arripililer 2             |                         | 1.10 |  |  |  |

| 11 | IN1 <sub>B</sub>    | Inputs to buffer amplifier 1                | BIAS                    | 1.15 |  |  |  |

| 12 | 12 IN1 <sub>A</sub> | inpute to builter arriphilier 1             | OUT                     | 1.13 |  |  |  |

| Pin N | lo. and Name     | Function                                                                                                                                                                                                                                                                                                                | Internal Circuit                                                   | Pin<br>Voltage<br>(V) |

|-------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------|

| 13    | OUT ADJ          | DC output voltage adjustment Either connect this pin or leave it open depending on the level of V <sub>CC2</sub> . If the power supply of a 1.5 V system is applied to V <sub>CC2</sub> , connect this pin to BIAS IN (pin14) If the power supply of a 3 V system is applied to V <sub>CC2</sub> , leave this pin open. | 18 VCC2 VCC1                                                       | 1.85                  |

| 14    | BIAS IN          | Bias circuit input                                                                                                                                                                                                                                                                                                      |                                                                    | 1.15                  |

| 15    | BIAS OUT         | Bias circuit output                                                                                                                                                                                                                                                                                                     |                                                                    | 1.15                  |

| 16    | V <sub>CC1</sub> | V <sub>CC</sub> for everything other than power drive stage                                                                                                                                                                                                                                                             |                                                                    | 3                     |

| 18    | RF IN            | Ripple filter input                                                                                                                                                                                                                                                                                                     |                                                                    | 2.7                   |

| 17    | GND              |                                                                                                                                                                                                                                                                                                                         |                                                                    | 0                     |

| 19    | PW SW            | Power switch (IC ON: H level IC OFF: L level Refer to application note 4.                                                                                                                                                                                                                                               | VCC1<br>19<br>100 kΩ<br>130 kΩ<br>19<br>100 kΩ<br>100 kΩ<br>100 kΩ | 3                     |

| 20    | ALL MUTE         | All mute switch (Mute ON: L level Mute OFF: H level Refer to application note 4.                                                                                                                                                                                                                                        | V <sub>CC</sub> 10 kΩ 20 kΩ  10 kΩ  10 kΩ                          | _                     |

| 21    | MUTE3            | Mute switch of buffer amplifier 3  (Mute ON: L level  Mute OFF: H level  Refer to application note 4.                                                                                                                                                                                                                   |                                                                    | _                     |

| 22    | MUTE2            | Mute switch of buffer amplifier 2  (Mute ON: L level  Mute OFF: H level  Refer to application note 4.                                                                                                                                                                                                                   | V <sub>CC</sub>                                                    | _                     |

| 23    | MUTE1A           | Mute switch of buffer amplifier 1A (Mute ON: L level Mute OFF: H level this switch is used when it turn on A channel mutes of a buffer amplifier 1. Refer to application note 4.                                                                                                                                        |                                                                    | _                     |

| 24    | MUTE1            | Mute switch of buffer amplifier 1 (Mute ON: L level Mute OFF: H level Refer to application note 4.                                                                                                                                                                                                                      |                                                                    | _                     |

## **Application Notes**

#### 1. Mute switch and voltage gain

This IC is designed so that a volume feeling may not change with a single output and many outputs. When the input signal to buffer amplifier is same and a linear domain, the relation between mute switches and voltage gain are as follows.

Test condition:  $V_{CC} = 3 \text{ V}, \text{ } f = 1 \text{ kHz}, \text{ } V_{in} = -20 \text{dBV}, \text{ } \text{theoretical value}$

#### (1) 1 input mode

|                | MUTE SW                          |       |       |      |      |      | input sig |      |      | Total gain |      |

|----------------|----------------------------------|-------|-------|------|------|------|-----------|------|------|------------|------|

|                |                                  |       | T     | BL   |      | _    | JF2       | _    | JF3  | ,          | B)   |

| MUTE1          | MUTE1A                           | MUTE2 | MUTE3 | Ach  | Bch  | Ach  | Bch       | Ach  | Bch  | Ach        | Bch  |

| Input signal i | s applied to BU                  | JF 1. |       |      |      |      |           |      |      |            |      |

| OFF            | OFF                              | ON    | ON    | 0    | 0    | _    | _         | _    | _    | 0          | 0    |

| OFF            | OFF                              | OFF   | ON    | -6   | -6   | _    | _         |      | _    | -6         | -6   |

| OFF            | OFF                              | ON    | OFF   | -6   | -6   | _    | _         | _    | _    | -6         | -6   |

| OFF            | OFF                              | OFF   | OFF   | -9.5 | -9.5 | _    | _         | _    | _    | -9.5       | -9.5 |

| OFF            | ON                               | ON    | ON    | _    | 0    |      | _         | _    |      | _          | 0    |

| OFF            | ON                               | OFF   | ON    | _    | -6   | _    | _         | _    | _    | _          | -6   |

| OFF            | ON                               | ON    | OFF   | _    | -6   | _    | _         | _    | _    | _          | -6   |

| OFF            | ON                               | OFF   | OFF   | _    | -9.5 | _    | _         | _    | _    | _          | -9.5 |

| Input signal i | Input signal is applied to BUF 2 |       |       |      |      |      |           |      |      |            |      |

| ON             | ON/OFF                           | OFF   | ON    | _    | _    | 0    | 0         | _    | _    | 0          | 0    |

| ON             | ON/OFF                           | OFF   | OFF   | _    | _    | -6   | -6        | _    | _    | -6         | -6   |

| OFF            | OFF                              | OFF   | ON    | _    | _    | -6   | -6        | _    | _    | -6         | -6   |

| OFF            | ON                               | OFF   | ON    | _    | _    | 0    | -6        | _    | _    | 0          | -6   |

| OFF            | OFF                              | OFF   | OFF   | _    | _    | -9.5 | -9.5      | _    | _    | -9.5       | -9.5 |

| OFF            | ON                               | OFF   | OFF   | _    | _    | -6   | -9.5      | _    | _    | -6         | -9.5 |

| Input signal i | s applied to BU                  | JF 3. |       |      |      |      |           |      |      |            |      |

| ON             | ON/OFF                           | ON    | OFF   | _    |      | _    | _         | 0    | 0    | 0          | 0    |

| ON             | ON/OFF                           | OFF   | OFF   | _    |      | _    | _         | -6   | -6   | -6         | -6   |

| OFF            | OFF                              | ON    | OFF   | _    | _    | _    | _         | -6   | -6   | -6         | -6   |

| OFF            | ON                               | ON    | OFF   | _    | _    | _    | _         | 0    | -6   | 0          | -6   |

| OFF            | OFF                              | OFF   | OFF   | _    | _    | _    | _         | -9.5 | -9.5 | -9.5       | -9.5 |

| OFF            | ON                               | OFF   | OFF   | _    | _    | _    | _         | -6   | -9.5 | -6         | -9.5 |

(2) 2 inputs mode

| MUTE SW        |                 |              |       | Attenuation to an input signal (dB) |      |      |      |      |      | Total gain |      |  |

|----------------|-----------------|--------------|-------|-------------------------------------|------|------|------|------|------|------------|------|--|

|                | WOT             | LOW          |       | BUF1 BI                             |      | BL   | JF2  | BL   | BUF3 |            | (dB) |  |

| MUTE1          | MUTE1A          | MUTE2        | MUTE3 | Ach                                 | Bch  | Ach  | Bch  | Ach  | Bch  | Ach        | Bch  |  |

| Input signal i | s applied to BU | JF 1 and BUF | 2.    |                                     |      |      |      |      |      |            |      |  |

| OFF            | OFF             | OFF          | ON    | -6                                  | -6   | -6   | -6   | _    | _    | 0          | 0    |  |

| OFF            | OFF             | OFF          | OFF   | -9.5                                | -9.5 | -9.5 | -9.5 | _    | _    | -3.5       | -3.5 |  |

| OFF            | ON              | OFF          | ON    | _                                   | _    | _    | _    | _    | _    | _          | _    |  |

| OFF            | ON              | OFF          | OFF   | _                                   | -6   | -9.5 | -6   | _    | _    | -3.5       | 0    |  |

| Input signal i | s applied to BU | JF 1 and BUF | 3.    |                                     |      |      |      |      |      |            |      |  |

| OFF            | OFF             | ON           | OFF   | -6                                  | -6   | _    | _    | -6   | -6   | 0          | 0    |  |

| OFF            | OFF             | OFF          | OFF   | -9.5                                | -9.5 | _    | _    | -9.5 | -9.5 | -3.5       | -3.5 |  |

| OFF            | ON              | ON           | OFF   | _                                   | -6   | _    | _    | -6   | -6   | -6         | 0    |  |

| OFF            | ON              | OFF          | OFF   | _                                   | -9.5 | _    | _    | -9.5 | -9.5 | -9.5       | -3.5 |  |

| Input signal i | s applied to BU | JF 2 and BUF | 3.    |                                     |      |      |      |      |      |            |      |  |

| ON             | ON/OFF          | OFF          | OFF   | _                                   | _    | -6   | -6   | -6   | -6   | 0          | 0    |  |

| OFF            | ON              | OFF          | OFF   |                                     | _    | -6   | -9.5 | -6   | -9.5 | 0          | -3.5 |  |

| OFF            | OFF             | OFF          | OFF   |                                     |      | -9.5 | -9.5 | -9.5 | -9.5 | -3.5       | -3.5 |  |

(3) 3 inputs mode

| MUTE SW    |        |       |       |      | Attenuation to an input signal (dB) |      |      |      |      |      | Total gain |  |

|------------|--------|-------|-------|------|-------------------------------------|------|------|------|------|------|------------|--|

| IVIOTE SVV |        |       | BU    | JF1  | BL                                  | JF2  | BL   | JF3  | (d   | B)   |            |  |

| MUTE1      | MUTE1A | MUTE2 | MUTE3 | Ach  | Bch                                 | Ach  | Bch  | Ach  | Bch  | Ach  | Bch        |  |

| OFF        | OFF    | OFF   | OFF   | -9.5 | -9.5                                | -9.5 | -9.5 | -9.5 | -9.5 | 0    | 0          |  |

| OFF        | ON     | OFF   | OFF   | _    | -9.5                                | -9.5 | -9.5 | -9.5 | -9.5 | -3.5 | 0          |  |

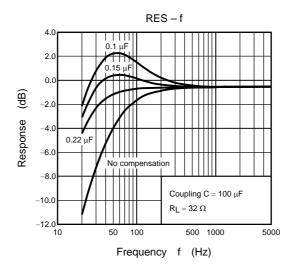

#### 2. Low-cut compensation

The low-frequency range can be decreased using an output-coupling capacitor and a load ( $f_c=50~Hz$  at  $C=100~\mu F,~R=32~\Omega$ ). However, since the capacitor is connected between the IC's output pin (pin 2/4) and EQ pin (pin 1/5), the low-frequency gain of the power amplifier increases, enabling low-cut compensation to be performed. For the response of capacitors of different values, please refer to Figure 1.

Figure 1 Capacitor response

#### 3. Adjustment of DC output voltage

Please perform the OUT ADJ pin (pin 13) as follows by the power supply of VCC1 and VCC2.

If a boost voltage is applied to VCC1, VCC2 is connected to a battery and the difference between VCC1 and VCC2 is greater than or equal to 0.7 V, short pins 13 and 14 together. In this case the DC output voltage

will be

$$\frac{V_{CC2}}{2}$$

.

• If the difference between VCC1 and VCC2 is less than 0.7 V, or if VCC1 and VCC2 are connected to the same power supply, leave pin 13 open.

In these cases the DC output voltage will be  $\frac{V_{CC2} - 0.7 \text{ V}}{2}$ .

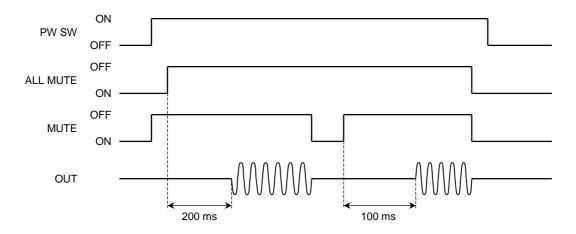

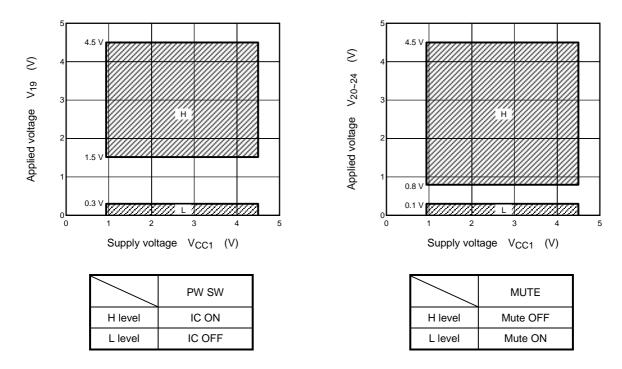

#### 4. Switch

(1) Timing chart Refer to Fig. 2 for the IC timing chart.

Figure 2 Timing chart

7

#### (2) PW SW

The device is ON when this pin is set to High. To prevent the IC being turned ON by external noise, it is necessary to connect an external pull-down resistor to the PW SW pin. The pin is highly sensitive.

#### (3) Mute smoothing

The resistor is connected to a mute pin less than 100  $k\Omega$

When larger than this, the switch circuit doesn't operate normally.

#### (4) Switch sensitivity (Ta = 25°C)

Figure 3 Switch sensitivity

#### 5. Capacitor

The following capacitors must have excellent temperature and frequency characteristics.

#### **Absolute Maximum Ratings (Ta = 25°C)**

| Characteristic        | Symbol                | Rating  | Unit |

|-----------------------|-----------------------|---------|------|

| Supply voltage 1      | V <sub>CC1</sub>      | 4.5     | V    |

| Supply voltage 2      | V <sub>CC2</sub>      | 4.5     | V    |

| Output current        | I <sub>o (peak)</sub> | 100     | mA   |

| Power dissipation     | P <sub>D</sub> (Note) | 350     | mW   |

| Operating temperature | T <sub>opr</sub>      | -25~75  | °C   |

| Storage temperature   | T <sub>stg</sub>      | -55~150 | °C   |

Note: Derated by 2.8 mW/°C above Ta = 25°C

# Electrical Characteristics (Unless otherwise specified, $V_{CC1}$ = $V_{CC2}$ = 3 V, Rg = 600 $\Omega$ , R<sub>L</sub> = 32 $\Omega$ , f = 1 kHz, Ta = 25°C, SW1~SW5: a, SW6~SW8: a)

| Characteristic                    | Symbol             | Test condition                                                                                                                                                     | Min. | Тур. | Max. | Unit |  |  |  |

|-----------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|--|--|--|

|                                   | I <sub>CCQ1</sub>  | IC OFF mode SW1~5: b                                                                                                                                               | _    | _    | 5    | μΑ   |  |  |  |

|                                   | I <sub>CCQ2</sub>  | 1 input on mode<br>BUF1: ON (SW5: a, SW3/4: b)<br>BUF2: ON (SW4: a, SW3/5: b)<br>BUF3: ON (SW3: a, SW4/5: b)                                                       |      | 0.9  | 1.6  |      |  |  |  |

| Quiescent supply current          | I <sub>CCQ3</sub>  | 2 input on mode<br>BUF1/2: ON (SW4/5: a, SW3: b)<br>BUF1/3: ON (SW3/5: a, SW4: b)<br>BUF2/3: ON (SW3/4: a, SW5: b)                                                 | _    | 1.0  | 1.8  | mA   |  |  |  |

|                                   | I <sub>CCQ4</sub>  | 3 input on mode                                                                                                                                                    | _    | 1.1  | 2.0  |      |  |  |  |

|                                   | I <sub>CCQ5</sub>  | 1 input on mode<br>V <sub>CC1</sub> = 2.4 V, V <sub>CC2</sub> = 1.2 V<br>BUF1: ON (SW5: a, SW3/4: b)<br>BUF2: ON (SW4: a, SW3/5: b)<br>BUF3: ON (SW3: a, SW4/5: b) | _    | 0.9  | 1.6  |      |  |  |  |

|                                   | I <sub>CC1</sub>   | 1 input on mode 0.1 mW/32 $\Omega$ × 2 ch BUF1: ON (SW5: a, SW3/4: b) BUF2: ON (SW4: a, SW3/5: b) BUF3: ON (SW3: a, SW4/5: b)                                      | _    | 2.2  | _    |      |  |  |  |

| Power supply current during drive | I <sub>CC2</sub>   | 2 input on mode 0.1 mW/32 Ω × 2 ch<br>BUF1/2: ON (SW4/5: a, SW3: b)<br>BUF1/3: ON (SW3/5: a, SW4: b)<br>BUF2/3: ON (SW3/4: a, SW5: b)                              | _    | 2.3  | _    | mA   |  |  |  |

|                                   | I <sub>CC3</sub>   | 3 input on mode 0.1 mW/32 $\Omega \times 2$ ch                                                                                                                     | _    | 2.4  | _    |      |  |  |  |

|                                   | G <sub>V1</sub>    | 1 input on mode V <sub>0</sub> = -20dBV<br>BUF1: ON (SW5: a, SW3/4: b)<br>BUF2: ON (SW4: a, SW3/5: b)<br>BUF3: ON (SW3: a, SW4/5: b)                               |      | 1.2  |      |      |  |  |  |

| Voltage gain                      | G <sub>V2</sub>    | 2 input on mode V <sub>0</sub> = -20dBV<br>BUF1/2: ON (SW4/5: a, SW3: b)<br>BUF1/3: ON (SW3/5: a, SW4: b)<br>BUF2/3: ON (SW3/4: a, SW5: b)                         | -1.0 | 0.5  | 2.0  | dB   |  |  |  |

|                                   | G <sub>V3</sub>    | 3 input on mode V₀ = −20dBV                                                                                                                                        | -0.8 | 0.7  | 2.2  | 1    |  |  |  |

| Channel balance                   | СВ                 | $V_0 = -20 dBV$                                                                                                                                                    | -1.5 | 0    | 1.5  | dB   |  |  |  |

|                                   | P <sub>o1</sub>    | THD = 10%                                                                                                                                                          | 15   | 20   | _    |      |  |  |  |

| Output power                      | P <sub>o2</sub>    | V <sub>CC1</sub> = 2.4 V, V <sub>CC2</sub> = 1.2 V<br>THD = 10%                                                                                                    | 3    | 6    | _    | mW   |  |  |  |

| Total harmonic distortion         | THD                | P <sub>o</sub> = 1 mW                                                                                                                                              | _    | 0.1  | 0.3  | %    |  |  |  |

| Output noise voltage              | V <sub>no</sub>    | $R_g = 600 \Omega$ , Filter: IHF-A, SW6~8: b                                                                                                                       | _    | -100 | -96  | dBV  |  |  |  |

| Cross talk                        | СТ                 | $V_0 = -20 dBV$                                                                                                                                                    | -53  | -60  | _    | dB   |  |  |  |

| Ripple rejection ratio            | RR                 | $f_r = 100 \text{ Hz}, V_r = -20 \text{dBV}$                                                                                                                       | -70  | -80  | _    | dB   |  |  |  |

| Muting attonuction                | ATT1               | ALL MUTE SW: ON, V <sub>0</sub> = -20dBV                                                                                                                           | -75  | -90  | _    | ۷D   |  |  |  |

| Muting attenuation                | ATT2               | MUTE SW: ON, $V_0 = -20 dBV$                                                                                                                                       | -47  | -62  | _    | dB   |  |  |  |

| PW SW ON current                  | l19                | V <sub>CC1</sub> = 1.8 V, V <sub>CC2</sub> = 0.9 V                                                                                                                 | 5    | _    | _    | μА   |  |  |  |

| PW SW OFF voltage                 | V19                | V <sub>CC1</sub> = 1.8 V, V <sub>CC2</sub> = 0.9 V                                                                                                                 | 0    | _    | 0.3  | V    |  |  |  |

| MUTE SW OFF current               | I <sub>20-24</sub> | V <sub>CC1</sub> = 1.8 V, V <sub>CC2</sub> = 0.9 V                                                                                                                 | 5    | _    | _    | μА   |  |  |  |

| MUTE SW ON voltage                | V <sub>20-24</sub> | V <sub>CC1</sub> = 1.8 V, V <sub>CC2</sub> = 0.9 V                                                                                                                 | 0    | _    | 0.1  | V    |  |  |  |

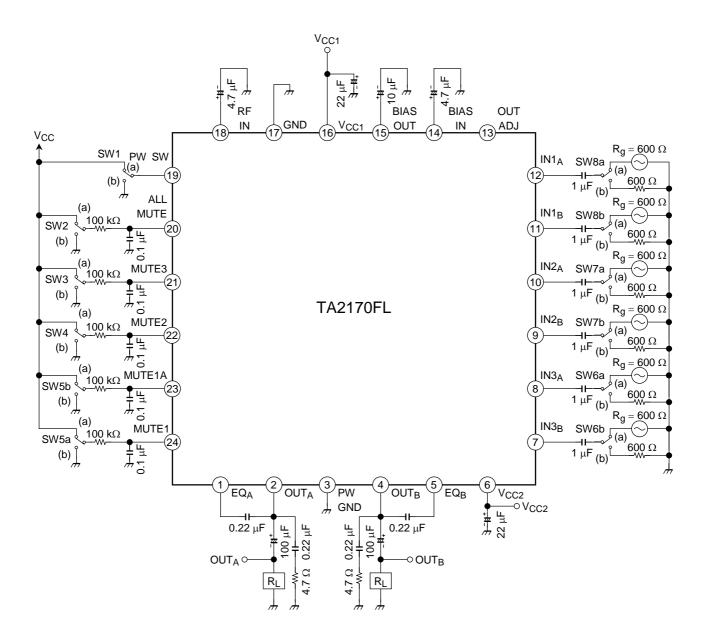

#### **Test Circuit**

## Markings

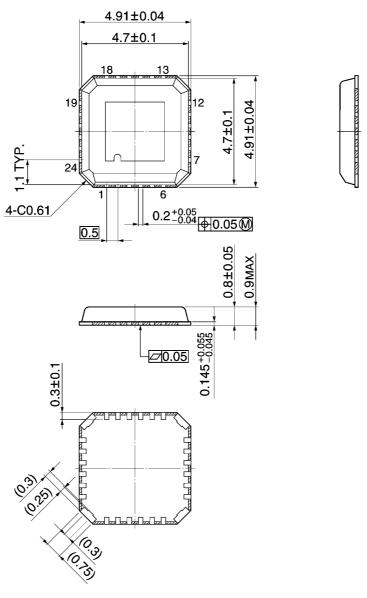

## **Package Dimensions**

QON24-P-0505-0.50 Unit: mm

- Note 1) The solder plating portion in four corners of the package shall not be treated as an external terminal.

- Note 2) Don't carry out soldering to four corners of the package.

- Note 3) area: Resin surface

Weight: 0.05 g (typ.)

#### **RESTRICTIONS ON PRODUCT USE**

000707EBA

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

- The products described in this document are subject to the foreign exchange and foreign trade laws.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

- The information contained herein is subject to change without notice.