## SP8000 SERIES HIGH SPEED DIVIDERS

# SP8690 A, B & M 200 MHz ÷ 10/11 AC COUPLED VHF, LOW POWER, PROGRAMMABLE DIVIDERS

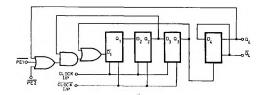

The SP8690 A, B & M are divider circuits that can be logically programmed to divide by either 10 or 11.

PLESSEY SEMICONDUCTORS

The device is available over three temperature ranges : 'A' grade is -55 C to +125 C and the 'B' grade is 0 C to +70 C and the 'M' grade is -40 C to +85 C.

The clock inputs can be either single or differentially driven and must be AC-coupled to the signal source. If single driven then the unused input must be decoupled to the earth plane. The device will self-oscillate if no input is present; to prevent this, a  $68k\Omega$  resistor should be connected from pin 1 or 16 to 0V. This will reduce the sensitivity of the device by approximately  $100mV p_p$ .

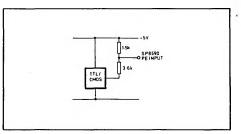

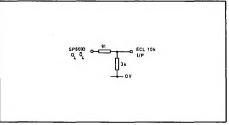

The division ratio is controlled by two  $\overline{PE}$  inputs which are ECL III and ECL 10K compatible throughout the temperature range. The device will divide by ten when either input is high and by eleven when both inputs are low. These inputs may be interfaced to TTL and CMOS by the inclusion of 2 resistors, as shown in Fig. 3. There is a free collector, saturating output stage for interfacing with either TTL or CMOS, together with true and inverse outputs with ECL II compatible levels. These may be interfaced to ECL 10K as shown in Fig. 4.

The device may be used as a fixed  $\div$  10 by connecting Q4 to one PE input.

$l\bar{f}$  the 0 -- 1 transition of Q4 (or the 1 -- 0 transition of Q4) is used to clock the next stage then this will give the maximum loop delay for control, i.e. 10 clock periods minus the internal delays.

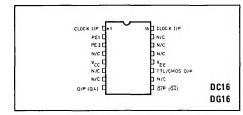

Fig.1 Pin connections

### FEATURES

- Full Temperature Range Operation 'A' Grade —55°C to -125°C 'B' Grade 0°C to +70°C 'M' Grade —40°C to +85°C

- Toggle Frequency in Excess of 200MHz

- Power Dissipation 70mW Typical

- ECL Compatibility on All Inputs

- Capacitively Coupled Clock Input for Synthesiser and Counter Applications

- True and Inverse Outputs Available with ECL Compatibility

- Output Available for Driving TTL or CMOS

| Division ratio |    |    |    |    |

|----------------|----|----|----|----|

| I/P            | 11 | 10 | 10 | 10 |

| PE1            | L  | н  | L  | н  |

| PE2            | L  | L  | н  | н  |

| С              | ount s | equen                 | ce | ]                                     |

|----------------|--------|-----------------------|----|---------------------------------------|

| Q <sub>1</sub> | Q2     | <b>a</b> <sub>3</sub> | Q4 | ]                                     |

| L              | н      | н                     | н  |                                       |

| L              | L      | н                     | н  | 1                                     |

| L              | L      | L                     | н  | 1                                     |

| н              | L      | L                     | н  | 1                                     |

| н              | н      | L                     | н  |                                       |

| L              | н      | н                     | L  | ]                                     |

| L              | L      | н                     | L  | ]                                     |

| L              | L      | L                     | L  |                                       |

| Н              | L      | L                     | L  | ]                                     |

| н              | н      | L                     | L  | · · · · · · · · · · · · · · · · · · · |

| н              | н      | н                     | н  | Extra state                           |

#### SP8690/5

### **ELECTRICAL CHARACTERISTICS**

#### Test Conditions (unless otherwise stated):

| Tamb           | 'A' grade –55 °C to                      |                  |

|----------------|------------------------------------------|------------------|

|                | 'B' grade 0°C to +<br>'M' grade -40°C to |                  |

| Supply voltage | $VCC = +5V \pm 0.25$                     |                  |

|                | VEE = 0V<br>Clock I/P voltage            | 400mV to 800mV p |

|                | Clock I/1 Voltage                        |                  |

age 400mV to 800mV peak to peak Pin 16 (decoupled to 0V)

| · · · · · · · · · · · · · · · · · · ·                                         | Value         |             |      |          |                                                                                            |

|-------------------------------------------------------------------------------|---------------|-------------|------|----------|--------------------------------------------------------------------------------------------|

| Characteristic                                                                | Min.          | Тур.        | Max. | Units    | Conditions                                                                                 |

| Max. toggle frequency                                                         | 200           |             |      | MHz      |                                                                                            |

| Min. freq. with sine wave clock<br>input                                      |               | 15          |      | MHz      |                                                                                            |

| Min. slew rate of square wave<br>I/P for correct operation<br>PE input levels |               | 40          |      | V/µs     |                                                                                            |

| Vinh                                                                          | +4.1          |             | +4.5 | v        | Vcc=+5V                                                                                    |

| VINL<br>Q4 & Q4 output voltage levels                                         | 0.0           |             | +3.5 | v        | Tamb≕+25°C (note 1)<br>Tamb=+25°C (note 2)                                                 |

| Voн                                                                           | 4.15          |             |      | v        | lout (external) = OmA                                                                      |

| Vol                                                                           |               |             | +3.5 | V        | (There is internal circuitry equivalent to<br>a 3.8kΩ pulldown resistor on each<br>output) |

| TTL/CMOS output voltage<br>levels                                             |               |             |      |          | outputy                                                                                    |

| Vol                                                                           |               |             | +0.4 | v        | Sink current 3.2mA on                                                                      |

| Vон                                                                           | see<br>note 3 |             |      |          | TTL output                                                                                 |

| Input pulldown resistors between                                              |               |             |      |          |                                                                                            |

| input pins 2 & 3 and —ve rail<br>Power supply drain current                   |               | 10<br>14    |      | kΩ<br>mA | Vcc = +5V; Tamb = 25°C                                                                     |

| Impedance of clock I/P                                                        |               | 1.6         |      | kΩ       | in=OHz                                                                                     |

| Clock to TTL output delay<br>(O/P - ve going)                                 |               | 22          |      | ns       | 8mA sink current                                                                           |

| Clock to TTL output delay                                                     |               | 22          |      | ns       | oma sink current                                                                           |

| (O/P -ve going)                                                               |               | 8           |      | ns       | TTL output                                                                                 |

| Clock to ECL output delay                                                     |               | 8<br>6<br>2 |      | ns       | See note 4                                                                                 |

| Set up time<br>Release time                                                   |               | 4           |      | ns<br>ns | See note 5                                                                                 |

NOTES

1. The PE reference voltage level is compatible with ECL II and ECL 10k over the specified temperature range.

2. The Q4 and Q4 output levels are compatible with ECL II and ECL 10k over the specified temperature range.

The TTL/CMOS output has a free collector, and the high state output voltage will depend on the supply that the collector load is taken to. This should not exceed +12V.

Set up time is defined as the minimum time that can elapse between a L—H transition of a control input and the next L—H clock pulse transition to ensure that the ÷10 mode is forced by that clock pulse.

Release time is defined as the minimum time that can elapse between a L—H transition of a control input and the next L—H clock pulse transition to ensure that the +11 mode is forced by that clock pulse.

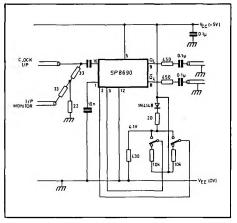

Fig.3 TTL/CMOS interface

Fig.4 ECL 10K output interface

Fig.5 Test circuit for dynamic measurements

## ABSOLUTE MAXIMUM RATINGS

Supply voltage[Vcc—Vɛɛ] Input voltage Vın d.c.

Output current lout (Q4 & Q4)

10mA

Maximum junction temperature

150°C

Storage temperature range

-55°C to +150°C

V8 Not greater than the supply voltage in use 10mA