# SP8000 SERIES HIGH SPEED DIVIDERS

## SP8685 A, B&M UHF PROGRAMMABLE DIMDER 500MHz ÷ 10/11

The SP8685 A, B & M are high speed programmable – 10/11 counters operating at an input frequency of up to 500 MHz over the temperature ranges - $55^{\circ}$ C to +125^{\circ}C ('A' grade), 0^{\circ}C to +70^{\circ}C ('B' grade) and -40^{\circ}C to +85^{\circ}C respectively.

The clock input is biased internally and is coupled to the signal source by a capacitor. The input signal path is completed by an input reference decoupling capacitor which is connected to earth.

The division ratio is controlled by two PE inputs. The counter will divide by 10 when either input is in the high state, and by 11 when both inputs are in the low state. These inputs are compatible with standard ECL 10K inputs and have the same temperature characteristics. Both inputs have nominal 4.3K2 internal pulldown resistors.

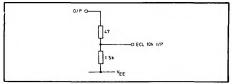

The true and inverse outputs- are compatible with standard ECL II outputs. They may be used to drive ECL 10K circuits by the inclusion of two resistors as shown in Fig. 4.

When using the device as a divide-by-ten prescaler the inverse output (o/p) should be connected to a PE input.

| Clock<br>Pulse | <b>Q</b> 1 | Q <sub>2</sub> | Ο,         | Q₄  |

|----------------|------------|----------------|------------|-----|

| 1              | L          | н              | н          | н   |

| 2              | L          | L              | н          | н   |

| 3              | L          | L              | L          | н   |

| 4              | н          | L              | L          | н   |

| 5              | н          | н              | L          | н   |

| 6              | L          | н              | н          | L   |

| 7              | L          | L              | н          | L   |

| 8              | L          | L              | L          | L   |

| 9              | н          | L              | L          | L   |

| 10             | _ H_       | н_             | _ <u>L</u> | _ L |

| 11             | LH.        | <u> </u>       | <u> </u>   | 규브리 |

Table 1 Count sequence Extra state

| PE, | PE2 | Div<br>Ratio |  |  |

|-----|-----|--------------|--|--|

| L   | L   | 11           |  |  |

| H   | L   | 10           |  |  |

| L   | H   | 10           |  |  |

| H   | H   | 10           |  |  |

Table 2 Truth table for control inputs

Fig. 1 Pin connections

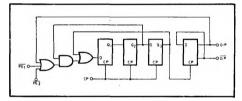

Fig. 2 Logic diagram SP8685

#### FEATURES

- Full temperature range operation:

- 'A' grade 55°C to +125°C

- 'B' grade 0°C to +70°C

- 'M' grade -40°C to +85°C

- Self Biasing CP Input

- Wide Input Dynamic Range

- Control Inputs ECL 10K Compatible

- Low Propagation Delay

- True and Inverse Outputs Available

#### ABSOLUTE MAXIMUM RATINGS

| Power supply voltage $V_{CC} - V_{EE}$ | 0V to +8V             |  |  |

|----------------------------------------|-----------------------|--|--|

| Input voltage, PE inputs               | 0V to V <sub>CC</sub> |  |  |

| Input voltage, CP input                | 2V peak-to-peak       |  |  |

| Output current                         | 20mA                  |  |  |

| Operating junction temperature         | +150°C                |  |  |

| Storage temperature                    | –55°C to +150°C       |  |  |

#### SP8685

### ELECTRICAL CHARACTERISTICS

PE inputs - ECL 10K compatible

Outputs - ECL II compatible

Test conditions (unless otherwise stated)

Tamb 'A' grade -55°C to +125°C

'B' grade 0°C to +70°C 'M' grade -40°C to +85°C

Supply voltages:  $V_{CC} = +5.2V \pm 0.25V$  $V_{EE} = 0V$

Clock input voltage: 400mV to 800mV (p-p)

|                                      | Value     |      |            | 11-10- | Conditions                                                                               |  |

|--------------------------------------|-----------|------|------------|--------|------------------------------------------------------------------------------------------|--|

| Characteristic                       | Min. Typ. |      | Max. Units |        | Conditions                                                                               |  |

| Max i/p frequency                    | 500       |      |            | MHz    | V <sub>cc</sub> = +5.2V                                                                  |  |

| Min i/p frequency                    | 1         |      | 40         |        | Sinewave Input                                                                           |  |

| Min, slow rate for square wave input |           |      | 100        | V/µs   |                                                                                          |  |

| Propogation delay                    |           |      |            |        | [                                                                                        |  |

| (clock i/p to device o/p)            |           | 4    | 1          | ns     |                                                                                          |  |

| PE input reference level             |           | +3.9 |            | v      | V <sub>cc</sub> = +5.2V, 25 <sup>°</sup> C<br>V <sub>cc</sub> = +5.2V, 25 <sup>°</sup> C |  |

| Power supply drain current           |           | 45   | 60         | mA     | V <sub>cc</sub> = +5.2V, 25°C                                                            |  |

| PE input pulldown                    |           |      |            |        |                                                                                          |  |

| Resistors                            |           | 4.3  |            | ΚΩ     |                                                                                          |  |

| Clock i/p impedance                  |           |      |            |        |                                                                                          |  |

| (i/p to i/p ref low frequency)       |           | 400  |            | Ω      |                                                                                          |  |

#### APPLICATION NOTES

Fig. 4 SP8685 output – ECL 10K i/p and ECLII (or ECL 10K o/ps unloaded) – ECL 10K i/p

Fig. 5 TTL o/p - SP8685 PE i/p; SL8685 o/p - TTL i/p. (Total delay from SP8685 clock i/p to Schottky gate o/p = 15ns, typ.)

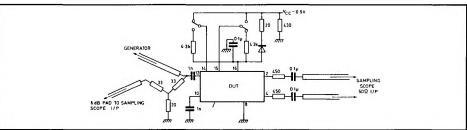

Fig. 3 Test circuit

At an input frequency of 500 MHz the control loop delay time (SP8685 o/p to PE i/p) is approximately 16 ns. This will be a severe problem if TTL is used in the control loop.

Fig. 7 Divide-by-20/21. Control loop delay time approximately 30ns using SP1034.