- Meets or Exceeds the Standards Set by ISO 8802.3:1990 and ANSI/IEEE 802.3-1990

- Receiver Squelch Circuit Integrity Improved With Noise Filter

- Differential (Twisted-Pair) I/O Driver and Receiver

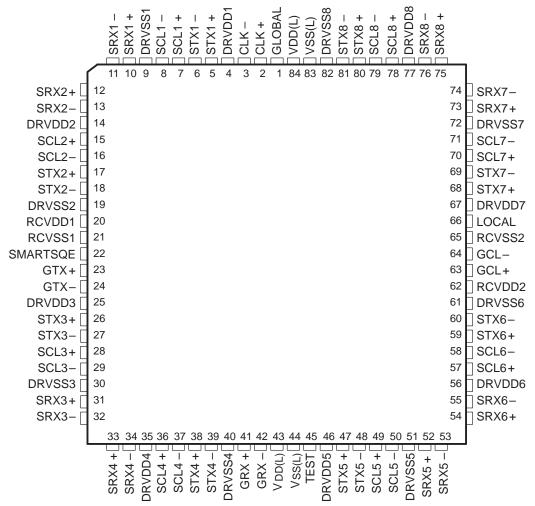

- 84-Pin, Plastic Leaded Chip Carrier (PLCC)

Package

- Control Logic Function for Local and Global Modes

- Low Port-to-Port Data Propagation Delay

- Drives Twisted-Pair Transmission Lines Up to 50 Meters

- Collision Detection for Multiple-User Networks

#### description

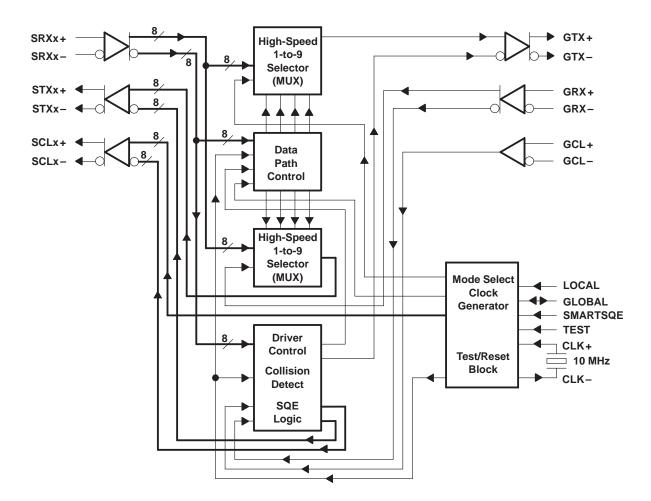

The SN75LBC088 attachment unit interface (AUI) concentrator chip (ACC) incorporates eight data terminal equipment (DTE) or station ports and one medium attachment unit (MAU) or global port on the same chip for connection to a local area network (LAN). Each station port emulates the driver/receiver functionality, timing, and signal response of a transceiver or MAU designed to meet the IEEE 802.3-1990 standard. The functional components of the ACC are a differential driver, collision detection driver, and a differential line receiver/squelch.

#### description (continued)

This device also has two operational modes, local and global, and a self-exerciser test mode. The SN75LBC088 uses the LinBiCMOS<sup>™</sup> process technology to ensure high-speed operation, analog precision, and low power consumption.

Each of the eight station ports includes two differential drivers (STX1 thru STX8 [STXx] and SCL1 thru SCL8 [SCLx]) and one differential receiver [SRX1 thru SRX8 (SRXx)]. The SRXx (station receive) input pair is for receiving data sent from the station to the network. The STXx (station transmit) output pair is for transmitting network data to the station. The SCLx (station collision) output pair transmits the collision condition to the station.

The global port supports one differential driver (GTX) and two differential receivers (GRX and GCL). The GTX output pair drives data from a station port to the network. The GRX input pair receives network data from the external transceiver and channels it to all eight station ports. The GCL input pair receives network collision status to be forwarded to the individual station ports.

Each station port differential output pair of the SN75LBC088 drives a  $78-\Omega$ , balanced, terminated, twisted-pair transmission line up to 50 meters. In the off or idle state, the drivers maintain minimal differential output voltage on the twisted-pair lines and remain within the required output common-mode range. When the driver is internally enabled, the driver goes through what is called a soft start or half-step driver start up due to the first transition out of idle swings only half the normal differential amplitude. The differential outputs then rise to full amplitude output levels within 35 ns. The output amplitude is maintained for the remainder of the packet. After the last transmitted packet positive edge, the driver's enable circuit maintains the differential potential above the output common-mode voltage for at least 210 ns, decay down to a minimum differential voltage, and then return to an idle state. Each driver powers up in the idle state to ensure no activity is placed on the twisted-pair cable that could be interpreted as network traffic.

The line receiver squelch function interfaces to a differential twisted-pair line terminated external to the device. The receiver squelch circuit allows differential receive signals to pass through while the input amplitude and pulse duration are greater than the minimum squelch threshold. This ensures a good signal-to-noise ratio while the data path is active and prevents system noise from causing false data transitions during line shut-down and line-idle conditions.

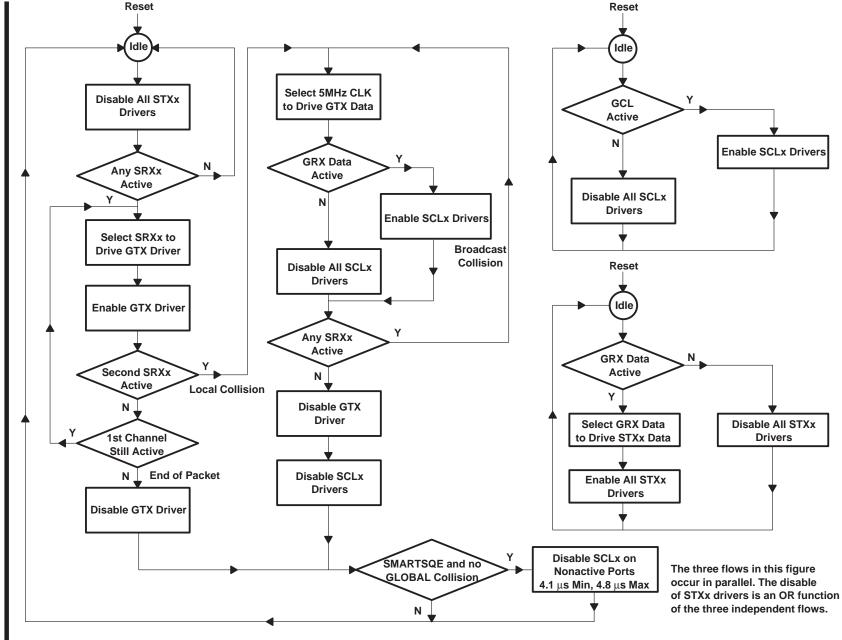

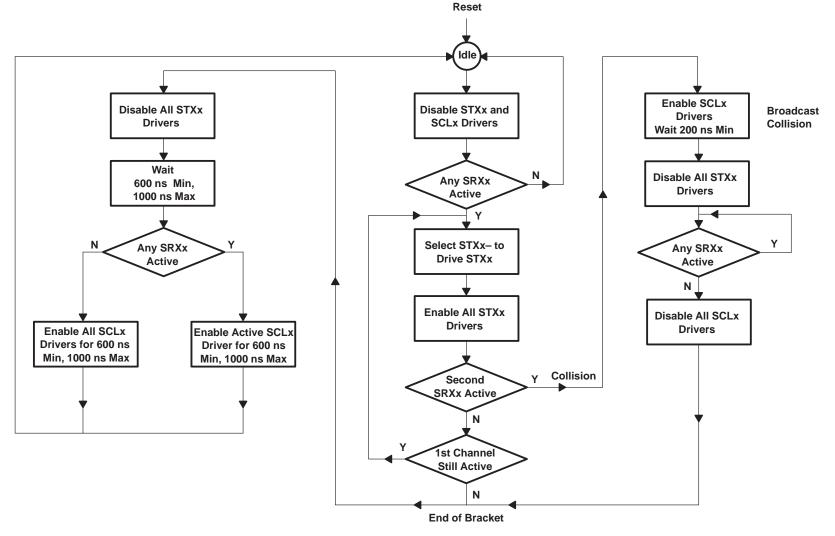

The SN75LBC088 functional control logic operates in two externally switched modes, local and global. Depending on the selected mode, the internal control logic selects the proper internal data path routing and collision handling. The internal data path is altered prior to enabling external line drivers to prevent data transmissions occurring during data path multiplexing.

Local mode is the simplest of the two modes of operation. While all SRXx input receivers from the stations are inactive, the device is in an idle state. The idle state disables all the STXx and SCLx output drivers to the stations. While in local mode, all control signals to and from the global port are logically disabled by the control logic. When transmit activity is detected on any of the eight SRXx input receivers, the channel's internal squelch goes high. While this condition exists, the single SRXx receiver is routed to all STXx drivers. When the transmission is complete, the channel's internal squelch returns low. This starts an end-of-packet hold on all the STXx output drivers. The driver switches to the idle state after the hold time has elapsed. During the specified squelch (SQE) test interval, the SN75LBC088 internally generates a SQE test burst. When Smart SQE is enabled (SMARTSQE pulled low), the SQE test burst is sent to the SCLX output of the station that transmitted last. If Smart SQE is not enabled, it sends the burst to all the SCLx outputs. The device recognizes a collision when one station is active and any other station(s) becomes active. The device then places a 10-MHz collision signal on all the SCLx output drivers. All STXx data is considered undefined during a collision. The STXx drivers are shut down while the SCLx drivers are active and are not reactivated until all SRXx receiver activity is finished. The device returns to the idle state after all transmit traffic has ceased.

LinBiCMOS is a trademark of Texas Instruments Incorporated.

SLLS150A - DECEMBER 1992 - REVISED MAY 1993

#### description (continued)

In global mode, the local station users are logically connected to the LAN backbone media. Global mode has two types of signal flow patterns: station to other stations and the LAN, and the LAN to all stations. When a station starts to transmit, its squelch deactivates and is considered active. The control logic then selects the active channel's data for transmission to the LAN. Unlike the local mode, the other stations do not get the data directly from the active port. Data first reaches the transceiver, gets looped back, and then is sent to the eight STXx drivers. This action emulates the operation between a station and a transceiver in a normal point-to-point link.

In global mode, local and global collisions are handled differently. For a local collision, the device cannot force a collision on the LAN backbone directly. To create a collision on the LAN, the device transmits a 5-MHz signal onto the GTX drivers to force activity on the LAN segment. Any LAN activity collides with this forced 5-MHz signal and is seen as a collision by the collision receiver. This action keeps the network synchronized. After the global port's data loops back from the LAN, the collision signal is sent to all the local nodes via the SCLx output drivers.

A global collision (collision on the network) is handled normally since station transmit data is routed to the GTX driver. In this instance, data sources are directly in collision. Once a collision is detected on the network, the transceiver asserts a collision signal that is detected on the GCL input receiver. The GCL receiver collision signal is then routed to all the SCLx output drivers tied to the stations.

In global mode, the transceiver generates SQE. When a station finishes a transmission, the transceiver generates the SQE. This is detected on the GCL input. When Smart SQE is enabled (SMARTSQE pulled low), the SQE is sent to the station that originated the transmission. Because of this activity, the ACC has to remember which station transmitted the last signal and only allow collision back to that station during the SQE window. Once the SQE passes, the ACC then allows a collision signal back to all stations to indicate a network collision. When Smart SQE is disabled, the SQE signal is routed to all station collision lines (SCLx).

The SN75LBC088 supports a self-exerciser test mode. The self-exerciser mode tests all the drivers and receivers on the chip. This mode is invoked by pulling both GLOBAL and TEST low. While in the self-exerciser mode, a 6.4- $\mu$ s packet is generated of consistent preamble on the GTX driver port with a 6.4- $\mu$ s idle time. The GTX driver, with the help of loop back connectors, routes the preamble to both the GRX and the GCL receivers. The GRX data is then sent internally to all the STXx drivers. External connectors on the STXx drivers individually loop this data back to the local SRXx receiver. When the squelch for a receiver is turned off and the global GCL receiver is unsquelched, the collision driver for that receiver starts sending a collision signal. Each port drives a collision signal based on its own SRXx receiver squelch being held high and the presence of a global collision signal, therefore exercising all the drivers and receivers on the chip.

## functional block diagram

# **Terminal Functions**

| TER                | MINAL                             |     |                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|--------------------|-----------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME NO.           |                                   | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| CLK-               | 3                                 | 0   | Clock output. Output for an external series-resonant 10-MHz crystal required for internal timing.                                                                                                                                                                                                                                                              |  |  |  |  |

| CLK+               | 2                                 | I   | Clock input. Input for an external series-resonant 10-MHz crystal required for internal timing. The CLK+ accepts an external TTL level clock also.                                                                                                                                                                                                             |  |  |  |  |

| DRVDDx             | 4, 14, 25, 35,<br>46, 56, 67, 77  |     | V <sub>DD</sub> power supply. These terminals provide power to the drivers.                                                                                                                                                                                                                                                                                    |  |  |  |  |

| DRVSSx             | 9, 19, 30, 40,<br>51, 61, 72, 82  |     | V <sub>SS</sub> power ground. These terminals provide a ground return for the driver circuits.                                                                                                                                                                                                                                                                 |  |  |  |  |

| GCL-               | 64                                | ı   | Global collision. Differential inputs that receive the network collision status for forwarding to the                                                                                                                                                                                                                                                          |  |  |  |  |

| GCL+               | 63                                | ı   | individual station ports.                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| GLOBAL             | 1                                 | I/O | Global. This is a bidirectional terminal. When functioning as an output, the chip is in a test mode and monitors internal nodes that are multiplexed to it. When functioning as an input, the terminal is pulled low (LOCAL held high) and the station ports are connected to the LAN. This terminal is held inactive (high) with an internal pullup resistor. |  |  |  |  |

| GRX-               | 42                                | I   | Global receive. Differential inputs that receive network data from an external transceiver and route it                                                                                                                                                                                                                                                        |  |  |  |  |

| GRX+               | 41                                | I   | to all eight station ports.                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| GTX-               | 24                                | 0   | Global transmit. Differential outputs that transmit data from one of eight station ports to the network.                                                                                                                                                                                                                                                       |  |  |  |  |

| GTX+               | 23                                | 0   |                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| LOCAL              | 66                                | I   | Local. When in local mode, this terminal is pulled low (GLOBAL held high) and the station ports are disconnected from the LAN. This terminal is held inactive (high) with an internal pullup resistor.                                                                                                                                                         |  |  |  |  |

| RCVDD1             | 20                                |     | V <sub>DD</sub> power supply. These terminals provide power to the receivers.                                                                                                                                                                                                                                                                                  |  |  |  |  |

| RCVDD2             | 62                                |     |                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| RCVSS1             | 21                                |     | V <sub>SS</sub> power ground. These terminals provide a ground return for receivers.                                                                                                                                                                                                                                                                           |  |  |  |  |

| RCVSS2             | 65                                |     |                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| SCLx-              | 8, 16, 29, 37<br>50, 58, 71, 79   | 0   | Station port collision. Differential outputs that transmit the collision condition to the station. When during any station transmit activity one or more additional stations become active, the device recognizes this                                                                                                                                         |  |  |  |  |

| SCLx+              | 7, 15, 28, 36,<br>49, 57, 70, 78  | 0   | as a collision. The device then places a 10-MHz collision signal on all of the SCLx output drivers.                                                                                                                                                                                                                                                            |  |  |  |  |

| SRX-               | 11, 13, 32, 34,<br>53, 55, 74, 76 | I   | Station port receive. Differential input for receiving data from the station to the network.                                                                                                                                                                                                                                                                   |  |  |  |  |

| SRX+               | 10, 12, 31, 33,<br>52, 54, 73, 75 | I   |                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| STX-               | 6, 18, 27, 39,<br>48, 60, 69, 81  | 0   | Station port transmit. Differential output for transmitting network data to the the station.                                                                                                                                                                                                                                                                   |  |  |  |  |

| STX+               | 5, 17, 26, 38,<br>47, 59, 68, 80  | 0   |                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| SMARTSQE           | 22                                | I   | This input enables the smart SQE circuitry. In normal operating mode, this enables the SMARTSQE test function performed at the end of a data packet transmission. In the test mode, SMARTSQE works with TEST to place the chip into a special mode. This terminal is held inactive (high) with an internal pullup resistor.                                    |  |  |  |  |

| TEST               | 45                                | I   | Test. To invoke the self-exerciser test mode, this terminal and GLOBAL are enabled.                                                                                                                                                                                                                                                                            |  |  |  |  |

| V <sub>DD(L)</sub> | 43, 84                            |     | V <sub>DD</sub> logic power supply. These terminals provide power to the CMOS logic.                                                                                                                                                                                                                                                                           |  |  |  |  |

| VSS(L)             | 44, 83                            |     | VSS logic ground. These terminals provide power to a ground return for the CMOS logic.                                                                                                                                                                                                                                                                         |  |  |  |  |

#### **MODE CONFIGURATION**

| GLOBAL | LOCAL | SMARTSQE | TEST | CHIP CONFIGURATION   |

|--------|-------|----------|------|----------------------|

| Н      | L     | Н        | Н    | Local mode, no SQE   |

| Н      | L     | L        | Н    | Local mode with SQE  |

| L      | Н     | Н        | Н    | Global mode, no SQE  |

| L      | Н     | L        | Н    | Global mode with SQE |

| L      | Н     | Н        | L    | Self exerciser       |

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Supply voltage, V <sub>DD</sub>                      | 7 V |

|------------------------------------------------------|-----|

| Input voltage, V <sub>I</sub>                        | 6 V |

| Output voltage at any output, V <sub>O</sub>         | 6 V |

| Supply current, I <sub>CC</sub> 500 r                | mΑ  |

| Operating free-air temperature range, T <sub>A</sub> |     |

| Storage temperature range, T <sub>stg</sub>          | 5°C |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### **DISSIPATION RATING TABLE**

| PACKAGE | $T_{\mbox{A}} \le 25^{\circ}\mbox{C}$ POWER RATING | OPERATING FACTOR<br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 70°C<br>POWER RATING |

|---------|----------------------------------------------------|-------------------------------------------------|---------------------------------------|

| FN      | 3.0 W                                              | 0.024 W/°C                                      | 1.92 W                                |

## recommended operating conditions

|                                             |                                            | MIN  | NOM | MAX   | UNIT |

|---------------------------------------------|--------------------------------------------|------|-----|-------|------|

| Supply voltage, V <sub>DD</sub>             | DRVDDx, RCVDD1, RCVDD2, V <sub>DD(L)</sub> | 4.75 | 5   | 5.25  | V    |

| Common-mode input voltage, V <sub>IC</sub>  |                                            | 1    |     | 4.2   | V    |

| High-level input voltage, VIH               | GLOBAL, LOCAL, SMARTSQE, TEST              | 2.4  |     |       | V    |

| Low-level input voltage, V <sub>IL</sub>    | GLOBAL, LOCAL, SMARTSQE, TEST              |      |     | 0.8   | V    |

| Differential input voltage, V <sub>ID</sub> | GRX±, GCL±, SRXx±                          | ±318 |     | ±1315 | mV   |

| Operating free-air temperature, TA          |                                            | 0    |     | 70    | °C   |

# electrical characteristics over recommended operating free-air temperature and supply voltage range (unless otherwise noted)

#### drivers

|     | PARAMETER                      | TEST CONDITIONS | MIN  | MAX   | UNIT |

|-----|--------------------------------|-----------------|------|-------|------|

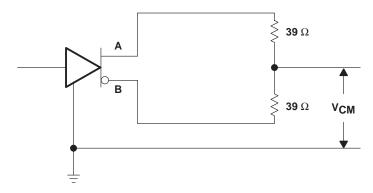

| VCM | Common-mode voltage            | See Figure 1    | 1.0  | 4.2   | V    |

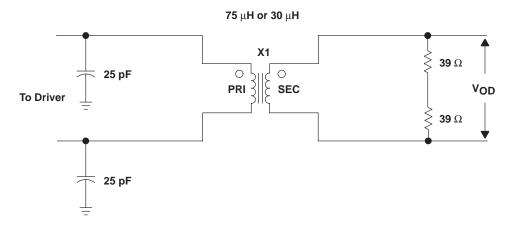

| VOD | Differential-output voltage    | See Figure 2    | ±600 | ±1315 | mV   |

|     | Idle differential voltage      | See Figure 2    |      | ±40   | mV   |

|     | Idle differential load current |                 |      | 4     | mA   |

#### receivers

|          | PARAMETER                                           | TEST CONDITIONS        | MIN  | TYP | MAX                       | UNIT |

|----------|-----------------------------------------------------|------------------------|------|-----|---------------------------|------|

|          | Differential-input threshold to disable squelch     | t > 30 ns <sup>†</sup> |      |     | V <sub>ID</sub> ><br>-275 | mV   |

|          | Differential-input threshold to not disable squelch | t < 20 ns†             |      |     | V <sub>ID</sub> < -255    | mV   |

| $V_{ID}$ | Differential-input voltage                          |                        | ±380 |     | ±1315                     | mV   |

| VIC      | Common-mode voltage                                 |                        | 1    |     | 4.2                       | V    |

| IIC      | Common-mode current                                 |                        |      |     | ±1                        | mA   |

|          | Hysteresis (threshold)                              |                        |      | ±40 | ·                         | mV   |

$<sup>\</sup>dagger$ t is the duration time that the input signal swings from its common-mode state.

#### drivers and receivers

|                    | F | PARAMETER                                  | TEST CONDITIONS | MIN MAX | UNIT |

|--------------------|---|--------------------------------------------|-----------------|---------|------|

| ICC Supply current |   | DRVDDy BCVDD4 BCVDD2 V ")                  | Steady state    | 150     | -m A |

|                    |   | DRVDDx, RCVDD1, RCVDD2, V <sub>DD(L)</sub> | Active          | 450     | mA   |

## switching characteristics

|                   | PARAMETER                                                                           | FROM<br>(INPUT)          | TO<br>(OUTPUT)                | TEST<br>CONDITIONS | MIN   | TYP | MAX | UNIT |  |

|-------------------|-------------------------------------------------------------------------------------|--------------------------|-------------------------------|--------------------|-------|-----|-----|------|--|

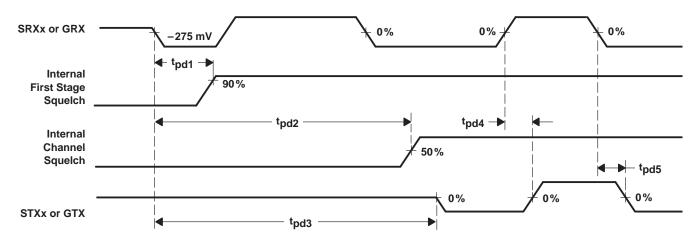

| <sup>t</sup> pd1  | Propagation delay time, internal first stage squelch (see Note 1)                   | SRXX<br>GRX              | Internal 1st<br>stage squelch | See Figure 6       | 30    |     | 65  | ns   |  |

| t <sub>pd2</sub>  | Propagation delay time, internal squelch valid (see Note 2)                         | SRXx or GRXx             | Internal channel squelch      | See Figure 6       | 130   |     | 150 | ns   |  |

| + 10              | Propagation delay time, driver startup                                              | SRXx                     | GTX, STXx                     | See Figure 6       | 150   |     | 270 | ne   |  |

| <sup>t</sup> pd3  | Propagation delay time, driver startup                                              | GRX                      | STXx                          | See Figure 6       | 150   |     | 270 | ns   |  |

|                   | Dropogation delay time atoody atota                                                 | SRXx                     | GTX, STXx                     | See Figure 6       |       |     | 35  |      |  |

| <sup>t</sup> pd4  | Propagation delay time, steady state                                                | GRX                      | STXx                          | See Figure 6       |       |     | 35  | ns   |  |

|                   | Decreasing deleviting atomic state                                                  | SRXx                     | GTX, STXx                     | Can Figure C       |       |     | 25  |      |  |

| <sup>t</sup> pd5  | Propagation delay time, steady state                                                | GRX                      | STXx                          | See Figure 6       |       |     | 35  | ns   |  |

|                   |                                                                                     | SRXx                     | GTX, STXx                     |                    | 0 5 0 |     |     |      |  |

| tsk               | Skew time, signal edge (see Note 3)                                                 | GRX                      | STXx                          | See Figure 6       |       | 2   |     | ns   |  |

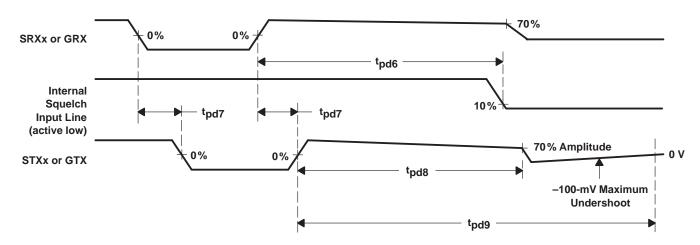

| <sup>t</sup> pd6  | Propagation delay time, last received edge to internal squelch                      | SRXx or GRX              | Internal channel squelch      | See Figure 7       | 144   |     | 200 | ns   |  |

|                   | Description delegation of the description                                           | SRXx                     | GTX, STXx                     | 0                  |       |     | 0.5 |      |  |

| <sup>t</sup> pd7  | Propagation delay time, steady state                                                | GRX                      | STXx                          | See Figure 7       |       |     | 35  | ns   |  |

| tpd8              | Propagation delay time, last positive edge out to 70% point                         | GTX, STXx                | GTX, STXx                     | See Figure 7       | 210   |     | 320 | ns   |  |

| t <sub>pd9</sub>  | Propagation delay time, driver idle from last positive edge out (see Note 4)        | GTX, STXx                | GTX, STXx                     | See Figure 7       | 0.21  |     | 8   | μs   |  |

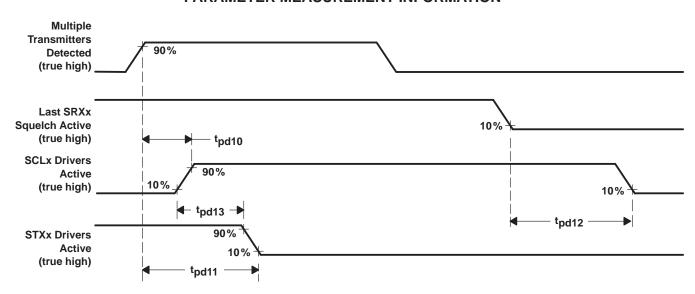

| <sup>t</sup> pd10 | Propagation delay time, collision detected to SCLx drivers active                   | SRXx                     | Collision signal active       | See Figure 8       |       |     | 320 | ns   |  |

| <sup>t</sup> pd11 | Propagation delay time, collision detected to STXx drivers inactive                 | SRXx                     | STXx drivers inactive         | See Figure 8       | 350   |     | 700 | ns   |  |

| <sup>t</sup> pd12 | Propagation delay time, last SRXx going inactive to collision signal going inactive | Last receiver inactive   | Collision drivers inactive    | See Figure 8       |       |     | 290 | ns   |  |

| <sup>t</sup> pd13 | Propagation delay time, SCLx drivers active overlap to STXx drivers active          | Collision drivers active | STXx drivers active           | See Figure 8       | 200   | _   |     | ns   |  |

NOTES: 1. The measurement is referenced to the differential input crossing the -275-mV threshold.

- 2. The first transmitted bit cell after the squelch deactivates is allowed to have bit cell timing errors. Bit cells beyond this must not be distorted.

- 3. Skew =  $t_{pd4} t_{pd5} \times t_{pd4}$  must be within  $\pm 2$  ns of  $t_{pd5}$  when measured at the 0% amplitude point. 4. Driver-idle condition exists when the output differential amplitude is less than 40 mV maximum.

Figure 1. Driver Common-Mode Voltage Test Circuit

Figure 2. Differential Driver Load Circuit

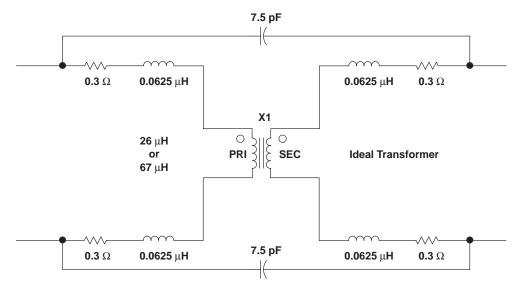

Figure 3. AUI Transformer Model

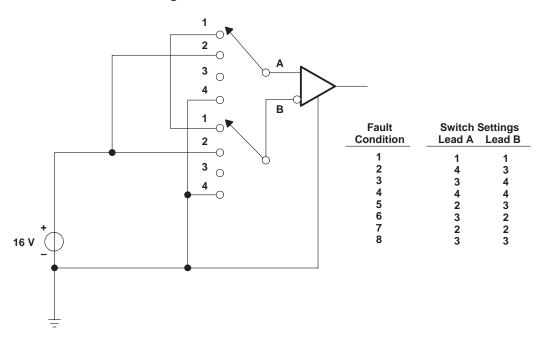

Figure 4. Driver Fault Test Circuit

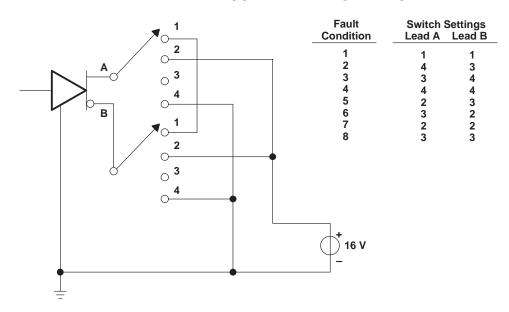

Figure 5. Receiver Fault Test Circuit

Figure 6. Differential Start-Up Sequence

Figure 7. Differential Shut-Down Sequence

Figure 8. Local Mode Differential STXx Driver Shut-Down Sequence During Collision

SLLS150A - DECEMBER 1992 - REVISED MAY 1993

Figure 10. ACC Local Mode Control Flow

ti.com 24-Jun-2005

#### PACKAGING INFORMATION

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins Package<br>Qty | Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp (3) |

|------------------|-----------------------|-----------------|--------------------|---------------------|-------------------------|------------------|-------------------|

| SN75LBC088FN     | OBSOLETE              | PLCC            | FN                 | 84                  | TBD                     | Call TI          | Call TI           |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS) or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2005, Texas Instruments Incorporated