Picture-in-Picture Processor with On-Chip PLL

# Preliminary Data

# Features

- On-chip PLL

- Full frame display for 50/60 Hz in order to increase the vertical resolution and to suppress moving artifacts.

- Compatibility to the 16:9 display format by means of independent setting of the vertical and horizontal decimation factors and the width of the border frame

- Decimation of the Y, U, V data for pictures sizes 1/9 and 1/16 with 6 bits width of the input word without rounding error

- Intermediate storage of the inset picture (on-chip-memory)

- RGB- or Y-, U-, V-signal generation

- 100% pin- and software compatible with SDA 9188X if external PLL is used

- Increased bandwith of analog outputs due to higher output currents

- New select function for multi-PIP feature

| Туре        | Ordering Code | Package                    |  |  |

|-------------|---------------|----------------------------|--|--|

| SDA 9188-3X | Q67100-H5142  | P-DSO-28-3 (350 mil) (SMD) |  |  |

# **Functional Description**

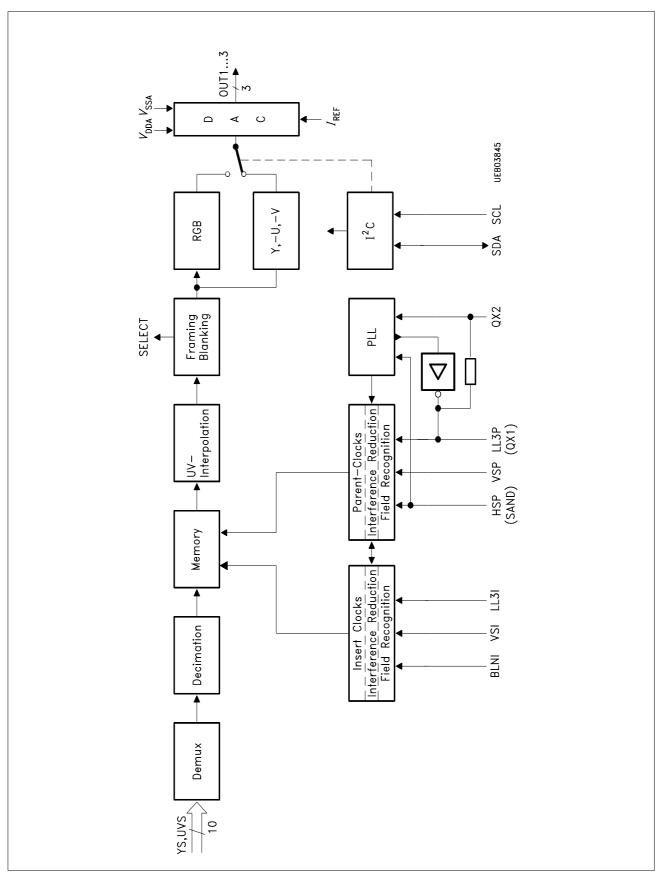

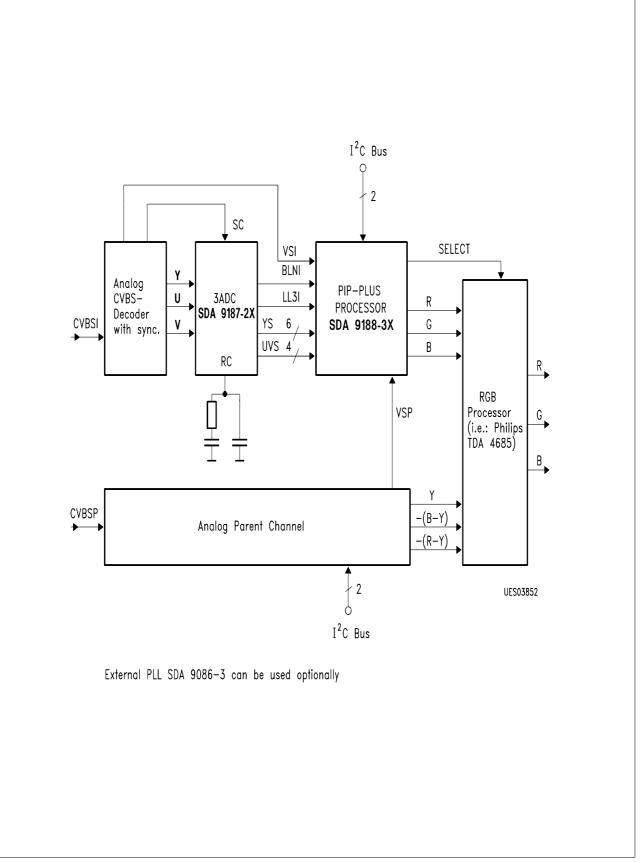

The SDA 9188-3X Picture-in-Picture (PIP) processor with on-chip PLL combines two asynchronous picture sources so that a small moving picture (the inset picture) can be superimposed in a moving picture of normal size (the parent picture).

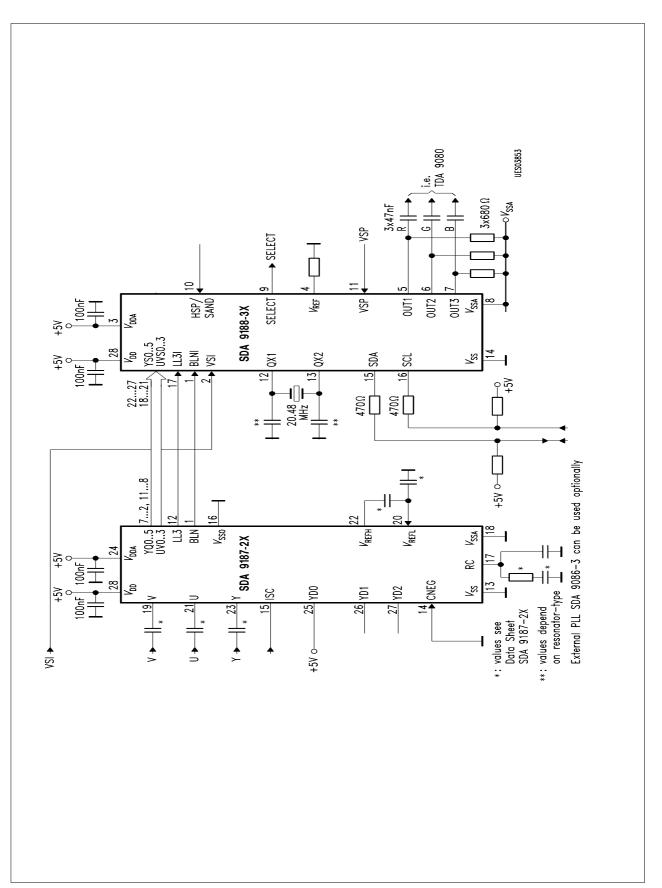

The components of the video signal of the inset source have to be fed in a digitized form to the SDA 9188-3X (**figure 1**). Amplitude resolution of the signal components is 6 bit at a sampling rate of 13.5 MHz for the luminance signal and 3.375 MHz for the chrominance signals.

1

SDA 9188-3X

MOS IC

The PIP processor SDA 9188-3X handles picture reduction (decimation with horizontally and vertically acting filters), intermediate data storage in an integrated image memory (169.812 bits) as well as the output of the decimated picture.

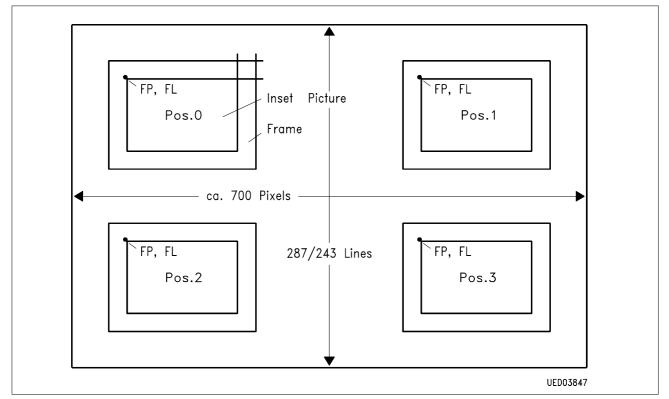

The picture can be set 1/9 or 1/16 of its original size. In order to indicate the border between parent picture and inset picture the inset picture can be surrounded with a frame: its width is adjustable in 2 stages and its brightness in 16 stages. Different signal sources can be identified by using different framing colors. The four corners of the parent picture are possible positions for the inset picture. The inset picture can also be inserted as a still picture, independently of the parent picture.

The output signals of the SDA 9188-3X are analog. Either RGB or Y, U, V signals can be output, whereby a 6-bit broadband conversion is obtained for all components. Clamping for RGB output signal is performed in an RGB processor (e.g. TDA 4685).

Only a few additional devices are required for a complete picture-in-picture system. **Application circuits 1a and 1b** illustrate the use of the PIP device.

If the CVBS input signal is to be decoded using an analog color decoder for the PIP, the analog/ digital interface for the inset picture (3 A/D Converter, SDA 9187-2X) performs the conversion of the Y, U, V components into digital signals as well as the generation of the inset clocks BLNI and LL3I.

The SDA 9188-3X processes both 50 Hz/625 and 60 Hz/525 line signals. The field frequency can be 50/60 Hz or 100/120 Hz. For systems with Siemens Dig TV Featurebox a field frequency of 100 Hz or 120 Hz is also possible by doubling the clock frequency LL3P (LL1.5P). Frame mode display with 50 Hz or 60 Hz can also be set via the I<sup>2</sup>C bus. Adaptation to the number of lines occurs automatically. If the field frequency in the parent and inset channels are different, artifacts may result in the picture.

Synchronization with the parent channel is performed via the horizontal and vertical sync signals HSP/SAND and VSP. The clock fequency is 13.5 MHz (LL3P) without standard conversion and 27 MHz (LL1.5P) with standard conversion (100/120 Hz). The display clock is generated on chip. Optionally the external clock generator SDA 9086-3 can be used in the same way as with the SDA 9188X.

The horizontal and vertical sync signals BLNI and VSI plus the LL3I clock (13.5 MHz) are used for synchronization with the inset source.

The interface between inset and parent channel is done by the on-chip memory. The memory write access is controlled by the inset clock and the read access is controlled by the parent clock.

The SELECT output signal inserts the inset picture into the parent picture driving an external analog switch, e.g. the TDA 4685. All operation modes of the SDA 9188-3X can be controlled via the I<sup>2</sup>C bus. Nine registers can be used.

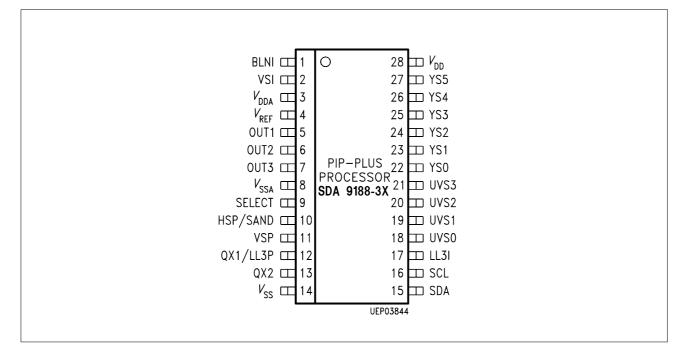

#### **Pin Configuration**

(top view)

# **Pin Definitions and Functions**

| Pin No. | Symbol            | Function                                              | Descriptions                                                                   |

|---------|-------------------|-------------------------------------------------------|--------------------------------------------------------------------------------|

| 1       | BLNI              | Blanking inset                                        | Inset line synchronization                                                     |

| 2       | VSI               | Vertical synchronous inset                            | Inset field synchronization                                                    |

| 3       | V <sub>DD A</sub> | Analog supply                                         | $V_{\rm DD}$ -power supply for D/A converter and PLL                           |

| 4       | V <sub>REF</sub>  | Reference voltage                                     | External resistor can be used for generation of the internal reference voltage |

| 5-7     | OUT1-OUT3         | Analog R, G, B, Y, -U, -V-<br>outputs                 | Analog RGB or YUV outputs                                                      |

| 8       | V <sub>SS A</sub> | Analog ground                                         | Ground for D/A converter and PLL                                               |

| 9       | SELECT            | SELECT                                                | Valid signals at OUT1-OUT3                                                     |

| 10      | HSP/SAND          | Horizontal synchronous/<br>Sandcastle parent          | Parent line synchronization                                                    |

| 11      | VSP               | Vertical synchronous parent                           | Parent field synchronization                                                   |

| 12      | LL3P/QX1          | Line locked clock parent/<br>Output of the oscillator | Parent system clock or to be connected to the crystal                          |

| 13      | QX2               | Input of the oscillator                               | To be connected to the crystal                                                 |

| 14      | V <sub>SS</sub>   | Digital ground                                        | Ground                                                                         |

| 15      | SDA               | Serial Data                                           | I <sup>2</sup> C Data                                                          |

| 16      | SCL               | Serial Clock                                          | I <sup>2</sup> C Clock                                                         |

| 17      | LL3I              | Line locked clock inset                               | Inset system clock                                                             |

| 18-27   | UV0-UV3,<br>Y0-Y5 | UV, Y-Data                                            | Digital YUV input data                                                         |

| 28      | V <sub>DD</sub>   | Digital supply                                        | V <sub>DD</sub> supply                                                         |

## Block Diagram

Semiconductor Group

#### **Circuit Description**

#### Data Transfer

The digital data are transferred under the control of LL3I, BLNI and VSI on pins YS0-YS5 and UVS0-UVS3. The decimated data are stored automatically. Either R, G, B, or Y, -U, -V analog signals are available at the outputs OUT1-OUT3. The validity of the signals is identified by SELECT = 1. In a digital system environment the input is controlled by LL3P, HSP and VSP.

#### **Inset Data Reduction**

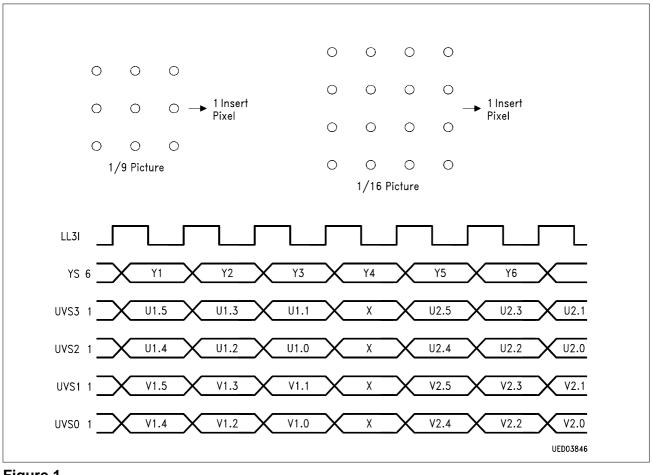

The data rate at the inputs YS0-YS5, UVS0-UVS3 is 13.5 MHz in multiplexed format, see figure 1.

In order to reduce the quantity of data which have to be stored and to prevent artifacts in the inset picture, nine pixels are processed into one inset pixel for a 1/9 picture. For the 1/16 picture 16 pixels are processed into one inset pixel.

This is done by horizontal and vertical averaging of pixels:

The characteristic of decimation for the luminance signal is 1-1-1 for 1/9- and 1-1-1-1 for 1/16 picture. Crominance signal: 1-2-1 for 1/9 and 1-1-1-1 for 1/16 picture.

#### Figure 1 Input Data Format

During the decimation process the following parts of the original picture are processed:

| ne 36 302; Pixel 13 636 |

|-------------------------|

| ne 26 256; Pixel 13 636 |

|                         |

| ne 36 303; Pixel 17 640 |

| ne 26 257; Pixel 17 640 |

| ne 26<br>ne 36          |

## **Temporary Storage of Inset Picture**

The PIP memory has a capacity of 169.812 bits. The memory organisation is  $89 \times 212 \times 9$  bits.

Data are written in with the inset and read out with the parent clock frequency.

For standard video signals with 50 or 60 Hz a full frame display is possible. To assure a correct display of the two fields, the control of the memory is done dependendly of the field and the phase relation of the Inset and Parent channel. Frame mode display is only possible for standard 50 Hz/ 60 Hz video signals. Certain VCR-functions (e.g. fast forward-mode), non interlaced signals and 50 Hz/60 Hz mixed-mode would cause inacceptable picture distortions. Under these conditions the SDA 9188-3X switches automatically into field mode display.

Also freezed pictures can only be displayed in the field-mode.

## **Output of Data in Parent Window**

The four corners of the parent picture are foreseen as positions for inserting the inset picture. To enable compatibility to different system configurations, readout from memory can be shifted horizontally in 63 steps by max. 252 LL3P cycles and vertically in 15 steps by max. 30 lines in the parent field setting the control bits RDH and RDV in control register 2 and 3.

The coordinates BRP, BRL of the normal location of all four insertion positions are given in **table 3** for RDH = RDV = 8.

The SELECT signal goes high during the display of the inset picture. Outside of the inset picture SELECT signal is low and the analog outputs OUT1-OUT3 provide the black level. The external wiring can produce a delay between the SELECT signal and the analog outputs. This delay can be compensated by bits SD0-SD2 in register 2 via the I<sup>2</sup>C bus.

A frame with one of eight colors can be inserted using control bits FRON, COL0-2. The width of the frame is fixed by FRWV at three or two lines and by FRWH at six or four pixels. The brightness can be adjusted in 16 stages.

## Figure 2 Insertion Positions of Inset Picture

# Table 3Display of Inset Picture

| Position | TV Standard (Parent)<br>(Frame Line Number) | Picture<br>Size | Location of Top Left Corner Point<br>for FRWH = 1, FRWV = 1 |     |               |  |  |

|----------|---------------------------------------------|-----------------|-------------------------------------------------------------|-----|---------------|--|--|

|          |                                             |                 | TV Line<br>(FL)                                             |     | Pixel<br>(FP) |  |  |

|          |                                             |                 | NINT                                                        | INT |               |  |  |

| 0        | 625                                         | X               | 57                                                          | 29  | 54            |  |  |

| 0        | 525                                         | Х               | 41                                                          | 21  | 54            |  |  |

| 1        | 625                                         | 1/9             | 57                                                          | 29  | 448           |  |  |

| 1        | 525                                         | 1/9             | 41                                                          | 21  | 448           |  |  |

| 1        | 625                                         | 1/16            | 57                                                          | 29  | 502           |  |  |

| 1        | 525                                         | 1/16            | 41                                                          | 21  | 502           |  |  |

| 2        | 625                                         | 1/9             | 365                                                         | 183 | 54            |  |  |

| 2        | 525 *                                       | 1/9             | 293                                                         | 147 | 54            |  |  |

| 2        | 625                                         | 1/16            | 409                                                         | 205 | 54            |  |  |

| 2        | 525 *                                       | 1/16            | 333                                                         | 167 | 54            |  |  |

|   | TV Standard (Parent)<br>(Frame Line Number) | Picture<br>Size | Location of Top Left Corner Point<br>for FRWH = 1, FRWV = 1 |     |               |  |

|---|---------------------------------------------|-----------------|-------------------------------------------------------------|-----|---------------|--|

|   |                                             |                 | TV Line<br>(FL)                                             |     | Pixel<br>(FP) |  |

|   |                                             |                 | NINT                                                        | INT |               |  |

| 3 | 625                                         | 1/9             | 365                                                         | 183 | 448           |  |

| 3 | 525 *                                       | 1/9             | 293                                                         | 147 | 448           |  |

| 3 | 625                                         | 1/16            | 409                                                         | 205 | 502           |  |

| 3 | 525 *                                       | 1/16            | 333                                                         | 167 | 502           |  |

Pixel data related to positive HSP edge

Line data related to positive VSP edge

\* If the System is in the 50/60 Hz mixed mode RDV in Register 2 is forced to the logical "0" state.

If FRWV is set to "0" during the INT Mode the inset position will be shifted by one line.

The width of the borderframe is depending on the programming of the bits FRWV and FRWH (in Register 5) 3 or 2 lines and 6 or 4 pixels.

The pixels and line number of the inset picture depend on the standard of the inset channel and on the selected picture size.

#### Table 1 Inset Picture Size

| Picture | TV Standard (Inset) |     | Line Number L |    |    |

|---------|---------------------|-----|---------------|----|----|

| Size    | (Frame Line Number) | Y   | U             | V  |    |

| 1/9     | 625                 | 212 | 53            | 53 | 88 |

| 1/9     | 525                 | 212 | 53            | 53 | 76 |

| 1/16    | 625                 | 160 | 40            | 40 | 66 |

| 1/16    | 525                 | 160 | 40            | 40 | 57 |

#### Interpolation of Chrominance Data Rate to Luminance Data Rate

To avoid chrominance artifacts after D/A conversion and for digital RGB conversion, the data rate of the chrominance signals is quadrupled in order to match the luminance data rate. This is done by repeating the chrominance data twice followed by low-pass filtering.

## RGB, Y, U, V Outputs

A digital RGB matrix converts the Y, U, V data in R, G, B data.

The equation of the implemented RGB Matrix are:

R = Y + 0.75 V

G = Y - 0.375 V - 0.1875 U

$\mathsf{B}=\mathsf{Y}+\mathsf{U}$

For a signal with 100 % white and 75 % color saturation the amplitudes of the analog input signals have to be set according the following relation:

Y / U / V = 0.72 / 0.95 / 1

By means of an internal switch at the output of the RGB matrix it is possible to by-pass the matrix with the digital data for Y, U and V and feed them directly into the D/A converters. During this operation mode the chrominance data U and V will be inverted.

## D/A Conversion

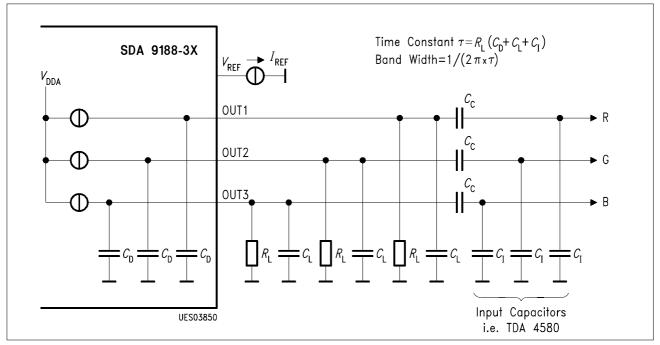

SDA 9188-3X includes three 6-bits D/A converters. Each D/A converter delivers a current through an external resistor that is to be connected between OUT1-OUT3 and  $V_{SSA}$ . The resistor value determines the output voltages (**see application circuit**). The assignment of outputs OUT1-OUT3 to R, G, B and Y, U, V is shown in **table 5**. It is possible to change the output voltage via I<sup>2</sup>C bus **Register 4**.

The tolerances of the output voltages can be reduced significantly if the resistor at  $V_{\text{REF}}$  is replaced by means of a constant current source.

# Table 5Assignment of Output Signals to OUT1-OUT3

| Output | RGB | YUV |  |

|--------|-----|-----|--|

| OUT1   | R   | – V |  |

| OUT2   | G   | Y   |  |

| OUT3   | В   | – U |  |

## Borderframe

The width of the border frame can be adjusted in two steps, the intensity of the frame can be set in 16 steps via the I<sup>2</sup>C bus.

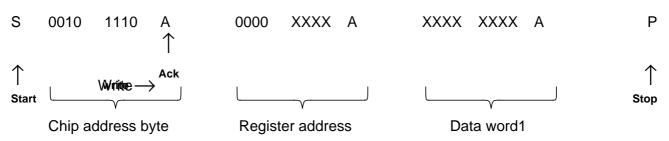

## I<sup>2</sup>C BUS

#### Organization of I<sup>2</sup>C Bus Registers

SDA 9188-3X has the device address

$00101110 = 2E_H$

Applying the supply voltage  $V_{DD}$  produces a power-up reset. The bus lines SDA and SCL are enabled. All bits in the registers except bit PL27 (D3 in Register 0) are set to 0. Bit PL27 is set to 1.

The I<sup>2</sup>C bus interface works as a slave receiver and only functions if the inset clock LL3I is available.

#### Write Operation

After writing a byte into any register, the register address is automatically incremented for the write access to the next register.

The following table shows the functions that can be set on the  $I^2C$  bus and define the data bytes. Not used data bits have to be written with "0". Before PON = 1 all other bits have to be defined in relation to the used hardware.

| Function  | SUB-    |        |        |       |         |         |         |         |         |

|-----------|---------|--------|--------|-------|---------|---------|---------|---------|---------|

|           | address | D7     | D6     | D5    | D4      | D3      | D2      | D1      | D0      |

| CONTROL 0 | 00      | 0      | 0      | STILL | SIZE    | PL27    | NINT    | OUT     | PON     |

| CONTROL 1 | 01      | 0      | 0      | 0     | FRY     | COL2    | COL1    | COL0    | FRON    |

| CONTROL 2 | 02      | 0      | SD2    | SD1   | SD0     | RDV 3   | RDV 2   | RDV 1   | RDV 0   |

| CONTROL 3 | 03      | POS 1  | POS 0  | RDH 5 | RDH 4   | RDH 3   | RDH 2   | RDH 1   | RDH 0   |

| CONTROL 4 | 04      | CON0   | CON1   | CON2  | CON3    | 0       | SOP     | PLLOFF  | HSP5    |

| CONTROL 5 | 05      | DECVER | DECHOR | FRWV  | FRWH    | PMOD1   | PMOD0   | IMOD1   | IMOD0   |

| CONTROL 6 | 06      | FRAME  | STATI  | VSIIS | VSIDEL4 | VSIDEL3 | VSIDEL2 | VSIDEL1 | VSIDEL0 |

| CONTROL 7 | 07      | AMSEC  | STATP  | VSPIS | VSPDEL4 | VSPDEL3 | VSPDEL2 | VSPDEL1 | VSPDEL0 |

| CONTROL 8 | 08      | 0      | 0      | 0     | FRYEN   | FRY5    | FRY4    | FRY3    | FRY2    |

| CONTROL 9 | 09      | 0      | PLLTC  | SOS   | VCOSEL3 | VCOSEL2 | VCOSEL1 | VCOSEL0 | 0       |

## Table 6: I<sup>2</sup>C Bus Register

The bits are numbered in the reverse order to the data stream of the I<sup>2</sup>C bus.

If the control software addresses the internal register number 8 or 9 there is no longer any software compatibility to the devices SDA 9088-2 and SDA 9089X. This is caused by the fact that in these devices register 0 and 1 can also be accessed via the subaddress 08 and 09.

# Register 0 (Address 00<sub>H</sub>)

| Bit    | Function                                | Name  | Remarks                                                                               |

|--------|-----------------------------------------|-------|---------------------------------------------------------------------------------------|

| d0     | 0 = PIP OFF<br>1 = PIP ON               | PON   | If d0 = 0, no SELECT generated<br>PON = 1 should be set after the initialization      |

| d1     | 0 = Y, -U, -V<br>1 = RGB                | OUT   | Output format                                                                         |

| d2     | 0 = Normal picture<br>1 = Double scan   | NINT  | Reproduction mode                                                                     |

| d3     | 0 = 13.5 MHz PLL<br>1 = 27 MHz PLL      | PL27  | Switching of the clock prescaler of the PLL for 50/60 Hz or 100/120 Hz operation mode |

| d4     | 0 = 1/9<br>1 = 1/16                     | SIZE  | Picture size; if d4 = 0 the picture size depends on DECHOR, DECVER in Register 5      |

| d5     | 0 = normal picture<br>1 = still picture | STILL | Still/moving picture                                                                  |

| d6, d7 | not assigned                            |       |                                                                                       |

# Register 1 (Address 01<sub>H</sub>)

| Bit   | Function                                                                                                                                                                                   | Name          | Remarks                 |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------------------|

| d0    | 0 = without frame<br>1 = with frame                                                                                                                                                        | FRON          | FRON                    |

| d1-d3 | frame color<br>$d3 \ d2 \ d1$<br>$0 \ 0 \ 0 = blue$<br>$0 \ 0 \ 1 = violet$<br>$0 \ 1 \ 0 = green$<br>$0 \ 1 \ 1 = white$<br>$1 \ 0 \ 0 = red$<br>$1 \ 0 \ 1 = yellow$<br>$1 \ 1 = orange$ | COL0-<br>COL2 |                         |

| d4-d7 | <ul> <li>1 1 1 = cyan</li> <li>Intensity of the border frame</li> <li>1 = dark frame for white, yellow,orange and cyan bright frame for blue, violet, green and red</li> </ul>             | FRY           | Only valid if FRYEN = 0 |

| d7-d5 | 0 = bright frame for white,yellow, orange and<br>cyan<br>dark frame for blue, violet, green and red<br>without function                                                                    |               |                         |

Register 2 (Address 02<sub>H</sub>)

| Bit   | Function                                                                                                                                                                                                                                                                                                                           | Name          | Remarks                                                                                                                                                                         |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| d0-d3 | Vertical read delay<br>in HSP period         d3       d2       d1       d0         0       0       0       0       = 0         0       0       0       1       = 2         0       0       1       0       = 4         :       :       :       :         1       1       0       1       = 26         1       1       1       = 30 | RDV0-<br>RDV3 | Increment in two HSP<br>periods.<br>If POS1 = 1 is selected, i.e.<br>525-lines parent picture and<br>625-lines inset picture are displayed,<br>then RDV bits are not evaluated. |

| d4-d6 | SELECT delay<br>in<br>LL3P period<br>$d6 \ d5 \ d4$<br>$0 \ 0 \ 0 = 0$<br>$0 \ 0 \ 1 = 1$<br>$0 \ 1 \ 0 = 2$<br>$0 \ 1 \ 1 = 3$<br>$1 \ 0 \ 0 = 4$<br>$1 \ 0 \ 1 = 5$<br>$1 \ 1 \ 0 = 6$<br>$1 \ 1 \ 1 = 7$                                                                                                                        | SD0-<br>SD2   |                                                                                                                                                                                 |

| d7    | without function                                                                                                                                                                                                                                                                                                                   |               |                                                                                                                                                                                 |

# Register 3 (Address 03<sub>H</sub>)

| Bit    | Function                                                                                            | Name          | Remarks                        |

|--------|-----------------------------------------------------------------------------------------------------|---------------|--------------------------------|

| d0-d5  | Horizontal read delay<br>in LL3P period                                                             | RDH0-<br>RDH5 | Increment in four LL3P periods |

|        | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                |               |                                |

| d6, d7 | Inset picture location<br>d7 d6<br>0 0 top left<br>0 1 top right<br>1 0 down left<br>1 1 down right | POS0-<br>POS1 |                                |

Register 4 (Address 04<sub>H</sub>)

| Bit   | Function                                             | Name    | Remarks                                                                                                                                                                                                   |

|-------|------------------------------------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| d0    | 1 = TTL level at HSP                                 | HSP5    | Set to '1'                                                                                                                                                                                                |

| d1    | 0 = Internal PLL<br>1 = External PLL                 | PLLOFF  | Switching between internal and external clock generation                                                                                                                                                  |

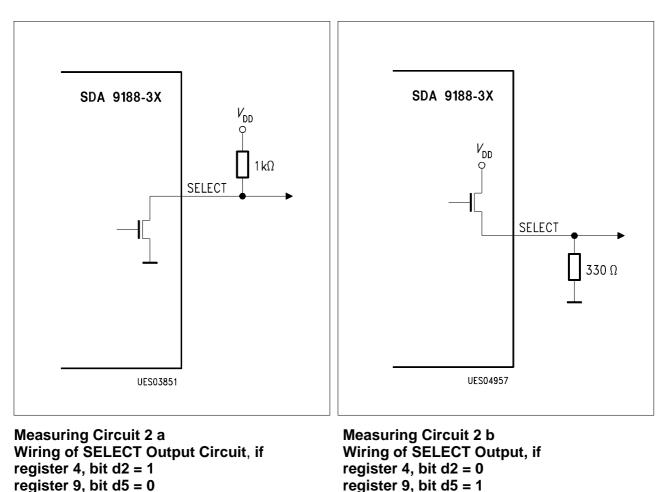

| d2    | 0 = SELECT PULLUP INTERN<br>1 = SELECT PULLUP EXTERN | SOP     | Open Drain for SELECT output                                                                                                                                                                              |

| d3    |                                                      |         | Without function, has to be set to 0                                                                                                                                                                      |

| d4-d7 | Contrast DA-Converter                                | CON 0-3 | with an external resistor of<br>10 k $\Omega$ between $V_{SS}$ and $V_{REF}$<br>the output level for (d7 d4) = 0001<br>is nearly the same as for 3.9 k $\Omega$ and<br>(d7 d4) = 0000<br>Contrast minimal |

|       | 1 1 1 1                                              |         | Contrast maximal                                                                                                                                                                                          |

Register 5 (Address 05<sub>H</sub>)

| Bit    | Function                                                                                           | Name     | Remarks                                                                                                                                |

|--------|----------------------------------------------------------------------------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------|

| d1, d0 | 00 = Automatic TV standard recognition<br>01 = 50 Hz<br>10 = 60 Hz<br>11 = Freeze the current mode | IMOD0, 1 | For multistandard applicat.<br>Fixed setting<br>Fixed setting<br>Undisturbed switching<br>during the change of the<br>received station |

| d3, d2 | same like d1, d0                                                                                   | PMOD0, 1 | as above but for the parent channel                                                                                                    |

| d4     | 0 = Frame width horizontal: 6 Pixel<br>1 = Frame width horizontal: 4 Pixel                         | FRWH     | Separated setting of the frame<br>width and height is possible<br>i.e. for 16:9 operation                                              |

| d5     | 0 = Frame width vertical: 3 lines<br>1 = Frame width vertical: 2 lines                             | FRWV     | Separated setting of the frame<br>width and height is possible<br>i.e. for 16:9 operation                                              |

| d6     | 0 = Horizontal decimation 3:1<br>1 = Horizontal decimation 4:1                                     | DECHOR   | Separated setting of the picture width and height is possible i.e. for 16:9 operation, but only if Size = 0 in Register 0              |

| d7     | 0 = Vertical decimation 3:1<br>1 = Vertical decimation 4:1                                         | DECVER   | Separated setting of the picture width and height is possible i.e. for 16:9 operation, but only if Size = 0 in Register 0              |

Register 6 (Address 06<sub>H</sub>)

| Bit   | Function                                                                     | Name   | Remarks                                                                                                                                                                                          |

|-------|------------------------------------------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| d4:d0 | Setting the delay of VSI<br>(see test circuit 6)                             | VSIDEL | Setting is possible in steps<br>of 2,37 μs (see<br>measurement circuit 6)                                                                                                                        |

| d5    | 0 = Vertical noise reduction inactive<br>1 = Vertical noise reduction active | VSIS   | Noise reduction of the VSI<br>pulse (should be set to '1'<br>under normal conditions.)                                                                                                           |

| d6    | 0 = Check for correct TV standard inactive                                   |        | If the check is active a full                                                                                                                                                                    |

|       | 1 = Check for correct TV standard active                                     | STATI  | frame display is only<br>possible if the number of<br>lines is exactly according<br>the TV standard:<br>312.5 (50 Hz)<br>262.5 (60 Hz)                                                           |

| d7    | 0 = Field display<br>1 = Frame display                                       | FRAME  | Only active if the line<br>number and the interlace<br>mode are equal for both<br>inset and parent signal.<br>If the display mode is 100/<br>120 Hz or progressive<br>scan d7 has to be set to 0 |

# Register 7 (Address 07<sub>H</sub>)

| Bit   | Function                                                                               | Name   | Remarks                                                                                                                                                                                                |

|-------|----------------------------------------------------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| d4:d0 | Delay of the VSP pulse                                                                 | VSPDEL | Setting is possible in steps<br>of 2,37 μs (50 Hz or<br>1,185 μs 100 Hz)<br>(see measuring circuit 6)                                                                                                  |

| d5    | 0 = Vertical noise reduction OFF<br>1 = Vertical noise reduction ON                    | VSPIS  | Noise reduction for the<br>vertical pulse of the parent<br>channel (should be set to<br>'1' under normal<br>conditions).                                                                               |

| d6    | 0 = Check for correct TV standard inactive<br>1 = Check for correct TV standard active | STATP  | If the check for the correct<br>TV standard is active a full<br>frame display is only<br>possible if the number of<br>lines is exactly according<br>the TV standard:<br>312.5 (50 Hz)<br>262.5 (60 Hz) |

| d7    | 0 = PAL/NTSC<br>1 = SECAM                                                              | AMSEC  | Doubling of the gain if a sufficient SECAM decoder without delay line is used                                                                                                                          |

# Register 8 (Address 08<sub>H</sub>)

| Bit   | Function                                                                                 | Name   | Remarks                                        |

|-------|------------------------------------------------------------------------------------------|--------|------------------------------------------------|

| d3:d0 | 0000 = min. brightness of the border frame<br>1111 = max. brightness of the border frame | FRY5:2 | Setting only valid if the bit d4 is set to '1' |

| d4    | 0 = brightness of the border frame can be selected by FRY                                | FRYEN  |                                                |

|       | 1 = brightness of the border frame can be selected by FRY5:2                             |        |                                                |

| d7:d5 | not used to be set to "0".                                                               |        |                                                |

Register 9 (Address 09<sub>H</sub>)

| Bit   | Function              | Name          | Remarks                                                                                                   |

|-------|-----------------------|---------------|-----------------------------------------------------------------------------------------------------------|

| d0    | -                     |               | Set to '0'                                                                                                |

| d1 d4 | VCO Nominal Frequency | VCOSEL<br>0 3 | Set to '0' under nominal conditions                                                                       |

| d5    | Select open Source    | SOS           | If d5 = 1<br>Pulldown-transistor of<br>select output is switched<br>OFF<br>Resistor to ground<br>required |

| d6    | PLL-Time constant     | PLLTC         | 0 = fast time constant<br>1 = slow time constant                                                          |

| d7    | -                     |               | Set to '0'                                                                                                |

# Absolute Maximum Ratings

$T_{\rm A}$  = 0 ... 70 °C (all voltages are referred to  $V_{\rm SS}$ )

| Parameter                                                    | Symbol                 | Symbol Limit Values |                       | Unit | Test Condition |

|--------------------------------------------------------------|------------------------|---------------------|-----------------------|------|----------------|

|                                                              |                        | min.                | max.                  |      |                |

| Supply voltage                                               | V <sub>DD</sub>        | - 1                 | 6                     | V    |                |

| Pin voltages                                                 | V <sub>IN</sub>        | - 1                 | V <sub>DD</sub> + 0.5 | V    |                |

| Difference between                                           | $V_{ m DD}/V_{ m DDA}$ | - 0.25              | 0.25                  | V    |                |

| Ambient temperature                                          | T <sub>A</sub>         | - 20                | 70                    | °C   |                |

| Storage temperature                                          | T <sub>stg</sub>       | - 20                | 125                   | °C   |                |

| Power dissipation                                            | P <sub>tot</sub>       |                     | 1                     | W    |                |

| Thermal resistance                                           | R <sub>th SU</sub>     |                     | 55                    | K/W  |                |

| <b>Operating Range</b> $T_A = 0 \dots 70 \ ^{\circ}\text{C}$ |                        |                     |                       |      |                |

| Supply voltage                                               | $V_{DD}$               | 4.5                 | 5.5                   | V    |                |

| Ambient temperature                                          | T <sub>A</sub>         | 0                   | 70                    | °C   |                |

## Characteristics

$T_{\rm A}$  = 0 ... 70 °C (all voltages are referred to  $V_{\rm SS}$ )

| Parameter           |                   | Symbol Limit Values                  |         |          | Unit      | Test Condition |                                                  |

|---------------------|-------------------|--------------------------------------|---------|----------|-----------|----------------|--------------------------------------------------|

|                     |                   |                                      | min.    | typ.     | max.      |                |                                                  |

| Supply voltage      |                   | $V_{\rm DD}/V_{\rm DDA}$             | 4.5     | 5        | 5.5       | V              |                                                  |

| Current consumption | digital<br>analog | I <sub>DD</sub><br>I <sub>DD A</sub> | 13<br>5 | 40<br>10 | 120<br>18 | mA<br>mA       | without load<br>LL3I = 13.5 MHz<br>LL3P = 27 MHz |

#### Inputs YS0-YS5, UVS0-UVS3 LL3I, BLNI, VSI, LL3P, VSP

| H-input voltage                               | V <sub>IH</sub> | 2.3   | V <sub>DD</sub> | V  |                           |

|-----------------------------------------------|-----------------|-------|-----------------|----|---------------------------|

| L-input voltage                               | $V_{IL}$        | - 1.0 | 0.8             | V  |                           |

| Input capacitance                             | C               |       | 7               | pF |                           |

| Input leakage current<br>(not valid for LL3P) | IL              |       | 10              | μA | V <sub>IH</sub> = 5.5 V   |

| Input leakage current                         | LL3P/<br>QX2    |       | 200             | μA | $V_{\rm IH} = V_{\rm DD}$ |

# Characteristics (cont'd)

| Parameter | Symbol | Limit Values |      | Unit | <b>Test Condition</b> |  |

|-----------|--------|--------------|------|------|-----------------------|--|

|           |        | min.         | typ. | max. |                       |  |

# **Output Select**

| •                 |                        |     |              |    |                                                      |

|-------------------|------------------------|-----|--------------|----|------------------------------------------------------|

| H-output voltage  | $V_{QH}$               | 2.4 | $V_{\rm DD}$ | V  | $-I_{QH} = 0.2 \text{ mA},$<br>SOP = 0               |

|                   | $V_{QH}$               | 1.5 | $V_{\rm DD}$ | V  | $-I_{QH} = 4.5 \text{ mA},^{2)}$<br>SOS = 1, SOP = 0 |

| L-output voltage  | $V_{QL}$               | 0   | 0.4          | V  | $I_{\rm QH} = 1.6  \rm mA$<br>SOP = 0, SOS = 0       |

| H-output voltage  | $V_{QH}$               |     | $V_{DD}$     | V  | SOP = 1                                              |

| L-output voltage  | $V_{QL}$               | 0   | 1            | V  | $I_{QL} = 5 \text{ mA}^{-1}$<br>SOP = 1, SOS = 0     |

| Transition period | $t_{\rm r}, t_{\rm f}$ |     | 15           | ns | SOP = 0, SOS = 0<br>C <sub>1</sub> = 30 pF           |

<sup>1)</sup> Measuring Circuit 9a <sup>2)</sup> Measuring Circuit 9b

# Input HSP / SAND

| H-input voltage       | V <sub>IH</sub> | 2.3   | $V_{ m DD}$ | V  | HSP5 = 1                     |

|-----------------------|-----------------|-------|-------------|----|------------------------------|

| L-input voltage       | $V_{IL}$        | - 1.0 | 0.8         | V  | HSP5 = 1                     |

| Input capacitance     | C               |       | 7           | pF |                              |

| Input leakage current | IL              | - 10  | 10          | μA | $0 \le V \le V_{DD} + 0.5 V$ |

# Characteristics (cont'd)

| Parameter               | Symbol                 | Limit Values |      | Unit     | Test | Measuring                |         |

|-------------------------|------------------------|--------------|------|----------|------|--------------------------|---------|

|                         |                        | min.         | nom. | max.     |      | Condition                | Circuit |

| Input SCL,              |                        |              |      |          |      |                          |         |

| In/Output SDA           |                        |              |      |          |      |                          | 1       |

| L-input voltage         | $V_{IL}$               | - 1          |      | 1.5      | V    |                          |         |

| H-input voltage         | $V_{IH}$               | 3            |      | $V_{DD}$ | V    |                          |         |

| Input leakage current   | IL                     |              |      | 10       | μA   | $V_{\rm IH} = 5,5 \rm V$ |         |

| Input capacitance       | $\bar{C}_1$            |              |      | 7        | pF   |                          |         |

| Input frequency         | $f_{\rm SCL}$          |              |      | 100      | kHz  |                          |         |

| Transition period       | $t_{\rm r}, t_{\rm f}$ |              |      | 2        | μs   |                          |         |

| Max. capacitance at bus | $C_{\max}$             |              |      | 400      | pF   |                          |         |

| Fall time               | t <sub>f</sub>         |              |      | 0.2      | μs   | from 3 V to 1 V          |         |

| SDA by acknowledge      | $V_{AL}$               | 0            |      | 0.4      | v.   | $I_{AL} = 3 \text{ mA}$  |         |

# Output OUT1 ... 3 \*

| Output current             | Io                   | - 1.61 | – 1.79 | – 1.97 | mA  | $V_{\rm DDA} = 5 \ V$                 | 1 |

|----------------------------|----------------------|--------|--------|--------|-----|---------------------------------------|---|

| Output voltage Range       | V <sub>OH</sub>      | 0      | 1.0    | 2      | Vpp | Bits D4 D7 of                         | 1 |

|                            |                      |        |        |        |     | Reg. 4 = 0000                         | 1 |

|                            |                      |        |        |        |     | $I_{\text{REF}} = \text{nom.}$        |   |

| Resolution                 | I <sub>O quant</sub> |        | 28.4   |        | μA  | $V_{\rm DDA} = 5 \text{ V}$           | 1 |

| Load resistance            | $R_{L}$              | 0      | 560    | 1000   | Ω   |                                       | 1 |

| Output capacitance         | Co                   |        |        | 7      | pF  |                                       | 1 |

| Coupling capacitance       | Cc                   |        | 47     |        | nF  |                                       | 1 |

| Reference current          | $I_{REF}$            | - 0.3  | - 0.58 | - 0.8  | mA  |                                       | 1 |

| Time constant              | t <sub>const</sub>   |        |        | 35     | ns  | BW = 4.5 MHz                          | 1 |

| Differential non-          |                      | - 0.5  |        | 0.5    | LSB | Range 0 1                             |   |

| linearity **               |                      |        |        |        |     | V                                     |   |

| Maximum difference of      |                      | - 3    |        | 3      | %   | Bit d1 of                             |   |

| output current at the      |                      |        |        |        |     | Reg. 0 = 1                            |   |

| RGB outputs                |                      |        |        |        |     |                                       |   |

| for the same               |                      |        |        |        |     |                                       |   |

| full modulation            |                      |        |        |        |     |                                       |   |

| Change of the output       | $\Delta I_{\rm O}$   | 20     |        |        | %   | $R_{\text{REF}} = 10 \text{ k}\Omega$ |   |

| currents by changing of    |                      |        |        |        |     |                                       |   |

| bits CON 0-3 in Register 4 |                      |        |        |        |     |                                       |   |

| Reference resistance       | R <sub>REF</sub>     | 2.7    | 3.9    | 4.7    | kΩ  | Bits D4 D7 of                         |   |

|                            |                      |        |        |        |     | Reg. 4 = 0000                         |   |

$^{\ast}$  The nominal color saturation is achieved in RGB mode by an amplitude ratio of 0.72/0.95/1 for Y/U/V at the inputs.  $^{\ast\ast}$  of D/A converter

# Internal PLLMaximum frequency tolerance $\pm$ 7 %<br/>(includes variation of horizontal-frequency and resonator tolerance).<br/>Attention: Voltage at pins QX1, QX2 must be below the limit values of<br/>absolute maximum ratings under all conditions.<br/>Minimum input amplitude at pin QX2 = 1 Vpp.

#### Maximum series resistor of quartz or ceramic resonator.

|                      | Load capacitance<br>at pin 12, 13 | R <sub>s</sub> |                                                    |

|----------------------|-----------------------------------|----------------|----------------------------------------------------|

|                      | 33 pF<br>22 pF                    | 10 Ω<br>20 Ω   | -                                                  |

|                      | 15 pF<br>10 pF                    | 30 Ω<br>40 Ω   |                                                    |

| Horizontal Frequency | min                               | max.           | Conditions                                         |

|                      | 14.53                             | 16.72 kHz      | Quartz Frequency 20.48 MHz<br>Bit d3 of Reg. 0 = 0 |

|                      | 29.06                             | 33.47 kHz      | Bit d3 of Reg. 0 = 1                               |

|                      | 30                                | 34.375 kHz     | Bit d3 of Reg. 0 = 1<br>Quartz Frequency 21.09 MHz |

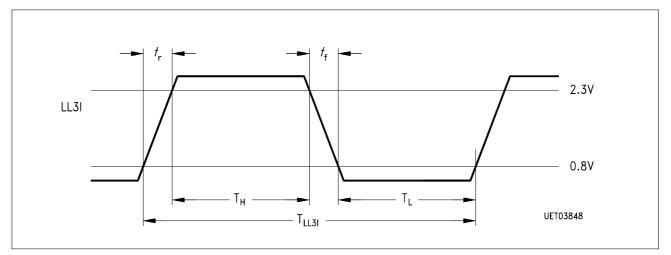

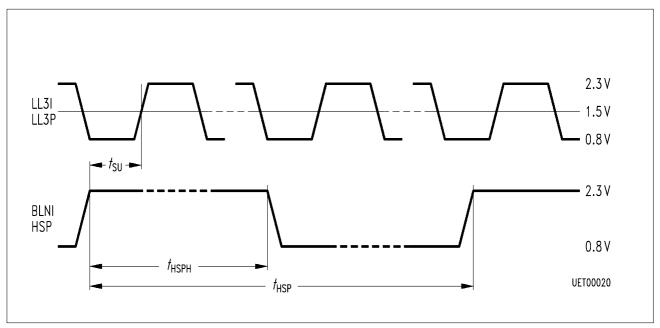

# Timing Diagram 1

| Parameter | Symbol | Limit Values |      |      | Unit |

|-----------|--------|--------------|------|------|------|

|           |        | min.         | typ. | max. |      |

#### LL3I

| Period time | T <sub>LL3 I</sub> | 68 | 74 | 80 | ns |

|-------------|--------------------|----|----|----|----|

| Rise time   | t <sub>r</sub>     |    |    | 5  | ns |

| Fall time   | t <sub>f</sub>     |    |    | 4  | ns |

| Low time    | TL                 | 30 |    |    | ns |

| High time   | T <sub>H</sub>     | 28 |    |    | ns |

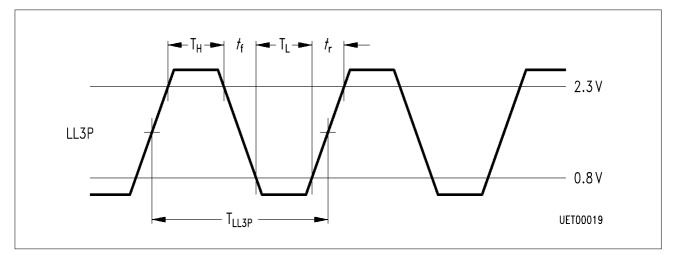

Timing Diagram 2

| Parameter | Symbol | Limit Values |      |      | Unit |

|-----------|--------|--------------|------|------|------|

|           |        | min.         | typ. | max. |      |

#### LL3P

| Period time | T <sub>LL1.5</sub> | 34 | 37 | 40 | ns |

|-------------|--------------------|----|----|----|----|

| Rise time   | $t_{\rm r}$        |    |    | 4  | ns |

| Fall time   | $t_{\rm f}$        |    |    | 4  | ns |

| Low time    | TL                 | 14 |    |    | ns |

| High time   | T <sub>H</sub>     | 12 |    |    | ns |

# Timing Diagram 3

| Parameter             | Symbol             |      | Limit Val | ues  | Unit                                    |

|-----------------------|--------------------|------|-----------|------|-----------------------------------------|

|                       |                    | min. | typ.      | max. |                                         |

| BLNI                  |                    |      |           |      |                                         |

| Period time 625 lines | t <sub>BLN</sub>   | 864  | 864       | 864  | T <sub>LL3I</sub>                       |

| Period time 525 lines | t <sub>BLN</sub>   | 858  | 864       | 864  | T <sub>LL3I</sub>                       |

| High time             | t <sub>BLN H</sub> | 1    |           | 857  | T <sub>LL3I</sub>                       |

| Set-up time           | t <sub>SU</sub>    | 12   |           |      | ns                                      |

| HSP                   |                    |      |           |      |                                         |

| Period time 625 lines | t <sub>HSP</sub>   | 864  | 864       | 864  | T <sub>LL3P</sub> / T <sub>LL1.5P</sub> |

| Period time 525 lines | t <sub>HSP</sub>   | 858  | 864       | 864  | $T_{LL3P}$ / $T_{LL1.5P}$               |

| High time             | t <sub>HSP H</sub> | 4    |           | 854  | $T_{LL3P}$ / $T_{LL1.5P}$               |

| Set-up time           | t <sub>SU</sub>    | 12   |           |      | ns                                      |

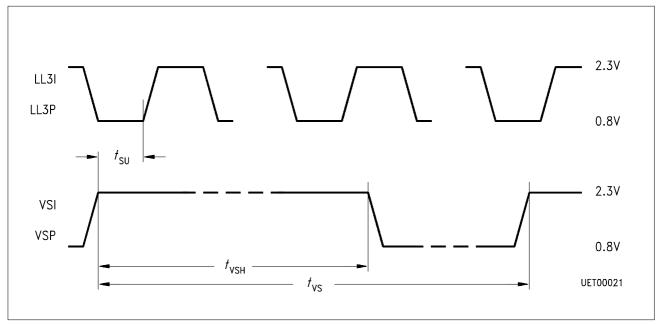

## **Timing Diagram 4**

| Parameter | Symbol |      | Unit |      |  |

|-----------|--------|------|------|------|--|

|           |        | min. | typ. | max. |  |

## VSI

| Period time 625 lines | t <sub>vs</sub>   |    | 312.5 | T <sub>BLNI</sub> |

|-----------------------|-------------------|----|-------|-------------------|

| Period time 525 lines | t <sub>VS</sub>   |    | 262.5 | T <sub>BLNI</sub> |

| High time             | t <sub>vs H</sub> | 1  |       | T <sub>LL3I</sub> |

| Set-up time           | t <sub>SU</sub>   | 15 |       | ns                |

#### VSP

| Period time 625 lines | t <sub>VS</sub>   |    | 312.5 | T <sub>HSP</sub>  |

|-----------------------|-------------------|----|-------|-------------------|

| Period time 525 lines | t <sub>vs</sub>   |    | 262.5 | T <sub>HSP</sub>  |

| High time             | t <sub>vs H</sub> | 1  |       | T <sub>LL3P</sub> |

| Set-up time           | t <sub>SU</sub>   | 15 |       | ns                |

Full frame display is possible if the input signal is fully according the TV standard.

The phase relation of the VSI/BLNI or the VSP/HSP signals has to be programmed in a way that the rising edge is neither close to the rising edge of the HS pulse nor in the middle of the TV line. (**Test circuit 6**).

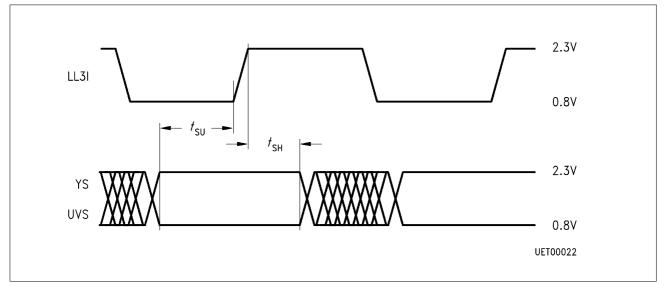

**Timing Diagram 5**

| Parameter | Symbol | Limit Values |      | Unit |

|-----------|--------|--------------|------|------|

|           |        | min.         | max. |      |

YS, UVS

| Set-up time | t <sub>su</sub> | 15 | ns |

|-------------|-----------------|----|----|

| Hold time   | t <sub>sH</sub> | 5  | ns |

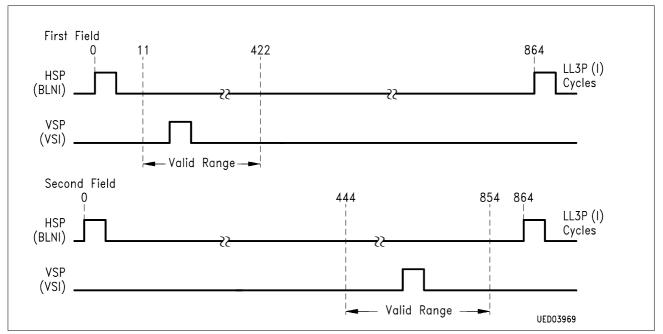

**Timing Diagram 6:** Allowed phase relation of the VSP/HSP or the VSI/BLNI pulse if the VSPDEL 0:4 or VSIDEL 0:4 = 00000.

Measuring Circuit 1 Wiring of D/A Converter Outputs

Semiconductor Group

## **Application Circuit 1a**

Semiconductor Group

# **Application Circuit 1b**