**SCAN18373T**

www.ti.com

SNLS036A - MAY 2004 - REVISED MAY 2004

# **SCAN18373T Transparent Latch with Tri-State Outputs**

Check for Samples: SCAN18373T

#### **FEATURES**

- IEEE 1149.1 (JTAG) Compliant

- Buffered Active-Low Latch Enable

- Tri-State Outputs for Bus-Oriented Applications

- 9-bit Data Busses for Parity Applications

- Reduced-Swing Outputs Source 24 mA/Sink 48 mA

- Ensured to Drive 50Ω Transmission Line to TTL Input Levels of 0.8V and 2.0V

- TTL Compatible Inputs

- 25 mil Pitch Cerpack Packaging

- Includes CLAMP and HIGHZ Instructions

- Standard Microcircuit Drawing (SMD) 5962-9311801

# **DESCRIPTION**

The SCAN18373T is a high speed, low-power transparent latch featuring separate data inputs organized into dual 9-bit bytes with byte-oriented latch enable and output enable control signals. This device is compliant with IEEE 1149.1 Standard Test Access Port and Boundary Scan Architecture with the incorporation of the defined boundary-scan test logic and test access port consisting of Test Data Input (TDI), Test Data Out (TDO), Test Mode Select (TMS), and Test Clock (TCK).

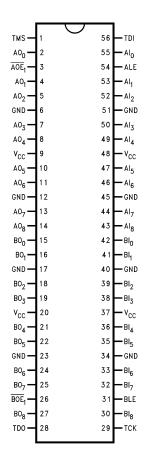

## **Connection Diagram**

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SNLS036A-MAY 2004-REVISED MAY 2004

www.ti.com

| Pin Names                                 | Description                    |

|-------------------------------------------|--------------------------------|

| AI <sub>(0-8)</sub> , BI <sub>(0-8)</sub> | Data Inputs                    |

| ALE, BLE                                  | Latch Enable Inputs            |

| AOE <sub>1</sub> , BOE <sub>1</sub>       | TRI-STATE Output Enable Inputs |

| AO <sub>(0-8)</sub> , BO <sub>(0-8)</sub> | TRI-STATE Latch Outputs        |

## **TRUTH TABLES**

|     | AO (0-8)         |          |                 |

|-----|------------------|----------|-----------------|

| ALE | AOE <sub>1</sub> | AI (0-8) |                 |

| X   | Н                | X        | Z               |

| Н   | L                | L        | L               |

| Н   | L                | Н        | Н               |

| L   | L                | X        | AO <sub>0</sub> |

(1) H= HIGH Voltage Level L= LOW Voltage Level

X= Immaterial

Z= High Impedance

AO<sub>0</sub> = Previous AO before H-to-L transition of ALE BO<sub>0</sub> = Previous BO before H-to-L transition of BLE

|     | BO (0-8)         |          |                 |

|-----|------------------|----------|-----------------|

| BLE | BOE <sub>1</sub> | BI (0-8) |                 |

| X   | Н                | X        | Z               |

| Н   | L                | L        | L               |

| Н   | L                | Н        | Н               |

| L   | L                | X        | BO <sub>0</sub> |

(1) H= HIGH Voltage Level L= LOW Voltage Level X= Immaterial

Z= High Impedance

AO<sub>0</sub> = Previous AO before H-to-L transition of ALE BO<sub>0</sub> = Previous BO before H-to-L transition of BLE

**NSTRUMENTS**

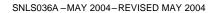

#### **FUNCTIONAL DESCRIPTION**

The SCAN18373T consists of two sets of nine D-type latches with Tri-State standard outputs. When the Latch Enable (ALE or BLE) input is HIGH, data on the inputs ( $AI_{(0-8)}$  or  $BI_{(0-8)}$ ) enters the latches. In this condition the latches are transparent, i.e., a latch output will change state each time its input changes. When Latch Enable is LOW, the latches store the information that was present on the inputs a set-up time preceding the HIGH-to-LOW transition of the Latch Enable. The TRI-STATE standard outputs are controlled by the Output Enable ( $\overline{AOE_1}$  or  $\overline{BOE_1}$ ) input. When Output Enable is LOW, the standard outputs are in the 2-state mode. When Output Enable is HIGH, the standard outputs are in the high impedance mode, but this does not interfere with entering new data into the latches.

#### **Logic Diagram**

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

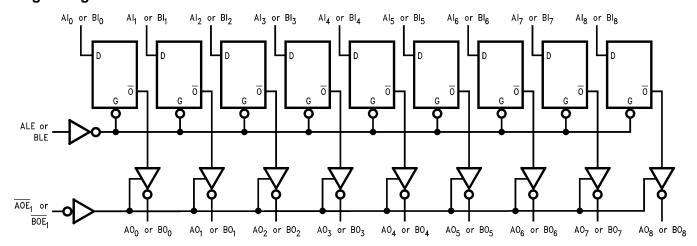

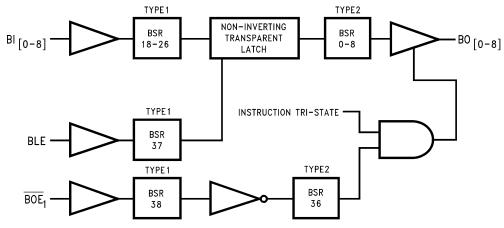

## **Block Diagrams**

Figure 1. Byte-A

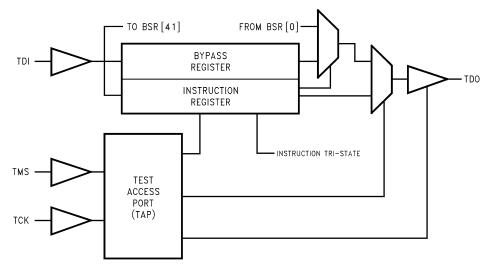

Figure 2. Tap Controller

BSR stands for Boundary Scan Register.

Figure 3. Byte-B

SNLS036A -MAY 2004-REVISED MAY 2004

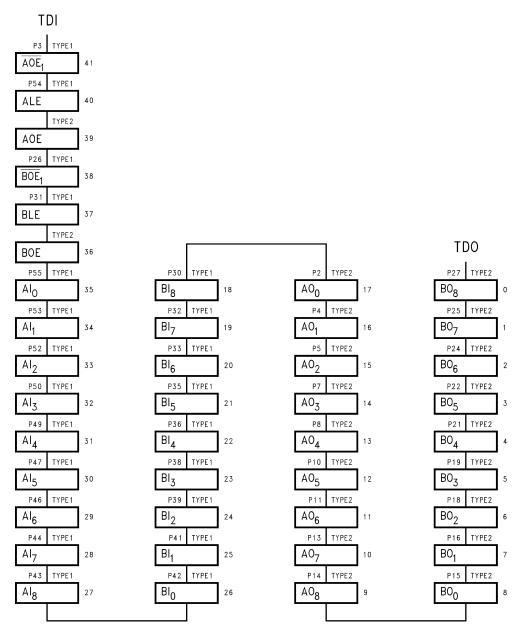

## **Description of Boundary-Scan Circuitry**

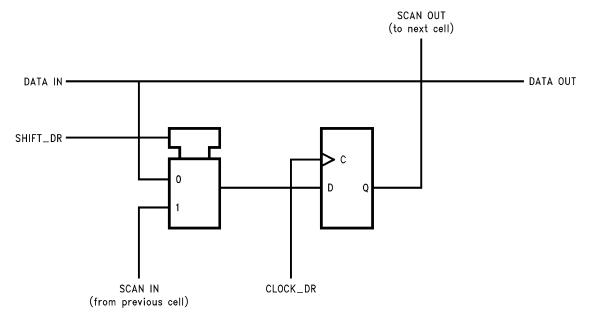

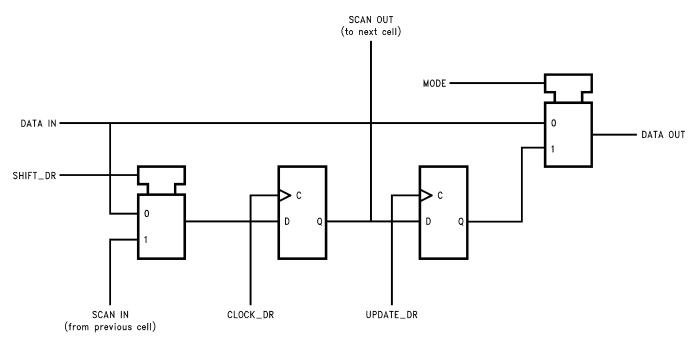

The scan cells used in the BOUNDARY-SCAN register are one of the following two types depending upon their location. Scan cell TYPE1 is intended to solely observe system data, while TYPE2 has the additional ability to control system data. (See IEEE Standard 1149.1 for a further description of scan cell TYPE1 and for a further description of scan cell TYPE2.)

Scan cell TYPE1 is located on each system input pin while scan cell TYPE2 is located at each system output pin as well as at each of the two internal active-high output enable signals. AOE controls the activity of the A-outputs while BOE controls the activity of the B-outputs. Each will activate their respective outputs by loading a logic high.

The BYPASS register is a single bit shift register stage identical to scan cell TYPE1. It captures a fixed logic low.

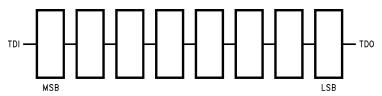

Figure 4. Bypass Register Scan Chain Definition Logic 0

The INSTRUCTION register is an eight-bit register which captures the value 00111101.

The two least significant bits of this captured value (01) are required by IEEE Std 1149.1. The upper six bits are unique to the SCAN18373T device. SCAN CMOS Test Access Logic devices do not include the IEEE 1149.1 optional identification register. Therefore, this unique captured value can be used as a "pseudo ID" code to confirm that the correct device is placed in the appropriate location in the boundary scan chain.

Figure 5. Instruction Register Scan Chain Definition

#### $MSB \rightarrow LSB$

| Instruction Code | Instruction    |

|------------------|----------------|

| 00000000         | EXTEST         |

| 10000001         | SAMPLE/PRELOAD |

| 10000010         | CLAMP          |

| 00000011         | HIGHZ          |

| All Others       | BYPASS         |

Figure 6. Scan Cell TYPE1

Figure 7. Scan Cell TYPE2

Submit Documentation Feedback

Figure 8. Boundary-Scan Register Scan Chain Definition (42 Bits in Length)

SNLS036A -MAY 2004-REVISED MAY 2004

www.ti.com

# **Boundary-Scan Register Definition Index**

| Bit No. | Pin Name         | Pin No. | Pin Type | Pin Type Scan Cell Type |         |  |

|---------|------------------|---------|----------|-------------------------|---------|--|

| 41      | AOE <sub>1</sub> | 3       | Input    | TYPE1                   | Control |  |

| 40      | ACP              | 54      | Input    | TYPE1                   | Signals |  |

| 39      | AOE              |         | Internal | TYPE2                   |         |  |

| 38      | BOE <sub>1</sub> | 26      | Input    | TYPE1                   |         |  |

| 37      | BCP              | 31      | Input    | TYPE1                   |         |  |

| 36      | BOE              |         | Internal | TYPE2                   |         |  |

| 35      | $AI_0$           | 55      | Input    | TYPE1                   | A-in    |  |

| 34      | Al <sub>1</sub>  | 53      | Input    | TYPE1                   |         |  |

| 33      | $Al_2$           | 52      | Input    | TYPE1                   |         |  |

| 32      | $Al_3$           | 50      | Input    | TYPE1                   |         |  |

| 31      | Al <sub>4</sub>  | 49      | Input    | TYPE1                   |         |  |

| 30      | Al <sub>5</sub>  | 47      | Input    | TYPE1                   |         |  |

| 29      | Al <sub>6</sub>  | 46      | Input    | TYPE1                   |         |  |

|         | Al <sub>7</sub>  | 44      | Input    | TYPE1                   |         |  |

| 27      | Al <sub>8</sub>  | 43      | Input    | TYPE1                   |         |  |

| 26      | BI <sub>0</sub>  | 42      | Input    | TYPE1                   | B-in    |  |

| 25      | BI <sub>1</sub>  | 41      | Input    | TYPE1                   |         |  |

| 24      | Bl <sub>2</sub>  | 39      | Input    | TYPE1                   |         |  |

|         | BI <sub>3</sub>  | 38      | Input    | TYPE1                   |         |  |

|         | Bl <sub>4</sub>  | 36      | Input    | TYPE1                   |         |  |

| 21      | Bl <sub>5</sub>  | 35      | Input    | TYPE1                   |         |  |

|         | BI <sub>6</sub>  | 33      | Input    | TYPE1                   |         |  |

|         | BI <sub>7</sub>  | 32      | Input    | TYPE1                   |         |  |

|         | BI <sub>8</sub>  | 30      | Input    | TYPE1                   |         |  |

| 17      | AO <sub>0</sub>  | 2       | Output   | TYPE2                   | A-out   |  |

| 16      | AO <sub>1</sub>  | 4       | Output   | TYPE2                   |         |  |

|         | AO <sub>2</sub>  | 5       | Output   | TYPE2                   |         |  |

|         |                  | 7       | Output   | TYPE2                   |         |  |

|         |                  | 8       | Output   | TYPE2                   |         |  |

| 12      | AO <sub>5</sub>  | 10      | Output   | TYPE2                   |         |  |

|         | AO <sub>6</sub>  | 11      | Output   | TYPE2                   |         |  |

|         | AO <sub>7</sub>  | 13      | Output   | TYPE2                   |         |  |

|         | AO <sub>8</sub>  | 14      | Output   | TYPE2                   |         |  |

|         | BO <sub>0</sub>  | 15      | Output   | TYPE2                   | B-out   |  |

| 7       | BO <sub>1</sub>  | 16      | Output   | TYPE2                   |         |  |

|         | BO <sub>2</sub>  | 18      | Output   | TYPE2                   |         |  |

|         |                  | 19      | Output   | TYPE2                   |         |  |

| 4       | BO <sub>4</sub>  | 21      | Output   | TYPE2                   |         |  |

|         |                  | 22      | Output   | TYPE2                   |         |  |

|         | BO <sub>6</sub>  | 24      | Output   | TYPE2                   |         |  |

|         | BO <sub>7</sub>  | 25      | Output   | TYPE2                   |         |  |

|         | BO <sub>8</sub>  | 27      | Output   | TYPE2                   | =       |  |

Submit Documentation Feedback

Copyright © 2004, Texas Instruments Incorporated

www.ti.com

SNLS036A -MAY 2004-REVISED MAY 2004

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## ABSOLUTE MAXIMUM RATINGS (1)(2)

| Supply Voltage (V <sub>CC</sub> )               |                        | −0.5V to +7.0V                  |

|-------------------------------------------------|------------------------|---------------------------------|

| DC least Diada Coment (L.)                      | V <sub>I</sub> = −0.5V | −20 mA                          |

| DC Input Diode Current (I <sub>IK</sub> )       | $V_I = V_{CC} + 0.5V$  | +20 mA                          |

| DC Output Diada Current (L.)                    | $V_{O} = -0.5V$        | −20 mA                          |

| DC Output Diode Current (I <sub>OK</sub> )      | $V_O = V_{CC} + 0.5V$  | +20 mA                          |

| DC Output Voltage (V <sub>O</sub> )             |                        | -0.5V to V <sub>CC</sub> + 0.5V |

| DC Output Source/Sink Current (I <sub>O</sub> ) |                        | ±70 mA                          |

| DC V <sub>CC</sub> or Ground Current            | Per Output Pin         | ±70 mA                          |

| Junction Temperature                            | Cerpack                | +175°C                          |

| Storage Temperature                             |                        | −65°C to +150°C                 |

| ESD (Min)                                       |                        | 2000V                           |

<sup>(1)</sup> Absolute maximum ratings are those values beyond which damage to the device may occur. The databook specifications should be met, without exception, to ensure that the system design is reliable over its power supply, temperature, and output/input loading variables. Texas Instruments does not recommend operation of SCAN circuits outside databook specifications.

#### RECOMMENDED OPERATING CONDITIONS

| Supply Voltage (V <sub>CC</sub> )       | SCAN Products                                                     | 4.5V to 5.5V          |

|-----------------------------------------|-------------------------------------------------------------------|-----------------------|

| Input Voltage (V <sub>I</sub> )         | 0V to V <sub>CC</sub>                                             |                       |

| Output Voltage (V <sub>O</sub> )        |                                                                   | 0V to V <sub>CC</sub> |

| Operating Temperature (T <sub>A</sub> ) | Military                                                          | −55°C to +125°C       |

| Minimum Input Edge Rate dV/dt           | V <sub>IN</sub> from 0.8V to 2.0V<br>V <sub>CC</sub> @ 4.5V, 5.5V | 125 mV/ns             |

#### DC ELECTRICAL CHARACTERISTICS

All outputs loaded; thresholds associated with output under test.

|                             | Parameter                        |                     | Military                            |          | Conditions                                                        |

|-----------------------------|----------------------------------|---------------------|-------------------------------------|----------|-------------------------------------------------------------------|

| Symbol                      |                                  | V <sub>CC</sub> (V) | T <sub>A</sub> =<br>-55°C to +125°C | Units    |                                                                   |

|                             |                                  |                     | Specified Limits                    |          |                                                                   |

| V <sub>IH</sub>             | Minimum High<br>Input Voltage    | 4.5<br>5.5          | 2.0<br>2.0                          | V        | $V_{OUT} = 0.1V$<br>or $V_{CC} - 0.1V$                            |

| V <sub>IL</sub>             | Maximum Low<br>Input Voltage     | 4.5<br>5.5          | 0.8<br>0.8                          | V        | $V_{OUT} = 0.1V$<br>or $V_{CC} - 0.1V$                            |

|                             | Minimum High                     | 4.5<br>5.5          | 3.15<br>4.15                        | V        | I <sub>OUT</sub> = -50 μA                                         |

|                             | Output Voltage                   | 4.5<br>5.5          | 2.4<br>2.4                          | V        | $V_{IN} = V_{IL} \text{ or } V_{IH}$<br>$I_{OH} = -24 \text{ mA}$ |

| W                           | Maximum Low                      | 4.5<br>5.5          | 0.1<br>0.1                          | V        | I <sub>OUT</sub> = 50 μA                                          |

| V <sub>OL</sub>             | Output Voltage                   | 4.5<br>5.5          | 0.55<br>0.55                        | V        | $V_{IN} = V_{IL} \text{ or } V_{IH}$<br>$I_{OL} = 48 \text{ mA}$  |

| I <sub>IN</sub>             | Maximum Input<br>Leakage Current | 5.5                 | ±1.0                                | μΑ       | $V_I = V_{CC}$ , GND                                              |

| I <sub>IN</sub><br>TDI, TMS | Maximum Input<br>Leakage         | 5.5                 | 3.7<br>-385                         | μΑ<br>μΑ | $V_I = V_{CC}$<br>$V_I = GND$                                     |

|                             | Minimum Input<br>Leakage         | 5.5                 | -160                                | μA       | V <sub>I</sub> = GND                                              |

<sup>(2)</sup> If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

SNLS036A-MAY 2004-REVISED MAY 2004

## DC ELECTRICAL CHARACTERISTICS (continued)

All outputs loaded; thresholds associated with output under test.

|                  |                                               |                     | Military                            |           |                                                                                             |

|------------------|-----------------------------------------------|---------------------|-------------------------------------|-----------|---------------------------------------------------------------------------------------------|

| Symbol           | Parameter                                     | V <sub>CC</sub> (V) | T <sub>A</sub> =<br>-55°C to +125°C | Units     | Conditions                                                                                  |

|                  |                                               |                     | Specified Limits                    |           |                                                                                             |

| I <sub>OLD</sub> | Minimum Dynamic Output Current <sup>(1)</sup> | 5.5                 | 63<br>-27                           | mA<br>mA  | $V_{OLD} = 0.8V \text{ Max}$<br>$V_{OHD} = 2.0V \text{ Min}$                                |

| I <sub>OZ</sub>  | Maximum Output<br>Leakage Current             | 5.5                 | ±10.0                               | μА        | $V_{I}$ (OE) = $V_{IL}$ , $V_{IH}$                                                          |

| Ios              | Output Short Circuit Current                  | 5.5                 | -100                                | mA<br>Min | V <sub>O</sub> = 0V                                                                         |

|                  | Maximum Quiescent Supply                      | 5.5                 | 168                                 | μΑ        | $V_O = Open$<br>TDI, TMS = $V_{CC}$                                                         |

| Icc              | Current                                       | 5.5                 | 930                                 | μΑ        | V <sub>O</sub> = Open<br>TDI, TMS = GND                                                     |

|                  |                                               | 5.5                 | 2.0                                 | mA        | $V_I = V_{CC} - 2.1V$                                                                       |

| I <sub>CCt</sub> | Maximum I <sub>CC</sub> per Input             | 5.5                 | 2.15                                | mA        | V <sub>I</sub> = V <sub>CC</sub> - 2.1V<br>TDI/TMS Pin, Test One<br>with the Other Floating |

<sup>(1)</sup> Maximum test duration 2.0 ms, one output loaded at a time.

## **NOISE SPECIFICATIONS**

| Symbol           | Parameter                                     | V <sub>CC</sub> (V) | Military                         | Units | Fig. No. |

|------------------|-----------------------------------------------|---------------------|----------------------------------|-------|----------|

|                  |                                               | (V)                 | T <sub>A</sub> = −55°C to +125°C |       |          |

|                  |                                               |                     | Specified Limits                 |       |          |

| V <sub>OLP</sub> | Maximum High Output Noise (1)(2)              | 5.0                 | 0.8                              | V     |          |

| V <sub>OLV</sub> | Minimum Low Output<br>Noise <sup>(1)(2)</sup> | 5.0                 | -0.8                             | V     |          |

<sup>(1)</sup> Maximum number of outputs that can switch simultaneously is n. (n-1) outputs are switched LOW and one output held LOW.

## **AC ELECTRICAL CHARACTERISTICS**

Normal Operation

|                                        |                               |                                    | Mil                                       | itary        |             |  |

|----------------------------------------|-------------------------------|------------------------------------|-------------------------------------------|--------------|-------------|--|

| Symbol Parameter                       |                               | V <sub>CC</sub> (V) <sup>(1)</sup> | T <sub>A</sub> =-55°C<br>C <sub>L</sub> = | Units        | Fig.<br>No. |  |

|                                        |                               |                                    | Min                                       | Max          |             |  |

| t <sub>PLH</sub> ,<br>t <sub>PHL</sub> | Propagation<br>Delay, D to Q  | 5.0                                | 2.5<br>2.5                                | 11.0<br>11.5 | ns          |  |

| t <sub>PLH</sub> ,<br>t <sub>PHL</sub> | Propagation<br>Delay, LE to Q | 5.0                                | 2.5<br>2.5                                | 12.0<br>13.0 | ns          |  |

| t <sub>PLZ</sub> ,<br>t <sub>PHZ</sub> | Disable Time                  | 5.0                                | 1.5<br>1.5                                | 11.0<br>10.3 | ns          |  |

| $t_{PZL},$ $t_{PZH}$                   | Enable Time                   | 5.0                                | 2.0<br>2.0                                | 13.5<br>11.5 | ns          |  |

(1) Voltage Range 5.0 is  $5.0V \pm 0.5V$ .

Submit Documentation Feedback

<sup>(2)</sup> Maximum number of outputs that can switch simultaneously is n. (n-1) outputs are switched HIGH and one output held HIGH.

SNLS036A -MAY 2004-REVISED MAY 2004

## **AC OPERATING REQUIREMENTS**

**Normal Operation**

| Symbol         | Parameter                        | V <sub>cc</sub> (V) <sup>(1)</sup> | Military  T <sub>A</sub> = −55°C to +125°C  C <sub>L</sub> = 50 pF  Specified Minimum | Units | Fig.<br>No. |

|----------------|----------------------------------|------------------------------------|---------------------------------------------------------------------------------------|-------|-------------|

| ts             | Setup Time, H or L<br>Data to LE | 5.0                                | 3.0                                                                                   | ns    |             |

| t <sub>H</sub> | Hold Time, H or L<br>LE to Data  | 5.0                                | 1.5                                                                                   | ns    |             |

| t <sub>W</sub> | LE Pulse Width                   | 5.0                                | 5.0                                                                                   | ns    |             |

<sup>(1)</sup> Voltage Range 5.0 is 5.0V ±0.5V.

# **AC ELECTRICAL CHARACTERISTICS**

Scan Test Operation

| Symbol                                 | Parameter                                                                | V <sub>cc</sub> (V) <sup>(1)</sup> | Mi                                                        | Units        | Fig.<br>No. |  |

|----------------------------------------|--------------------------------------------------------------------------|------------------------------------|-----------------------------------------------------------|--------------|-------------|--|

|                                        |                                                                          |                                    | T <sub>A</sub> =-55°C to +125°C<br>C <sub>L</sub> = 50 pF |              |             |  |

|                                        |                                                                          |                                    | Min                                                       | Max          |             |  |

| t <sub>PLH</sub> ,<br>t <sub>PHL</sub> | Propagation Delay<br>TCK to TDO                                          | 5.0                                | 3.5<br>3.5                                                | 15.8<br>15.8 | ns          |  |

| t <sub>PLZ</sub> ,<br>t <sub>PHZ</sub> | Disable Time<br>TCK to TDO                                               | 5.0                                | 2.5<br>2.5                                                | 12.8<br>12.8 | ns          |  |

| t <sub>PZL</sub> ,<br>t <sub>PZH</sub> | Enable Time<br>TCK to TDO                                                | 5.0                                | 3.0<br>3.0                                                | 16.7<br>16.7 | ns          |  |

| t <sub>PLH</sub> ,<br>t <sub>PHL</sub> | Propagation Delay<br>TCK to Data Out<br>during Update-DR State           | 5.0                                | 5.0<br>5.0                                                | 21.7<br>21.7 | ns          |  |

| t <sub>PLH</sub> ,<br>t <sub>PHL</sub> | Propagation Delay<br>TCK to Data Out<br>during Update-IR State           | 5.0                                | 5.0<br>5.0                                                | 22.0<br>22.0 | ns          |  |

| t <sub>PLH</sub> ,<br>t <sub>PHL</sub> | Propagation Delay<br>TCK to Data Out<br>during Test Logic<br>Reset State | 5.0                                | 5.5<br>5.5                                                | 23.0<br>23.0 | ns          |  |

| t <sub>PLZ</sub> ,<br>t <sub>PHZ</sub> | Propagation Delay<br>TCK to Data Out<br>during Update-DR State           | 5.0                                | 4.0<br>4.0                                                | 19.6<br>19.6 | ns          |  |

| t <sub>PLZ</sub> ,<br>t <sub>PHZ</sub> | Propagation Delay<br>TCK to Data Out<br>during Update-IR State           | 5.0                                | 5.0<br>5.0                                                | 22.4<br>22.4 | ns          |  |

| t <sub>PLZ</sub> ,<br>t <sub>PHZ</sub> | Propagation Delay<br>TCK to Data Out<br>during Test Logic<br>Reset State | 5.0                                | 5.0<br>5.0                                                | 23.3<br>23.3 | ns          |  |

| t <sub>PZL</sub> ,<br>t <sub>PZH</sub> | Propagation Delay<br>TCK to Data Out<br>during Update-DR State           | 5.0                                | 5.0<br>5.0                                                | 22.6<br>22.6 | ns          |  |

| t <sub>PZL</sub> ,<br>t <sub>PZH</sub> | Propagation Delay<br>TCK to Data Out<br>during Update-IR State           | 5.0                                | 6.5<br>6.5                                                | 26.2<br>26.2 | ns          |  |

| t <sub>PZL</sub> ,<br>t <sub>PZH</sub> | Propagation Delay<br>TCK to Data Out<br>during Test Logic<br>Reset State | 5.0                                | 7.0<br>7.0                                                | 27.4<br>27.4 | ns          |  |

<sup>(1)</sup> Voltage Range 5.0 is 5.0V  $\pm$ 0.5V. All propagation delays involving TCK are measured from the falling edge of TCK.

#### **AC OPERATING REQUIREMENTS**

Scan Test Operation

|                  |                                                                                 |        |                                    | Military                                                                      |       |             |

|------------------|---------------------------------------------------------------------------------|--------|------------------------------------|-------------------------------------------------------------------------------|-------|-------------|

| Symbol           | Parameter                                                                       |        | V <sub>CC</sub> (V) <sup>(1)</sup> | $T_A = -55^{\circ}\text{C to } +125^{\circ}\text{C}$<br>$C_L = 50 \text{ pF}$ | Units | Fig.<br>No. |

|                  |                                                                                 |        |                                    | Specified Minimum                                                             |       |             |

| t <sub>S</sub>   | Setup Time,<br>Data to TCK <sup>(2)</sup>                                       |        | 5.0                                | 3.0                                                                           | ns    |             |

| t <sub>H</sub>   | Hold Time,<br>TCK to Data <sup>(2)</sup>                                        |        | 5.0                                | 5.5                                                                           | ns    |             |

| t <sub>S</sub>   | Setup Time, H or L<br>AOE <sub>1</sub> , BOE <sub>1</sub> to TCK <sup>(3)</sup> |        | 5.0                                | 3.0                                                                           | ns    |             |

| t <sub>H</sub>   | Hold Time, H or L<br>TCK to $\overline{AOE}_1$ , $\overline{BOE}_1^{(3)}$       |        | 5.0                                | 4.5                                                                           | ns    |             |

| t <sub>S</sub>   | Setup Time, H or L<br>Internal AOE, BOE,<br>to TCK <sup>(4)</sup>               |        | 5.0                                | 3.0                                                                           | ns    |             |

| t <sub>H</sub>   | Hold Time, H or L<br>TCK to Internal<br>AOE, BOE <sup>(4)</sup>                 |        | 5.0                                | 3.0                                                                           | ns    |             |

| t <sub>S</sub>   | Setup Time<br>ALE, BLE <sup>(5)</sup> to TCK                                    |        | 5.0                                | 3.0                                                                           | ns    |             |

| t <sub>H</sub>   | Hold Time<br>TCK to ALE, BLE <sup>(5)</sup>                                     |        | 5.0                                | 4.0                                                                           | ns    |             |

| t <sub>S</sub>   | Setup Time, H or L<br>TMS to TCK                                                |        | 5.0                                | 8.0                                                                           | ns    |             |

| t <sub>H</sub>   | Hold Time, H or L<br>TCK to TMS                                                 |        | 5.0                                | 2.0                                                                           | ns    |             |

| t <sub>S</sub>   | Setup Time, H or L<br>TDI to TCK                                                |        | 5.0                                | 4.0                                                                           | ns    |             |

| t <sub>H</sub>   | Hold Time, H or L<br>TCK to TDI                                                 |        | 5.0                                | 4.5                                                                           | ns    |             |

| t <sub>W</sub>   | Pulse Width TCK                                                                 | H<br>L | 5.0                                | 12.0<br>5.0                                                                   | ns    |             |

| f <sub>max</sub> | Maximum TCK<br>Clock Frequency                                                  |        | 5.0                                | 25                                                                            | MHz   |             |

| T <sub>pu</sub>  | Wait Time, Power Up to TCK                                                      |        | 5.0                                | 100                                                                           | ns    |             |

| T <sub>dn</sub>  | Power Down Delay                                                                |        | 0.0                                | 100                                                                           | ms    |             |

- (1) Voltage Range 5.0 is 5.0V ±0.5V. All Input Timing Delays involving TCK are measured from the rising edge of TCK.

(2) This delay represents the timing relationship between the data input and TCK at the associated scan cells numbered 0-8, 9-17, 18-26 and 27-35.

- Timing pertains to BSR 38 and 41 only.

This delay represents the timing relationship between AOE/BOE and TCK for scan cells 36 and 39 only.

Timing pertains to BSR 37 and 40 only.

#### **CAPACITANCE**

| Symbol           | Parameter                     | Max  | Units | Conditions             |

|------------------|-------------------------------|------|-------|------------------------|

| C <sub>IN</sub>  | Input Pin Capacitance         | 5.0  | pF    | $V_{CC} = 5.0V$        |

| C <sub>OUT</sub> | Output Pin Capacitance        | 15.0 | pF    | $V_{CC} = 5.0V$        |

| C <sub>PD</sub>  | Power Dissipation Capacitance | 35.0 | pF    | V <sub>CC</sub> = 5.0V |

Submit Documentation Feedback

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive Communications and Telecom **Amplifiers** amplifier.ti.com www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP **Energy and Lighting** dsp.ti.com www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical logic.ti.com Logic Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers <u>microcontroller.ti.com</u> Video and Imaging <u>www.ti.com/video</u>

RFID www.ti-rfid.com

OMAP Applications Processors <a href="www.ti.com/omap">www.ti.com/omap</a> TI E2E Community <a href="e2e.ti.com">e2e.ti.com</a>

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>