#### INTEGRATED CIRCUITS

# DATA SHEET

# SAA7385 Error correction and host interface IC for CD-ROM (SEQUOIA)

Preliminary specification

File under Integrated Circuits, IC01

**SAA7385**

| CONTE                         | NTS                                                                                                    | 11                                           | BUFFER MANAGER                                                                                                                                                                                                          |  |  |  |

|-------------------------------|--------------------------------------------------------------------------------------------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1<br>1.1<br>1.2<br>1.3<br>1.4 | FEATURES General 53CF94 SCSI controller 80C32 high-speed microcontroller Front-end interface logic     | 11.1<br>11.2<br>11.3<br>11.4<br>11.5<br>11.6 | Front-end to buffer manager interface Microcontroller to buffer manager interface ECC to buffer manager interface SCSI to buffer manager interface Miscellaneous buffer manager considerations 53CF94 related registers |  |  |  |

| 1.5<br>1.6                    | Buffer controller Hardware third-level error correction                                                | 12                                           | FRAME BUFFER ORGANIZATION                                                                                                                                                                                               |  |  |  |

| 1.7                           | Additional product support                                                                             | 13                                           | SUMMARY OF CONTROL REGISTER MAP                                                                                                                                                                                         |  |  |  |

| 2                             | GENERAL DESCRIPTION                                                                                    | 14                                           | LIMITING VALUES                                                                                                                                                                                                         |  |  |  |

| 3                             | QUICK REFERENCE DATA                                                                                   | 15                                           | OPERATING CHARACTERISTICS                                                                                                                                                                                               |  |  |  |

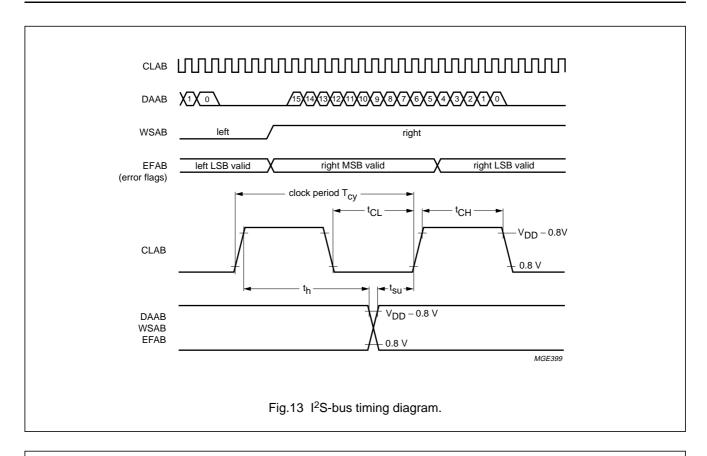

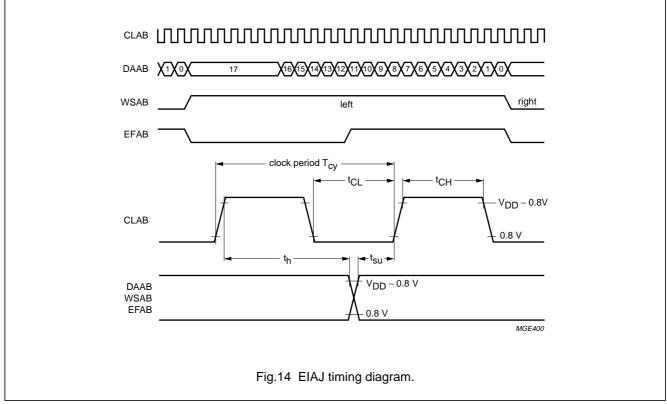

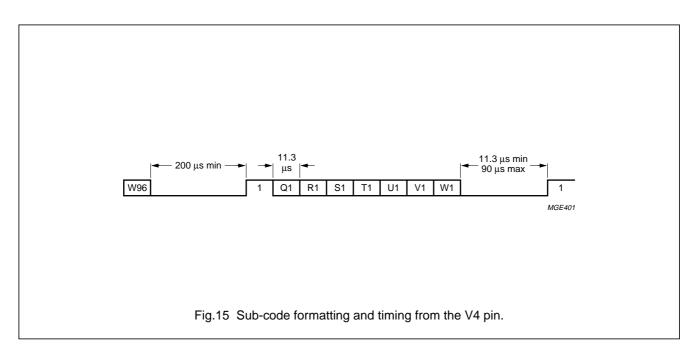

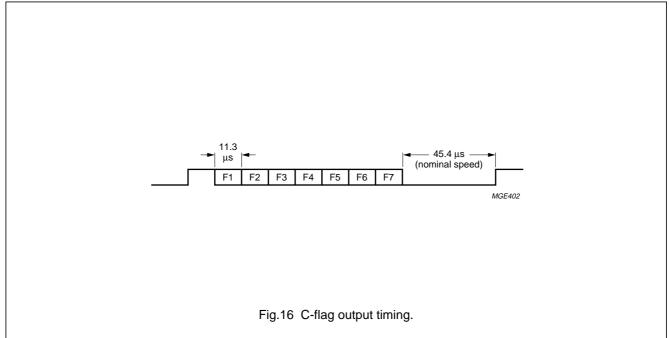

| 4<br>5                        | ORDERING INFORMATION BLOCK DIAGRAM                                                                     | 15.1<br>15.2<br>15.3                         | I <sup>2</sup> S-bus timing; data mode<br>EIAJ timing; audio mode<br>R-W timing (see Fig.15)                                                                                                                            |  |  |  |

| 6                             | PINNING                                                                                                | 15.4                                         | C-flag timing (see Fig.16)                                                                                                                                                                                              |  |  |  |

| 7                             | FUNCTIONAL DESCRIPTION                                                                                 | 15.5                                         | S2B interface timing                                                                                                                                                                                                    |  |  |  |

| 7.1<br>7.2<br>7.3<br>7.4      | 80C32 microcontroller<br>53CF94 fast SCSI controller<br>Input clock doubler<br>Front-end               | 15.6<br>15.7<br>15.8                         | SCSI interface timing Microprocessor interface DRAM interface (the SAA7385 is designed to operate with standard 70 ns DRAMs)                                                                                            |  |  |  |

| 8                             | MICROCONTROLLER INTERFACE                                                                              | 16                                           | PACKAGE OUTLINE                                                                                                                                                                                                         |  |  |  |

| 8.1                           | Microcontroller interface status register                                                              | 17                                           | SOLDERING                                                                                                                                                                                                               |  |  |  |

| 8.2<br>8.3<br>8.4             | Microcontroller interface command register Microcontroller interrupts Microcontroller RAM organization | 17.1<br>17.2<br>17.3                         | Introduction Reflow soldering Wave soldering                                                                                                                                                                            |  |  |  |

| 9                             | FRONT PANEL AND MISCELLANEOUS CONTROL SIGNALS                                                          | 17.4<br>18                                   | Repairing soldered joints DEFINITIONS                                                                                                                                                                                   |  |  |  |

| 9.1<br>9.2                    | S2B UART registers Miscellaneous control registers                                                     | 19                                           | LIFE SUPPORT APPLICATIONS                                                                                                                                                                                               |  |  |  |

| 10                            | FRONT-END                                                                                              |                                              |                                                                                                                                                                                                                         |  |  |  |

| 10.1                          | Minute Second Frame (MSF) addressing and header information                                            |                                              |                                                                                                                                                                                                                         |  |  |  |

| 10.2                          | Front-end status and control                                                                           |                                              |                                                                                                                                                                                                                         |  |  |  |

### Error correction and host interface IC for CD-ROM (SEQUOIA)

**SAA7385**

#### 1 FEATURES

#### 1.1 General

- Single chip digital solution for an 8 x speed CD-ROM controller chip

- 10 Mbytes/s NCR53CF94 equivalent SCSI controller included

- High-speed 80C32 microcontroller with 256  $\times$  8 scratch-pad SRAM included

- High performance CD-ROM interface logic

- 128 pin QFP package.

#### 1.2 53CF94 SCSI controller

- Separate clock input to allow operation up to the maximum 10 Mbytes/s

- Fast synchronous SCSI-2 compatible

- 24-bit transfer counter for single transfers up to 16 Mbytes

- High-speed 16-bit DMA interface to the buffer manager DRAM

- On-chip 48 mA SCSI drivers

- Software compatible with members of the 53C90 family

- · Allows for SCAM support.

#### 1.3 80C32 high-speed microcontroller

- 33.87 MHz full system speed operation

- · Three timers/event counters

- · Programmable full duplex serial channel

- Eight general purpose microcontroller I/O pins

- · External program ROM.

#### 1.4 Front-end interface logic

- Full 8 × speed hardware operation

- Block decoder

- · Sector sequencer

- CRC checking of Mode 1 and Mode 2, Form 1 sectors

- 212 ms watch-dog timer

- · Sub-code interface with synchronization

- · C-flag interface for absolute time stamp.

#### 1.5 Buffer controller

- Ten level arbitration logic

- Utilizes low cost 70 ns DRAMs

- Page mode DRAM access for high-speed error correction and SCSI data transfer

- Data organization by 3 kbyte frames

- 256 kbyte or 1 Mbyte DRAM supported.

#### 1.6 Hardware third-level error correction

- Third-level correction provides superior performance in unfavourable conditions

- Full hardware error correction to reduce microcontroller overhead

- Corrections are automatically written to the DRAM frame buffer.

#### 1.7 Additional product support

- All control registers mapped into 80C32 special function memory space

- Dedicated S2B interface UART

- · Input clock synthesizer

- · Red book audio pass through.

#### 2 GENERAL DESCRIPTION

The SAA7385 is a high integration ASIC that incorporates all of the digital electronics necessary to connect a CD decoder to a SCSI host. An 80C32 microcontroller and a 53CF94 SCSI controller are embedded in the ASIC. The following functions are supported:

- · Input clock doubler

- Block decoder

- CRC checking of Mode 1 and Mode 2, Form 1 sectors

- Red book audio pass through to SCSI

- · Buffer manager

- Third-level error correction

- · Sub-code and Q-channel support

- Dedicated S2B interface UART

- Embedded 80C32 microcontroller

- Embedded 53CF94 SCSI controller.

### Error correction and host interface IC for CD-ROM (SEQUOIA)

**SAA7385**

The SAA7385 uses a 33.8688 MHz clock and is capable of accepting data at eight times (n = 8 or 1.4 Mbytes/s) the normal CD-ROM data rate.

Third level error correction hardware is included to improve the correction efficiency of the system. The buffer manager hardware utilizes a ten-level arbitration unit and can stop the clock to the microcontroller to emulate a wait condition when necessary.

The SAA7385 comprises five major functional blocks:

- The 80C32 microcontroller is an industry standard core

- The 53CF94 is an industry standard core

- The front-end block connects to the external CD-60 based decoder and fully processes the incoming data stream to provide bytes of data that are stored in the external buffer

- The buffer manager block provides the address generation and timing control for the external DRAM buffer

- The ECC block performs the error correction functions in hardware on the data in the DRAM buffer.

Supply of this Compact Disc IC does not convey an implied license under any patent right to use this IC in any Compact Disc application.

#### 3 QUICK REFERENCE DATA

| SYMBOL           | PARAMETER                     | MIN.       | TYP. | MAX. | UNIT |

|------------------|-------------------------------|------------|------|------|------|

| $V_{DD}$         | digital supply voltage        | 4.5        | 5.0  | 5.5  | ٧    |

| T <sub>amb</sub> | operating ambient temperature | 0          | _    | 70   | °C   |

| T <sub>stg</sub> | storage temperature           | <b>-55</b> | _    | +150 | °C   |

#### 4 ORDERING INFORMATION

| TYPE      | PACKAGE |                                                                                              |          |  |  |  |  |  |

|-----------|---------|----------------------------------------------------------------------------------------------|----------|--|--|--|--|--|

| NUMBER    | NAME    | DESCRIPTION                                                                                  | VERSION  |  |  |  |  |  |

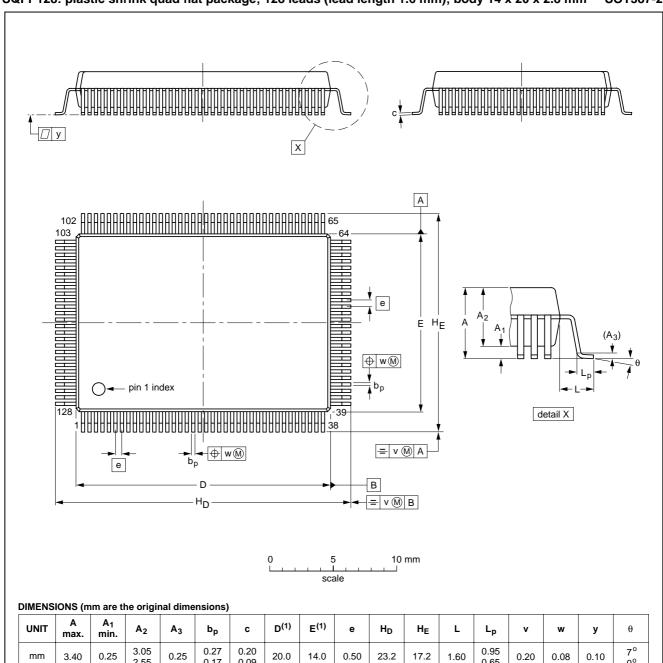

| SAA7385GP | SQFP128 | plastic quad flat package; 128 leads (lead length 1.6 mm); body $14 \times 20 \times 2.8$ mm | SOT387-2 |  |  |  |  |  |

# Error correction and host interface IC for CD-ROM (SEQUOIA)

**SAA7385**

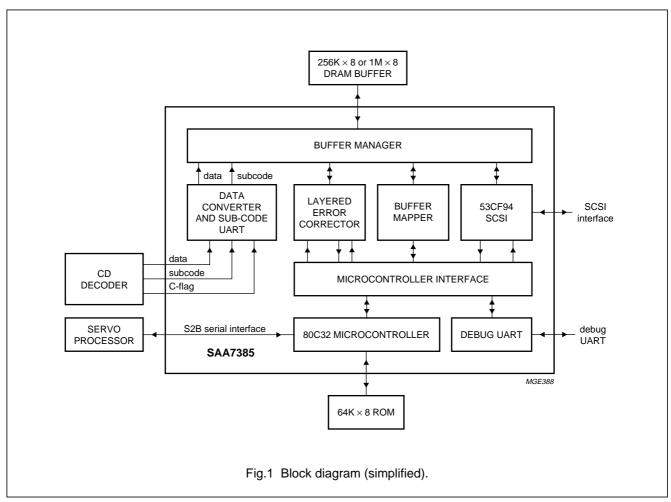

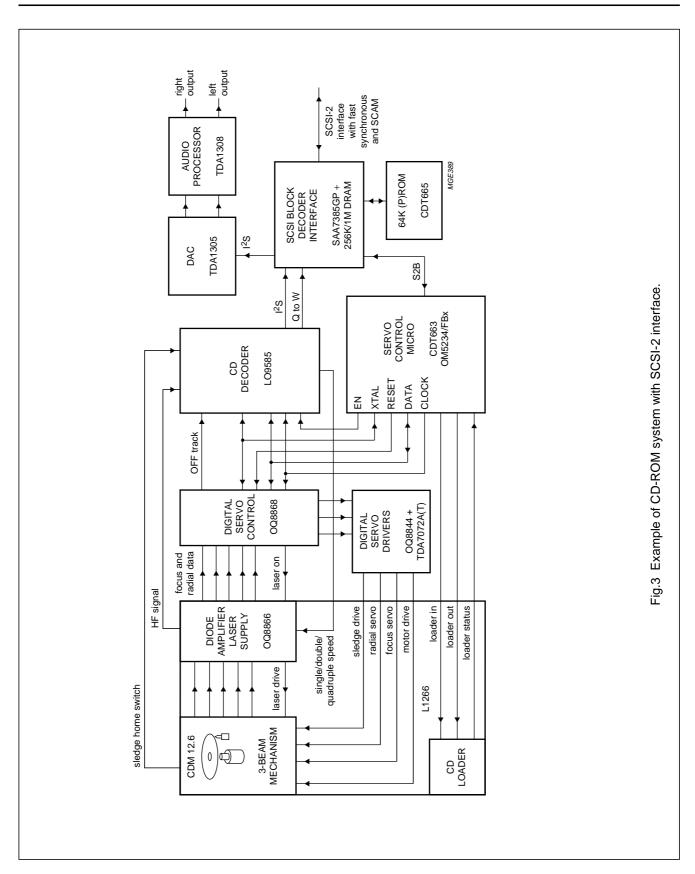

#### 5 BLOCK DIAGRAM

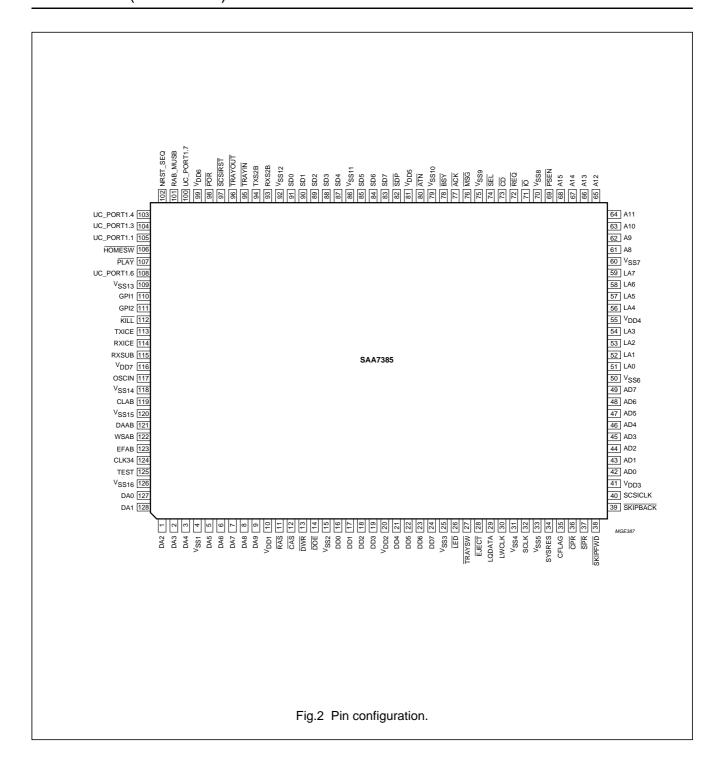

#### 6 PINNING

All input, output and bidirectional signals are TTL level unless otherwise stated (Pull-Down = PD25 = 25  $\mu$ A; Pull-Up = PU25 = 25  $\mu$ A, PU400 = 400  $\mu$ A; Slew = S2 = 2 mA, S4 = 4 mA; CMOS slew = CMOS S2 = CMOS 2 = 2 mA; SCSI pad = SCSI = 48 mA).

| SYMBOL           | PIN | I/O | PAD | DESCRIPTION               |

|------------------|-----|-----|-----|---------------------------|

| DA2              | 1   | 0   | S4  | DRAM address bus; bit DA2 |

| DA3              | 2   | 0   | S4  | DRAM address bus; bit DA3 |

| DA4              | 3   | 0   | S4  | DRAM address bus; bit DA4 |

| V <sub>SS1</sub> | 4   | _   | _   | ground 1                  |

| DA5              | 5   | 0   | S4  | DRAM address bus; bit DA5 |

| DA6              | 6   | 0   | S4  | DRAM address bus; bit DA6 |

| DA7              | 7   | 0   | S4  | DRAM address bus; bit DA7 |

| DA8              | 8   | 0   | S4  | DRAM address bus; bit DA8 |

| DA9              | 9   | 0   | S4  | DRAM address bus; bit DA9 |

| $V_{DD1}$        | 10  | _   | _   | power supply 1            |

SAA7385

| SYMBOL           | PIN | I/O | PAD                 | DESCRIPTION                                          |

|------------------|-----|-----|---------------------|------------------------------------------------------|

| RAS              | 11  | 0   | S4                  | DRAM row address section; active LOW                 |

| CAS              | 12  | 0   | S4                  | DRAM column address selection; active LOW            |

| DWR              | 13  | 0   | S4                  | DRAM write; active LOW                               |

| DOE              | 14  | 0   | S4                  | DRAM output enable; active LOW                       |

| V <sub>SS2</sub> | 15  | _   | _                   | ground 2                                             |

| DD0              | 16  | I/O | 4 mA, Schmitt, PD25 | DRAM data bus; bit DD0                               |

| DD1              | 17  | I/O | 4 mA, Schmitt, PD25 | DRAM data bus; bit DD1                               |

| DD2              | 18  | I/O | 4 mA, Schmitt, PD25 | DRAM data bus; bit DD2                               |

| DD3              | 19  | I/O | 4 mA, Schmitt, PD25 | DRAM data bus; bit DD3                               |

| $V_{DD2}$        | 20  | _   | _                   | power supply 2                                       |

| DD4              | 21  | I/O | 4 mA, Schmitt, PD25 | DRAM data bus; bit DD4                               |

| DD5              | 22  | I/O | 4 mA, Schmitt, PD25 | DRAM data bus; bit DD5                               |

| DD6              | 23  | I/O | 4 mA, Schmitt, PD25 | DRAM data bus; bit DD6                               |

| DD7              | 24  | I/O | 4 mA, Schmitt, PD25 | DRAM data bus; bit DD7                               |

| V <sub>SS3</sub> | 25  | _   | _                   | ground 3                                             |

| LED              | 26  | 0   | 24 mA, CMOS test    | panel LED; active LOW; WTGCTL(4)                     |

| TRAYSW           | 27  | I   | Schmitt, PU25       | active LOW when tray is in                           |

| EJECT            | 28  | I   | Schmitt, PU25       | opens tray; active LOW                               |

| LQDATA           | 29  | 0   | 2 mA                | serial data to DAC                                   |

| LWCLK            | 30  | 0   | 2 mA                | word strobe to DAC                                   |

| V <sub>SS4</sub> | 31  | _   | _                   | ground 4                                             |

| SCLK             | 32  | 0   | 2 mA                | data serial clock                                    |

| V <sub>SS5</sub> | 33  | _   | _                   | ground 5                                             |

| SYSRES           | 34  | 0   | 2 mA, PU25          | system reset; OR of POR, SCSIRST and watch-dog timer |

| CFLAG            | 35  | I   | Schmitt, PU400      | C1 and C2 status                                     |

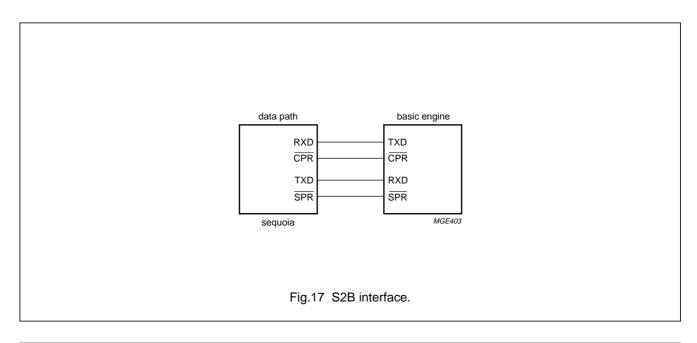

| CPR              | 36  | 0   | 2 mA                | S2B interface ready to accept data; active LOW       |

| SPR              | 37  | I   | Schmitt             | S2B interface ready to send data; active LOW         |

| SKIPFWD          | 38  | I   | Schmitt, PU25       | skip forwards; active LOW; RDSW(3)                   |

| SKIPBACK         | 39  | I   | Schmitt, PU25       | skip backwards; active LOW; RDSW(2)                  |

| SCSICLK          | 40  | I   | standard            | SCSI interface clock                                 |

| $V_{DD3}$        | 41  | _   | _                   | power supply 3                                       |

| AD0              | 42  | I/O | S4, Schmitt         | microcontroller multiplexed data bus; bit AD0        |

| AD1              | 43  | I/O | S4, Schmitt         | microcontroller multiplexed data bus; bit AD1        |

| AD2              | 44  | I/O | S4, Schmitt         | microcontroller multiplexed data bus; bit AD2        |

| AD3              | 45  | I/O | S4, Schmitt         | microcontroller multiplexed data bus; bit AD3        |

| AD4              | 46  | I/O | S4, Schmitt         | microcontroller multiplexed data bus; bit AD4        |

| AD5              | 47  | I/O | S4, Schmitt         | microcontroller multiplexed data bus; bit AD5        |

| AD6              | 48  | I/O | S4, Schmitt         | microcontroller multiplexed data bus; bit AD6        |

| AD7              | 49  | I/O | S4, Schmitt         | microcontroller multiplexed data bus; bit AD7        |

| V <sub>SS6</sub> | 50  | _   | _                   | ground 6                                             |

| LA0              | 51  | 0   | CMOS S2, PU25       | EPROM latched lower address; bit LA0                 |

SAA7385

| SYMBOL            | PIN | I/O | PAD           | DESCRIPTION                                                |  |

|-------------------|-----|-----|---------------|------------------------------------------------------------|--|

| LA1               | 52  | 0   | CMOS S2, PU25 | EPROM latched lower address; bit LA1                       |  |

| LA2               | 53  | 0   | CMOS S2, PU25 | EPROM latched lower address; bit LA2                       |  |

| LA3               | 54  | 0   | CMOS S2, PU25 | EPROM latched lower address; bit LA3                       |  |

| V <sub>DD4</sub>  | 55  | _   | _             | power supply 4                                             |  |

| LA4               | 56  | 0   | CMOS S2, PU25 | EPROM latched lower address; bit LA4                       |  |

| LA5               | 57  | 0   | CMOS S2, PU25 | EPROM latched lower address; bit LA5                       |  |

| LA6               | 58  | 0   | CMOS S2, PU25 | EPROM latched lower address; bit LA6                       |  |

| LA7               | 59  | 0   | CMOS S2, PU25 | EPROM latched lower address; bit LA7                       |  |

| V <sub>SS7</sub>  | 60  | _   | _             | ground 7                                                   |  |

| A8                | 61  | 0   | CMOS S2, PU25 | EPROM upper address; bit A8                                |  |

| A9                | 62  | 0   | CMOS S2, PU25 | EPROM upper address; bit A9                                |  |

| A10               | 63  | 0   | CMOS S2, PU25 | EPROM upper address; bit A10                               |  |

| A11               | 64  | 0   | CMOS S2, PU25 | EPROM upper address; bit A11                               |  |

| A12               | 65  | 0   | CMOS S2, PU25 | EPROM upper address; bit A12                               |  |

| A13               | 66  | 0   | CMOS S2, PU25 | EPROM upper address; bit A13                               |  |

| A14               | 67  | 0   | CMOS S2, PU25 | EPROM upper address; bit A14                               |  |

| A15               | 68  | 0   | CMOS S2, PU25 | EPROM upper address; bit A15                               |  |

| PSEN              | 69  | 0   | CMOS 2, PU25  | program store enable; active LOW                           |  |

| V <sub>SS8</sub>  | 70  | _   | _             | ground 8                                                   |  |

| ĪŌ                | 71  | I/O | SCSI          | SCSI phase signal, active LOW                              |  |

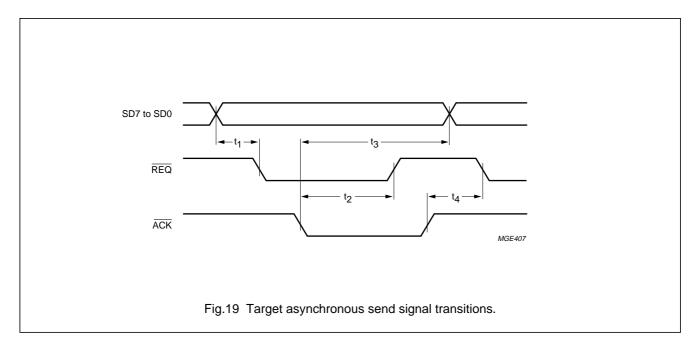

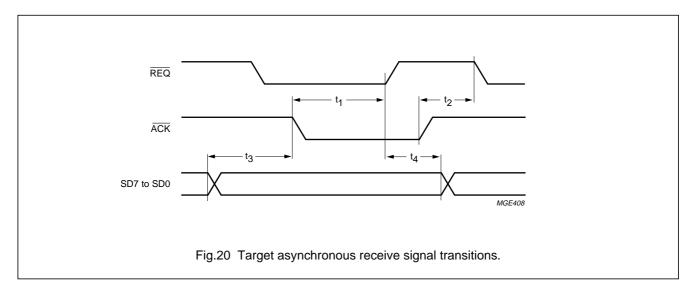

| REQ               | 72  | I/O | SCSI          | SCSI request, active LOW                                   |  |

| CD                | 73  | I/O | SCSI          | SCSI phase signal, active LOW                              |  |

| SEL               | 74  | I/O | SCSI          | SCSI select, active LOW                                    |  |

| V <sub>SS9</sub>  | 75  | _   | _             | ground 9                                                   |  |

| MSG               | 76  | I/O | SCSI          | SCSI phase signal, active LOW                              |  |

| ACK               | 77  | I/O | SCSI          | SCSI acknowledge, active LOW                               |  |

| BSY               | 78  | I/O | SCSI          | SCSI busy, active LOW                                      |  |

| V <sub>SS10</sub> | 79  | _   | _             | ground 10                                                  |  |

| ĀTN               | 80  | I/O | SCSI          | output in initiator mode; input in target mode, active LOW |  |

| $V_{DD5}$         | 81  | _   | _             | power supply 5                                             |  |

| SDP               | 82  | I/O | SCSI          | SCSI parity, active LOW                                    |  |

| SD7               | 83  | I/O | SCSI          | SCSI data bus; bit SD7                                     |  |

| SD6               | 84  | I/O | SCSI          | SCSI data bus; bit SD6                                     |  |

| SD5               | 85  | I/O | SCSI          | SCSI data bus; bit SD5                                     |  |

| V <sub>SS11</sub> | 86  | _   | _             | ground 11                                                  |  |

| SD4               | 87  | I/O | SCSI          | SCSI data bus; bit SD4                                     |  |

| SD3               | 88  | I/O | SCSI          | SCSI data bus; bit SD3                                     |  |

| SD2               | 89  | I/O | SCSI          | SCSI data bus; bit SD2                                     |  |

| SD1               | 90  | I/O | SCSI          | SCSI data bus; bit SD1                                     |  |

| SD0               | 91  | I/O | SCSI          | SCSI data bus; bit SD0                                     |  |

| V <sub>SS12</sub> | 92  | _   | _             | ground 12                                                  |  |

# Error correction and host interface IC for CD-ROM (SEQUOIA)

SAA7385

| SYMBOL            | PIN | I/O | PAD           | DESCRIPTION                                               |

|-------------------|-----|-----|---------------|-----------------------------------------------------------|

| RXS2B             | 93  | I   | Schmitt, PU25 | S2B interface receive                                     |

| TXS2B             | 94  | 0   | 4 mA          | S2B interface transmit                                    |

| TRAYIN            | 95  | I/O | 4 mA, PD25    | tray extend control; active LOW (general purpose signal)  |

| TRAYOUT           | 96  | I/O | 4 mA, PD25    | tray retract control; active LOW (general purpose signal) |

| SCSIRST           | 97  | I   | Schmitt       | SCSI reset, active LOW; also causes a system reset        |

| POR               | 98  | I   | CMOS          | power-on reset; active LOW                                |

| V <sub>DD6</sub>  | 99  | _   | _             | power supply 6                                            |

| UC_PORT1.7        | 100 | I/O | CMOS 2, PU25  | drive speed select; microcontroller port 1.7              |

| RAB_MUSB          | 101 | I/O | CMOS 2, PU25  | RD/WR, acknowledge; microcontroller port 1.2              |

| NRST_SEQ          | 102 | I/O | CMOS 2, PU25  | reset to engine; microcontroller port 1.5                 |

| UC_PORT1.4        | 103 | I/O | CMOS 2, PU25  | general purpose microcontroller I/O port; port 1.4        |

| UC_PORT1.3        | 104 | I/O | CMOS 2, PU25  | general purpose microcontroller I/O port; port 1.3        |

| UC_PORT1.1        | 105 | I/O | CMOS 2, PU25  | general purpose microcontroller I/O port; port 1.1        |

| HOMESW            | 106 | I/O | 2 mA, PU25    | actuator sled home; active LOW; microcontroller port 1.0  |

| PLAY              | 107 | I   | Schmitt       | laser on and focused status; active LOW; RDSW(4)          |

| UC_PORT1.6        | 108 | I/O | CMOS 2, PU25  | general purpose microcontroller I/O port; port 1.6        |

| V <sub>SS13</sub> | 109 | _   | _             | ground 13                                                 |

| GPI1              | 110 | I   | Schmitt, PU25 | general purpose input; microcontroller port 3.4           |

| GPI2              | 111 | I   | Schmitt, PU25 | general purpose input; microcontroller port 3.5           |

| KILL              | 112 | I   | Schmitt, PU25 | shut off audio; active LOW                                |

| TXICE             | 113 | 0   | 4 mA          | debug UART output; from 80C32 serial port                 |

| RXICE             | 114 | I   | Schmitt, PU25 | debug UART input; to 80C32 serial port                    |

| RXSUB             | 115 | I   | Schmitt, PU25 | sub-code input                                            |

| $V_{DD7}$         | 116 | _   | _             | power supply 7                                            |

| OSCIN             | 117 | I   | standard      | master input clock; 34 or 16 MHz                          |

| V <sub>SS14</sub> | 118 | _   | _             | ground 14                                                 |

| CLAB              | 119 | I   | Schmitt       | clock                                                     |

| V <sub>SS15</sub> | 120 | _   | _             | ground 15                                                 |

| DAAB              | 121 | I   | Schmitt       | data                                                      |

| WSAB              | 122 | I   | Schmitt       | word strobe                                               |

| EFAB              | 123 | Ī   | Schmitt       | error flag                                                |

| CLK34             | 124 | 0   | 2 mA          | 34 MHz output clock                                       |

| TEST              | 125 | I   | Schmitt, PD25 | test pin; must be ground                                  |

| V <sub>SS16</sub> | 126 | _   | _             | ground 16                                                 |

| DA0               | 127 | 0   | S4            | DRAM address bus; bit DA0                                 |

| DA1               | 128 | 0   | S4            | DRAM address bus; bit DA1                                 |

**SAA7385**

**SAA7385**

### Error correction and host interface IC for CD-ROM (SEQUOIA)

**SAA7385**

#### 7 FUNCTIONAL DESCRIPTION

#### 7.1 80C32 microcontroller

The standard specification for details of the operation for this part may be found in any data sheet covering the 80C32 microcontroller. The one deviation from a normal 80C32 is the addition of all of the control registers for the special function register map for the 80C32. All of the SAA7385 control registers, including the 53CF94 control registers appear within this space.

#### 7.2 53CF94 fast SCSI controller

The details of operation of this block may be found in the "53CF94 data manual". Two deviations from the operation of a normal 53CF94 have been made. The first is that the part supports single-ended SCSI bus operation only. The second deviation is the additional feature of mapping the control registers into the 80C32 special function register map as previously mentioned.

#### 7.3 Input clock doubler

To facilitate compatibility of the SAA7385 with the maximum number of CD decoders, a clock doubler has been included. This clock doubler may take a 16.9344 MHz clock and double this when requested to do so by the microcontroller. Logic has been included to remove the possibility of a 'runt' clock pulse when the doubler is engaged. Once engaged, the only way to disengage it is via a reset condition.

#### 7.4 Front-end

The front-end is comprised of many sub-sections.

#### 7.4.1 BLOCK DECODER

The block decoder first reverses the bits of each received byte and then runs them through a linear feedback shift register to be de-scrambled. The polynomial used to de-scramble the serial data is as follows: X<sup>15</sup> + X + 1

It also detects and tests the synchronization field and will start the data clock when commanded. The de-scrambled header is assembled into four registers (MODE, MINS, SECS and FRMS) with header ready and header error status (see HDRRDY and HDRERR in RDDSTAT). The data clock does not have to be enabled to receive valid headers.

Also included in this section is the logic required to decide when to start collecting data and sub-code information taken from the synchronization signal.

#### 7.4.2 SECTOR SEQUENCER

The sector sequencer de-serializes the data and error flags from the block decoder and determines when to:

- · Write data to the buffer

- · Write flags to the buffer

- Test the header to determine the Mode

- Test the sub-header to determine the Form

- Test the CRC

- End the sector and write the status byte to the buffer.

Included in the sector sequencer is the CRC generator which checks each Yellow Book or Green Book sector as it is shifted into the SAA7385 in accordance with the following polynomial:

$$X^{32} + X^{31} + X^{16} + X^{15} + X^4 + X^3 + X + 1$$

The status of each sector is saved and written to the buffer at the end of the sector.

#### 7.4.3 SUB-CODE RECEIVE AND Q-CHANNEL EXTRACTOR

A UART which samples asynchronous bits on a 24 clocks per bit basis is included. This is required because Philips decoders output the sub-code data at nominally 24 clocks per bit, but not synchronized to the data. Also included is a sub-code synchronization detector which senses the beginning of each new sector of sub-code information. The serial sub-code information is assembled into bytes in the following order:

Data bits 7 to 0 = 0, Q, R, S, T, U, V and W.

As each byte is assembled, it is sent to the buffer manager to be written to the DRAM buffer. At the same time, the Q-channel bits are assembled into bytes and sent to the buffer. All Q-channel bytes except CRC are sorted in registers for use by the microcontroller. The track, mode, minutes, seconds and frames bytes (RDTK, RDMD, RDMN, RDSC and RDFM) are also stored in registers for use by the microcontroller. The Q-channel CRC (last two bytes) is checked just before the end of the sub-code sector. If the CRC check fails, BADQ in RDDSTAT is available to the microcontroller and is written into the buffer at the end of the sector. When the five Q-channel registers have been updated, QFRMRDY in RDDSTAT is set. The five Q-channel registers are valid while QFRMRDY is set. In the audio mode, HDRRDY in RDDSTAT generates this interrupt, but the QFRMRDY bit will still be available as status to the microcontroller.

### Error correction and host interface IC for CD-ROM (SEQUOIA)

**SAA7385**

#### 7.4.4 C-FLAG RECEIVER

The C-flag bits, or corrector flags, are also 24 data clocks long and reception of these bits is achieved using the same method as for the sub-code; in this event, the C-flag data is synchronized to the data. The difference is that only one bit is used; F1, the absolute time synchronization information. When in audio mode and ENABRED in FECTL is set, receipt of F1 set will start the internal data clock after the next rising edge of word strobe (WSAB) which is the left channel sample when the CD decoder is programmed for EIAJ audio format. When in audio mode, the Q-channel information provides the MSF address and the F1 flag provides the start of frame information; together these provide an absolute byte address on the disc.

#### 7.4.5 S2B UART

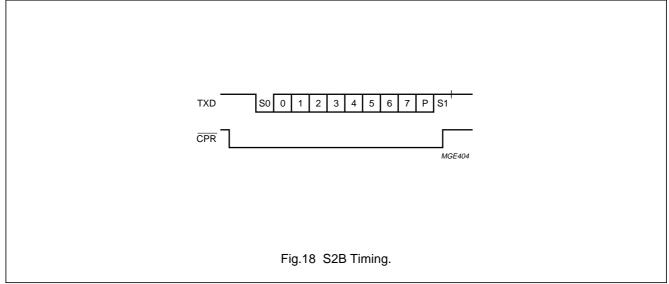

This UART is provided for remote debugging of the firmware. It is hard-wired for one start-bit, eight data bits, a parity bit and one stop bit. Parity testing can be programmed to be either odd parity or even parity. Parity error and over-run status are provided via PE and OVRRUN in S2BSTAT. Selectable baud rates of 31.25, 62.5 and 187.5 kbaud are available via ICESEL1 and ICESEL0 in BRGSEL.

#### 7.4.6 WATCH-DOG TIMER

A pair of counters are included which output a 967  $\mu$ s reset pulse to the entire chip and the SYSRES pin if the timer is not reset during the 212 ms time-out period. The watch-dog timer is reset by setting RWMD in FECTL HIGH then LOW. If RWMD is left HIGH, the watch-dog function is disabled.

#### 7.4.7 GLUE LOGIC (GLIC)

The final block of logic in the front-end consists of: a programmable, linear pulse-width modulator for spindle-motor control; an address de-multiplexer for the address/data bus of the microcontroller; plus audio multiplexing and muting circuitry for full control of Red Book audio data to an external Digital-to-Analog Converter (DAC).

#### 7.4.8 BUFFER MANAGER

The buffer manager provides the arbitration for the different processes that wish to access the DRAM buffer. These processes include the front-end, microcontroller requests, ECC accesses, SCSI interface requests and DRAM refreshing. The DRAM control logic will start an access on the next rising edge of the clock after a request is received. If two or more requests are pending then the priority is as follows:

- 1. Front-end (highest priority)

- 2. Microcontroller requests

- SCSI interface requests

- 4. ECC requests (lowest priority).

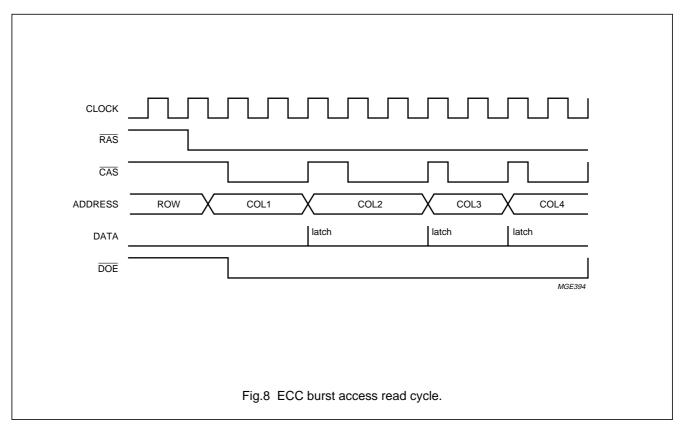

A refresh cycle is required every 15.6  $\mu$ s and will be granted priority for one access. A burst access by ECC or SCSI will only be interrupted by a higher priority access request.

In addition to the priority logic, logic is required for the front-end sources of data. The priority is: frame data (highest), flag data, sub-code data, Q-channel data and finally status byte. All front-end sources are granted priority over the SCSI logic, ECC, refresh and data will be written into the frame store during the next cycle. However, the microcontroller has priority over the lower three front-end sources and will be granted an access after front-end frame data or flag data is written to memory.

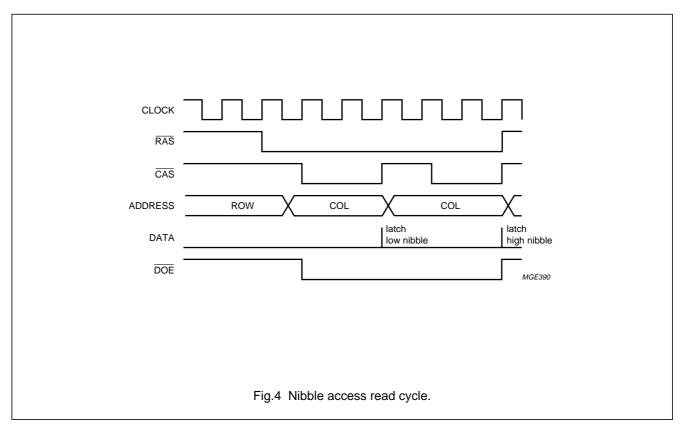

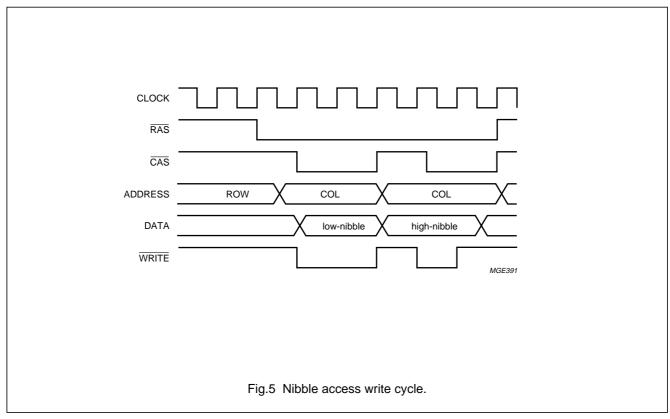

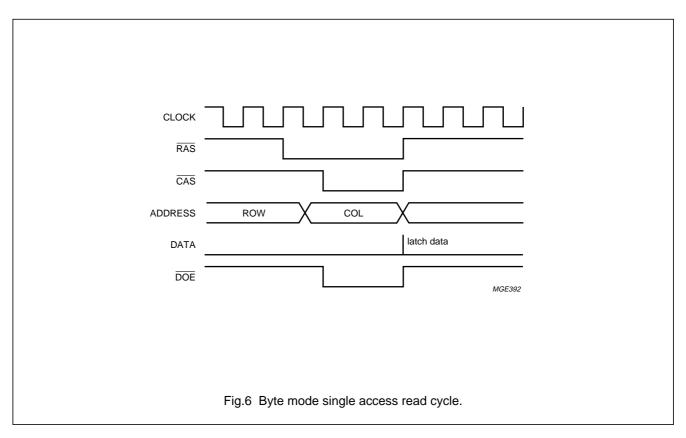

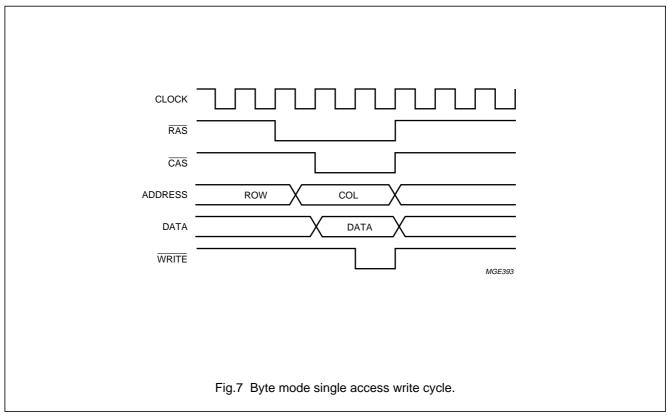

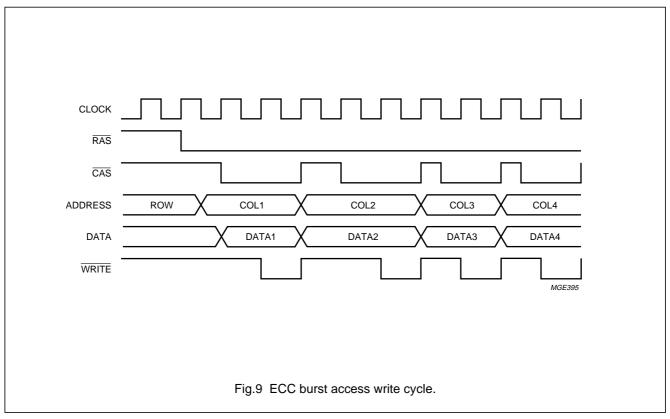

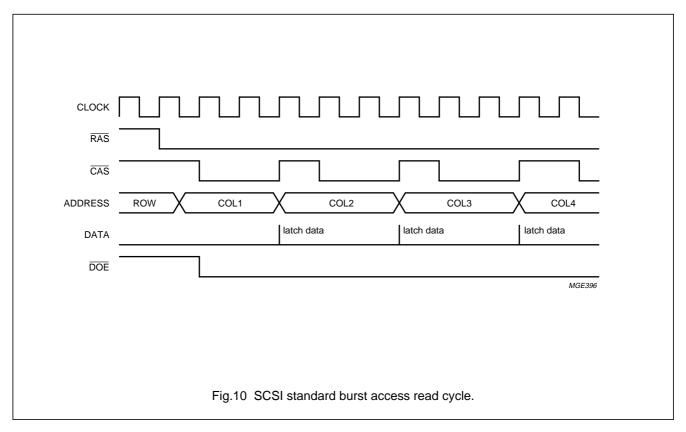

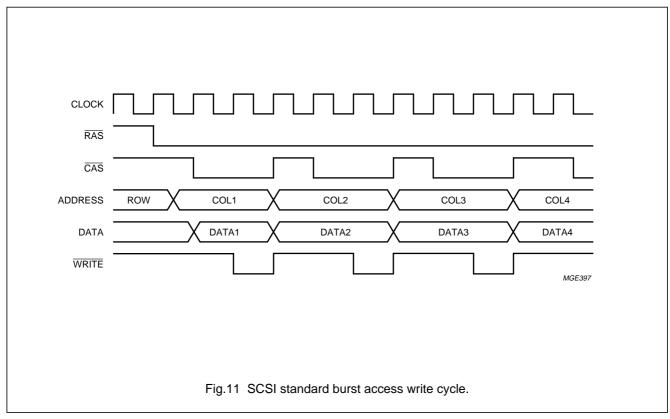

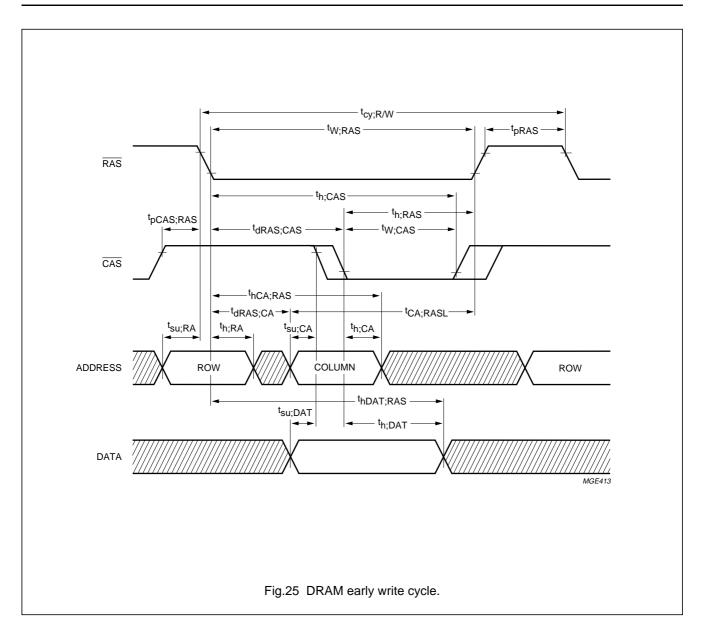

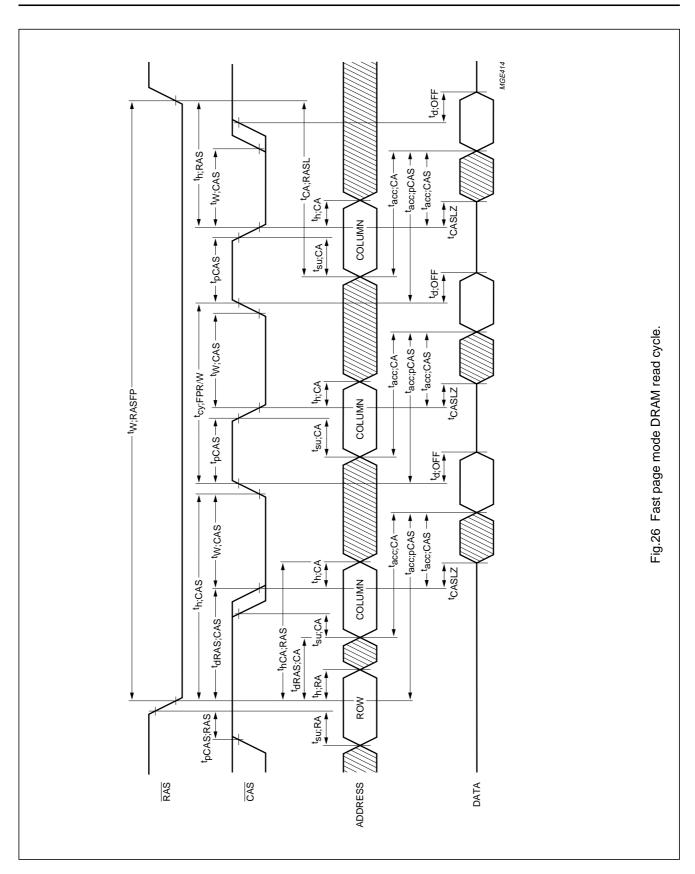

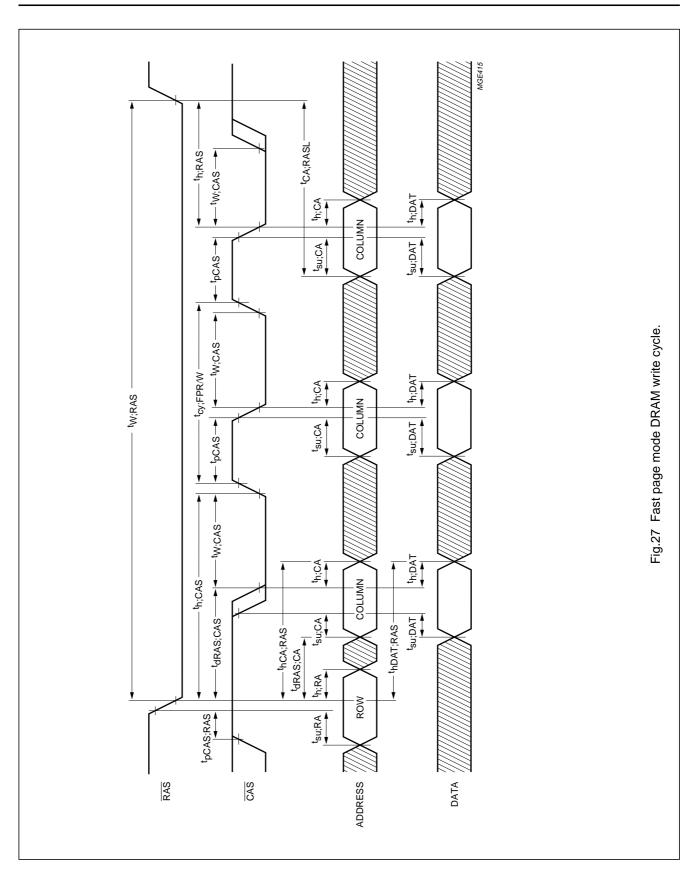

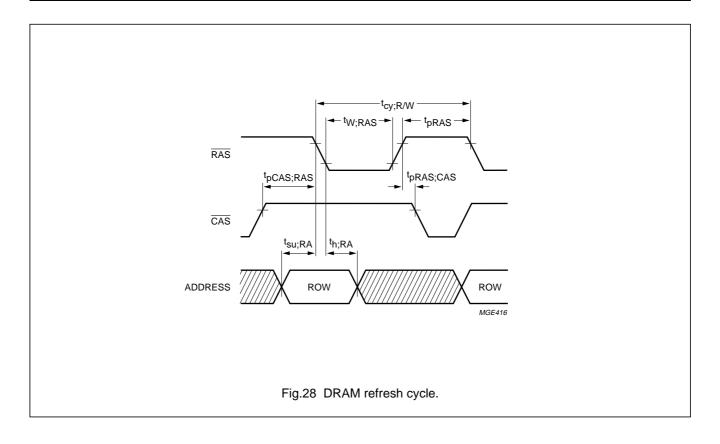

The required timing (see Figs 4 to 11) operate with the industry standard 70 ns DRAMs. The interface is designed to operate with one or two DRAMs using:  $256 \text{ kbit} \times 4 \text{ or}$  1 Mbit  $\times$  4 devices. If a single DRAM is connected, all access cycles require a page mode cycle to load both the high and the low nibble of data. With a byte-wide memory attached, a single byte cycle takes five clock cycles of 29.5 ns each, totalling 147.5 ns. In nibble mode, a single byte cycle takes 236 ns.

**SAA7385**

**SAA7385**

**SAA7385**

**SAA7385**

### Error correction and host interface IC for CD-ROM (SEQUOIA)

**SAA7385**

#### 8 MICROCONTROLLER INTERFACE

#### 8.1 Microcontroller interface status register

Table 1 NUM\_COR register: 0xF08E

| MNEMONIC | R/W | DATA BYTE            |   |   |   |   |   |   |   |

|----------|-----|----------------------|---|---|---|---|---|---|---|

| MNEMONIC |     | 7                    | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| NUM_COR  | R   | NUM_COR7 to NUM_COR0 |   |   |   |   |   |   |   |

Register 0xF08E indicates the number of corrections performed during the most recently executed CORRECT\_P\_SYNDROMES or CORRECT\_Q\_SYNDROMES command. Note that NUM\_COR is only valid after completion of the CORRECT\_P\_SYNDROMES or CORRECT\_Q\_SYNDROMES command, and becomes invalid upon execution of any other command.

Table 2 ECC\_STATUS register: 0xF086

| MNEMONIC   | R/W | DATA BYTE |   |   |         |         |        |        |         |

|------------|-----|-----------|---|---|---------|---------|--------|--------|---------|

| WINEWONIC  |     | 7         | 6 | 5 | 4       | 3       | 2      | 1      | 0       |

| ECC_STATUS | R   | _         | _ | _ | FLG_EQ0 | CRC_EQ0 | PS_EQ0 | QS_EQ0 | ECC_ACT |

Register 0xF086 provides status information on the current or last ECC command.

Table 3 ECC\_STATUS definitions

| MNEMONIC | DESCRIPTION                                                                          |

|----------|--------------------------------------------------------------------------------------|

| ECC_ACT  | asserted while a command other than ASSERT_ABORT or RELEASE_ABORT remains active     |

| QS_EQ0   | asserted when all Q syndromes are zero                                               |

| PS_EQ0   | asserted when all P syndromes are zero                                               |

| CRC_EQ0  | asserted when the CRC remainder calculated by the CRC_CALCULATE command is all zeros |

| FLG_EQ0  | asserted when all flag bytes in ECC RAM are zero                                     |

#### 8.2 Microcontroller interface command register

Table 4 ECCCTL register: 0xF085

| MNEMONIC | R/W | DATA BYTE |   |   |   |                              |   |   |   |

|----------|-----|-----------|---|---|---|------------------------------|---|---|---|

|          |     | 7         | 6 | 5 | 4 | 3                            | 2 | 1 | 0 |

| ECCCTL   | R/W | -         | _ | _ | _ | ECC_COMMAND3 to ECC_COMMAND0 |   |   |   |

The ECC\_COMMAND definitions are explained in Table 5.

# Error correction and host interface IC for CD-ROM (SEQUOIA)

**SAA7385**

Table 5

Definitions of ECC\_COMMAND3 to ECC\_COMMAND0

| EEC_COMMAND | DESCRIPTION                              |

|-------------|------------------------------------------|

| 0000        | ASSERT_ABORT                             |

| 0001        | RELEASE_ABORT                            |

| 0010        | CALCULATE_SYNDROMES (not Mode 2, Form 1) |

| 0011        | CALCULATE_SYNDROMES (Mode 2, Form 1)     |

| 0100        | CRC_RECALCULATE (not Mode 2, Form 1)     |

| 0101        | CRC_RECALCULATE (Mode 2, Form 1)         |

| 0110        | COPY_RESULTS (not Mode 2, Form 1)        |

| 0111        | COPY_RESULTS (Mode 2, Form 1)            |

| 1000        | CORRECT_P_SYNDROMES                      |

| 1001        | CORRECT_Q_SYNDROMES                      |

| 1100        | TEST_ECC_ROM                             |

| 1101        | TEST_ECC_RAM_READ                        |

| 1110        | TEST_ECC_RAM_WRITE                       |

Table 6 Command descriptions

| COMMAND             | DESCRIPTION                                                                                                                                                                                                                                                                                     |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ASSERT_ABORT        | Terminates any currently active operation and re-initializes the ECC logic. Remains in reset state until occurrence of the RELEASE_ABORT command. At power-on reset, the ECC is in the ASSERT_ABORT state. All microcontroller status bits are reset when the ECC is in the ASSERT_ABORT state. |

| RELEASE_ABORT       | Terminates the ASSERT_ABORT command and enables activation of other commands.                                                                                                                                                                                                                   |

| CRC_RECALCULATE     | Calculate CRC remainder buffer data, storing result in ECC RAM and updating microcontroller status bit CRC_EQ0. Mode 2, Form 1 uses address 16 : 2075, or 0 : 2067; note 1.                                                                                                                     |

| CALCULATE_SYNDROMES | Prepares buffer for correction, calculates P and Q syndromes, and copies error flags and CRC remainder from buffer to ECC RAM. The microcontroller status bits PS_EQ0, QS_EQ0 and FLAGS_EQ0 are updated at the end of this operation.                                                           |

|                     | Copy header from buffer to ECC RAM (Mode 2, Form 1 only)                                                                                                                                                                                                                                        |

|                     | 2. Write to the buffer. Not Mode 2, Form 1:                                                                                                                                                                                                                                                     |

|                     | Address 0 $\rightarrow$ 0x00; Address 1 : 10 $\rightarrow$ 0xFF; Address 11 $\rightarrow$ 0x00; Address 2068 : 2075 $\rightarrow$ 0x00                                                                                                                                                          |

|                     | Mode 2, Form 1:                                                                                                                                                                                                                                                                                 |

|                     | Address $0 \rightarrow 0x00$ ; Add 1 : $10 \rightarrow 0xFF$ ; Add 11 : $15 \rightarrow 0x00$                                                                                                                                                                                                   |

|                     | 3. Read header and frame data from buffer to calculate P and Q syndromes psyn[0:85].s1, psyn[0:85].s0, qsyn[0:51].s1 and qsyn[0:51].s0, storing results in ECC RAM; see Table 76                                                                                                                |

|                     | 4. Copy error flags from buffer to ECC RAM                                                                                                                                                                                                                                                      |

|                     | 5. Copy CRC remainder from buffer to ECC RAM                                                                                                                                                                                                                                                    |

|                     | 6. Update microcontroller status bits PS_EQ0, QS_EQ0 and FLAGS_EQ0.                                                                                                                                                                                                                             |

### Error correction and host interface IC for CD-ROM (SEQUOIA)

**SAA7385**

| COMMAND             | DESCRIPTION                                                                                                                                                     |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| COPY_RESULTS        | Copies current ECC RAM contents to the buffer memory:                                                                                                           |

|                     | Copy header flags from ECC RAM to buffer (Mode 2, Form 1 only)                                                                                                  |

|                     | 2. Copy error Flags from ECC RAM to buffer                                                                                                                      |

|                     | Copy CRC remainder from ECC RAM to buffer                                                                                                                       |

|                     | 4. Copy P syndromes from ECC RAM to buffer                                                                                                                      |

|                     | 5. Copy Q syndromes from ECC RAM to buffer.                                                                                                                     |

| CORRECT_P_SYNDROMES | Scan all P syndromes and perform P-syndrome calculation. The microcontroller status bits PS_EQ0, QS_EQ0 and FLAGS_EQ0 are updated at the end of this operation. |

| CORRECT_Q_SYNDROMES | Scan all Q syndromes and perform Q-syndrome calculation. The microcontroller status bits PS_EQ0, QS_EQ0 and FLAGS_EQ0 are updated at the end of this operation. |

| TEST_ECC_ROM        | Read each exponent and log in the alpha ROM to the NUM_COR register. This command may only be terminated by the ASSERT_ABORT command.                           |

| TEST_ECC_RAM_READ   | Read ECC RAM addresses 0 : 591 and copy to buffer addresses 0 : 591.                                                                                            |

| TEST_ECC_RAM_WRITE  | Read buffer addresses 0 : 591 and copy to ECC RAM addresses 0 : 591.                                                                                            |

#### Note

1. 16: 2075 and 0: 2067 are address frame offsets. The frame buffer organization is shown in Table 75.

#### 8.3 Microcontroller interrupts

An interrupt pulse is generated upon completion of any of the following commands:

- CALCULATE\_SYNDROMES (not Mode 2, Form 1)

- CALCULATE\_SYNDROMES (Mode 2, Form 1)

- CRC\_RECALCULATE (not Mode 2, Form 1)

- CRC\_RECALCULATE (Mode 2, Form 1)

- COPY\_RESULTS (not Mode 2, Form 1)

- COPY\_RESULTS (Mode 2, Form 1)

- CORRECT\_P\_SYNDROMES

- CORRECT\_Q\_SYNDROMES

- TEST\_ECC\_ROM

- TEST\_ECC\_RAM\_READ

- TEST\_ECC\_RAM\_WRITE.

If a command is aborted by the ASSERT\_ABORT command, a spurious interrupt may be generated within five clock cycles of the ASSERT\_ABORT command.

### Error correction and host interface IC for CD-ROM (SEQUOIA)

**SAA7385**

Table 7 Command execution times

| COMMAND                                  | CYCLES | TIME (μs)<br>at 33 MHz | MEMORY<br>ACCESSES |

|------------------------------------------|--------|------------------------|--------------------|

| CALCULATE_SYNDROMES (not Mode 2, Form 1) | 5604   | 186.8                  | 2658               |

| CALCULATE_SYNDROMES (Mode 2, Form 1)     | 5600   | 186.7                  | 2654               |

| CRC_RECALCULATE (not Mode 2, Form 1)     | 4136   | 137.9                  | 2068               |

| CRC_RECALCULATE (Mode 2, Form 1)         | 4120   | 137.3                  | 2060               |

| COPY_RESULTS (not Mode 2, Form 1)        | 1148   | 38.3                   | 574                |

| COPY_RESULTS (Mode 2, Form 1)            | 1156   | 38.5                   | 578                |

| CORRECT_P_SYNDROMES                      | 1466   | 48.9                   | 0                  |

| (maximum addition per correction)        | 157    | 5.2                    | 2                  |

| CORRECT_Q_SYNDROMES                      | 888    | 29.6                   | 0                  |

| (maximum addition per correction)        | 167    | 5.6                    | 2                  |

| TEST_ECC_RAM_READ                        | 1184   | 39.5                   | 592                |

| TEST_ECC_RAM_WRITE                       | 1184   | 39.5                   | 592                |

All times indicated reflect two clock cycles per memory access for all accesses other than P and Q corrections. P and Q corrections reflect seven clock cycles per memory access. Execution times will be extended due to refresh timing, other buffer traffic, and configuration of nibble-wide memory.

#### 8.3.1 INTERRUPT REGISTER DEFINITIONS

Two registers are used to control the operation of the interrupt logic. The register INTRMSK allows each interrupt to be enabled or disabled. INTRMSK and INTRFLG are cleared on reset to initially disable and clear all interrupts; the output latch controlling the INT line is set on a reset; this must be cleared by writing 0x00 to INTRFLG. To enable an interrupt, the bit that corresponds to the interrupt in INTRFLG must be set. The INTRFLG register shows the status of the interrupts. If any bit is HIGH then an interrupt has occurred since the last time the bit was cleared. Writing a zero to any bit location in INTRFLG will clear the corresponding interrupt. If a masked interrupt occurs, the microcontroller can still detect the occurrence because the event is still posted in INTRFLG.

Table 8 Interrupt mask register: 0xF0FB

| MNEMONIC      | R/W |       | DATA BYTE |       |       |       |       |       |       |  |  |  |

|---------------|-----|-------|-----------|-------|-------|-------|-------|-------|-------|--|--|--|

| MINEMONIC R/W |     | 7     | 6         | 5     | 4     | 3     | 2     | 1     | 0     |  |  |  |

| INTRMSK       | R/W | MASK7 | MASK6     | MASK5 | MASK4 | MASK3 | MASK2 | MASK1 | MASK0 |  |  |  |

Each bit in register 0xF0FB corresponds to the interrupt at the same bit location in register 0xF0FC. To enable an interrupt, the bit in this register must be set HIGH.

Table 9 Interrupt flag register: 0xF0FC

| MNEMONIC | R/W   |   | DATA BYTE |         |         |        |        |         |         |  |  |  |  |

|----------|-------|---|-----------|---------|---------|--------|--------|---------|---------|--|--|--|--|

| MNEMONIC | IX/VV | 7 | 6         | 5       | 4       | 3      | 2      | 1       | 0       |  |  |  |  |

| INTRFLG  | R/W   | _ | FETXINT   | FERXINT | ECC_COR | FE_HDR | FE2352 | STR_LST | FRM_STR |  |  |  |  |

If any bit is set in this register (Table 9) then an interrupt may be sent to the microcontroller. Table 10 shows when the interrupts are asserted; assuming the corresponding mask bit is set.

### Error correction and host interface IC for CD-ROM (SEQUOIA)

**SAA7385**

Table 10 INTRFLG field descriptions

| FIELD    | DESCRIPTION                                         |

|----------|-----------------------------------------------------|

| FRM_STR  | set one when one complete frame is stored           |

| STR_LST  | set at the start of the last frame                  |

| FE_2352  | set if the front-end data exceeds 2352 bytes        |

| FE_HDR   | front-end interrupt for header (or Q channel) ready |

| ECC_COR  | ECC interrupt for correction complete               |

| RFERXINT | front-end interrupt for receive ready               |

| FETXINT  | front-end interrupt for transmit ready              |

#### 8.4 Microcontroller RAM organization

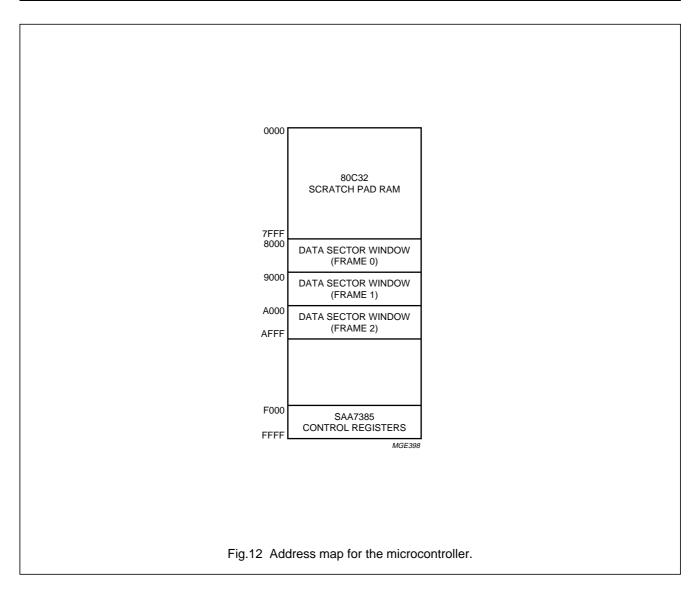

MICFRM# is used to determine the frame address for the microcontroller access through the frame window 0x8000 to 0x8FFF. To obtain the actual byte location within the buffer RAM, the lower 12 bits of the microcontroller address form the relative offset and hence the absolute address is found.

Note that the microcontroller has the option of addressing memory in a linear fashion using the 32 kbyte address space between 0x000 and 0x7FFF. If this 32 kbyte page is used, the PAGEREG must be programmed with the required page address. PAGEREG is used to select the required page when the microcontroller makes a linear access to the buffer memory using the address space 0x7000 to 0x7FFF. The actual address is the fifteen LSBs from the microcontroller plus 32768 times the value in PAGEREG.

Table 11 Microcontroller frame number address registers: 0xF0F6 and 0xF0F7

| MNEMONIC | R/W |      |      |      | DATA | BYTE |      |      |      |

|----------|-----|------|------|------|------|------|------|------|------|

|          |     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| MICFRM#  | R/W | NUM7 | NUM6 | NUM5 | NUM4 | NUM3 | NUM2 | NUM1 | NUM0 |

| MICFRM#  | R/W | 1    | _    | _    | _    | _    | -    | _    | NUM8 |

Registers 0xF0F6 and 0xF0F7 provide the frame number address for the microcontroller access to memory. The counter associated with these registers is loaded after the most significant byte is written; the least significant byte must be written first to ensure that the counter is loaded correctly. If a DRAM access is in progress that uses the address from the counter, the update will be delayed until the access is complete.

### Error correction and host interface IC for CD-ROM (SEQUOIA)

**SAA7385**

Table 12 Microcontroller address page register: 0xF0FF

| MNEMONIC  | R/W   |   |   |                        | DATA B | YTE   |       |       |       |

|-----------|-------|---|---|------------------------|--------|-------|-------|-------|-------|

| MINEMONIC | IN/VV | 7 | 6 | 5                      | 4      | 3     | 2     | 1     | 0     |

| PAGEREG   | R/W   | _ | _ | PAGE_EN <sup>(1)</sup> | MA_19  | MA_18 | MA_17 | MA_16 | MA_15 |

#### Note

1. PAGE\_EN is disconnected.

Register 0xF0FF is used by the buffer manager for the upper address lines when the microcontroller addresses non-frame memory. These registers overlap frame memory, so register 0xF0FF must be programmed with an address in the top part of the memory if no overlap is required. The microcontroller page address line is selected from this register. The outputs are used directly to control DRAM access cycles, and will affect any current DRAM cycle in progress.

It is possible to access three contiguous frames from the microcontroller by reading the three data sector windows, 0x8000 to 0x8FFF, 0x9000 to 0x9FFF and 0xA000 to 0xAFFF. This function is required for the decoding of the sub-code information. If the 'next' frame wraps past the last frame pointer (LASTFRM) then the pointers are modified to wrap back to the start pointer onwards (FEFRM#); this section is transparent to the microcontroller.

Table 13 Program memory control register: 0xF09F

| MNEMONIC | R/W |         |        |         | DATA I  | ВҮТЕ |   |   |   |

|----------|-----|---------|--------|---------|---------|------|---|---|---|

|          | K/W | 7       | 6      | 5       | 4       | 3    | 2 | 1 | 0 |

| PRGMEM   | R/W | DATAPRG | EN_WIN | SEL_TOP | INV_A15 | 1    | _ | _ | _ |

Register 0xF09F controls a system test feature where an SRAM is used for the 80C32 external program memory; note DATAPRG must be set for any of these features to be enabled.

Table 14 PRGMEM field descriptions

| FIELD   | LOGIC | DESCRIPTION                                                                        |

|---------|-------|------------------------------------------------------------------------------------|

| INV_A15 | 0     | normal operation                                                                   |

|         | 1     | invert A(15) to program memory for data memory access                              |

| SEL_TOP | 0     | select bottom 32 kbyte window                                                      |

|         | 1     | select top 32 kbyte window                                                         |

| EN_WIN  | 0     | windowing disabled                                                                 |

|         | 1     | 32 kbyte windows are enabled and SEL_TOP is used to determine window selected      |

| DATAPRG | 0     | normal operation                                                                   |

|         | 1     | data memory is mapped to program memory and data memory DRAM accesses are disabled |

# Error correction and host interface IC for CD-ROM (SEQUOIA)

**SAA7385**

Table 15 SAA7385 address map details for the 80C32

| ADDRESS      | FUNCTION                                                                                                                                                                                                                                                                               |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0000 to 7FFF | This 32 kbyte window is used to address and portion the DRAM buffer. It is intended for non-frame mapped memory to be addressed through this window. The upper page address bits (to address the full range of the DRAM buffer) are set by the linear address page register (PAGEREG). |

| 8000 to 8FFF | All accesses to frame memory use this window to read or write to the buffer memory. The actual address to the DRAM buffer is Micro Frame Number (MICFRM#) times 3 k plus the 12 LSBs from the 80C32.                                                                                   |

| 9000 to 9FFF | This frame window is identical to the frame 0 window with the exception that one is added to the value from the Micro Frame Number (MICFRM#).                                                                                                                                          |

| A000-AFFF    | This frame window is identical to the frame 0 window with the exception that two is added to the value from the Micro Frame Number (MICFRM#).                                                                                                                                          |

| B000-EFFF    | Not used; outputs are driven LOW                                                                                                                                                                                                                                                       |

| F000-FFFF    | SAA7385 control registers                                                                                                                                                                                                                                                              |

### Error correction and host interface IC for CD-ROM (SEQUOIA)

**SAA7385**

#### 9 FRONT PANEL AND MISCELLANEOUS CONTROL SIGNALS

This chapter describes the various SAA7385 control signals; front panel and basic engine signals, jumper settings and use of the general purpose signals.

Table 16 Start clock doubler: 0xF091

| MNEMONIC | R/W  |   |   |   | DATA | BYTE |   |   |   |

|----------|------|---|---|---|------|------|---|---|---|

|          | r./w | 7 | 6 | 5 | 4    | 3    | 2 | 1 | 0 |

| CLKSEL   | W    | - | - | _ | _    | -    | _ | _ | _ |

A write of any value to this address will engage the clock doubler. The state of the doubler may be obtained by reading C\_34\_16 in BRGSEL (see Table 30). If this bit is set then the clock doubler is engaged. On power-on, the clock doubler is disabled. Once the clock doubler is engaged, it can only be reset by one of the reset sources; a power-on reset, a SCSI reset or a reset from the watch-dog timer. The clock doubler must not be engaged when a 33.8688 MHz clock is connected to OSCIN (pin 117).

Table 17 Frequency synthesizer test register: 0xF0D8; note 1

| MNEMONIC | R/W    |   |   |        | DATA  | BYTE  |         |   |   |  |  |  |  |

|----------|--------|---|---|--------|-------|-------|---------|---|---|--|--|--|--|

|          | FC/ WV | 7 | 6 | 5      | 4     | 3     | 2       | 1 | 0 |  |  |  |  |

| FSTEST   | R/W    | _ | _ | USE_IN | CPSEL | FVCOD | FS_LOCK | _ | _ |  |  |  |  |

#### Note

Register 0xF0D8 is used for IC-level testing and to power down the frequency synthesizer. Only bit USE\_IN should be asserted in normal operation.

Table 18 FSTEST field description

| FIELD   | LOGIC | DESCRIPTION                                                        |  |  |  |  |

|---------|-------|--------------------------------------------------------------------|--|--|--|--|

| FS_LOCK | 0     | normal operation                                                   |  |  |  |  |

|         | 1     | 3-state LED and switch LQDATA to FS_LOCK                           |  |  |  |  |

| FVCOD   | 0     | normal operation                                                   |  |  |  |  |

|         | 1     | test mode for FVCOD from the synthesizer                           |  |  |  |  |

| CPSEL   | 0     | normal operation                                                   |  |  |  |  |

|         | 1     | test mode for CPSEL from the synthesizer                           |  |  |  |  |

| USE_IN  | 0     | use internal synthesizer                                           |  |  |  |  |

|         | 1     | power down the synthesizer and operate off a 33.87 MHz input clock |  |  |  |  |

Table 19 Disconnected pulse-width modulator control: 0xF0B3; note 1

| MNEMONIC | R/W |   |   |   | DATA | BYTE |   |   |   |  |  |  |  |

|----------|-----|---|---|---|------|------|---|---|---|--|--|--|--|

|          | R/W | 7 | 6 | 5 | 4    | 3    | 2 | 1 | 0 |  |  |  |  |

| WTPWM    | R/W | _ | _ | _ | _    | _    | _ | _ | _ |  |  |  |  |

#### Note

Register 0xF0B3 is disconnected.

# Error correction and host interface IC for CD-ROM (SEQUOIA)

**SAA7385**

Table 20 General logic control register: 0xF0B9; note 1

| MNEMONIC   | DΛM | DATA BYTE |   |        |     |         |         |          |          |

|------------|-----|-----------|---|--------|-----|---------|---------|----------|----------|

| WINEWIONIC | R/W | 7         | 6 | 5      | 4   | 3       | 2       | 1        | 0        |

| WTGCTL     | W   | _         | _ | PWMSEL | LED | LA_MUTE | RA_MUTE | CHANNEL1 | CHANNEL0 |

#### Note

1. Register 0xF0B9 controls the audio mixing and the LED.

Table 21 WTGCTL field description

| FIELD    | LOGIC | DESCRIPTION                                     |

|----------|-------|-------------------------------------------------|

| CHANNELS | 00    | mute                                            |

|          | 01    | right data sent to both channels                |

|          | 10    | left data sent to both channels                 |

|          | 11    | stereo                                          |

| RA_MUTE  | _     | right channel digital mute                      |

| LA_MUTE  | -     | left channel digital mute                       |

| LED      | _     | active LOW control for the light emitting diode |

| PWMSEL   | _     | PWM is disconnected                             |

Table 22 Drive switches register: 0xF0BA; note 1

| MNEMONIC | R/W    |   |   |   | DATA | A BYTE  |          |       |        |  |  |  |  |

|----------|--------|---|---|---|------|---------|----------|-------|--------|--|--|--|--|

|          | IX/ VV | 7 | 6 | 5 | 4    | 3       | 2        | 1     | 0      |  |  |  |  |

| RDSW     | R      | _ | _ | _ | PLAY | SKIPFWD | SKIPBACK | EJECT | TRAYSW |  |  |  |  |

#### Note

1. Register 0xF0BA is used for sensing the drive switches.

Table 23 RDSW field description

| FIELD    | LOGIC | DESCRIPTION                                            |

|----------|-------|--------------------------------------------------------|

| TRAYSW   | 0     | tray position in                                       |

|          | 1     | tray position out                                      |

| EJECT    | _     | user is requesting the drive tray to open (active LOW) |

| SKIPBACK | _     | user is requesting a track skip backwards (active LOW) |

| SKIPFWD  | _     | user is requesting a track skip forwards (active LOW)  |

| PLAY     | _     | user is requesting the drive to play (active LOW)      |

Table 24 Jumper status register: 0xF0C9; note 1

| MNEMONIC | R/W |   |   |   | DATA       | BYTE    |   |   |   |  |  |  |  |  |

|----------|-----|---|---|---|------------|---------|---|---|---|--|--|--|--|--|

|          |     | 7 | 6 | 5 | 4          | 3       | 2 | 1 | 0 |  |  |  |  |  |

| RDJMPRS  | R   |   |   |   | JUMPER7 to | JUMPER0 |   |   |   |  |  |  |  |  |

#### Note

1. The bit fields for the jumpers are explained in Table 25.

# Error correction and host interface IC for CD-ROM (SEQUOIA)

**SAA7385**

#### Table 25 RDJMPRS field description

| FIELD              | DESCRIPTION                                                                                                                                                                         |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JUMPER7 to JUMPER0 | Indicates the value of the DRAM data bus on power-up. The data bus may be pulled HIGH or LOW using weak pull-ups and pull-downs hence up to eight jumper settings are accommodated. |

#### Table 26 General purpose bits: 0xF0C2; note 1

| MNEMONIC | R/W   |        |        |        | DATA   | BYTE   |        |            |        |

|----------|-------|--------|--------|--------|--------|--------|--------|------------|--------|

|          | IK/VV | 7      | 6      | 5      | 4      | 3      | 2      | 1 GPDAT1 G | 0      |

| GPIOCTL  | R/W   | GPDAT4 | GPDIR4 | GPDAT3 | GPDIR3 | GPDAT2 | GPDIR2 | GPDAT1     | GPDIR1 |

#### Note

Register 0xF0C2 controls the direction and output state of the general purpose I/O bits on the SAA7385. Reading

the GPIO direction bits reflects the last value that was written to the register. The four GPIO data bits shows the

current value of the input signals in the input mode. In the output mode, the last value written to the output latches is

that which is read back.

#### Table 27 GPIOCTL field description

| FIELD  | DESCRIPTION                                                                                                                     |

|--------|---------------------------------------------------------------------------------------------------------------------------------|

| GPDIR1 | General purpose bit direction control. Default LOW puts GPIO1 into the input mode, setting this HIGH puts GPIO1 in output mode. |

| GPDAT1 | GPIO1 data bit.                                                                                                                 |

| GPDIR2 | General purpose bit direction control. Default LOW puts GPIO2 into the input mode, setting this HIGH puts GPIO2 in output mode. |

| GPDAT2 | GPIO2 data bit.                                                                                                                 |

| GPDIR3 | General purpose bit direction control. Default LOW puts GPIO3 into the input mode, setting this HIGH puts GPIO3 in output mode. |

| GPDAT3 | GPIO3 data bit.                                                                                                                 |

| GPDIR4 | General purpose bit direction control. Default LOW puts GPIO4 into the input mode, setting this HIGH puts GPIO4 in output mode. |

| GPDAT4 | GPIO4 data bit.                                                                                                                 |

### Error correction and host interface IC for CD-ROM (SEQUOIA)

**SAA7385**

#### 9.1 S2B UART registers

This section describes the registers used for the S2B UART control.

Table 28 S2B UART transmit, receive and status buffer: 0xF0A1, F0A2 and F0A3

| MNEMONIC             | R/W    |       |       |       | DATA  | BYTE   |       |             |        |

|----------------------|--------|-------|-------|-------|-------|--------|-------|-------------|--------|

|                      | IX/ VV | 7     | 6     | 5     | 4     | 3      | 2     | DATA1 DATA0 | 0      |

| WTS2B <sup>(1)</sup> | W      | DATA7 | DATA6 | DATA5 | DATA4 | DATA3  | DATA2 | DATA1       | DATA0  |

| RDS2B                | R      | DATA7 | DATA6 | DATA5 | DATA4 | DATA3  | DATA2 | DATA1       | DATA0  |

| S2BSTAT              | R      | _     | _     | SPR   | CPR   | TXDRDY | PE    | OVRRUN      | RXDRDY |

#### Note

1. WTS2B is for the transmit data byte from the S2B UART and RDS2B is for the receive data byte from the S2B UART.

Table 29 S2BSTAT field description

| FIELD  | DESCRIPTION                                                                                                                                                                                                                                                                                          |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXDRDY | A logic 1 indicates that the receive data is valid.                                                                                                                                                                                                                                                  |

| OVRRUN | A logic 1 indicates that the data in the receive buffer was not read before it was over written by the next byte.                                                                                                                                                                                    |

| PE     | A logic 1 indicates that a parity error was detected in the receive data byte; this is usually caused by the wrong baud rate.                                                                                                                                                                        |

| TXDRDY | A logic 1 indicates that the transmit data buffer is empty and ready for another byte.                                                                                                                                                                                                               |

| CPR    | S2B handshake bit which may be interpreted as 'clear to send'; this is generated automatically by the UART. It is asserted whenever the UART receiver is ready for a byte and negated as soon as the stop bit is shifted in. It is again asserted as soon as the received byte is read by the 80C32. |

| SPR    | S2B handshake bit which may be interpreted as 'request to send'; this is received from the CD-ROM engine UART transmitter and will generate an interrupt to the 80C32 if the TXRDY bit is set and the interrupt is not masked.                                                                       |

Table 30 Baud rate generator control: 0xF0C0; note 1

| MNEMONIC  | R/W  |         |      |         | DATA    | ВҮТЕ |   |         |         |

|-----------|------|---------|------|---------|---------|------|---|---------|---------|

| MINEMONIC | K/VV | 7       | 6    | 5       | 4       | 3    | 2 | 1       | 0       |

| BRGSEL    | R/W  | C_34_16 | LOCK | EVENPAR | INVSUBC | INVQ | - | ICESEL1 | ICESEL0 |

#### Note

1. Register 0xF0C0 controls the S2B UART baud rate and selective inversion of the sub-code information. Control over the parity and the clock doubler is also included together with the ability to invert the sub-code and Q-channel information.

# Error correction and host interface IC for CD-ROM (SEQUOIA)

**SAA7385**

Table 31 BRGSEL field description

| FIELD        | LOGIC | DESCRIPTION                                                                                               |

|--------------|-------|-----------------------------------------------------------------------------------------------------------|

| ICESEL1 to 0 | 00    | 31.25 kbaud transfer rate                                                                                 |

|              | 01    | 62.5 kbaud transfer rate                                                                                  |

|              | 10    | 187.5 kbaud transfer rate                                                                                 |

|              | 11    | not specified                                                                                             |

| INVQ         | _     | inverts all Q-channel information if set                                                                  |

| INVSUBC      | _     | inverts all sub-code information if set                                                                   |

| EVENPAR      | _     | selects even parity for S2B UART is set                                                                   |

| LOCK         | _     | read only information; indicates clock synthesizer is stable (after reset) and it is ready to set C_34_16 |

| C_34_16      | _     | once LOCK is HIGH, asserting this bit engages the clock doubler                                           |

Table 32 UART special control register: 0xF09E; note 1

| MNEMONIC    | R/W | DATA BYTE |         |         |         |         |         |         |         |

|-------------|-----|-----------|---------|---------|---------|---------|---------|---------|---------|

| WINEWICINIC |     | 7         | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

| UARTCTL     | R/W | EXTUART   | UARTCNT | DIVIDE5 | DIVIDE4 | DIVIDE3 | DIVIDE2 | DIVIDE1 | DIVIDE0 |

#### Note

1. Register 0xF09E allows the 80C32 UART clock to be derived from 16.945 MHz. This external UART clock is required for reliable operation of the UART if the 80C32 is used for other functions during the transfer.

Table 33 UARTCTL field description

| FIELD        | LOGIC | DESCRIPTION                                                                                                                                                                                |

|--------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIVIDE5 to 0 | -     | value 0 produces a 0.264 MHz clock and 58 produces a 2.82 MHz clock for the UART; this is the maximum accepted by the 80C32, a smaller number is required for guaranteed operation e.g. 15 |

| UARTCNT      | 0     | normal UART data input sampled by the external clock                                                                                                                                       |

|              | 1     | select a UART data input sampled by the clock from the internal counter                                                                                                                    |

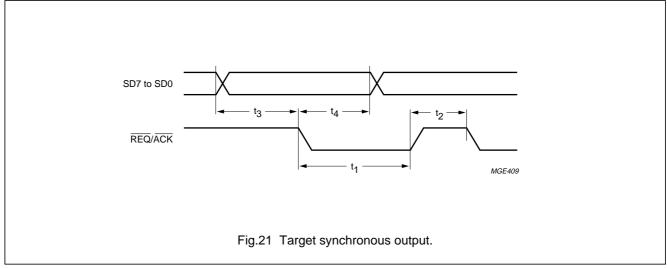

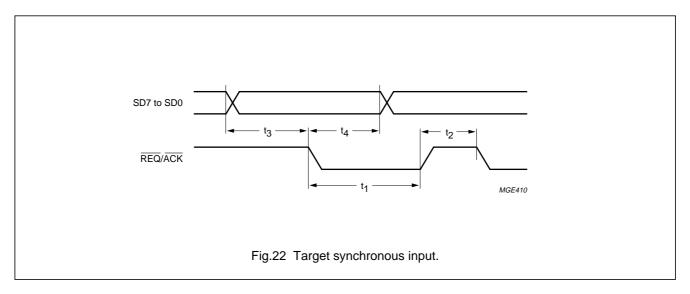

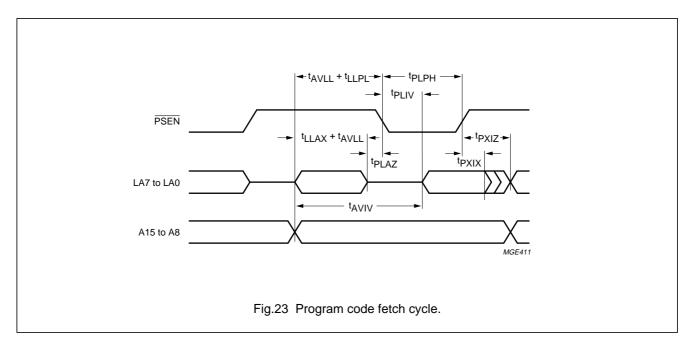

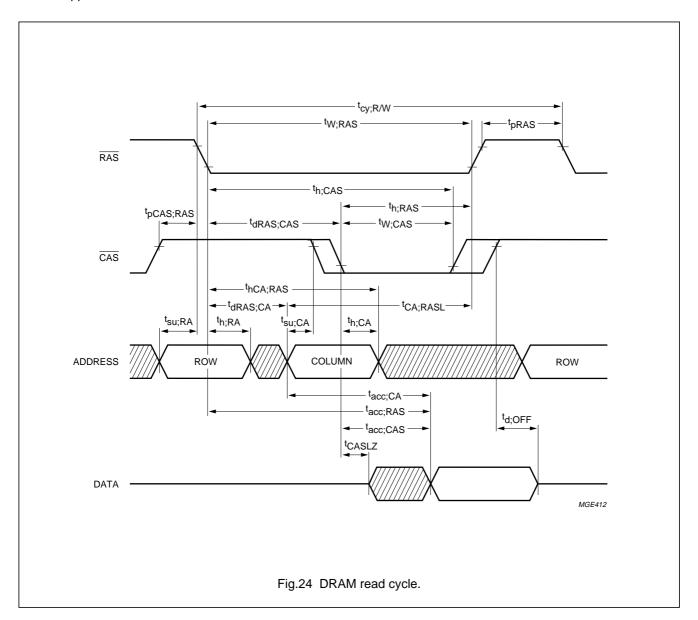

| EXTUART      | 0     | use external UART clock; disables internal clock                                                                                                                                           |