# INTEGRATED CIRCUITS

# DATA SHEET

# SAA7158 Back END IC

Preliminary specification

File under Integrated Circuits, IC02

July 1994

Back END IC SAA7158

#### **FEATURES**

- · Line Flicker Reduction (LFR) by means of MEDIAN filtering

- Vertical zoom

- · Digital colour transient improvement

- · Digital luminance peaking

- · Movie phase detection

- 4:4:4 YUV data throughput selectable, standard is 4:1:1 Y/U/V

- D/A conversion

- · UART interface.

#### **GENERAL DESCRIPTION**

#### **Application Environment**

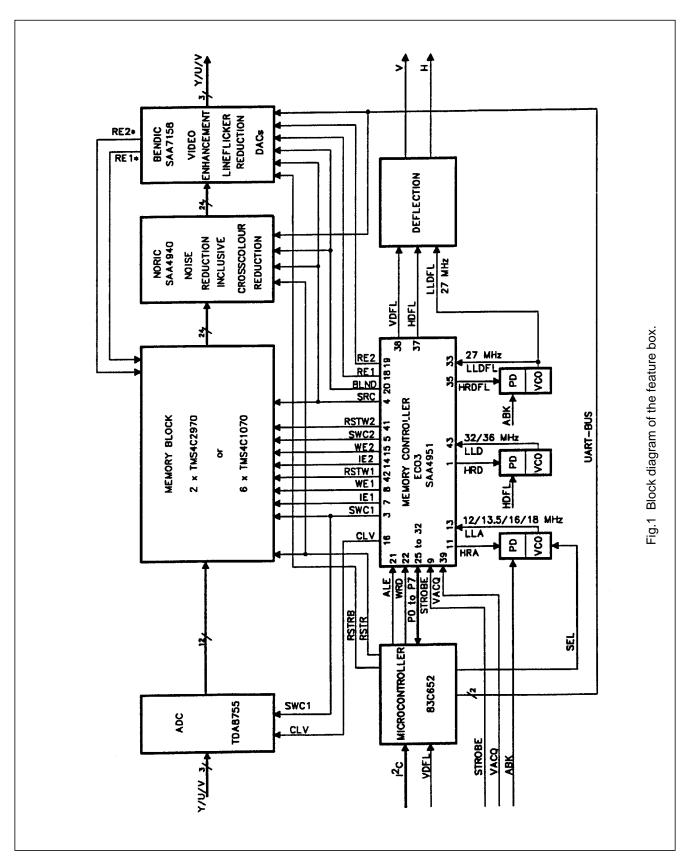

The Back END IC (abbreviated as BENDIC) is designed to cooperate with an 8051 type of microprocessor, the ECO3 (SAA4951) memory controller and Texas Instruments TMS4C2970 memories, but other configurations may be applicable. Fig.1 shows the block diagram of the feature box. The nominal clock frequency of the IC is 27 MHz or 32 MHz, with a maximum of 36 MHz.

The system supports the digital Y/U/V bus for selection of different video signal sources. The Y/U/V bus and the BENDIC data input are fully synchronous with respect to the clock signal. A line reference signal BLN for timing control purposes has to be provided by external elements which always controls the system timing, independent of active signal sources or desired functions.

#### **Analog Characteristics**

The BENDIC contains 3 independent, high speed digital to analog converters for luminance and colour difference signal processing and conversion. The resolution of the two DA converters for the colour difference signals is 8 bit. The luminance peaking up to 6 dB at high frequencies widens the resolution of the luminance channel. To avoid aliasing effects due to time discrete amplitude limiting the resolution of 9-bit is offered for the luminance conversion. All output stages provide high performance output stages for driving lines with low impedance line termination.

#### QUICK REFERENCE DATA

| SYMBOL           | PARAMETER                     | MIN. | MAX. | UNIT |

|------------------|-------------------------------|------|------|------|

| $V_{DD}$         | digital supply voltage        | 4.5  | 5.5  | ٧    |

|                  | analog supply voltage         | 4.75 | 5.25 | ٧    |

| T <sub>amb</sub> | operating ambient temperature | 0    | +70  | °C   |

#### ORDERING INFORMATION

| EXTENDED    |      |              | PACKAGE  |                       |

|-------------|------|--------------|----------|-----------------------|

| TYPE NUMBER | PINS | PIN POSITION | MATERIAL | CODE                  |

| SAA7158WP   | 68   | PLCC         | plastic  | SOT188 <sup>(1)</sup> |

#### Note

1. SOT188-2; 1996 November 26.

Back END IC SAA7158

Back END IC SAA7158

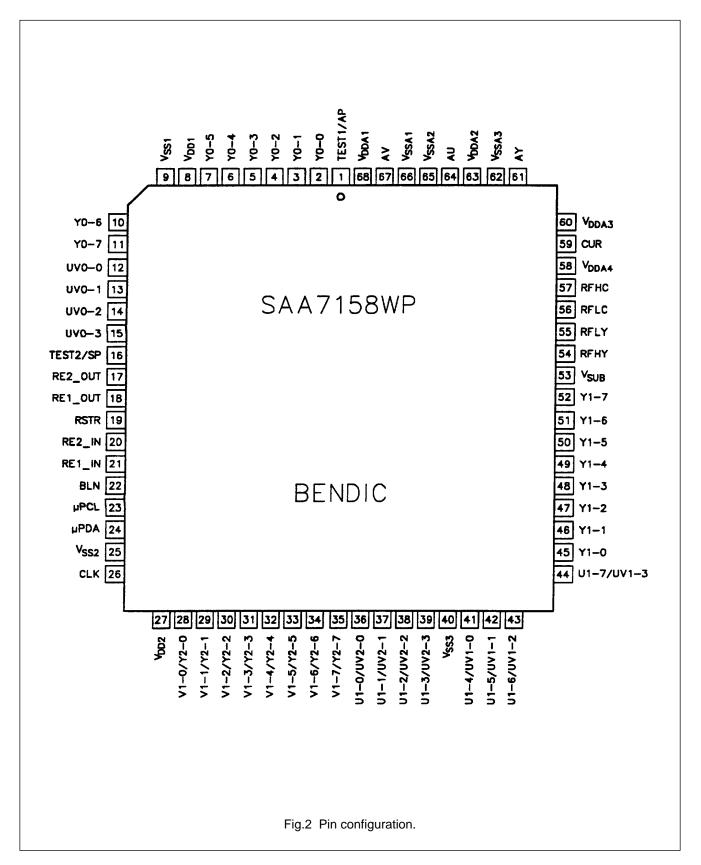

# **PINNING**

| SYMBOL           | PIN | TYPE           | DESCRIPTION                                                |  |

|------------------|-----|----------------|------------------------------------------------------------|--|

| TEST1/AP         | 1   | input          | action pin for testing; to be connected to V <sub>SS</sub> |  |

| Y0-0             | 2   | 3-state output | feedback_data to second memory, Y bit 0                    |  |

| Y0-1             | 3   | 3-state output | feedback_data to second memory, Y bit 1                    |  |

| Y0-2             | 4   | 3-state output | feedback_data to second memory, Y bit 2                    |  |

| Y0-3             | 5   | 3-state output | feedback_data to second memory, Y bit 3                    |  |

| Y0-4             | 6   | 3-state output | feedback_data to second memory, Y bit 4                    |  |

| Y0-5             | 7   | 3-state output | feedback_data to second memory, Y bit 5                    |  |

| V <sub>DD1</sub> | 8   | supply         | positive digital supply voltage (+5 V)                     |  |

| V <sub>SS1</sub> | 9   | ground         | digital ground                                             |  |

| Y0-6             | 10  | 3-state output | feedback_data to second memory, Y bit 6                    |  |

| Y0-7             | 11  | 3-state output | feedback_data to second memory, Y bit 7                    |  |

| UV0-0            | 12  | 3-state output | feedback_data to second memory, UV bit 0                   |  |

| UV0-1            | 13  | 3-state output | feedback_data to second memory, UV bit 1                   |  |

| UV0-2            | 14  | 3-state output | feedback_data to second memory, UV bit 2                   |  |

| UV0-3            | 15  | 3-state output | feedback_data to second memory, UV bit 3                   |  |

| TEST2/SP         | 16  | input          | shift pin for testing; to be connected to V <sub>SS</sub>  |  |

| RE2_OUT          | 17  | output         | redirected read enable to memory 2                         |  |

| RE1_OUT          | 18  | output         | redirected read enable to memory 1                         |  |

| RSTR             | 19  | input          | memory read, μP interface and movie detection reset        |  |

| RE2_IN           | 20  | input          | input for read enable to memory 2                          |  |

| RE1_IN           | 21  | input          | input for read enable to memory 1                          |  |

| BLN              | 22  | input          | blanking signal                                            |  |

| μPCL             | 23  | input          | clock for interface with 8051 UART, mode 0                 |  |

| μPDA             | 24  | in/output      | data for interface with 8051 UART, mode 0                  |  |

| V <sub>SS2</sub> | 25  | ground         | digital ground                                             |  |

| CLK              | 26  | input          | master clock, nominal 27 (32) MHz                          |  |

| V <sub>DD2</sub> | 27  | supply         | positive digital supply voltage (+5 V)                     |  |

| V1-0/Y2-0        | 28  | input          | V data, bit 0 in 4:4:4; Y data second memory, bit 0        |  |

| V1-1/Y2-1        | 29  | input          | V data, bit 1 in 4:4:4; Y data second memory, bit 1        |  |

| V1-2/Y2-2        | 30  | input          | V data, bit 2 in 4:4:4; Y data second memory, bit 2        |  |

| V1-3/Y2-3        | 31  | input          | V data, bit 3 in 4:4:4; Y data second memory, bit 3        |  |

| V1-4/Y2-4        | 32  | input          | V data, bit 4 in 4:4:4; Y data second memory, bit 4        |  |

| V1-5/Y2-5        | 33  | input          | V data, bit 5 in 4:4:4; Y data second memory, bit 5        |  |

| V1-6/Y2-6        | 34  | input          | V data, bit 6 in 4:4:4; Y data second memory, bit 6        |  |

| V1-7/Y2-7        | 35  | input          | V data, bit 7 in 4:4:4; Y data second memory, bit 7        |  |

| U1-0/UV2-0       | 36  | input          | U data, bit 0 in 4:4:4; UV data second memory, bit 0       |  |

| U1-1/UV2-1       | 37  | input          | U data, bit 1 in 4:4:4; UV data second memory, bit 1       |  |

| U1-2/UV2-2       | 38  | input          | U data, bit 2 in 4:4:4; UV data second memory, bit 2       |  |

| U1-3/UV2-3       | 39  | input          | U data, bit 3 in 4:4:4; UV data second memory, bit 3       |  |

| V <sub>SS3</sub> | 40  | ground         | digital ground                                             |  |

Back END IC SAA7158

| SYMBOL            | PIN | TYPE          | DESCRIPTION                                                                                                          |  |

|-------------------|-----|---------------|----------------------------------------------------------------------------------------------------------------------|--|

| U1-4/UV1-0        | 41  | input         | U data, bit 4 in 4:4:4; UV data first memory, bit 0                                                                  |  |

| U1-5/UV1-1        | 42  | input         | U data, bit 5 in 4:4:4; UV data first memory, bit 1                                                                  |  |

| U1-6/UV1-2        | 43  | input         | U data, bit 6 in 4:4:4; UV data first memory, bit 2                                                                  |  |

| U1-7/UV1-3        | 44  | input         | U data, bit 7 in 4:4:4; UV data first memory, bit 3                                                                  |  |

| Y1-0              | 45  | input         | Y data first memory, bit 0                                                                                           |  |

| Y1-1              | 46  | input         | Y data first memory, bit 1                                                                                           |  |

| Y1-2              | 47  | input         | Y data first memory, bit 2                                                                                           |  |

| Y1-3              | 48  | input         | Y data first memory, bit 3                                                                                           |  |

| Y1-4              | 49  | input         | Y data first memory, bit 4                                                                                           |  |

| Y1-5              | 50  | input         | Y data first memory, bit 5                                                                                           |  |

| Y1-6              | 51  | input         | Y data first memory, bit 6                                                                                           |  |

| Y1-7              | 52  | input         | Y data first memory, bit 7                                                                                           |  |

| V <sub>SUB</sub>  | 53  | analog ground | substrate pin; connect to analog ground (V <sub>SSA</sub> )                                                          |  |

| RFHY              | 54  | analog input  | connect C = 100 nF to analog ground (V <sub>SSA</sub> )                                                              |  |

| RFLY              | 55  | analog input  | connect to analog ground (V <sub>SSA</sub> )                                                                         |  |

| RFLC              | 56  | analog input  | connect to analog ground (V <sub>SSA</sub> )                                                                         |  |

| RFHC              | 57  | analog input  | connect C = 100 nF to analog ground (V <sub>SSA</sub> )                                                              |  |

| $V_{DDA4}$        | 58  | analog supply | analog supply voltage for reference ladders of the three DA converters and for current sources of the output buffers |  |

| CUR               | 59  | analog input  | current input for analog output buffers (0.4 mA from $V_{DDA4}$ = 5 V); connect with R = 15 k $\Omega$               |  |

| $V_{\text{DDA3}}$ | 60  | analog supply | analog supply voltage for output buffer AY                                                                           |  |

| AY                | 61  | analog output | analog luminance Y output                                                                                            |  |

| V <sub>SSA3</sub> | 62  | analog ground | analog ground for output buffer AY                                                                                   |  |

| $V_{\text{DDA2}}$ | 63  | analog supply | analog supply voltage for output buffer AU                                                                           |  |

| AU                | 64  | analog output | analog (B-Y) or –(B-Y) output                                                                                        |  |

| V <sub>SSA2</sub> | 65  | analog ground | analog ground for output buffer AU                                                                                   |  |

| V <sub>SSA1</sub> | 66  | analog ground | analog ground for output buffer AV                                                                                   |  |

| AV                | 67  | analog output | analog (R-Y) or –(R-Y) output                                                                                        |  |

| V <sub>DDA1</sub> | 68  | supply        | analog supply voltage for output buffer AV                                                                           |  |

Back END IC SAA7158

Back END IC SAA7158

#### **FUNCTIONAL DESCRIPTION**

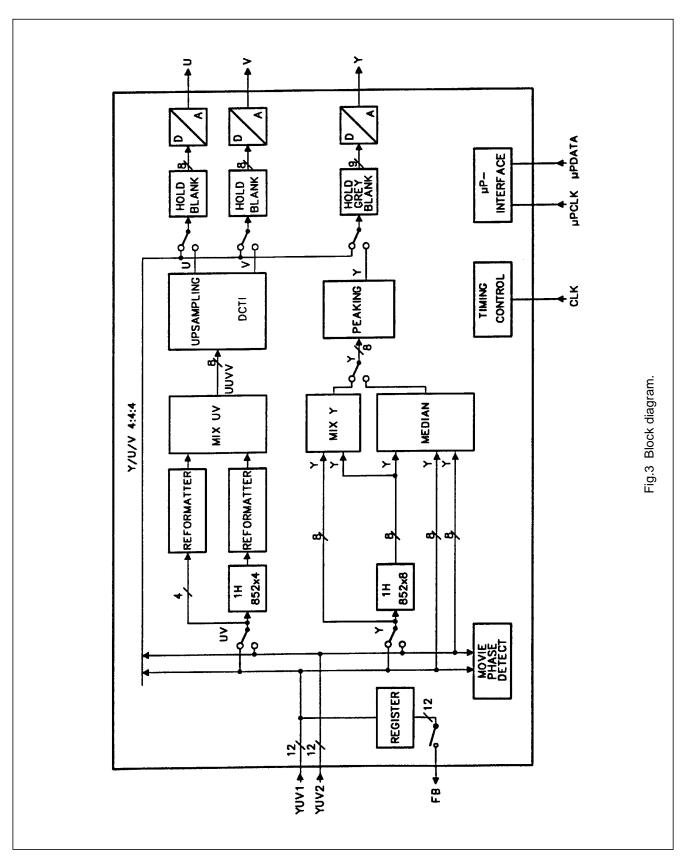

#### **Block Diagram**

The BENDIC will be produced in a CMOS double metal process. It is possible to feed the BENDIC with 8-bit wide luminance and chrominance signals Y/U/V in 4:1:1 mode from the digital Y/U/V bus and to run it in a bypass mode with Y/U/V in 4:4:4 mode without any bandwidth reduction.

The BENDIC contains the processing functions as depicted in Fig.3.

Following functions are available:

#### Datapath:

- 1H 4:1:1 line memory, 852 words by 8-bits luminance + 4-bits multiplexed chrominance

- REFORMATTER to get 8-bit wide UV from the Y/U/V bus format

- MIX UV and MIX Y to interpolate between actual and 1H-delayed input signals, programmable for realization of vertical zoom

- MEDIAN filter in luminance processing path for line flicker reduction

- MOVIE PHASE DETECT for supporting line flicker reduction control

- PEAKING for luminance channel

- UPSAMPLING and DCTI for chrominance transient improvement

- · HOLD/GREY/BLANK blocks for blanking and grey level insertion

- RE PROCESSING controls read enable for first and second memory, outputs are programmable for different applications

- Data switches for field select, mix/median select, 4:1:1/4:4:4 select

- DAC blocks for digital to analog conversion of Y, U, V video signals

- REGISTER with 3-state control for direct output of Y/U/V 1 input to memories.

# Control:

- $\bullet~\mu\text{P}$  INTERFACE for the control of BENDIC functions, including zoom control

- TIMING CONTROL and TEST as support blocks.

All video data signal processing inside the BENDIC is phaselinear and nonrecursive (except line delay in recirculation mode).

Back END IC SAA7158

Back END IC SAA7158

#### **Data Path Signal processing**

1H - 4:1:1 line memory, 852 words by 8-bits luminance + 4-bits multiplexed chrominance

The Y/U/V line memory is organized as 852 x 12 bits. It works as a shift register with recirculation mode if desired. The line start is synchronized to RE, and if there are more than 852 words to be stored it will stop and hold.

REFORMATTER to get 8-bit wide UV from the Y/U/V bus format

The reformatter changes the 4:1:1 format of UV signals into a sequential 8-bit U and V data stream with a sampling rate of half the master clock.

MIX UV and MIX Y to interpolate between actual and 1H-delayed input signals, programmable for realization of vertical zoom

The function of the MIX-blocks is to interpolate between two input sources A and B (original signal and 1H-delayed signal). Possible interpolation coefficients

are

$$\{1 \text{ or } \frac{3}{4} \text{ or } \frac{1}{2} \text{ or } \frac{1}{4} \text{ or } 0 \} \times (A-B) + B.$$

MEDIAN filter in luminance processing path for line flicker reduction

The median filter consists of two different median filters working in parallel with full clock rate. Filters for up and downsampling are implemented with an 8-bit output.

MOVIE PHASE DETECT for supporting line flicker reduction control

A pixel by pixel luminance level comparison is made on the active video of two consecutive fields from the memory. The absolute difference of the 4 most significant bits of each pixel from the two fields is added to the accumulated value of the current field in a register. The highest significant two bytes thereof are transferred during field blanking period with rising edge of RSTR signal into a register that can be read via the  $\mu P$  interface. After reading the register will be cleared.

PEAKING for luminance channel

The H-peaking of the luminance channel compensates the bandwidth reduction caused by various components of the TV signal processing chain. Because of the possibility to convert over and undershoots it is even possible to precompensate the si-amplitude attenuation of the D/A converter by 6 dB. The absolutely phaselinear filters can be programmed: frequency response, amplitude of the high frequency signals and degree of coring is controlled via the  $\mu P$  interface. Frequency responses c. f. separate application sheet.

UPSAMPLING and DCTI for chrominance transient improvement

After upsampling of U and V, in the DCTI block the U and V signals are processed with a  $\,$

look-backwards/look-forwards device. The chrominance signal values are stored in a 26 tap pixel delay line. Controlled by a multiplexer select signal K the values are read from the pixel delay line into the output registers of DCTI. The calculation of the K signal is done within this block. To determine the number of steps to look back and

forwards the following relation is used:  $\frac{d}{dt} \left( \left| \frac{dU}{dt} \right| + \left| \frac{dV}{dt} \right| \right)$

U and V are processed serially with the same circuitry. The final upsampling towards the master clock for D/A conversion is part of the algorithm and done by linear interpolation between two adjacent taps of choice. It is controlled by the K signal too.

HOLD/GREY/BLANK blocks for blanking and grey level insertion

The function of these blocks is to insert desired levels for Y, U and V, where no active video is present. BLANKing is performed during line and field blanking period indicated by BLN. GREY is performed where RE indicates that the memory is not read out, and pixel repetition is switched off by the  $\mu P$  interface; the grey value comes via the  $\mu P$  interface. HOLD is performed if pixel repetition is selected by the  $\mu P$  interface; the last value of Y, U and V is kept until RE is active again.

RE PROCESSING controls read enable for first and second memory

Here the output signals RE1 and RE2 are shifted by adding a programmable delay of 5, 6, 7 or 8 clock pulses with respect to the input signals. In addition RE1 will be influenced in case of zoom.

data switches for field select, mix/median select, 4:1:1/4:4:4 select

The switches shown in the block diagram Fig.3 are controlled via the  $\mu P$  interface and allow control of the data streams inside the BENDIC.

DAC blocks for digital to analog conversion of Y, U, V video signals

The D/A conversion is performed in the DAC blocks. The converters consist of the resistor strings to be connected externally and three buffers with a 25  $\Omega$  serial resistor at the output built in. To get 75  $\Omega$  impedance externally three 50  $\Omega$  resistors have to be used near the pins. The capacitive load at the outputs should not exceed 30 pF.

Back END IC SAA7158

REGISTER with 3-state control for direct output of Y/U/V 1 input to memories

The 3-state switch with internal register is supplied for the feedback data to the second memory. The feedback bus is a copy of the field 1 bus, but with 4 clockpulses delay. 3-state control is done via  $\mu P$  interface.

#### The control signals

#### CLK

Line locked clock of maximal 36 MHz.

This is the system clock. Within the BENDIC the CLK signal is distributed to the different blocks.

#### BLN

Blanking NOT signal.

This signal marks the horizontal and vertical blanking and defines with its rising edge the start phase of the UV 4:1:1 format. A programmable delay of 0, 1, 2 or 3 clock pulses shifts the internal pulse with respect to the input.

#### RE1\_in

Read enable memory 1 signal.

This signal is generated by the memory controller and its HIGH state determines the read enable on the first memory bank, after it is processed by BENDIC for the ZOOM mode and fine shift of the edges.

#### RE2 in

Read enable memory 2 signal.

This signal is generated by the memory controller and its HIGH state determines the read enable on the second memory bank, including a fine shift of the edges.

RE1\_in and RE2\_in are processed in the BENDIC to:

- external signals: RE1\_out and RE2\_out

- RE with correct internal delay to match datapath delays, is used to define the edges between video and side panels (grey insertion or pixel repetition).

#### **RSTR**

#### Reset signal

This signal is transferred (asynchronous with CLK) by e. g. a microprocessor to reset the communication between the microprocessor and the BENDIC. CLK has to be present in this case. In a typical application, RSTR is an active HIGH pulse, issued only in the vertical blanking period. During RSTR HIGH-state, the 'feedback\_data' lines are switched to 3-state, temporarily overruling the mode that has been set by the microprocessor. By this provision, RSTR can be used to prevent data collision on the 3-state databus, e. g. during a power on sequence. Also, this signal is used to transfer the 'movie phase detect' data to a register that can be read by the microprocessor.

#### μPCL

Microprocessor interface clock signal

This signal is transferred (asynchronous with CLK) by a microprocessor (8051, UART mode 0) as communication clock signal at 1 MHz.

#### μPDA

Microprocessor interface data signal

This signal is transferred or received (asynchronous with CLK) by a microprocessor (8051, UART mode 0) as communication data signal at 1 MBaud, related to  $\mu$ PCL. Data is valid the rising edge of  $\mu$ PCL.

#### The external control

The  $\mu P$  interface has the following functions:

- Receive settings from the  $\mu P$

- Transmit movie phase detect data to the μP

The interface is based on a two wire interface, one for clock, the other for bidirectional data form. It is compatible with the 8051 family UART mode 0 interface. The  $\mu P$  is the master of the communication, it generates the clock (nominal 12 MHz/12 = 1 MHz), only active when transfer is done.

The protocol for the communication is:

8 addressbits are sent by the  $\mu P$  (LSB first), if the address is a write address then 8 databits (LSB first) are sent by the  $\mu P$ , else (if the address is a read address) 8 databits are sent by BENDIC.

RSTR is used to reset the phase of the address/data transfer. The negative going edge of RSTR clears the address register. After reset the first transmitted bit is to be taken as the first (LSB) bit of an address.

For field1/field2 selection and for mix/median selection, 4 addresses are used to select each of the four combinations. A databyte is not obligatory after each of these four addresses, but a dummy databyte is needed if the transmission is to be followed by a further one.

Back END IC SAA7158

Table 1

Write address table.

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ADDRESS (HEX) | FUNCTION            | ВІТ             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------------|-----------------|

| bit4: UVbin     bit5: Yclip     bit6: 4:4:4     bit7: feedback     2   grey value setting     bit4: grey(0)     bit5: grey(1)     bit6: grey(2)     bit7: grey(3)     bit7: grey(3)     bit7: grey(3)     bit8: re1_d(0)     bit1: re1_d(1)     bit2: inv_re1     bit3: re2_d(0)     bit4: re2_d(1)     bit5: bln_d(0)     bit7: bln_d(1)     4   zoom setting     bit0: [ps     bit1: pixrep     bit2: black16     bit3: zoom(0)     bit4: zoom(1)     bit5: zoom(2)     bit6: zoom(3)     bit7: zoom(4)     bit6: gain(0)     bit6: gain(0) | 1             | dataformat setting  | bit2: invUV     |

| bit5: Yclip     bit6: 4:4:4     bit7: feedback     2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               |                     | bit3: UV8bit    |

| bit6: 4:4:4     bit7: feedback     2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               |                     | bit4: UVbin     |

| bit7: feedback                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |                     | bit5: Yclip     |

| 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |               |                     | bit6: 4:4:4     |

| bit5: grey(1) bit6: grey(2) bit7: grey(3)  3 read enable setting bit0: re1_d(0) bit1: re1_d(1) bit2: inv_re1 bit3: re2_d(0) bit4: re2_d(1) bit5: inv_re2 bit6: bln_d(0) bit 7: bln_d(1)  4 zoom setting bit0: lps bit1: pixrep bit2: black16 bit3: zoom(0) bit4: zoom(1) bit5: zoom(2) bit6: zoom(3) bit7: zoom(4)  5 CTI setting bit4: range(0) bit5: range(1) bit6: gain(0)                                                                                                                                                                 |               |                     | bit7: feedback  |

| bit6: grey(2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2             | grey value setting  | bit4: grey(0)   |

| bit7: grey(3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |               |                     | bit5: grey(1)   |

| bit0: re1_d(0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |                     | bit6: grey(2)   |

| bit1: re1_d(1) bit2: inv_re1 bit3: re2_d(0) bit4: re2_d(1) bit5: inv_re2 bit6: bln_d(0) bit 7: bln_d(1)  4 zoom setting bit0: lps bit1: pixrep bit2: black16 bit3: zoom(0) bit4: zoom(1) bit5: zoom(2) bit6: zoom(3) bit7: zoom(4)  5 CTI setting bit3: range(0) bit5: range(1) bit6: gain(0)                                                                                                                                                                                                                                                 |               |                     | bit7: grey(3)   |

| bit2: inv_re1     bit3: re2_d(0)     bit4: re2_d(1)     bit5: inv_re2     bit6: bln_d(0)     bit7: bln_d(1)     4   zoom setting     bit0: lps     bit1: pixrep     bit2: black16     bit3: zoom(0)     bit4: zoom(1)     bit5: zoom(2)     bit6: zoom(3)     bit7: zoom(4)     5   CTI setting     bit4: range(0)     bit5: range(1)     bit6: gain(0)                                                                                                                                                                                       | 3             | read enable setting | bit0: re1_d(0)  |

| bit3: re2_d(0) bit4: re2_d(1) bit5: inv_re2 bit6: bln_d(0) bit 7: bln_d(1)  4 zoom setting  bit0: lps bit1: pixrep bit2: black16 bit3: zoom(0) bit4: zoom(1) bit5: zoom(2) bit6: zoom(3) bit7: zoom(4)  5 CTI setting  bit3: range(0) bit5: range(1) bit6: gain(0)                                                                                                                                                                                                                                                                            |               |                     | bit1: re1_d(1)  |

| bit4: re2_d(1)     bit5: inv_re2     bit6: bln_d(0)     bit 7: bln_d(1)     4   zoom setting     bit0: lps     bit1: pixrep     bit2: black16     bit3: zoom(0)     bit4: zoom(1)     bit5: zoom(2)     bit6: zoom(3)     bit7: zoom(4)     5   CTI setting     bit4: range(0)     bit5: range(1)     bit6: gain(0)                                                                                                                                                                                                                           |               |                     | bit2: inv_re1   |

| bit5: inv_re2     bit6: bln_d(0)     bit 7: bln_d(1)     4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               |                     | bit3: re2_d(0)  |

| bit6: bln_d(0)     bit 7: bln_d(1)     4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               |                     | bit4: re2_d(1)  |

| bit 7: bln_d(1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               |                     | bit5: inv_re2   |

| 200m setting   bit0: lps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               |                     | bit6: bln_d(0)  |

| bit1: pixrep bit2: black16 bit3: zoom(0) bit4: zoom(1) bit5: zoom(2) bit6: zoom(3) bit7: zoom(4)  5 CTI setting bit4: range(0) bit5: range(1) bit6: gain(0)                                                                                                                                                                                                                                                                                                                                                                                   |               |                     | bit 7: bln_d(1) |

| bit2: black16 bit3: zoom(0) bit4: zoom(1) bit5: zoom(2) bit6: zoom(3) bit7: zoom(4)  5 CTI setting bit4: range(0) bit5: range(1) bit6: gain(0)                                                                                                                                                                                                                                                                                                                                                                                                | 4             | zoom setting        | bit0: lps       |

| bit3: zoom(0) bit4: zoom(1) bit5: zoom(2) bit6: zoom(3) bit7: zoom(4)  5 CTI setting bit4: range(0) bit5: range(1) bit6: gain(0)                                                                                                                                                                                                                                                                                                                                                                                                              |               |                     | bit1: pixrep    |

| bit4: zoom(1) bit5: zoom(2) bit6: zoom(3) bit7: zoom(4)  5 CTI setting bit4: range(0) bit5: range(1) bit6: gain(0)                                                                                                                                                                                                                                                                                                                                                                                                                            |               |                     | bit2: black16   |

| bit5: zoom(2) bit6: zoom(3) bit7: zoom(4)  5 CTI setting bit4: range(0) bit5: range(1) bit6: gain(0)                                                                                                                                                                                                                                                                                                                                                                                                                                          |               |                     | bit3: zoom(0)   |

| bit6: zoom(3) bit7: zoom(4)  5 CTI setting bit4: range(0) bit5: range(1) bit6: gain(0)                                                                                                                                                                                                                                                                                                                                                                                                                                                        |               |                     | bit4: zoom(1)   |

| bit7: zoom(4)  5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |               |                     | bit5: zoom(2)   |

| 5 CTI setting bit4: range(0) bit5: range(1) bit6: gain(0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |                     | bit6: zoom(3)   |

| bit5: range(1) bit6: gain(0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |               |                     | bit7: zoom(4)   |

| bit6: gain(0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5             | CTI setting         | bit4: range(0)  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               |                     | bit5: range(1)  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               |                     | bit6: gain(0)   |

| bit7: gain(1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |               |                     | bit7: gain(1)   |

| 6 peaking setting, bit0: av_w_med                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6             |                     | bit0: av_w_med  |

| average UV select bit1: WG(0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |               | average UV select   | bit1: WG(0)     |

| bit2: WG(1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               |                     | bit2: WG(1)     |

| bit3: BFB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |                     | bit3: BFB       |

| bit4: BP(0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               |                     | bit4: BP(0)     |

| bit5: BP(1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               |                     | bit5: BP(1)     |

| bit6: coring(0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               |                     | bit6: coring(0) |

| bit7: coring(1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               |                     | bit7: coring(1) |

Back END IC SAA7158

| ADDRESS (HEX) | FUNCTION            | BIT                                                               |

|---------------|---------------------|-------------------------------------------------------------------|

| 7C            | multiplexer setting | SET select field1 OFF; select median OFF (all databits are dummy) |

| 7D            | multiplexer setting | SET select field1 ON; select median OFF (all databits are dummy)  |

| 7E            | multiplexer setting | SET select field1 OFF; select median ON (all databits are dummy)  |

| 7F            | multiplexer setting | SET select field1 ON; select median ON (all databits are dummy)   |

# The function of the bits in the control datawords are explained below:

| feedback    | HI: feedback output is 3-state enabled = outputs active                                          |

|-------------|--------------------------------------------------------------------------------------------------|

| 4:4:4       | HI: YUV-4:4:4 mode selected instead of 4:1:1 mode                                                |

| Yclip       | HI: Y signal after peaking is clipped and converted to 9-bit range                               |

| UVbin       | HI: UV signals are taken from input as binary signals instead 2's complement                     |

| UV8bit      | HI: UV signals are taken from input as 8-bit values instead of 7-bit                             |

| invUV       | HI: UV signals are inverted before the DACs (outputs = $-U$ and $-V$ )                           |

| grey(3:0)   | determines highest 4 bits in shade of grey in side panels                                        |

| bln_d(1:0)  | shifts the internal BLN signal from 0 to 3 clock pulses with respect to input                    |

| re2_d(1:0)  | shifts 5 to 8 clock pulses the RE2 output signal versus input                                    |

| re1_d(1:0)  | shifts 5 to 8 clock pulses the RE1 output signal versus input, additionally influenced by zoom   |

| inv_re2     | HI: RE2 output is polarity reversed in relation to RE2 input                                     |

| inv_re1     | HI: RE1 output is polarity reversed in relation to RE1 input                                     |

| zoom(4:0)   | determines vertical zoom factor, which is (32/zoom(4:0)); zoom(4:0) = 0 is equivalent to no zoom |

| black16     | HI: the Y signal value during the blanking period is 16 instead of 0                             |

| pixrep      | HI: side panels have the same Y, U and V as on the edge of the last video information            |

| lps         | HI: functional test mode for line on line median on/off                                          |

| range(1:0)  | determines maximum in CTI range of looking back/looking forward                                  |

| gain(1:0)   | determines gain of CTI function                                                                  |

| coring(1:0) | determines coring level in Y peaking                                                             |

| av_w_med    | enable average UV while median in Y (UV := $1/2 \times direct + 1/2 \times delayed$ )            |

| BP(1:0)     | determines frequency response in Y peaking                                                       |

The BENDIC provides the correlation of two subsequent fields with its 'Movie phase detector' via the  $\mu P$  interface. The MSB or LSB values of this correlation factor is read from the BENDIC by sending an addressbyte and subsequently receiving a databyte from it, according to Table 2.

determines weighted addition in Y peaking with 1 or 1/2 or 1/4 or 0

HI: determines bypass for BF1 in Y peaking

July 1994 12

WG(1:0)

BFB

Back END IC SAA7158

Table 2 Read address table.

| ADDRESS<br>(HEX) | ВІТ           |

|------------------|---------------|

| 80               | bit0: corr(0) |

|                  | bit1: corr(1) |

|                  | bit2: corr(2) |

|                  | bit3: corr(3) |

|                  | bit4: corr(4) |

|                  | bit5: corr(5) |

|                  | bit6: corr(6) |

|                  | bit7: corr(7) |

| ADDRESS<br>(HEX) | ВІТ            |

|------------------|----------------|

| 81               | bit0: corr(8)  |

|                  | bit1: corr(9)  |

|                  | bit2: corr(10) |

|                  | bit3: corr(11) |

|                  | bit4: corr(12) |

|                  | bit5: corr(13) |

|                  | bit6: corr(14) |

|                  | bit7: corr(15) |

corr(15:0) is the measured Y correlation factor between two successive fields.

Back END IC SAA7158

# **CHARACTERISTICS**

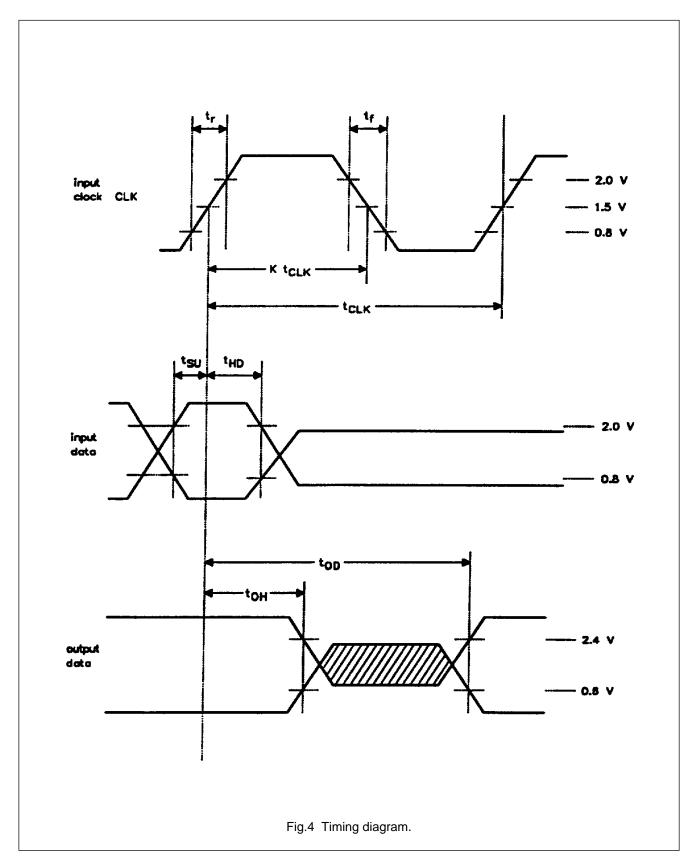

# Specification of input/output and clock levels and timing

The following table shows the specifications of input/output/clock levels and timing for  $T_{amb}$  = 0 to +70 °C;  $V_{DD}$  = 4.5 to 5.5 V;  $V_{DDA}$  = 4.75 to 5.25 V unless otherwise specified.

| SYMBOL              | PARAMETER                                              | CONDITIONS | MIN. | TYP. | MAX.                  | UNIT |

|---------------------|--------------------------------------------------------|------------|------|------|-----------------------|------|

| Supply              |                                                        |            | •    | •    |                       |      |

| V <sub>DD1-2</sub>  | digital supply voltages                                |            | 4.5  | _    | 5.5                   | V    |

| V <sub>DDA1-4</sub> | analog supply voltages                                 |            | 4.75 | _    | 5.25                  | V    |

| I <sub>DD1-2</sub>  | supply current digital                                 |            | _    | _    | 250                   | mA   |

| I <sub>DDA1-4</sub> | supply current analog                                  | note 1     | _    | _    | 18                    | mA   |

| Digital inpu        | ts                                                     |            |      | •    |                       |      |

| V <sub>IL</sub>     | LOW level input voltage                                |            | -0.5 | _    | +0.8                  | V    |

| V <sub>IH</sub>     | HIGH level input voltage                               |            | 2.0  | _    | V <sub>DD</sub> + 0.5 | V    |

| I <sub>LI</sub>     | input leakage current                                  |            | _    | -    | 10                    | μΑ   |

| C <sub>IC</sub>     | input capacitance (clocks)                             |            | _    | _    | 10                    | pF   |

| C <sub>ID</sub>     | input capacitance (data)                               |            | _    | _    | 10                    | pF   |

| C <sub>IZ</sub>     | input capacitance (I/O in high Z)                      |            | _    | _    | 10                    | pF   |

| Reference a         | and current inputs                                     | •          | •    | •    | •                     | •    |

| I <sub>CUR</sub>    | input current                                          |            | _    | _    | 0.4                   | mA   |

| Digital outp        | uts                                                    |            | •    |      |                       | •    |

| V <sub>OH</sub>     | HIGH level output voltage                              | note 2     | 2.4  | _    | V <sub>DD1-2</sub>    | V    |

| V <sub>OL</sub>     | LOW level output voltage                               | note 2     | 0    | _    | 0.6                   | V    |

| Timing              |                                                        |            |      |      |                       |      |

| t <sub>CLK</sub>    | CLK cycle time                                         |            | 27   | _    | 41                    | ns   |

| k <sub>CLK</sub>    | CLK duty cycle t <sub>CLK-HIGH</sub> /t <sub>CLK</sub> |            | 40   | _    | 60                    | %    |

| t <sub>r</sub>      | CLK rise time                                          |            | _    | _    | 5                     | ns   |

| t <sub>f</sub>      | CLK fall time                                          |            | _    | _    | 6                     | ns   |

| t <sub>SU</sub>     | input data setup time                                  |            | _    | _    | 5                     | ns   |

| $t_{HD}$            | input data hold time                                   |            | _    | _    | 6                     | ns   |

| t <sub>OH</sub>     | output data hold time                                  | note 2     | 6    | _    | _                     | ns   |

| t <sub>OD</sub>     | output data delay time                                 | note 2     | _    | _    | 25                    | ns   |

| Data output         | loads (3-state outputs)                                |            |      |      |                       |      |

| C <sub>ld</sub>     | output load capacitance                                |            | 10   | _    | 35                    | pF   |

| Characteris         | tics of the DA converters                              |            |      |      |                       |      |

| RSL <sub>Y</sub>    | resolution of the Y DAC                                |            | _    | 9    | _                     | bit  |

| RSL <sub>C</sub>    | resolution of the U and V DAC                          |            | _    | 8    | _                     | bit  |

| В                   | analog signal bandwidth (-3 dB)                        |            | 20   | _    | _                     | MHz  |

| CT                  | crosstalk between channels                             |            | _    | _    | -42                   | dB   |

Back END IC SAA7158

| SYMBOL           | PARAMETER                     | CONDITIONS          | MIN. | TYP.               | MAX. | UNIT |

|------------------|-------------------------------|---------------------|------|--------------------|------|------|

| DNL              | differential nonlinearity     | referred to 8 MSB's | _    | _                  | ±0.5 | LSB  |

| INL              | integral nonlinearity         | referred to 8 MSB's | _    | _                  | ±1   | LSB  |

| V <sub>out</sub> | output voltage (without load) |                     | _    | 2 V <sub>p-p</sub> | _    | V    |

#### **Notes**

- 1. f<sub>CLK</sub> = 36 MHz, f<sub>data</sub> = 18 MHz (rectangular full scale); without output load.

- 2. Timings and levels have to be measured with load circuits 1.2 k $\Omega$  connected to 3.0 V (TTL load), and C<sub>L</sub> = 25 pF.

#### APPLICATION NOTE FOR THE ANALOG PART OF BENDIC

The digital to analog conversion is done in parallel for the three channels. The DA converters (8-bit for U and V; 9-bit for Y) are based on resistor strings with low impedance output buffers. They are designed for 2  $V_{p-p}$  unloaded output swing. To avoid integral nonlinearity errors, the minimum output voltage is 200 mV; so the DC range for unloaded output is between 0.2 and 2.2 V.

A serial resistor of 25  $\Omega$  is integrated at the outputs of the buffers. With 50  $\Omega$  in series - close to the output pins - the nominal output voltage for 75  $\Omega$  line termination is 1  $V_{p-p}$  with a DC range of 0.1 to 1.1 V. Amplitude matching to external requirements has to be done with external dividers. Capacitance load should not exceed 30 pF.

The DAC's require three separate analog supply voltages  $V_{DDA1-3}$  and analog ground lines  $V_{SSA1-3}$  for the output buffers. The accuracy of an external voltage reference input  $V_{DDA4}$  directly influences the output amplitude of the video signals. The current input CUR supplies the output buffers with a current of about 0.3 mA at  $V_{DDA}$  = 5 V, if a resistor of 15 k $\Omega$  is connected to this pin.

A larger current improves the output bandwidth but makes the integral nonlinearity worse.

Back END IC SAA7158

Back END IC SAA7158

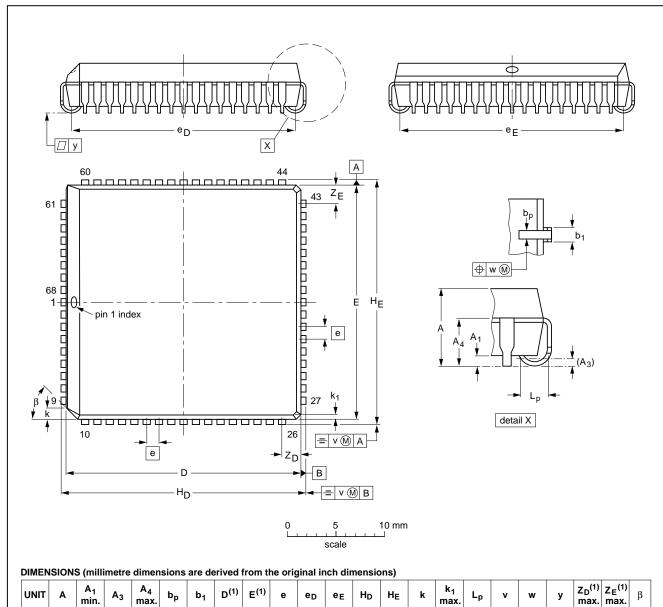

#### **PACKAGE OUTLINE**

# PLCC68: plastic leaded chip carrier; 68 leads

SOT188-2

#### Note

inches

4.57

4.19

0.180

0.165

0.51

0.020 0.01

0.25

3.30

0.13

1. Plastic or metal protrusions of 0.01 inches maximum per side are not included.

0.81

0.66

0.021 0.032 0.958 0.013 0.026 0.950

0.53

0.33

24.33

24.13

24.33

24.13

0.958

0.950

0.05

| OUTLINE  |        | REFER    | ENCES | EUROPEAN ISSUE DATE |                                 |  |

|----------|--------|----------|-------|---------------------|---------------------------------|--|

| VERSION  | IEC    | JEDEC    | EIAJ  | PROJECTION          | ISSUE DATE                      |  |

| SOT188-2 | 112E10 | MO-047AC |       |                     | <del>92-11-17</del><br>95-03-11 |  |

23.62 23.62

22.61

0.930 0.930 0.995

0.890 | 0.890 | 0.985

22.61

25.27

25.02

25.27

25.02

0.995 0.048

0.985 0.042

1.22 1.07

0.51

0.020

1.44

1.02

0.057

0.040

0.18

0.007 0.007

0.10

0.004 | 0.085 | 0.085

45°

Back END IC SAA7158

#### **SOLDERING**

#### Plastic leaded chip carriers

BY WAVE

During placement and before soldering, the component must be fixed with a droplet of adhesive. After curing the adhesive, the component can be soldered. The adhesive can be applied by screen printing, pin transfer or syringe dispensing.

Maximum permissible solder temperature is 260 °C and maximum duration of package immersion in solder bath is 10 s, if allowed to cool to less than 150 °C within 6 s. Typical dwell time is 4 s at 250 °C.

A modified wave soldering technique is recommended using two solder waves (dual-wave) in which a turbulent wave with high upward pressure is followed by a smooth laminar wave. Using a mildly-activated flux eliminates the need for removal of corrosive residues in most applications.

BY SOLDER PASTE REFLOW

Reflow soldering requires the solder paste (a suspension of fine solder particles, flux and binding agent) to be

applied to the substrate by screen printing, stencilling or pressure-syringe dispensing before device placement.

Several techniques exist for reflowing; for example, thermal conduction by heated belt, infrared, and vapour-phase reflow. Dwell times vary between 50 and 300 s according to method. Typical reflow temperatures range from 215 to 250 °C.

Preheating is necessary to dry the paste and evaporate the binding agent. Preheating duration: 45 min at 45 °C.

REPAIRING SOLDERED JOINTS (BY HAND-HELD SOLDERING IRON OR PULSE-HEATED SOLDER TOOL)

Fix the component by first soldering two, diagonally opposite, end pins. Apply the heating tool to the flat part of the pin only. Contact time must be limited to 10 s at up to 300 °C. When using proper tools, all other pins can be soldered in one operation within 2 to 5 s at between 270 and 320 °C. (Pulse-heated soldering is not recommended for SO packages).

For pulse-heated solder tool (resistance) soldering of VSO packages, solder is applied to the substrate by dipping or by an extra thick tin/lead plating before package placement.

#### **DEFINITIONS**

| Data sheet status         |                                                                                       |

|---------------------------|---------------------------------------------------------------------------------------|

| Objective specification   | This data sheet contains target or goal specifications for product development.       |

| Preliminary specification | This data sheet contains preliminary data; supplementary data may be published later. |

| Product specification     | This data sheet contains final product specifications.                                |

|                           |                                                                                       |

# Limiting values

Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of this specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

# Application information

Where application information is given, it is advisory and does not form part of the specification.

#### LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such improper use or sale.