# INTEGRATED CIRCUITS

Preliminary specification

2002 Jul 16

| CONTEN     | TS                                                    | 9    | LIMITING VALUES                                     |

|------------|-------------------------------------------------------|------|-----------------------------------------------------|

| 1          | FEATURES                                              | 10   | THERMAL CHARACTERISTICS                             |

| 2          | GENERAL DESCRIPTION                                   | 11   | CHARACTERISTICS                                     |

| 3          | QUICK REFERENCE DATA                                  | 12   | TIMING CHARACTERISTICS                              |

| 4          | ORDERING INFORMATION                                  | 13   | APPLICATION INFORMATION                             |

| 5          | BLOCK DIAGRAM                                         | 14   | PACKAGE OUTLINE                                     |

| 6          | PINNING                                               | 15   | SOLDERING                                           |

| 7          | FUNCTIONAL DESCRIPTION                                | 15.1 | Introduction to soldering surface mount<br>packages |

| 7.1        | Programming registers                                 | 15.2 | Reflow soldering                                    |

| 7.2        | Device ID                                             | 15.3 | Wave soldering                                      |

| 7.3        | Initialization                                        | 15.4 | Manual soldering                                    |

| 7.4        | Clock management                                      | 15.5 | Suitability of surface mount IC packages for        |

| 7.5        | Synchronization pulse distribution                    |      | wave and reflow soldering methods                   |

| 7.6<br>7.7 | Interrupt generation                                  | 16   | DATA SHEET STATUS                                   |

| 7.8        | Triple analog-to-digital converter<br>Input interface | 17   | DEFINITIONS                                         |

| 7.9        | Colour processing                                     | 18   | DISCLAIMERS                                         |

| 7.10       | RGB mode detection and auto-adjustment                | 19   | PURCHASE OF PHILIPS I <sup>2</sup> C COMPONENTS     |

| 7.11       | Decoupling FIFO                                       | 19   |                                                     |

| 7.12       | Scaling                                               |      |                                                     |

| 7.13       | On screen display                                     |      |                                                     |

| 7.14       | Colour look-up table                                  |      |                                                     |

| 7.15       | Dithering unit                                        |      |                                                     |

| 7.16       | Output interface                                      |      |                                                     |

| _          |                                                       |      |                                                     |

- 8 BOUNDARY SCAN TEST

- 8.1 Initialization of boundary scan circuit

- 8.2 Device identification codes

#### 1 FEATURES

- Integrated triple Analog-to-Digital Converter (ADC) for RGB analog sampling up to 110 MHz

- Integrated PLL for dot clock recovery

- Integrated composite sync slicer

- Integrated sync-on-green separation

- Support of Super Extended Graphics Adapter (SXGA) input mode

- Independent horizontal and vertical arbitrary ratio up and downscaling

- Video mode detection

- Auto-adjustment support for sampling phase and frequency, picture alignment and colour alignment

- · Advanced colour adjustment

- Integrated On Screen Display (OSD) controller with predefined and programmable font and bit-mapped graphics, as well as a hardware overlay cursor

- 10-bit gamma correction

- Support for 6-bit and 8-bit panels by temporal dithering

- Freely programmable output timing supports displays of virtually any manufacturer

- Directly interfaces row and column drivers (TCON), versatile timing generation

- Programmable output pin ordering

- Adjustable output pin ordering

- High-speed I<sup>2</sup>C-bus interface up to 3.4 Mbits/s

- Event driven interrupt generation for easy interfacing with microcontroller software.

#### 2 GENERAL DESCRIPTION

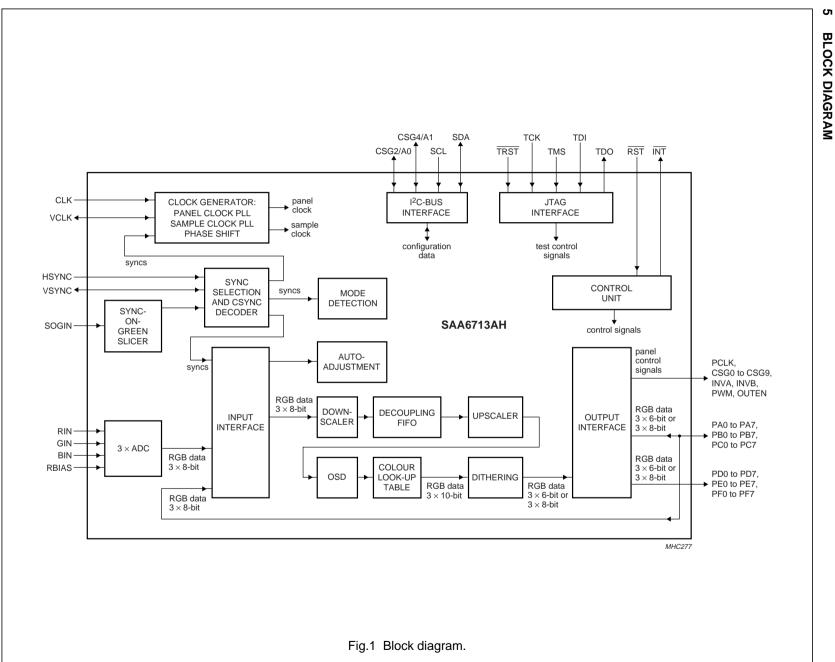

The SAA6713AH is a single input single-chip Thin Film Transistor (TFT) display controller IC with analog VGA standard input capabilities. Additionally, the SAA6713AH includes a wide range of functions for processing and the measurement of incoming RGB data according to the requirements of an XGA TFT display.

Covered functions are accurate measurements for the horizontal and vertical input frequencies to determine the incoming video mode and advanced auto-adjustment features that provide all data for a fast and accurate adjustment of frequency, phase and gain settings. The unit is able to generate interrupts for easy interfacing with a system microcontroller with separately maskable interrupt conditions. The input section handles incoming data up to SXGA resolution that can be downscaled individually in width and height to fit to the connected panel resolution. Independent horizontal and vertical upscaling with enhanced programmable filter possibilities provides the IC's core functionality of high-quality scaling. Picture quality is further supported by an enhanced colour management including a 10-bit gamma correction function. A sophisticated dithering unit allows the use of low-end 6-bit panels while keeping up the high quality image impression.

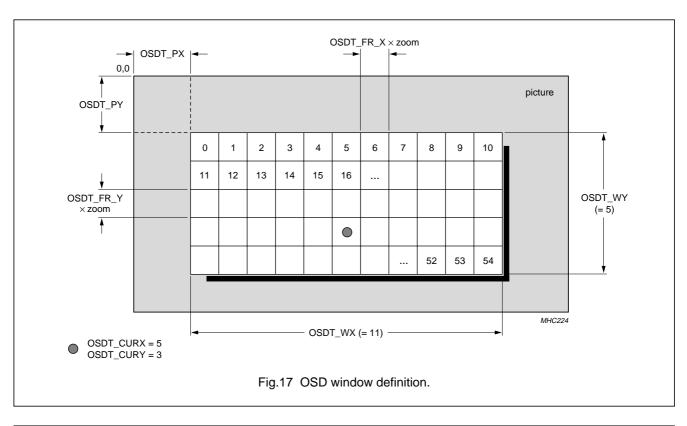

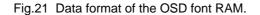

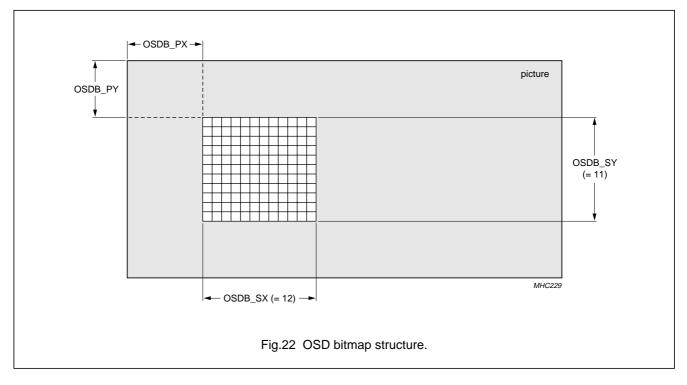

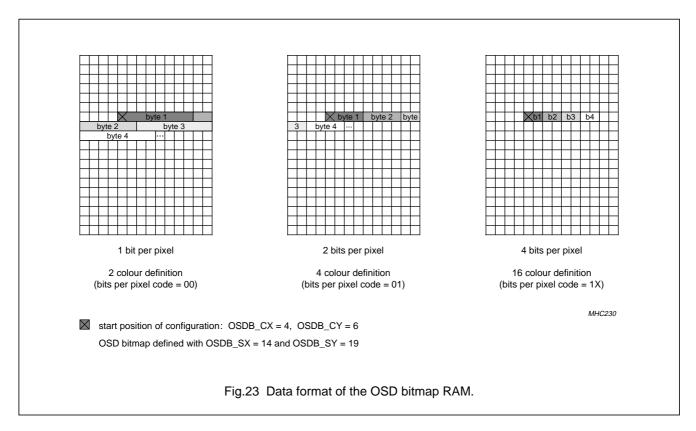

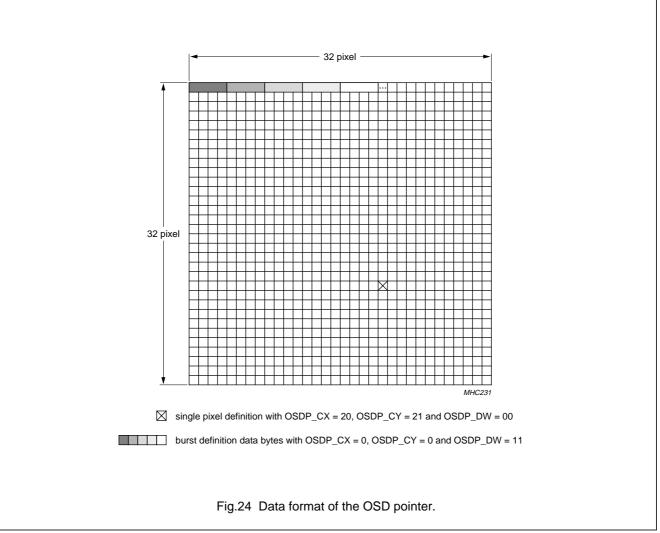

An advanced OSD generator is integrated with a fixed  $12 \times 18$  ROM font consisting of 179 ANSI characters, 77 Japanese characters, 48 multicolour icons and 48 single colour icons. In addition to these fixed size characters another 112 different border characters can be generated in any desired font size between  $8 \times 8$  and  $32 \times 32$  pixels. Another 38 special characters are provided particularly for multicolour slider icons that can be parametrized in size and style. For higher flexibility of the OSD appearance a downloadable mixed multicolour or single colour font with any programmable character size between  $8 \times 8$  to  $32 \times 32$  pixels and up to four colours per character can be used and displayed together with the predefined ROM characters. A special bitmap organized graphical OSD with up to 16 individual colours allows to include graphic items like company logos, while a double buffered OSD cursor gives the ability to use animated pointers within an on screen menu. The panel timing interface can not only drive today's common timing controller based panel interfaces, but it has also the capability to directly drive the row and column drivers of a panel itself. An adjustable output pin ordering guarantees easy board layout with any type of panel connector.

The SAA6713AH represents a fully integrated single-chip solution for low-end monitors, offering both high quality scaling and an advanced OSD generator.

# SAA6713AH

Preliminary specification

# SAA6713AH

#### 3 QUICK REFERENCE DATA

| SYMBOL                                                                     | PARAMETER                                                                                                                                    | CONDITIONS | MIN.            | TYP.     | MAX.   | UNIT |

|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------|----------|--------|------|

| V <sub>DDD(IC)</sub>                                                       | digital supply voltage for internal core on pins V <sub>DDD(IC1)</sub> to V <sub>DDD(IC9)</sub>                                              |            | 2.3             | 2.5      | 2.7    | V    |

| V <sub>DDA</sub>                                                           | analog supply voltage on pins $V_{DDA(R)}$ ,<br>$V_{DDA(G)}$ , $V_{DDA(B)}$ , $V_{DDA(ADC)(R)}$ , $V_{DDA(ADC)(G)}$<br>and $V_{DDA(ADC)(B)}$ |            | 2.3             | 2.5      | 2.7    | V    |

| V <sub>DD(PLL)</sub> ,<br>V <sub>DDD(PLL)</sub> ,<br>V <sub>DDA(PLL)</sub> | supply voltage for PLL on pins $V_{DD(PLL)(P)},$ $V_{DDD(PLL)(S)}$ and $V_{DDA(PLL)(S)}$                                                     |            | 2.3             | 2.5      | 2.7    | V    |

| V <sub>DDA(IB)</sub>                                                       | analog supply voltage for input buffer on pin $V_{\text{DDA(IB)}}$                                                                           |            | 2.7             | 3.0      | 3.3    | V    |

| V <sub>DDD(EP)</sub>                                                       | external digital pad supply voltage for pins V <sub>DDD(EP1)</sub> to V <sub>DDD(EP10</sub> )                                                |            | 3.0             | 3.3      | 3.6    | V    |

| V <sub>DDA(EP)</sub>                                                       | external analog pad supply voltage for pin $V_{\text{DDA}(\text{EP})}$                                                                       |            | 3.0             | 3.3      | 3.6    | V    |

| I <sub>DDD(tot)</sub>                                                      | total digital supply current                                                                                                                 |            | -               | tbf      | -      | mA   |

| Vi                                                                         | input voltage                                                                                                                                | note 1     | LV1             | TL compa | atible |      |

| Vo                                                                         | output voltage for TFT port                                                                                                                  |            | CMOS compatible |          |        |      |

| T <sub>amb</sub>                                                           | ambient temperature                                                                                                                          |            | 0               | -        | tbf    | °C   |

#### Note

1. Pins HSYNC, VSYNC, SDA and SCL are 5 V tolerant inputs.

#### 4 ORDERING INFORMATION

| TYPE NUMBER  |        | PACKAGE                                                                                                                |          |

|--------------|--------|------------------------------------------------------------------------------------------------------------------------|----------|

| ITFE NUMBER  | NAME   | DESCRIPTION                                                                                                            | VERSION  |

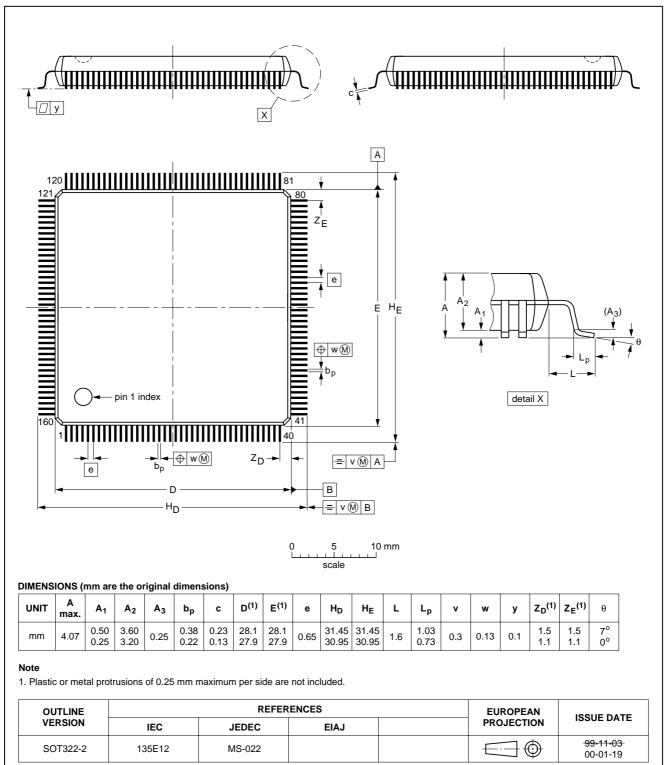

| SAA6713AH/V1 | QFP160 | plastic quad flat package; 160 leads (lead length 1.6 mm);<br>body $28 \times 28 \times 3.4$ mm; high stand-off height | SOT322-2 |

# SAA6713AH

2002 Jul 16

\_

σī

#### 6 PINNING

| SYMBOL                      | <b>PIN</b> <sup>(1)</sup> | TYPE | DESCRIPTION                                                                |

|-----------------------------|---------------------------|------|----------------------------------------------------------------------------|

| V <sub>SSA(BIAS)(B)</sub>   | 1                         | _    | analog ground for bias; blue channel                                       |

| BIN                         | 2                         | Α    | blue colour signal input                                                   |

| V <sub>DDA(ADC)(B)</sub>    | 3                         | _    | analog supply voltage for ADC; blue channel (2.5 V)                        |

| REF_B                       | 4                         | Α    | blue channel reference input                                               |

| V <sub>SSA(ADC)(B)</sub>    | 5                         | _    | analog supply ground for ADC; blue channel                                 |

| V <sub>DDA(B)</sub>         | 6                         | _    | analog supply voltage; blue channel (2.5 V)                                |

| V <sub>SSA(B)</sub>         | 7                         | _    | analog supply ground; blue channel                                         |

| V <sub>DDA(IB)</sub>        | 8                         | _    | analog supply voltage for input buffers (3.0 V)                            |

| RBIAS                       | 9                         | Α    | external bias resistor input                                               |

| V <sub>SSA(BIAS)(SOG)</sub> | 10                        | _    | analog ground for bias; sync-on-green                                      |

| SOGIN                       | 11                        | А    | sync-on-green input                                                        |

| V <sub>SSA(BIAS)(G)</sub>   | 12                        | _    | analog ground for bias; green channel                                      |

| GIN                         | 13                        | Α    | green colour signal input                                                  |

| V <sub>DDA(ADC)(G)</sub>    | 14                        | _    | analog supply voltage for ADC; green channel (2.5 V)                       |

| REF_G                       | 15                        | A    | green channel reference input                                              |

| V <sub>SSA(ADC)(G)</sub>    | 16                        | _    | analog supply ground for ADC; green channel                                |

| V <sub>DDA(G)</sub>         | 17                        | _    | analog supply voltage; green channel (2.5 V)                               |

| V <sub>SSA(G)</sub>         | 18                        | _    | analog supply ground; green channel                                        |

| V <sub>SSA(BIAS)(R)</sub>   | 19                        | _    | analog ground for bias; red channel                                        |

| RIN                         | 20                        | Α    | red colour signal input                                                    |

| V <sub>DDA(ADC)(R)</sub>    | 21                        | _    | analog supply voltage for ADC; red channel (2.5 V)                         |

| REF_R                       | 22                        | Α    | red channel reference input                                                |

| V <sub>SSA(ADC)(R)</sub>    | 23                        | _    | analog supply ground for ADC; red channel                                  |

| V <sub>DDA(R)</sub>         | 24                        | _    | analog supply voltage; red channel (2.5 V)                                 |

| V <sub>SSA(R)</sub>         | 25                        | _    | analog supply ground; red channel                                          |

| V <sub>DDD(IC1)</sub>       | 26                        | _    | internal digital core supply voltage 1 (2.5 V)                             |

| n.c.                        | 27                        | _    | not connected                                                              |

| n.c.                        | 28                        | _    | not connected                                                              |

| V <sub>SSD(IC1)</sub>       | 29                        | _    | internal digital core supply ground 1                                      |

| n.c.                        | 30                        | _    | not connected                                                              |

| n.c.                        | 31                        | _    | not connected                                                              |

| V <sub>DDD(IC2)</sub>       | 32                        | _    | internal digital core supply voltage 2 (2.5 V)                             |

| n.c.                        | 33                        | _    | not connected                                                              |

| n.c.                        | 34                        | _    | not connected                                                              |

| V <sub>SSD(IC2)</sub>       | 35                        | _    | internal digital core supply ground 2                                      |

| n.c.                        | 36                        | _    | not connected                                                              |

| RESERVED1                   | 37                        | _    | connect with a pull-up resistor of 51 $\Omega$ to V <sub>DDE</sub> (3.3 V) |

| V <sub>DDD(IC3)</sub>       | 38                        | _    | internal digital core supply voltage 3 (2.5 V)                             |

| V <sub>SSD(IC3)</sub>       | 39                        | _    | internal digital core supply ground 3                                      |

| n.c.                        | 40                        | _    | not connected                                                              |

| SYMBOL                | <b>PIN</b> <sup>(1)</sup> | TYPE | DESCRIPTION                                                                                                           |

|-----------------------|---------------------------|------|-----------------------------------------------------------------------------------------------------------------------|

| SDA                   | 41                        | I/O  | serial data input or output (I <sup>2</sup> C-bus)                                                                    |

| SCL                   | 42                        | I    | serial clock input (I <sup>2</sup> C-bus)                                                                             |

| RESERVED2             | 43                        | _    | connect with a pull-up resistor of 4.7 k $\Omega$ to V <sub>DDE</sub> (3.3 or 5 V)                                    |

| RESERVED3             | 44                        | _    | connect with a pull-up resistor of 4.7 k $\Omega$ to V <sub>DDE</sub> (3.3 or 5 V)                                    |

| V <sub>SSD(IC4)</sub> | 45                        | _    | internal digital core supply ground 4                                                                                 |

| V <sub>DDD(IC4)</sub> | 46                        | _    | internal digital core supply voltage 4 (2.5 V)                                                                        |

| CLK                   | 47                        | I    | master clock input                                                                                                    |

| V <sub>SSD(EP1)</sub> | 48                        | _    | external digital pad supply ground 1                                                                                  |

| V <sub>DDD(EP1)</sub> | 49                        | _    | external digital pad supply voltage 1 (3.3 V)                                                                         |

| ĪNT                   | 50                        | 0    | microcontroller interrupt output (active LOW)                                                                         |

| RST                   | 51                        | I    | master reset input (active LOW)                                                                                       |

| PCLK                  | 52                        | 0    | panel clock output                                                                                                    |

| CSG0                  | 53                        | 0    | control signal generator 0 output                                                                                     |

| CSG1                  | 54                        | 0    | control signal generator 1 output                                                                                     |

| CSG2/A0               | 55                        | I/O  | control signal generator 2 output (CSG2) or I <sup>2</sup> C-bus slave address input, latched via hardware reset (A0) |

| V <sub>SSD(EP2)</sub> | 56                        | _    | external digital pad supply ground 2                                                                                  |

| V <sub>DDD(EP2)</sub> | 57                        | _    | external digital pad supply voltage 2 (3.3 V)                                                                         |

| PA0                   | 58                        | I/O  | panel data port A bit 0                                                                                               |

| PA1                   | 59                        | I/O  | panel data port A bit 1                                                                                               |

| PA2                   | 60                        | I/O  | panel data port A bit 2                                                                                               |

| PA3                   | 61                        | I/O  | panel data port A bit 3                                                                                               |

| PA4                   | 62                        | I/O  | panel data port A bit 4                                                                                               |

| PA5                   | 63                        | I/O  | panel data port A bit 5                                                                                               |

| PA6                   | 64                        | I/O  | panel data port A bit 6                                                                                               |

| PA7                   | 65                        | I/O  | panel data port A bit 7                                                                                               |

| V <sub>SSD(EP3)</sub> | 66                        | _    | external digital pad supply ground 3                                                                                  |

| V <sub>DDD(EP3)</sub> | 67                        | _    | external digital pad supply voltage 3 (3.3 V)                                                                         |

| PB0                   | 68                        | I/O  | panel data port B bit 0                                                                                               |

| PB1                   | 69                        | I/O  | panel data port B bit 1                                                                                               |

| V <sub>SSD(IC5)</sub> | 70                        | _    | internal digital core supply ground 5                                                                                 |

| V <sub>DDD(IC5)</sub> | 71                        | _    | internal digital core supply voltage 5 (2.5 V)                                                                        |

| PB2                   | 72                        | I/O  | panel data port B bit 2                                                                                               |

| PB3                   | 73                        | I/O  | panel data port B bit 3                                                                                               |

| PB4                   | 74                        | I/O  | panel data port B bit 4                                                                                               |

| PB5                   | 75                        | I/O  | panel data port B bit 5                                                                                               |

| PB6                   | 76                        | I/O  | panel data port B bit 6                                                                                               |

| PB7                   | 77                        | I/O  | panel data port B bit 7                                                                                               |

| V <sub>SSD(EP4)</sub> | 78                        | _    | external digital pad supply ground 4                                                                                  |

| V <sub>DDD(EP4)</sub> | 79                        | _    | external digital pad supply voltage 4 (3.3 V)                                                                         |

| PC0                   | 80                        | I/O  | panel data port C bit 0                                                                                               |

**PIN**<sup>(1)</sup> TYPE DESCRIPTION SYMBOL PC1 81 I/O panel data port C bit 1 PC2 I/O panel data port C bit 2 82 PC3 panel data port C bit 3 83 I/O PC4 84 I/O panel data port C bit 4 PC5 I/O panel data port C bit 5 85 PC6 I/O 86 panel data port C bit 6 PC7 I/O 87 panel data port C bit 7 88 external digital pad supply ground 5 V<sub>SSD(EP5)</sub> \_ 89 external digital pad supply voltage 5 (3.3 V) V<sub>DDD(EP5)</sub> \_ V<sub>SSD(IC6)</sub> 90 \_ internal digital core supply ground 6 V<sub>DDD</sub>(IC6) 91 internal digital core supply voltage 6 (2.5 V) PD0 0 92 panel data port D bit 0 PD1 93 0 panel data port D bit 1 PD2 0 94 panel data port D bit 2 PD3 95 0 panel data port D bit 3 PD4 0 panel data port D bit 4 96 PD5 0 97 panel data port D bit 5 PD6 0 panel data port D bit 6 98 PD7 99 0 panel data port D bit 7 100 \_ external digital pad supply ground 6 V<sub>SSD(EP6)</sub> 101 external digital pad supply voltage 6 (3.3 V) V<sub>DDD(EP6)</sub> \_ 102 internal digital core supply ground 7 V<sub>SSD(IC7)</sub> \_ 103 internal digital core supply voltage 7 (2.5 V) V<sub>DDD(IC7)</sub> \_ PE0 104 0 panel data port E bit 0 0 PE1 105 panel data port E bit 1 PE2 106 0 panel data port E bit 2 PE3 107 0 panel data port E bit 3 PE4 108 0 panel data port E bit 4 PE5 109 0 panel data port E bit 5 PE6 0 110 panel data port E bit 6 PE7 111 0 panel data port E bit 7 112 external digital pad supply ground 7 \_ V<sub>SSD(EP7)</sub> 113 external digital pad supply voltage 7 (3.3 V) V<sub>DDD(EP7)</sub> panel data port F bit 0 PF0 114 0 PF1 115 0 panel data port F bit 1 PF2 116 0 panel data port F bit 2 PF3 117 0 panel data port F bit 3 PF4 0 panel data port F bit 4 118 PF5 119 0 panel data port F bit 5 PF6 120 0 panel data port F bit 6 PF7 121 0 panel data port F bit 7

| SYMBOL                   | <b>PIN</b> <sup>(1)</sup> | TYPE | DESCRIPTION                                                                                                           |

|--------------------------|---------------------------|------|-----------------------------------------------------------------------------------------------------------------------|

| V <sub>SSD(IC8)</sub>    | 122                       | _    | internal digital core supply ground 8                                                                                 |

| V <sub>DDD</sub> (IC8)   | 123                       | _    | internal digital core supply voltage 8 (2.5 V)                                                                        |

| V <sub>SSD(EP8)</sub>    | 124                       | _    | external digital pad supply ground 8                                                                                  |

| V <sub>DDD(EP8)</sub>    | 125                       | _    | external digital pad supply voltage 8 (3.3 V)                                                                         |

| CSG3                     | 126                       | 0    | control signal generator 3 output                                                                                     |

| CSG4/A1                  | 127                       | I/O  | control signal generator 4 output (CSG4) or I <sup>2</sup> C-bus slave address input, latched via hardware reset (A1) |

| CSG5                     | 128                       | 0    | control signal generator 5 output                                                                                     |

| CSG6                     | 129                       | 0    | control signal generator 6 output                                                                                     |

| CSG7                     | 130                       | 0    | control signal generator 7 output                                                                                     |

| V <sub>SSD(EP9)</sub>    | 131                       | _    | external digital pad supply ground 9                                                                                  |

| V <sub>DDD(EP9)</sub>    | 132                       | _    | external digital pad supply voltage 9 (3.3 V)                                                                         |

| CSG8                     | 133                       | 0    | control signal generator 8 output                                                                                     |

| CSG9                     | 134                       | 0    | control signal generator 9 output                                                                                     |

| VCLK                     | 135                       | I/O  | sample clock input or output; configurable as output if generated internally                                          |

| INVA                     | 136                       | 0    | data inversion output of ports A, B and C                                                                             |

| INVB                     | 137                       | 0    | data inversion output of ports D, E and F                                                                             |

| OUTEN                    | 138                       | 0    | output enable status output                                                                                           |

| PWM                      | 139                       | 0    | pulse width modulation for control of backlight brightness output                                                     |

| VSYNC                    | 140                       | I/O  | vertical sync input or output; configurable as output if decoded from composite sync                                  |

| HSYNC                    | 141                       | I    | horizontal and composite sync input                                                                                   |

| V <sub>SSD(EP10)</sub>   | 142                       | _    | external digital pad supply ground 10                                                                                 |

| V <sub>DDD(EP10)</sub>   | 143                       | _    | external digital pad supply voltage 10 (3.3 V)                                                                        |

| V <sub>SSD(IC9)</sub>    | 144                       | _    | internal digital core supply ground 9                                                                                 |

| V <sub>DDD(IC9)</sub>    | 145                       | _    | internal digital core supply voltage 9 (2.5 V)                                                                        |

| V <sub>SS(PLL)(P)</sub>  | 146                       | _    | supply ground for panel clock phase locked loop                                                                       |

| V <sub>DD(PLL)(P)</sub>  | 147                       | _    | supply voltage for panel clock phase locked loop (2.5 V)                                                              |

| n.c.                     | 148                       | _    | do not connect                                                                                                        |

| V <sub>SSA(PLL)(S)</sub> | 149                       | _    | analog supply ground for sample clock phase locked loop                                                               |

| V <sub>DDA(PLL)(S)</sub> | 150                       | _    | analog supply voltage for sample clock phase locked loop (2.5 V)                                                      |

| V <sub>SSD(PLL)(S)</sub> | 151                       | _    | digital supply ground for sample clock phase locked loop                                                              |

| V <sub>DDD(PLL)(S)</sub> | 152                       | _    | digital supply voltage for sample clock phase locked loop (2.5 V)                                                     |

| TRST                     | 153                       | I    | test reset input for boundary scan test (active LOW); note 2                                                          |

| ТСК                      | 154                       | I    | test clock input for boundary scan test; note 2                                                                       |

| TDI                      | 155                       | I    | test data input for boundary scan test; note 2                                                                        |

| TMS                      | 156                       | I    | test mode select input for boundary scan test or scan test; note 2                                                    |

| TDO                      | 157                       | 0    | test data output for boundary scan test                                                                               |

## SAA6713AH

| SYMBOL               | <b>PIN</b> <sup>(1)</sup> | TYPE | DESCRIPTION                                                            |

|----------------------|---------------------------|------|------------------------------------------------------------------------|

| V <sub>SSA(EP)</sub> | 158                       | -    | external analog pad supply ground                                      |

| V <sub>DDA(EP)</sub> | 159                       | -    | external analog pad supply voltage (3.3 V)                             |

| AGCANA               | 160                       | _    | analog test pad (should be connected to analog ground for application) |

#### Notes

- 1. For pin type description see Table 1.

- 2. For board design without boundary scan implementation connect pins TRST, TCK, TDI and TMS to ground.

#### **Table 1**Pin type description

| TYPE | DESCRIPTION             |

|------|-------------------------|

| А    | analog input            |

| 1    | digital input           |

| 0    | digital output          |

| I/O  | digital input or output |

#### VDDA(EP) TDO TTO TTO TTO TTD VDDD(PLL)(S) VSSC(PLL)(S) VSSC(PLL)(S) VSSC(PLL)(S) VSSC(PLL)(S) VSSC(PLL)(S) VSSC(PL)(S) VSSC(PP10) VSSD(EP10) AGCANA 1120 1120 1125 1125 1125 1122 1122 1122 VSSA(BIAS)(B) 1 $\bigcirc$ 120 PF6 BIN 2 119 PF5 VDDA(ADC)(B) 3 118 PF4 REF\_B 4 117 PF3 VSSA(ADC)(B) 5 116 PF2 VDDA(B) 6 115 PF1 V<sub>SSA(B)</sub> 7 114 PF0 VDDA(IB) 8 113 V<sub>DDD(EP7)</sub> RBIAS 9 112 VSSD(EP7) VSSA(BIAS)(SOG) 10 111 PE7 SOGIN 11 110 PE6 VSSA(BIAS)(G) 12 109 PE5 GIN 13 108 PE4 VDDA(ADC)(G) 14 107 PE3 REF\_G 15 106 PE2 VSSA(ADC)(G) 16 105 PE1 VDDA(G) 17 104 PE0 103 V<sub>DDD(IC7)</sub> VSSA(G) 18 VSSA(BIAS)(R) 19 102 VSSD(IC7) RIN 20 101 V<sub>DDD(EP6)</sub> **SAA6713AH** VDDA(ADC)(R) 21 100 V<sub>SSD(EP6)</sub> REF\_R 22 99 PD7 VSSA(ADC)(R) 23 98 PD6 VDDA(R) 24 97 PD5 V<sub>SSA(R)</sub> 25 96 PD4 VDDD(IC1) 26 95 PD3 n.c. 27 94 PD2 n.c. 28 93 PD1 VSSD(IC1) 29 92 PD0 n.c. 30 91 V<sub>DDD</sub>(IC6) n.c. 31 90 VSSD(IC6) VDDD(IC2) 32 89 V<sub>DDD(EP5)</sub> 88 VSSD(EP5) n.c. 33 n.c. 34 87 PC7 VSSD(IC2) 35 86 PC6 n.c. 36 85 PC5 RESERVED1 37 84 PC4 VDDD(IC3) 38 83 PC3 VSSD(IC3) 39 82 PC2 n.c. 40 81 PC1 SDA MHC278 Fig.2 Pin configuration.

2002 Jul 16

SAA6713AH

# XGA analog input flat panel controller

#### 7 FUNCTIONAL DESCRIPTION

In this chapter detailed information for the general configuration of the SAA6713AH is provided as well as detailed background information belonging to certain submodules of the device. Due to the high complexity of the device functionality this section should be studied very carefully.

#### 7.1 Programming registers

#### 7.1.1 CONFIGURATION PARAMETER MAPPING

The SAA6713AH operation is controlled by configuration parameters, that can be multiple-bit words or consist of only a single bit. The configuration parameters are mapped to bits of the 8 bit I<sup>2</sup>C-bus programming registers, that are accessible via the I<sup>2</sup>C-bus interface. Read-out data such as measurement results or interrupt states is mapped to readable I<sup>2</sup>C-bus registers.

The I<sup>2</sup>C-bus registers are organized in pages. Generally, a register can only be accessed if the particular page is activated with the exception of global registers, so non-global registers are addressed by the I<sup>2</sup>C-bus subaddress in combination with the matching active page, but global registers are addressed by the subaddress independently of the active page.

The global registers are mapped to I<sup>2</sup>C-bus subaddresses F8H to FFH. The active page is defined by page\_select at subaddress FFH. In general, registers belonging to the same functional unit are mapped onto the same page. The I<sup>2</sup>C-bus register pages are shown in Table 2.

| Table 2I <sup>2</sup> C-bus register pages | Table 2 | I <sup>2</sup> C-bus | register | pages |

|--------------------------------------------|---------|----------------------|----------|-------|

|--------------------------------------------|---------|----------------------|----------|-------|

| PAGE | FUNCTIONAL UNIT                       |

|------|---------------------------------------|

| 0    | control unit and clock generator      |

| 1    | ADC control                           |

| 2    | mode detection                        |

| 3    | auto-adjustment                       |

| 4    | input interface and picture generator |

| 5    | colour processing                     |

| 6    | decoupling FIFO                       |

| 7    | scalers                               |

| 8    | OSD                                   |

| 9    | OSD colour definition                 |

| 10   | gamma correction and dithering        |

| 11   | TFT output interface                  |

#### 7.1.2 I<sup>2</sup>C-BUS INTERFACE

The I<sup>2</sup>C-bus serial interface consists of two pins: the serial clock pin SCL and the serial data pin SDA.

#### 7.1.2.1 Transmission bit rate

The I<sup>2</sup>C-bus interface supports transmission speeds of up to 3.4 Mbits/s, given that a minimum system clock rate is provided. The required system clock rate depends on the target I<sup>2</sup>C-bus bit rate, which is the clock rate applied to pin SCL, and the spike suppression mode selected by iic\_spike\_mode in register IIC\_MODE (03H at page 0) as shown in Table 3. If iic\_spike\_mode is set to 2, a high oversampling rate is used and the most effective spike suppression is provided.

| iic_spike_<br>mode[1:0] | SYSTEM<br>CLOCK                | DESCRIPTION                |

|-------------------------|--------------------------------|----------------------------|

| 00                      | $>6 \times I^2$ C-bus bit rate | 2-out-of-2 filter          |

| 01                      | $>6 \times I^2$ C-bus bit rate | 2-out-of-3 majority filter |

| 10                      | >16 × $I^2$ C-bus bit rate     | 4-out-of-4 filter          |

| 11                      | not used                       |                            |

| Table 3 | I <sup>2</sup> C-bus spike | e suppression | modes |

|---------|----------------------------|---------------|-------|

|---------|----------------------------|---------------|-------|

#### 7.1.2.2 I<sup>2</sup>C-bus transmission timing

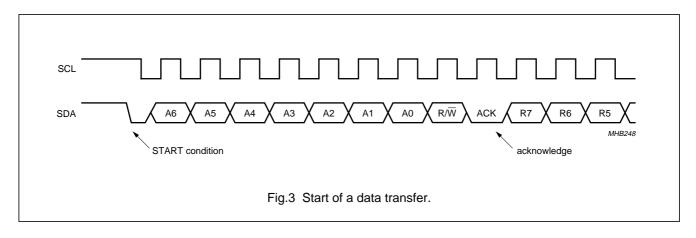

The SAA6713AH only operates as a slave and the clock pin SCL is exclusively input. Data is transmitted and received at I/O pin SDA. The SDA is an open-drain stage with an external pull-up resistor. When a logic 0 is applied, the bus is pulled to LOW-level by the output buffer. When a logic 1 is applied, the output buffer switches to 3-state and the pull-up resistor pulls the bus up to HIGH-level.

Data transfers are initiated by an I<sup>2</sup>C-bus master device by sending the start condition, which is a change from HIGH-to-LOW level at SDA when SCL is at HIGH-level (see Fig.3).

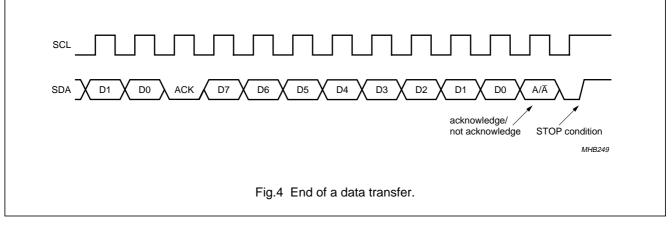

Data is transmitted byte wise. Data changes on SDA are allowed only when SCL is at LOW-level and data is sampled on the positive edge of SCL. The first transmitted byte is the recipients I<sup>2</sup>C-bus device address and the data transfer direction bit. All byte transfers are acknowledged by the recipient by pulling SDA to LOW-level for the following cycle.

# SAA6713AH

If the write mode was selected, the bus master sends a byte containing the starting subaddress and then a series of data bytes. In case the read mode was selected, the addressed slave returns a series of data bytes. A read transfer is preceded by a write transfer that transmits the starting subaddress.

Data transfers are aborted by the stop condition, when SDA is changed by the master from LOW-to-HIGH level when SCL is at HIGH-level (see Fig.4).

#### 7.1.2.3 I<sup>2</sup>C-bus device address

Bits A0 and A1 of the I<sup>2</sup>C-bus device address are externally selected by two input pins CSG2/A0 and CSG4/A1. The device address (byte) of the SAA6713AH is shown in Table 4.

#### Table 4 I<sup>2</sup>C-bus device address byte

| MSB |                     |   |   |   |    |    | LSB |  |  |  |  |  |

|-----|---------------------|---|---|---|----|----|-----|--|--|--|--|--|

|     | DEVICE ADDRESS BITS |   |   |   |    |    |     |  |  |  |  |  |

| 0   | 1                   | 1 | 1 | 0 | A1 | A0 | 0/1 |  |  |  |  |  |

The four possible I<sup>2</sup>C-bus device addresses are selected via resistor strapping at pins CSG2/A0 and CSG4/A1 (see Table 5).

During the hardware reset (pin  $\overline{RST} = LOW$ ), pins CSG2/A0 and CSG4/A1 are 3-stated. Their status at the trailing edge of signal  $\overline{RST}$  will latch and determine the device address. Pull-up and pull-down resistors (4.7 k $\Omega$ suggested) select the address. An internal pull-down resistance of approximately 100 k $\Omega$  is provided and eliminates potentially the need for any external strapping resistor. After reset, the pins carry the output of the programmable signal generators.

Table 5 Device address selection

| I <sup>2</sup> C-BUS DEVICE | STRAPPING   | <b>G</b> RESISTOR |

|-----------------------------|-------------|-------------------|

| ADDRESS                     | PIN CSG4/A1 | PIN CSG2/A0       |

| 70H                         | pull-down   | pull-down         |

| 72H                         | pull-down   | pull-up           |

| 74H                         | pull-up     | pull-down         |

| 76H                         | pull-up     | pull-up           |

# SAA6713AH

#### 7.1.2.4 I<sup>2</sup>C-bus subaddress

When transmitting a series of data bytes, after a data byte has been written or read, the subaddress for the following byte is automatically updated to allow burst access. During burst access a sequence of data bytes is written or read without repeated device or subaddressing. In general, the I<sup>2</sup>C-bus auto-increment feature uses the next higher subaddress as the succeeding byte's subaddress.

Auto-incrementing is suppressed for several addresses that provide access to the on-chip parameter RAM. In the event of upscaler register USC\_LUT\_DATA (02H at page 7) subsequent data is written to the same subaddress and the scaling curve RAM address is incremented instead.

For OSD registers OSDT\_PROP2 to OSDT\_PROP0, OSDB\_DEF and OSDP\_DEF (0FH to 11H, 31H and 4CH at page 8) and colour look-up table register CL\_VALUE\_LO (03H at page 10) different subaddress update modes are selectable and are described in the respective subsection.

#### 7.1.2.5 Multiple byte parameters

Parameters or read-out data words consisting of more than 8 bits are mapped into the address space in the order highest byte at the lowest address to lowest byte at the highest address. Multiple byte configuration parameters have to be written lowest address first and only become effective, once the byte of the highest address was written. Multiple byte read registers have to be read-out in the same order.

#### 7.1.2.6 *I*<sup>2</sup>*C*-bus test register

Register IIC\_TEST (02H at page 0) is a read and write register that can be used to verify correct operations of the I<sup>2</sup>C-bus. Any programmed value can be read back.

7.1.3 I<sup>2</sup>C-BUS REGISTER LISTING

The global registers are listed in Table 6.

The page-mapped registers are listed for each register page in Tables 7 to 17.

\_

Table 6

Global configuration registers

| REGISTER           | ADR      | R/W | RESET     | D7                         | D6           | D5 | D4                | D3              | D2          | D1         | D0         |

|--------------------|----------|-----|-----------|----------------------------|--------------|----|-------------------|-----------------|-------------|------------|------------|

| Global control: FA | H to FFI | 4   |           |                            |              |    | -                 |                 | 1           |            |            |

| GC_MISC0           | FAH      | W   | 00H       | avi_<br>noclamp_<br>sog_en | reserved     |    |                   |                 |             |            |            |

| GC_MISC1           | FBH      | W   | FFH       | avi_<br>noclamp_<br>pol    | reserved     |    |                   |                 |             |            |            |

| GC_RESET           | FCH      | W   | 1 0000    |                            |              |    | reset_<br>csdec_n | reserved        | reset_fclk  | reset_bclk | reset_oif  |

| GC_INT_MASK        | FDH      | W   | -0-0 0000 |                            | int_iif_en   |    | int_mode_<br>en   | int_auto_<br>en | int_fifo_en | int_osd_en | int_oif_en |

| GC_INT_CLR         | FEH      | W   | -1-1 1111 |                            | int_iif_clr  |    | int_mode          | int_auto        | int_fifo    | int_osd    | int_oif    |

| GC_INT_STAT        | FEH      | R   | -0-0 0000 |                            | int_iif_stat |    | int_mode          | int_auto        | int_fifo    | int_osd    | int_oif    |

| GC_PAGE            | FFH      | R/W | 0000      |                            |              |    |                   | page_selec      | :t[3:0]     | 1          |            |

Table 7

General control configuration registers (page 0); note 1

| REGISTER              | ADR     | R/W   | RESET   | D7            | D6 | D5         | D4                 | D3               | D2                | D1              | D0              |

|-----------------------|---------|-------|---------|---------------|----|------------|--------------------|------------------|-------------------|-----------------|-----------------|

| Device identification | on: 00H | to 03 | H       | ι             |    | -          | ļ                  |                  |                   | 1               | 4               |

| DEV_ID_HI             | 00H     | R     | 13H     | dev_id[15:8]  |    |            |                    |                  |                   |                 |                 |

| DEV_ID_LO             | 01H     | R     | 1CH     | dev_id[7:0]   |    |            |                    |                  |                   |                 |                 |

| IIC_TEST              | 02H     | R/W   | 00H     | iic_test[7:0] |    |            |                    |                  |                   |                 |                 |

| IIC_MODE              | 03H     | W     | 00      |               |    |            |                    |                  |                   | iic_spike_m     | ode[1:0]        |

| Clock distribution:   | 10H to  | 12H   |         | ·             |    | -          |                    |                  |                   |                 |                 |

| CD_CLK_EN             | 10H     | W     | 00 0000 |               |    | cfgclk_on  | osd_<br>cfgclk_on  | aaclk_on         | dscclk_on         | uscclk_on       | osdclk_on       |

| CD_CLK_AUTO           | 11H     | W     | 1111    |               |    |            |                    | aaclk_auto       | dscclk_<br>auto   | uscclk_<br>auto | osdclk_<br>auto |

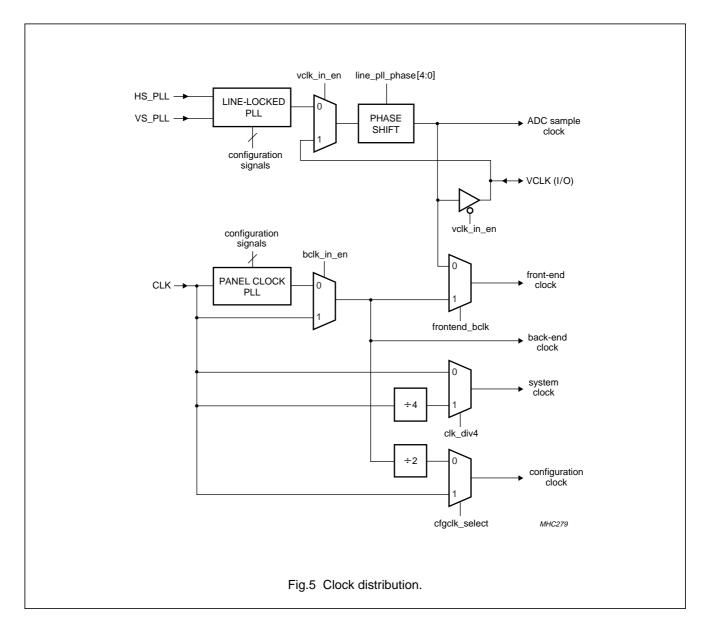

| CD_CLK_MUX            | 12H     | W     |         |               |    | vclk_in_en | cfgclk_<br>select  | fifo_fclk        | frontend_<br>bclk | bclk_in_en      | clk_div4        |

| Sync distribution:    | 18H and | 19H   |         | · ·           |    |            |                    |                  |                   |                 | -               |

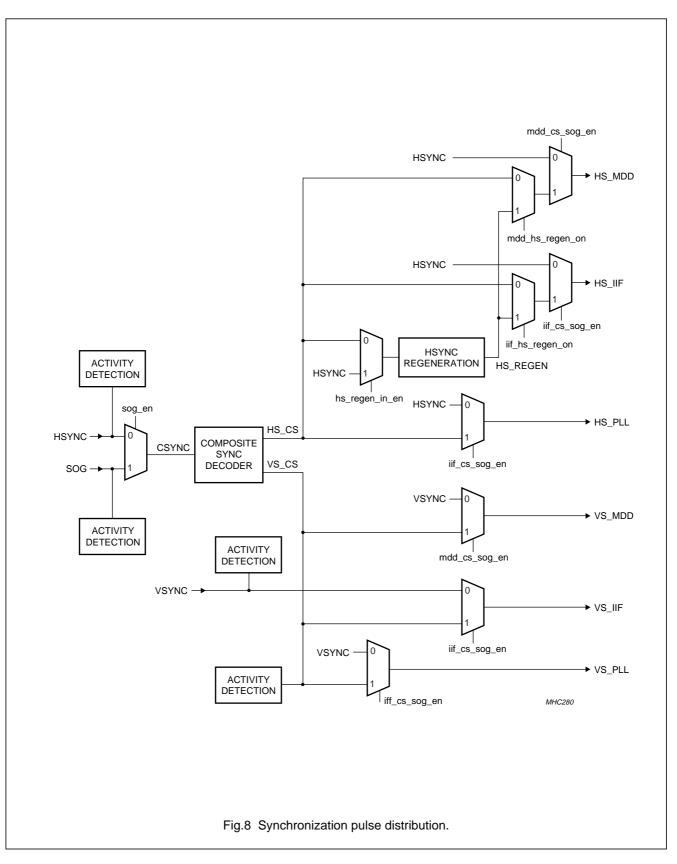

| SYNC_SEL              | 18H     | W     | 0 0000  |               |    |            | hs_regen_<br>in_en | vsync_out_<br>en | reserved          | sog_out_<br>en  | sog_en          |

XGA analog input flat panel controller

Preliminary specification

SAA6713AH

<u>ъ</u>

\_

| REGISTER                                       | ADR       | R/W    | RESET        | D7          | D6                  | D5                  | D4                  | D3                | D2                 | D1                  | D0                   |

|------------------------------------------------|-----------|--------|--------------|-------------|---------------------|---------------------|---------------------|-------------------|--------------------|---------------------|----------------------|

| SYNC_DIS                                       | 19H       | W      | -000 0000    |             | reserved            | mdd_cs_<br>sog_en   | mdd_hs_<br>regen_on |                   | reserved           | iif_cs_sog_<br>en   | iif_hs_<br>regen_on  |

| PLL programming                                | : 20H to  | 29H    | •            |             |                     |                     | •                   | •                 | •                  | •                   | •                    |

| CD_PLL_CTRL                                    | 20H       | W      | -010 -000    |             | line_pll_<br>hs_pol | line_pll_<br>vs_pol | line_pll_en         |                   | pll_src            | pll_pre_<br>div_en  | pll_en               |

| CD_PLL_P_HI                                    | 21H       | W      | 00H          | pll_pre_div | /[15:8]             | -                   |                     | •                 | -                  |                     | 1                    |

| CD_PLL_P_LO                                    | 22H       | W      | 00H          | pll_pre_div | /[7:0]              |                     |                     |                   |                    |                     |                      |

| CD_PLL_HI                                      | 23H       | W      | 00 0000      |             |                     | pll_m_div[1         | [:0]                | pll_n_div[11      | 1:8]               |                     |                      |

| CD_PLL_LO                                      | 24H       | W      | 00H          | pll_n_div[7 | <b>'</b> :0]        | -                   |                     | •                 |                    |                     |                      |

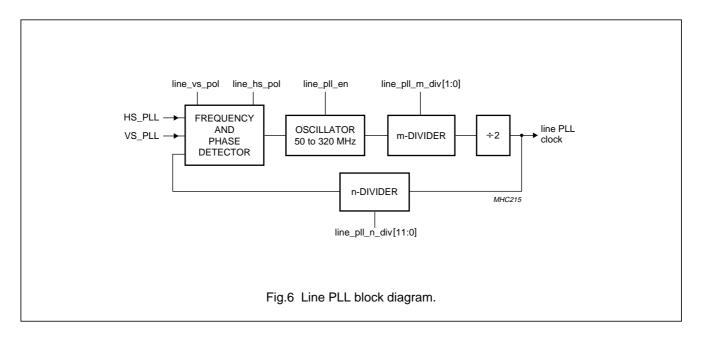

| CD_LPLL_HI                                     | 25H       | W      | 00 0000      |             |                     | line_pll_m_         | _div[1:0]           | line_pll_n_c      | div[11:8]          |                     |                      |

| CD_LPLL_LO                                     | 26H       | W      | 00H          | line_pll_n_ | _div[7:0]           | -                   |                     | •                 |                    |                     |                      |

| CD_LPLL_PHA                                    | 27H       | W      | 0 0000       |             |                     |                     | line_pll_pha        | ase[4:0]          |                    |                     |                      |

| CD_LPLL_PD                                     | 28H       | W      | -100 0000    |             | phase_<br>auto      | phase_<br>select    | pd_pll_phas         | se[4:0]           |                    |                     |                      |

| CD_PLL_LOCK                                    | 29H       | R      | XXX          |             |                     |                     |                     |                   | phase_<br>inlock   | pll_inlock          | Ilpll_inlock         |

| Interface timing: 3                            | 4H and    | 35H    |              |             |                     |                     | ·                   | ·                 | ·                  | •                   |                      |

| IT_CTRL                                        | 34H       | W      | 11           |             |                     |                     |                     |                   |                    | adc_pon_<br>pol     | bigger_<br>out_pol   |

| IT_PLL                                         | 35H       | W      | 1111         |             |                     |                     |                     | pll_coast_<br>pol | pll_pon_pol        | llpll_coast_<br>pol | llpll_pon_<br>pol    |

| Note                                           | •         |        | •            |             | •                   | •                   | •                   | •                 | •                  |                     |                      |

| 1. X = don't care.<br><b>Table 8</b> ADC confi | auration  | reaist | ers (page 1) |             |                     |                     |                     |                   |                    |                     |                      |

| REGISTER                                       |           | R/W    |              | D7          | D6                  | D5                  | D4                  | D3                | D2                 | D1                  | D0                   |

| ADC programming                                | g: 00H to | 06H    | 1            |             | -1                  |                     | 1                   | 1                 |                    | 1                   | 1                    |

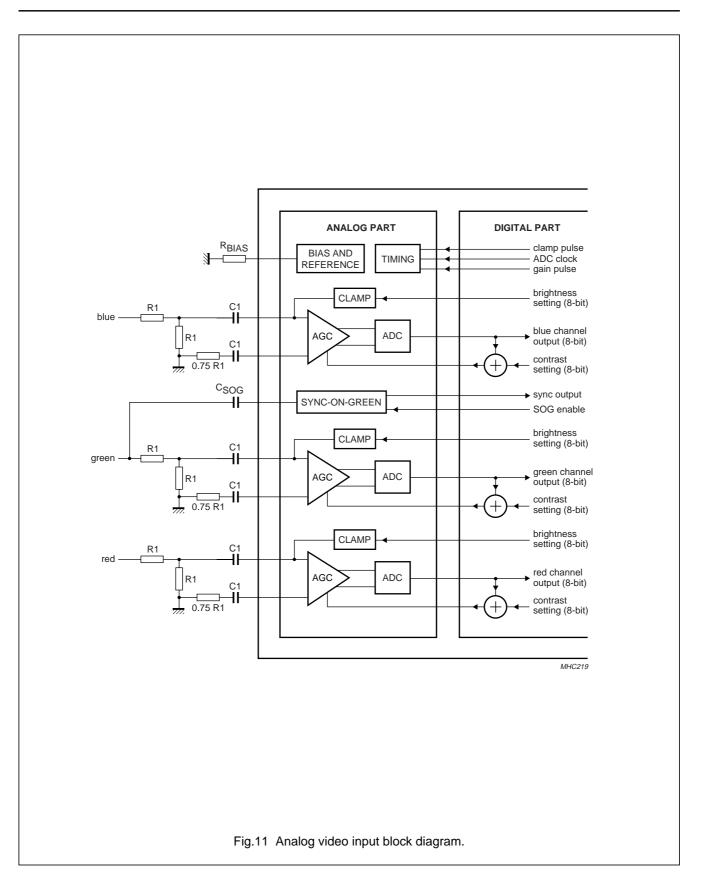

| ADC_CTRL                                       | 00H       | W      | 000          |             |                     |                     |                     |                   | sog_vs_<br>disable | reserved            | sync_on_<br>green_en |

| ADC_R_BRI                                      | 01H       | w      | 00Н          | adc_red_b   | rightness[7:0       | 0]                  |                     | 1                 | 1                  | 1                   | 1-                   |

| ADC_R_CON                                      | 02H       | w      | 00Н          | adc_red_c   | ontrast[7:0]        |                     |                     |                   |                    |                     |                      |

| ADC_G_BRI                                      | 03H       | W      | 00Н          | adc_green   | brightness          | [7:0]               |                     |                   |                    |                     |                      |

XGA analog input flat panel controller

Preliminary specification

SAA6713AH

| REGISTER                        | ADR       | R/W     | RESET          | D7                | D6                  | D5                  | D4                  | D3                  | D2                | D1                   | D0                   |

|---------------------------------|-----------|---------|----------------|-------------------|---------------------|---------------------|---------------------|---------------------|-------------------|----------------------|----------------------|

| ADC_G_CON                       | 04H       | W       | 00H            | adc_green_        | _contrast[7:0]      | ]                   | 1                   |                     | 1                 | 1                    | 1                    |

| ADC_B_BRI                       | 05H       | W       | 00H            | adc_blue_b        | rightness[7:0       | )]                  |                     |                     |                   |                      |                      |

| ADC_B_CON                       | 06H       | W       | 00H            | adc_blue_c        | ontrast[7:0]        |                     |                     |                     |                   |                      |                      |

| Fable 9         Mode determined | ection co | nfigura | ation register | rs (page 2); r    | ote 1               |                     |                     |                     |                   |                      |                      |

| REGISTER                        | ADR       | R/W     | RESET          | D7                | D6                  | D5                  | D4                  | D3                  | D2                | D1                   | D0                   |

| Mode detection: 0               | 0H to 0E  | Н       |                |                   |                     | •                   |                     | •                   |                   |                      | •                    |

| MD_CTRL                         | 00H       | W       | -000 0000      |                   | no_vsync_<br>int_en | clear_int           | int_lock            | delay_<br>vsync     | h_clocks_<br>accu | h_clocks_<br>cont    | md_on                |

| MD_INT_EN                       | 01H       | W       | 0000 0000      | jitter_int_en     | v_lines_<br>int_en  | v_clocks_<br>int_en | h_clocks_<br>int_en | no_hsync_<br>int_en | vsync_int_<br>en  | vsync_pol_<br>int_en | hsync_pol_<br>int_en |

| MD_POL                          | 02H       | R       | 0 0011         |                   |                     |                     | jitter_<br>detected | vsync_pol           | hsync_pol         | no_vsync             | no_hsync             |

| MD_V_LINE_HI                    | 03H       | R       | 000            |                   |                     |                     |                     |                     | v_lines[10:8      | 5]                   |                      |

| MD_V_LINE_LO                    | 04H       | R       | 00H            | v_lines[7:0]      |                     |                     | <u>.</u>            |                     |                   |                      |                      |

| MD_H_CLK_HI                     | 05H       | R       | 00H            | h_clocks[15:      | :8]                 |                     |                     |                     |                   |                      |                      |

| MD_H_CLK_LO                     | 06H       | R       | 00H            | h_clocks[7:0      | )]                  |                     |                     |                     |                   |                      |                      |

| MD_V_CLK_HI                     | 07H       | R       | 00H            | v_clocks[23:      | 16]                 |                     |                     |                     |                   |                      |                      |

| MD_V_CLK_MD                     | 08H       | R       | 00H            | v_clocks[15:      | 8]                  |                     |                     |                     |                   |                      |                      |

| MD_V_CLK_LO                     | 09H       | R       | 00H            | v_clocks[7:0      | ]                   |                     |                     |                     |                   |                      |                      |

| MD_INT_HI                       | 0AH       | R       | 00 0000        |                   |                     | vsync_int           | jitter_int          | vsync_pol_<br>int   | hsync_pol_<br>int | no_vsync_<br>int     | no_hsync_<br>int     |

| MD_INT_LO                       | 0BH       | R       | 000            |                   |                     |                     |                     |                     | v_lines_int       | h_clocks_<br>int     | v_clocks_<br>int     |

| MD_ACT_INT                      | 0CH       | R       | X000 0000      | delock_int        | reserved            | dvs_act_int         | dhs_act_int         | asog_act_<br>int    | acsvs_act_<br>int | avs_act_int          | ahs_act_int          |

| MD_SYNC_ACT                     | 0DH       | R       | 00 0000        |                   |                     | dvs_active          | dhs_active          | asog_<br>active     | acsvs_<br>active  | avs_active           | ahs_active           |

| MD_ACT_IEN                      | 0EH       | W       | 0000 0000      | delock_int_<br>en | reserved            | dvs_int_en          | dhs_int_en          | asog_int_<br>en     | acsvs_int_<br>en  | avs_int_en           | ahs_int_en           |

XGA analog input flat panel controller

Philips Semiconductors

Preliminary specification

SAA6713AH

Note

1. X = don't care.

-

| REGISTER         | ADR      | R/W   | RESET        | D7           | D6          | D5         | D4   | D3         | D2          | D1         | D0 |

|------------------|----------|-------|--------------|--------------|-------------|------------|------|------------|-------------|------------|----|

| Auto-adjustment: | 08H to 1 | 6H an | nd 40H to 4D | н            |             | ł          | - I  |            |             | - <b>I</b> | •  |

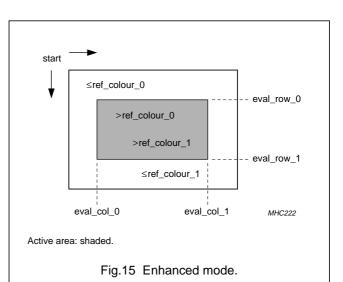

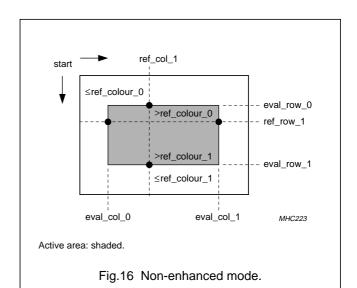

| AA_RC0_HI        | 08H      | W     | XXX          |              |             |            |      |            | ref_col_0[1 | 0:8]       |    |

| AA_RC0_LO        | 09H      | W     | XX           | ref_col_0[7  | :0]         | -1         | -1   |            | -           |            |    |

| AA_RR0_HI        | 0AH      | W     | XXXX         |              |             |            |      | ref_row_0[ | 11:8]       |            |    |

| AA_RR0_LO        | 0BH      | W     | XX           | ref_row_0[   | 7:0]        |            |      |            |             |            |    |

| AA_RC1_HI        | 0CH      | W     | XXX          |              |             |            |      |            | ref_col_1[1 | 0:8]       |    |

| AA_RC1_LO        | 0DH      | W     | XX           | ref_col_1[7  | [0]         | ·          |      | ·          |             |            |    |

| AA_RR1_HI        | 0EH      | W     | XXXX         |              |             |            |      | ref_row_1[ | 11:8]       |            |    |

| AA_RR1_LO        | 0FH      | W     | XX           | ref_row_1[   | 7:0]        | •          |      | ·          |             |            |    |

| AA_RCR0          | 10H      | W     | XX           | ref_colour_  | _0[23:16]   |            |      |            |             |            |    |

| AA_RCG0          | 11H      | W     | XX           | ref_colour_  | _0[15:8]    |            |      |            |             |            |    |

| AA_RCB0          | 12H      | W     | XX           | ref_colour_  | _0[7:0]     |            |      |            |             |            |    |

| AA_RCR1          | 13H      | W     | XX           | ref_colour_  | 1[23:16]    |            |      |            |             |            |    |

| AA_RCG1          | 14H      | W     | XX           | ref_colour_  | _1[15:8]    |            |      |            |             |            |    |

| AA_RCB1          | 15H      | W     | XX           | ref_colour_  | _1[7:0]     |            |      |            |             |            |    |

| AA_CTRL          | 16H      | W     | 01 1000      |              |             | aa_cycles[ | 1:0] | aa_submo   | de[1:0]     | aa_mode[1: | 0] |

| AA_EPR0          | 40H      | R     | 00H          | ref_pixel_re | ed_0[7:0]   |            |      |            |             |            |    |

| AA_EPG0          | 42H      | R     | 00H          | ref_pixel_g  | reen_0[7:0] |            |      |            |             |            |    |

| AA_EPB0          | 44H      | R     | 00H          | ref_pixel_b  | lue_0[7:0]  |            |      |            |             |            |    |

| AA_EPR1          | 41H      | R     | 00H          | ref_pixel_re | ed_1[7:0]   |            |      |            |             |            |    |

| AA_EPG1          | 43H      | R     | 00H          | ref_pixel_g  | reen_1[7:0] |            |      |            |             |            |    |

| AA_EPB1          | 45H      | R     | 00H          | ref_pixel_b  | lue_1[7:0]  |            |      |            |             |            |    |

| AA_ER0_HI        | 46H      | R     | 00H          | eval_row_0   | [15:8]      |            |      |            |             |            |    |

| AA_ER0_LO        | 47H      | R     | 00H          | eval_row_0   | )[7:0]      |            |      |            |             |            |    |

| AA_EC0_HI        | 48H      | R     | 00H          | eval_col_0   | [15:8]      |            |      |            |             |            |    |

| AA_EC0_LO        | 49H      | R     | 00H          | eval_col_0   | [7:0]       |            |      |            |             |            |    |

| AA_ER1_HI        | 4AH      | R     | 00H          | eval_row_1   | [15:8]      |            |      |            |             |            |    |

| AA_ER1_LO        | 4BH      | R     | 00H          | eval_row_1   | [7:0]       |            |      |            |             |            |    |

| AA_EC1_HI        | 4CH      | R     | 00H          | eval_col_1   | [15:8]      |            |      |            |             |            |    |

| AA_EC1_LO        | 4DH      | R     | 00H          | eval_col_1   | [7:0]       |            |      |            |             |            |    |

Philips Semiconductors

XGA analog input flat panel controller

\_

2002 Jul 16

Preliminary specification

# Note 2002 Jul 16

1. X = don't care.

#### Table 11 Input interface configuration registers (page 4)

| REGISTER             | ADR    | R/W | RESET     | D7                | D6               | D5                   | D4               | D3           | D2             | D1         | D0         |

|----------------------|--------|-----|-----------|-------------------|------------------|----------------------|------------------|--------------|----------------|------------|------------|

| Input interface: 00H | to 0FI | 4   |           |                   |                  |                      |                  |              |                |            |            |

| II_CTRL              | 00H    | W   | 0–00 0101 | test_out_<br>en   |                  | reverse_<br>field_id | interlace_<br>on | test_pic_on  | ext_select     | set to '0' | in_form_on |

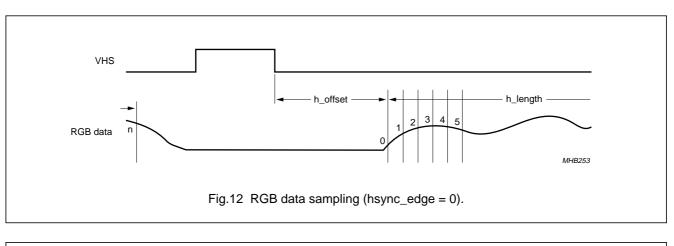

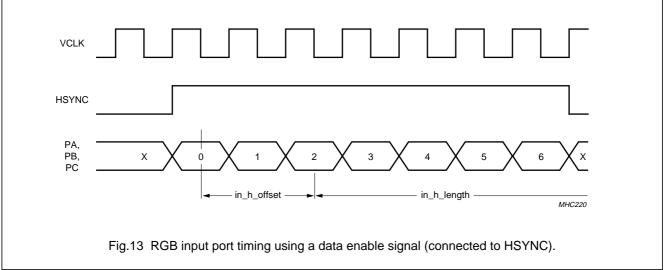

| II_SYNC_CTRL         | 01H    | W   | 110011    | sync_clk_<br>edge | ext_clk_<br>edge | reserved             |                  |              | hsync_<br>edge | vs_pol     | hs_pol     |

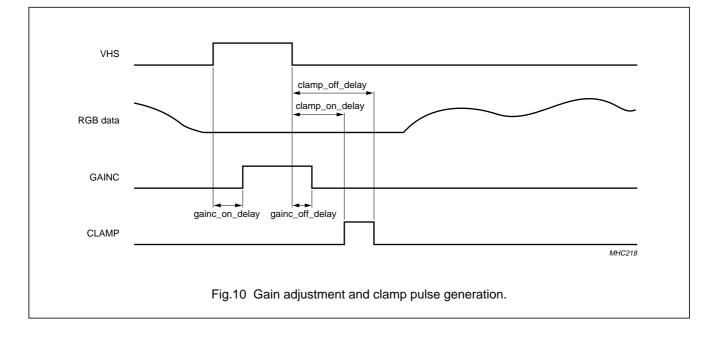

| II_ADC_CTRL          | 02H    | W   | 1001 1111 | delay_vs          | convert_2s       | reserved             |                  | gainc_en     | clamp_en       | gainc_pol  | clamp_pol  |

| II_CLAMP_ON          | 03H    | W   | 02H       | clamp_on_c        | lelay[7:0]       |                      |                  |              |                |            |            |

| II_CLAMP_OFF         | 04H    | W   | 05H       | clamp_off_c       | lelay[7:0]       |                      |                  |              |                |            |            |

| II_GAINC_ON          | 05H    | W   | 01H       | gainc_on_d        | elay[7:0]        |                      |                  |              |                |            |            |

| II_GAINC_OFF         | 06H    | W   | 01H       | gainc_off_d       | elay[7:0]        |                      |                  |              |                |            |            |

| II_HLEN_HI           | 07H    | W   | 0000      |                   |                  |                      |                  | in_h_length  | [11:8]         |            |            |

| II_HLEN_LO           | 08H    | W   | 3CH       | in_h_length       | [7:0]            |                      |                  |              |                |            |            |

| II_VLEN_HI           | 09H    | W   | 0000      |                   |                  |                      |                  | in_v_length  | [11:8]         |            |            |

| II_VLEN_LO           | 0AH    | W   | 28H       | in_v_length       | [7:0]            |                      |                  |              |                |            |            |

| II_HOFF_HI           | 0BH    | W   | 0000      |                   |                  |                      |                  | in_h_offset[ | 11:8]          |            |            |

| II_HOFF_LO           | 0CH    | W   | 00H       | in_h_offset[      | 7:0]             |                      |                  |              |                |            |            |

| II_VOFF_HI           | 0DH    | W   | 0000      |                   |                  |                      |                  | in_v_offset[ | 11:8]          |            |            |

| II_VOFF_LO           | 0EH    | W   | 00H       | in_v_offset[      | 7:0]             |                      |                  | ·            |                |            |            |

| II_HJIT              | 0FH    | W   | 05H       | hs_jitter_th[     | 7:0]             |                      |                  |              |                |            |            |

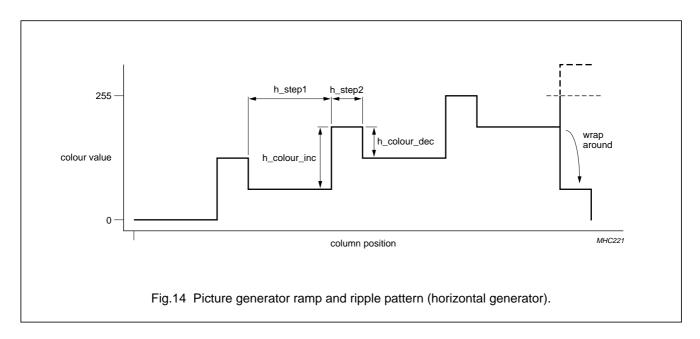

| Picture generator: 1 | 0H to  | 1CH |           |                   |                  |                      |                  |              |                |            |            |

| PG_CTRL              | 10H    | W   | 0010 0010 | invert            | white_<br>border | h_ramp_r             | h_ramp_g         | h_ramp_b     | v_ramp_r       | v_ramp_g   | v_ramp_b   |

| PG_HTOTAL_HI         | 11H    | W   | 0000      |                   |                  |                      |                  | h_length_to  | tal[11:8]      |            | •          |

| PG_HTOTAL_LO         | 12H    | W   | 51H       | h_length_to       | tal[7:0]         |                      |                  |              |                |            |            |

| PG_VTOTAL_HI         | 13H    | W   | 0000      |                   |                  |                      |                  | v_length_to  | tal[11:8]      |            |            |

| PG_VTOTAL_LO         | 14H    | W   | 35H       | v_length_to       | tal[7:0]         | •                    | •                | •            |                |            |            |

| PG_HSTEP1            | 15H    | W   | 01H       | h_step1[7:0       | ]                |                      |                  |              |                |            |            |

| PG_HINC1             | 16H    | W   | 02H       | h_colour_in       | c1[7:0]          |                      |                  |              |                |            |            |

| PG_HSTEP2            | 17H    | W   | 00H       | h_step2[7:0       | ]                |                      |                  |              |                |            |            |

# Philips Semiconductors

XGA analog input flat panel controller

Preliminary specification

SAA6713AH

19

\_

\_

| REGISTER  | ADR | R/W | RESET | D7                 | D6                 | D5 | D4 | D3 | D2 | D1 | D0 |

|-----------|-----|-----|-------|--------------------|--------------------|----|----|----|----|----|----|

| PG_HINC2  | 18H | W   | FFH   | h_colour_ind       | 2[7:0]             | •  | •  | •  | •  | •  | •  |

| PG_VSTEP1 | 19H | W   | 14H   | v_step1[7:0]       |                    |    |    |    |    |    |    |

| PG_VINC1  | 1AH | W   | FFH   | v_colour_ind       | v_colour_inc1[7:0] |    |    |    |    |    |    |

| PG_VSTEP2 | 1BH | W   | 01H   | v_step2[7:0]       |                    |    |    |    |    |    |    |

| PG_VINC2  | 1CH | W   | FFH   | v_colour_inc2[7:0] |                    |    |    |    |    |    |    |

#### Table 12 Colour processing configuration registers (page 5)

| REGISTER          | ADR      | R/W | RESET | D7             | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|-------------------|----------|-----|-------|----------------|----|----|----|----|----|----|----|

| Colour processing | : 00H to | 0BH | 1     | ΥΥΥΥ           |    | -1 |    | 1  | 4  |    | •  |

| CP_GAIN_Y         | 00H      | W   | 80H   | gain_y[7:0]    |    |    |    |    |    |    |    |

| CP_GAIN_CB        | 01H      | W   | 80H   | gain_cb[7:0]   |    |    |    |    |    |    |    |

| CP_GAIN_CR        | 02H      | W   | 80H   | gain_cr[7:0]   |    |    |    |    |    |    |    |

| CP_OFFS_Y         | 03H      | W   | 00H   | offset_y[7:0]  |    |    |    |    |    |    |    |

| CP_OFFS_CB        | 04H      | W   | 00H   | offset_cb[7:0] | ]  |    |    |    |    |    |    |

| CP_OFFS_CR        | 05H      | W   | 00H   | offset_cr[7:0] |    |    |    |    |    |    |    |

| CP_GAIN_R         | 06H      | W   | 80H   | gain_r[7:0]    |    |    |    |    |    |    |    |

| CP_GAIN_G         | 07H      | W   | 80H   | gain_g[7:0]    |    |    |    |    |    |    |    |

| CP_GAIN_B         | 08H      | W   | 80H   | gain_b[7:0]    |    |    |    |    |    |    |    |

| CP_OFFS_R         | 09H      | W   | 00H   | offset_r[7:0]  |    |    |    |    |    |    |    |

| CP_OFFS_G         | 0AH      | W   | 00H   | offset_g[7:0]  |    |    |    |    |    |    |    |

| CP_OFFS_B         | 0BH      | W   | 00H   | offset_b[7:0]  |    |    |    |    |    |    |    |

#### Table 13 Decoupling FIFO configuration registers (page 6)

| REGISTER            | ADR   | R/W | RESET | D7            | D6     | D5 | D4 | D3 | D2 | D1        | D0       |

|---------------------|-------|-----|-------|---------------|--------|----|----|----|----|-----------|----------|

| Decoupling FIFO: 00 | H and | 01H |       | -             |        |    |    |    |    |           |          |

| DF_THLD             | 00H   | W   | 01H   | fifo_threshol | d[7:0] |    |    |    |    |           |          |

| DF_CTRL             | 01H   | W   | 10    |               |        |    |    |    |    | line_lock | reserved |

# XGA analog input flat panel controller

| 2002 |

|------|

| Jul  |

| 16   |

\_

#### Table 14 Scaler configuration registers (page 7); note 1

| REGISTER           | ADR              | R/W    | RESET        | D7            | D6                   | D5         | D4         | D3 | D2        | D1           | D0         |

|--------------------|------------------|--------|--------------|---------------|----------------------|------------|------------|----|-----------|--------------|------------|

| Upscaler: 00H to 0 | 9H, 0DH          | I, OFH | l, 11H and 1 | 4H to 18H     |                      | 1          |            | !  |           | Į            | -          |

| USC_CTRL           | 00H              | W      | 1010 1101    | filter_type[1 | :0]                  | 1          | 0          | 0  | 0         | usc_flip_h   | usc_en     |

| USC_LUT_ADR        | 01H              | W      | 1100 0000    | v_lut_sel     | h_lut_sel            | lut_addr[5 | :0]        |    |           |              | •          |

| USC_LUT_DATA       | 02H              | W      | XX           | lut_data[7:0  | ]                    | •          |            |    |           |              |            |

| USC_H_INC_HI       | 03H              | W      | 0000         |               | h_scale_incr[11:8]   |            |            |    |           |              |            |

| USC_H_INC_LO       | 04H              | W      | 55H          | h_scale_inc   | r[7:0]               | •          | •          | •  |           |              |            |

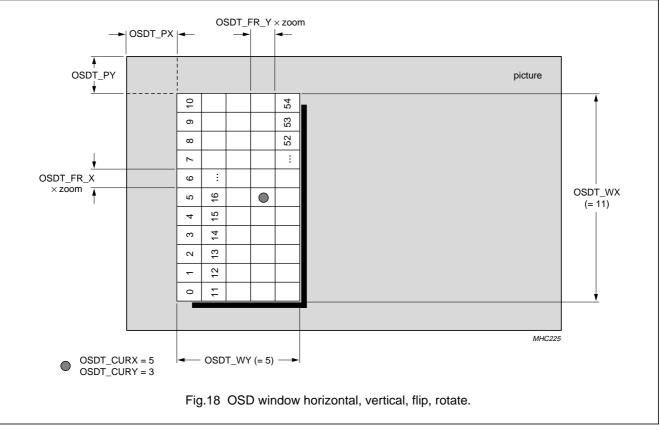

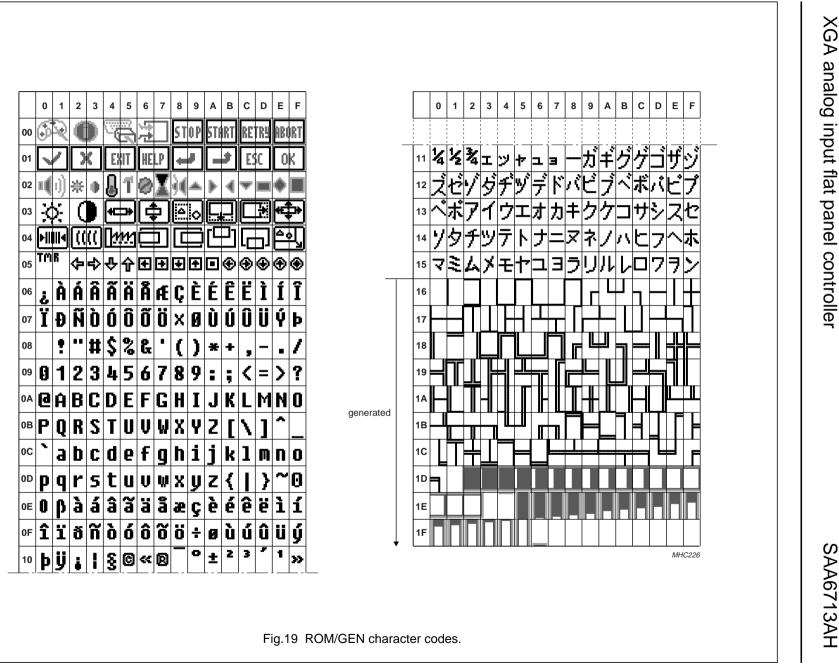

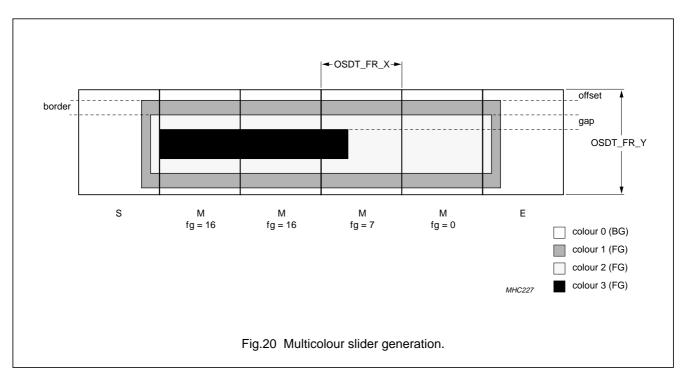

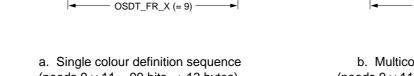

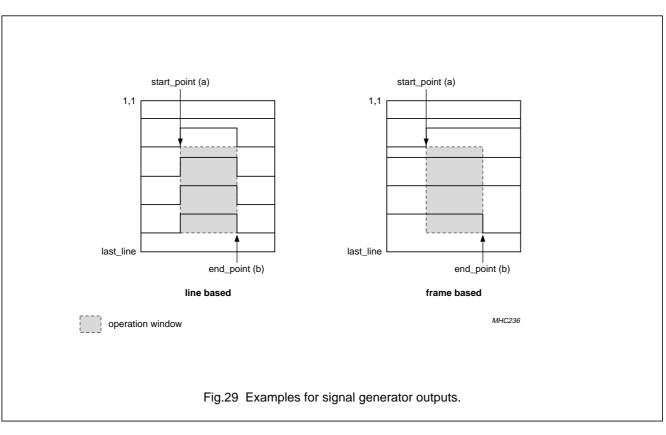

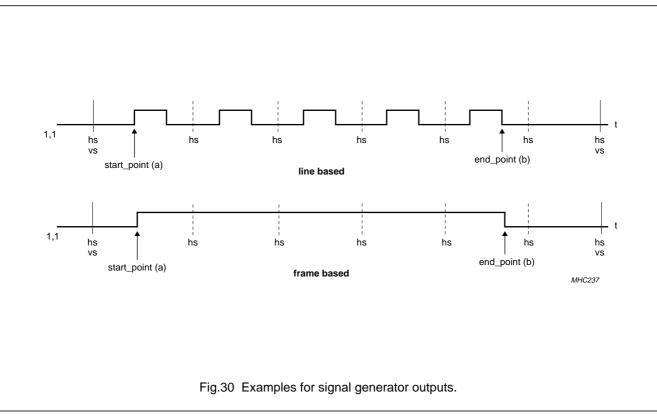

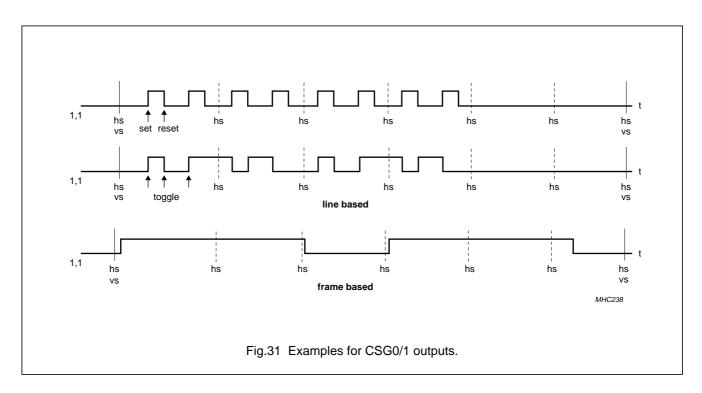

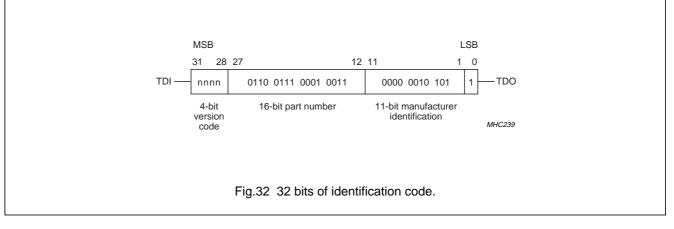

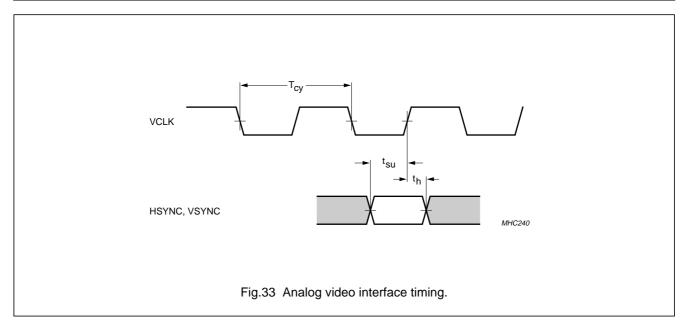

| USC_H_CORR         | 05H              | W      | -010 0010    |               | h_scale_co           | rr[6:0]    |            |    |           |              |            |