### INTEGRATED CIRCUITS

# DATA SHEET

# **SAA5252**

Line twenty-one acquisition and display (LITOD)

Product specification Supersedes data of March 1995 File under Integrated Circuits, IC02 1996 Jul 18

### Line twenty-one acquisition and display (LITOD)

**SAA5252**

### **FEATURES**

- Complete 'stand-alone' Line 21 decoder in one package

- On-chip display RAM allowing full page Text mode

- · Enhanced character display modes

- · Full colour captions

- RGB interface for standard colour decoder ICs

- · Automatic handling of Field 2 data

- Automatic selection of (1H, 1V), (2H, 1V) or (2H, 2V) scan modes

- Onboard OSD facility using Character generator

- RGB inputs to support existing OSD ICs

- I<sup>2</sup>C-bus or 'stand-alone' pin control

- Automatic data-ready signal generation on data acquisition

- Can decode signals recorded on standard VHS and S-VHS tape.

### **GENERAL DESCRIPTION**

The SAA5252 (LITOD) is a single-chip CMOS device, which will acquire, decode and display Line 21 Closed Captioning data from a 525-line composite video signal. Operation as an On-Screen Display (OSD) device is also possible. Normal and line progressive scan modes are supported.

### **QUICK REFERENCE DATA**

| SYMBOL           | PARAMETER                     | MIN. | TYP. | MAX. | UNIT |

|------------------|-------------------------------|------|------|------|------|

| V <sub>DD</sub>  | supply voltage                | 4.5  | 5.0  | 5.5  | ٧    |

| I <sub>DD</sub>  | supply current                | _    | 30   | _    | mA   |

| V <sub>syn</sub> | CVBS sync amplitude           | 0.1  | 0.3  | 0.6  | V    |

| $V_{vid}$        | CVBS video amplitude          | 0.7  | 1.0  | 1.4  | V    |

| T <sub>amb</sub> | operating ambient temperature | -20  | _    | +70  | °C   |

| T <sub>stg</sub> | storage temperature           | -55  | _    | +125 | °C   |

### ORDERING INFORMATION

| TYPE     | PACKAGE |                                                            |          |  |  |  |  |

|----------|---------|------------------------------------------------------------|----------|--|--|--|--|

| NUMBER   | NAME    | DESCRIPTION                                                | VERSION  |  |  |  |  |

| SAA5252P | DIP24   | plastic dual in-line package; 24 leads (600 mil)           | SOT101-1 |  |  |  |  |

| SAA5252T | SO24    | plastic small outline package; 24 leads; body width 7.5 mm | SOT137-1 |  |  |  |  |

## Line twenty-one acquisition and display (LITOD)

SAA5252

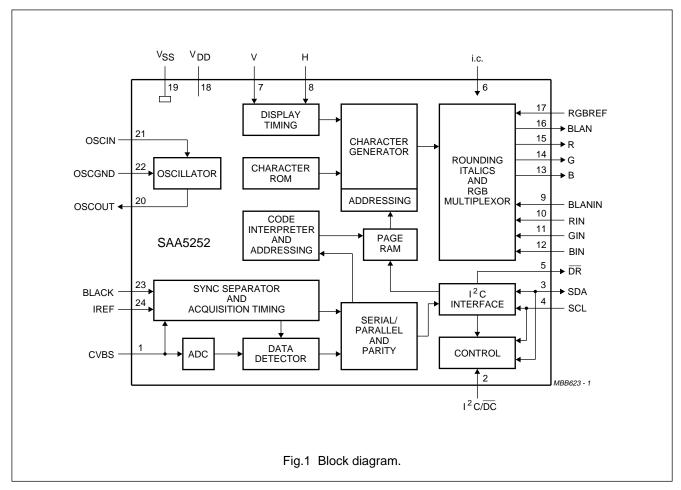

### **BLOCK DIAGRAM**

# Line twenty-one acquisition and display (LITOD)

SAA5252

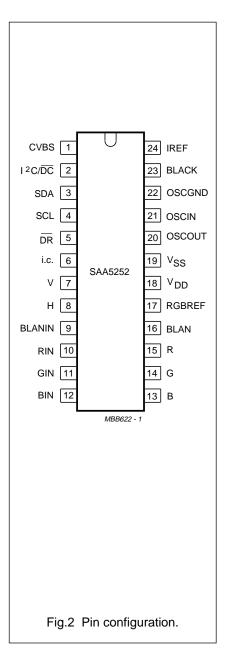

### **PINNING**

| SYMBOL              | PIN | DESCRIPTION                                                                               |

|---------------------|-----|-------------------------------------------------------------------------------------------|

| CVBS                | 1   | composite video input; signal should be connected via a 100 nF capacitor                  |

| I <sup>2</sup> C/DC | 2   | input selects I <sup>2</sup> C or Direct Control                                          |

| SDA                 | 3   | serial data port for I <sup>2</sup> C-bus or mode select input for direct control         |

| SCL                 | 4   | serial clock input for I <sup>2</sup> C-bus or mode select input for direct control       |

| DR                  | 5   | data-ready signal to microcontroller (active-LOW) or mode select input for direct control |

| i.c.                | 6   | internally connected; connect to V <sub>SS</sub> for normal operation                     |

| V                   | 7   | vertical reference input for display timing                                               |

| Н                   | 8   | horizontal reference input for display timing                                             |

| BLANIN              | 9   | video blanking input from external OSD device                                             |

| RIN                 | 10  | RED video input from external OSD device                                                  |

| GIN                 | 11  | GREEN video input from external OSD device                                                |

| BIN                 | 12  | BLUE video input from external OSD device                                                 |

| В                   | 13  | BLUE video output                                                                         |

| G                   | 14  | GREEN video output                                                                        |

| R                   | 15  | RED video output                                                                          |

| BLAN                | 16  | video blanking output                                                                     |

| RGBREF              | 17  | input voltage defining output HIGH level for RGB pins for closed captioning output        |

| V <sub>DD</sub>     | 18  | +5 V supply                                                                               |

| V <sub>SS</sub>     | 19  | 0 V ground                                                                                |

| OSCOUT              | 20  | oscillator output                                                                         |

| OSCIN               | 21  | oscillator input                                                                          |

| OSCGND              | 22  | oscillator ground                                                                         |

| BLACK               | 23  | video black level storage input; connected to V <sub>SS</sub> via 100 nF capacitor        |

| IREF                | 24  | reference current input; connected to $V_{SS}$ via 27 $k\Omega$ resistor                  |

### Line twenty-one acquisition and display (LITOD)

SAA5252

### LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 134).

| SYMBOL            | PARAMETER                                     | CONDITIONS | MIN.       | MAX.                  | UNIT |

|-------------------|-----------------------------------------------|------------|------------|-----------------------|------|

| $V_{DD}$          | supply voltage (all supplies)                 |            | -0.3       | +6.5                  | V    |

| $V_{Imax}$        | maximum input voltage (any input)             | note 1     | -0.3       | $V_{DD} + 0.5$        | V    |

| V <sub>Omax</sub> | maximum output voltage (any output)           | note 1     | _          | V <sub>DD</sub> + 0.5 | V    |

| $V_{dif}$         | difference between V <sub>SS</sub> and OSCGND |            | _          | ±0.25                 | V    |

| I <sub>IOK</sub>  | DC input or output diode current              |            | _          | ±20                   | mA   |

| I <sub>Omax</sub> | maximum output current (each output)          |            | _          | ±10                   | mA   |

| T <sub>amb</sub>  | operating ambient temperature                 |            | -20        | +70                   | °C   |

| T <sub>stg</sub>  | storage temperature                           |            | <b>-55</b> | +125                  | °C   |

| V <sub>es</sub>   | electrostatic handling                        |            |            |                       |      |

|                   | human body model                              | note 2     | -2000      | +2000                 | V    |

|                   | machine model                                 | note 3     | -200       | +200                  | V    |

### Notes

- 1. This maximum value has an absolute maximum of 6.5 V independent of V<sub>DD</sub>.

- 2. The human body model ESD simulation is equivalent to discharging a 100 pF capacitor via a 1.5 kΩ resistor, which produces a single discharge transient. Reference "Philips Semiconductors Test Method UZW-BO/FQ-A302 (similar to MIL-STD 883C method 3015.7)".

- The machine model ESD simulation is equivalent to discharging a 200 pF capacitor via a resistor and series inductor with effective dynamic values of 25 Ω and 2.5 μH, which produces a damped oscillating discharge. Reference "Philips Semiconductors Test Method UZW-BO/FQ-B302 (similar to EIAJ IC-121 Test Method 20 condition C)".

### Quality

This device will meet the requirements of the "Philips Semiconductors General Quality Specification UZW-BO/FQ-0601" in accordance with "Quality Reference Handbook (order number 9397 750 00192)". This details the acceptance criteria for all Q & R tests applied to the product.

# Line twenty-one acquisition and display (LITOD)

SAA5252

### **CHARACTERISTICS**

$V_{DD}$  = 5 to 5.5 V;  $V_{SS}$  = 0 V;  $T_{amb}$  = –20 to +70  $^{\circ}C;$  unless otherwise specified.

| SYMBOL                | PARAMETER                                       | CONDITIONS            | MIN. | TYP.           | MAX.                  | UNIT |

|-----------------------|-------------------------------------------------|-----------------------|------|----------------|-----------------------|------|

| Supplies              | 1                                               |                       |      |                | -                     | •    |

| $V_{DD}$              | supply voltage                                  |                       | 4.5  | 5.0            | 5.5                   | V    |

| I <sub>DDtot</sub>    | total supply current                            |                       | _    | 30             | _                     | mA   |

| Inputs                |                                                 |                       | ·    |                |                       | 1    |

| CVBS (PIN             | 1)                                              |                       |      |                |                       |      |

| V <sub>syn</sub>      | sync voltage amplitude                          |                       | 0.1  | 0.3            | 0.6                   | V    |

| $V_{\text{vid}(p-p)}$ | video voltage amplitude<br>(peak-to-peak value) |                       | 0.7  | 1.0            | 1.4                   | V    |

| V <sub>dat</sub>      | caption data voltage amplitude                  |                       | 0.25 | 0.35           | 0.49                  | V    |

| Z <sub>source</sub>   | source impedance                                |                       | _    | _              | 250                   | Ω    |

| V <sub>I</sub>        | input switching voltage level of sync separator |                       | 1.7  | 2.0            | 2.3                   | V    |

| Z <sub>I</sub>        | input impedance                                 |                       | 2.5  | 5              | _                     | kΩ   |

| C <sub>I</sub>        | input capacitance                               |                       | _    | _              | 10                    | pF   |

| IREF (PIN 2           | 24)                                             |                       |      | '              |                       | •    |

| R <sub>24</sub>       | resistor to ground                              |                       | _    | 27             | _                     | kΩ   |

| V <sub>24</sub>       | voltage on pin 24                               |                       | _    | $1/_{2}V_{DD}$ | _                     | V    |

| H (PIN 8)             |                                                 |                       |      | '              | '                     |      |

| V <sub>IL</sub>       | LOW level input voltage                         |                       | -0.3 | _              | +0.8                  | V    |

| V <sub>IH</sub>       | HIGH level input voltage                        |                       | 2.0  | _              | V <sub>DD</sub> + 0.5 | V    |

| ILI                   | input leakage current                           | $V_I = 0$ to $V_{DD}$ | -10  | _              | +10                   | μА   |

| I <sub>lmax</sub>     | maximum input current                           |                       | -1   | _              | +1                    | mA   |

| Cı                    | input capacitance                               |                       | _    | _              | 10                    | pF   |

| t <sub>r</sub>        | pulse rise time                                 |                       | _    | _              | 5                     | μs   |

| t <sub>f</sub>        | pulse fall time                                 |                       | _    | _              | 5                     | μs   |

| $t_W$                 | pulse width                                     |                       |      |                |                       |      |

|                       | scan mode 1H                                    |                       | 1    | 12             | 63                    | μs   |

|                       | scan mode 2H                                    |                       | 1    | 6              | 31                    | μs   |

| V (PIN 7)             |                                                 |                       |      |                |                       |      |

| V <sub>IL</sub>       | LOW level input voltage                         |                       | -0.3 | _              | +0.8                  | V    |

| V <sub>IH</sub>       | HIGH level input voltage                        |                       | 2.0  | _              | V <sub>DD</sub> + 0.5 | V    |

| ILI                   | input leakage current                           | $V_I = 0$ to $V_{DD}$ | -10  | _              | +10                   | μΑ   |

| I <sub>lmax</sub>     | maximum input current                           |                       | -1   | _              | +1                    | mA   |

| Cı                    | input capacitance                               |                       | _    | _              | 10                    | pF   |

| t <sub>r</sub>        | pulse rise time                                 |                       | _    | _              | 5                     | ns   |

| t <sub>f</sub>        | pulse fall time                                 |                       | _    | _              | 5                     | ns   |

| t <sub>W</sub>        | pulse width                                     |                       | 1    | _              | _                     | μs   |

# Line twenty-one acquisition and display (LITOD)

SAA5252

| SYMBOL                   | PARAMETER                    | CONDITIONS            | MIN.  | TYP. | MAX.                  | UNIT |

|--------------------------|------------------------------|-----------------------|-------|------|-----------------------|------|

| RGBREF (F                | PIN, 17)                     |                       | -     | '    |                       | •    |

| V <sub>I</sub>           | input voltage                |                       | -0.3  |      | V <sub>DD</sub>       | V    |

| I <sub>LI</sub>          | input leakage current        | $V_I = 0$ to $V_{DD}$ | -10   | _    | +10                   | μΑ   |

| R, G AND B               | (PINS 15, 14 AND 13); note 1 |                       |       |      |                       |      |

| V <sub>IL</sub>          | LOW level input voltage      |                       | -0.3  |      | 0.8                   | V    |

| V <sub>IH</sub>          | HIGH level input voltage     |                       | 2.0   |      | V <sub>DD</sub> + 0.5 | V    |

| Z <sub>I</sub>           | input impedance              |                       | 2.5   | 5.0  |                       | kΩ   |

| BLANIN (PI               | N 9)                         |                       |       |      |                       | 1    |

| V <sub>IL</sub>          | LOW level input voltage      |                       | -0.3  |      | 0.8                   | V    |

| V <sub>IH</sub>          | HIGH level input voltage     |                       | 2.0   | _    | V <sub>DD</sub> + 0.5 | V    |

| ILI                      | input leakage current        | $V_I = 0$ to $V_{DD}$ | -10   |      | +10                   | μΑ   |

| t <sub>r</sub>           | input rise time              | between 10% and 90%   | _     | _    | 80                    | ns   |

| t <sub>f</sub>           | input fall time              | between 90% and 10%   | _     |      | 80                    | ns   |

| I <sup>2</sup> C/DC (PIN | · ·                          | I.                    |       |      | -                     | 1    |

| V <sub>IL</sub>          | LOW level input voltage      |                       | 0     |      | 0.8                   | V    |

| V <sub>IH</sub>          | HIGH level input voltage     |                       | 2.0   |      | V <sub>DD</sub>       | V    |

| ILI                      | input leakage current        | $V_I = 0$ to $V_{DD}$ | _10   | _    | +10                   | μΑ   |

| SCL (PIN 4)              | -                            | 1 2 2 55              |       |      |                       | 1 -  |

| V <sub>IL</sub>          | LOW level input voltage      |                       | -0.3  | _    | 1.5                   | V    |

| V <sub>IH</sub>          | HIGH level input voltage     |                       | 3.0   | _    | V <sub>DD</sub> + 0.5 | V    |

| f <sub>clk</sub>         | clock frequency              |                       | 0     | _    | 100                   | kHz  |

| t <sub>r</sub>           | input rise time              | between 10% and 90%   | _     | _    | 2                     | μs   |

| t <sub>f</sub>           | input fall time              | between 90% and 10%   | _     | _    | 2                     | μs   |

| I <sub>LI</sub>          | input leakage current        | $V_I = 0$ to $V_{DD}$ | -10   | _    | +10                   | μΑ   |

| Cı                       | input capacitance            |                       | _     | _    | 10                    | pF   |

| Inputs/out               | outs                         | 1                     | · !   | !    |                       | •    |

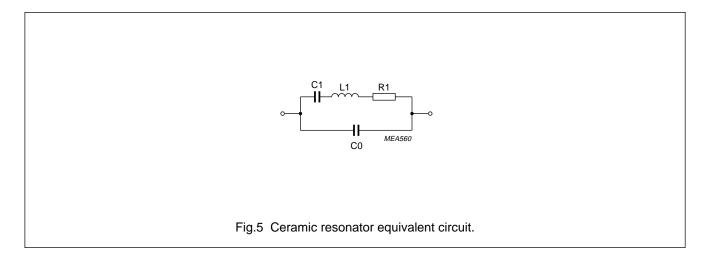

|                          | SONATOR (PINS 20, 21 AND 22) | ): see Fig.5          |       |      |                       |      |

| f <sub>osc</sub>         | oscillator frequency         | ,, eee : .g.e         | 11.82 | 12   | 12.18                 | MHz  |

| C0                       | parallel capacitance         |                       | _     | 5.35 | _                     | pF   |

| C1                       | series capacitance           |                       | _     | 37.4 | _                     | pF   |

| L1                       | series inductance            |                       | _     | 35.5 | _                     | μH   |

| R1                       | series resistance            |                       | _     | 6    | 25                    | Ω    |

| BLACK (PIN               | 1                            | 1                     |       |      |                       |      |

| C <sub>black</sub>       | storage capacitor to ground  |                       | 1_    | 100  |                       | nF   |

| V <sub>black</sub>       | black level voltage for      |                       | 1.8   | 2.15 | 2.5                   | V    |

| DIACK                    | nominal sync amplitude       |                       |       |      |                       | -    |

| I <sub>LI</sub>          | input leakage current        | $V_I = 0$ to $V_{DD}$ | -10   | _    | +10                   | μΑ   |

# Line twenty-one acquisition and display (LITOD)

SAA5252

| SYMBOL             | PARAMETER                                            | CONDITIONS                                    | MIN.                  | TYP.            | MAX.                  | UNIT |

|--------------------|------------------------------------------------------|-----------------------------------------------|-----------------------|-----------------|-----------------------|------|

| SDA (PIN 3;        | OPEN DRAIN)                                          | ,                                             | !                     |                 | !                     | Į.   |

| V <sub>IL</sub>    | LOW level input voltage                              |                                               | -0.3                  | _               | +1.5                  | V    |

| V <sub>IH</sub>    | HIGH level input voltage                             |                                               | 3.0                   | _               | V <sub>DD</sub> + 0.5 | V    |

| I <sub>LI</sub>    | input leakage current                                | $V_I = 0$ to $V_{DD}$                         | -10                   | _               | +10                   | μΑ   |

| Cı                 | input capacitance                                    |                                               | _                     | _               | 10                    | pF   |

| t <sub>r</sub>     | input rise time                                      | between 10% and 90%                           | _                     | _               | 2                     | μs   |

| t <sub>f</sub>     | input fall time                                      | between 90% and 10%                           | _                     | _               | 2                     | μs   |

| V <sub>OL</sub>    | LOW level output voltage                             | I <sub>OL</sub> = 3 mA                        | 0                     | _               | 0.5                   | V    |

| t <sub>f</sub>     | output fall time                                     | between 3 V and 1 V                           | _                     | _               | 200                   | ns   |

| C <sub>L</sub>     | load capacitance                                     |                                               | _                     | _               | 400                   | pF   |

| <br>DR (PIN 5; C   | DPEN DRAIN)                                          |                                               |                       |                 |                       |      |

| V <sub>IL</sub>    | LOW level input voltage                              |                                               | -0.3                  | _               | +1.5                  | V    |

| V <sub>IH</sub>    | HIGH level input voltage                             |                                               | 3.0                   | _               | V <sub>DD</sub> + 0.5 | V    |

| l <sub>LI</sub>    | input leakage current                                | $V_I = 0$ to $V_{DD}$                         | -10                   | _               | +10                   | μΑ   |

| V <sub>OL</sub>    | LOW level output voltage                             | I <sub>OL</sub> = 1.6 mA                      | 0                     | _               | 0.4                   | V    |

| t <sub>f</sub>     | output fall time                                     | between 4 V and 1 V with 3.3 $k\Omega$ to 5 V | _                     | _               | 50                    | ns   |

| C <sub>L</sub>     | load capacitance                                     |                                               | _                     | -               | 100                   | pF   |

| Outputs            |                                                      | •                                             |                       | <u>'</u>        |                       |      |

| R, G AND B         | (PINS 15, 14 AND 13; CAPTION                         | MODE)                                         |                       |                 |                       |      |

| V <sub>OL</sub>    | LOW level output voltage                             | I <sub>OL</sub> = +2 mA                       | 0                     | _               | 0.2                   | V    |

| V <sub>OH</sub>    | HIGH level output voltage                            | $I_{OH} = -2 \text{ mA}$                      | V <sub>17</sub> – 0.3 | V <sub>17</sub> | V <sub>17</sub> + 0.4 | V    |

| Z <sub>O</sub>     | output impedance                                     |                                               | _                     | _               | 200                   | Ω    |

| CL                 | load capacitance                                     |                                               | _                     | _               | 50                    | pF   |

| r                  | output rise time                                     | between 10% and 90%                           | _                     | _               | 10                    | ns   |

| t <sub>f</sub>     | output fall time                                     | between 90% and 10%                           | _                     | _               | 10                    | ns   |

| BLAN (PIN 1        | 16)                                                  | 1                                             | 1                     | <u>'</u>        | <u>'</u>              | 1    |

| V <sub>OL</sub>    | LOW level output voltage                             | I <sub>OL</sub> = +2 mA                       | 0                     | _               | 0.4                   | V    |

| V <sub>OH</sub>    | HIGH level output voltage                            | $I_{OH} = -2 \text{ mA}$                      | 1.1                   | _               | 2.8                   | V    |

| C <sub>L</sub>     | load capacitance                                     |                                               | _                     | _               | 50                    | pF   |

| <br>t <sub>r</sub> | output rise time                                     | between 10% and 90%                           | _                     | _               | 10                    | ns   |

| t <sub>f</sub>     | output fall time                                     | between 90% and 10%                           | _                     | _               | 10                    | ns   |

| tskew              | skew delay time between<br>display and R, G, B, BLAN |                                               | _                     | _               | 10                    | ns   |

# Line twenty-one acquisition and display (LITOD)

SAA5252

| SYMBOL                  | PARAMETER                                                      | CONDITIONS          | MIN. | TYP. | MAX. | UNIT |

|-------------------------|----------------------------------------------------------------|---------------------|------|------|------|------|

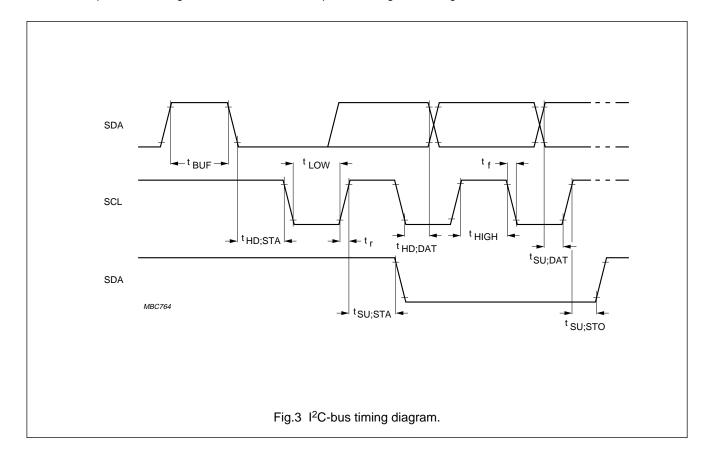

| I <sup>2</sup> C timing | (see Fig.3)                                                    |                     | -    | •    | •    | •    |

| t <sub>LOW</sub>        | clock LOW time                                                 |                     | 4    | _    | _    | μs   |

| t <sub>HIGH</sub>       | clock HIGH time                                                |                     | 4    | _    | _    | μs   |

| t <sub>SU;DAT</sub>     | data set-up time                                               |                     | 250  | _    | _    | ns   |

| t <sub>HD;DAT</sub>     | data hold time                                                 |                     | 170  | _    | _    | ns   |

| t <sub>SU;STO</sub>     | set-up time from clock<br>HIGH-to-STOP                         |                     | 4    | _    | _    | μs   |

| t <sub>BUF</sub>        | START set-up time following a STOP                             |                     | 4    | _    | _    | μs   |

| t <sub>HD;STA</sub>     | START hold time                                                |                     | 4    | _    | _    | μs   |

| t <sub>SU;STA</sub>     | START set-up time<br>following clock<br>LOW-to-HIGH transition |                     | 4    | _    | _    | μs   |

| t <sub>r</sub>          | output rise time                                               | between 10% and 90% | _    | _    | 10   | ns   |

| t <sub>f</sub>          | output fall time                                               | between 90% and 10% | _    | _    | 10   | ns   |

### Note

1. These inputs are analog,  $V_{\text{IL}}$  and  $V_{\text{IH}}$  values are quoted as a guide for digital RGB users.

## Line twenty-one acquisition and display (LITOD)

SAA5252

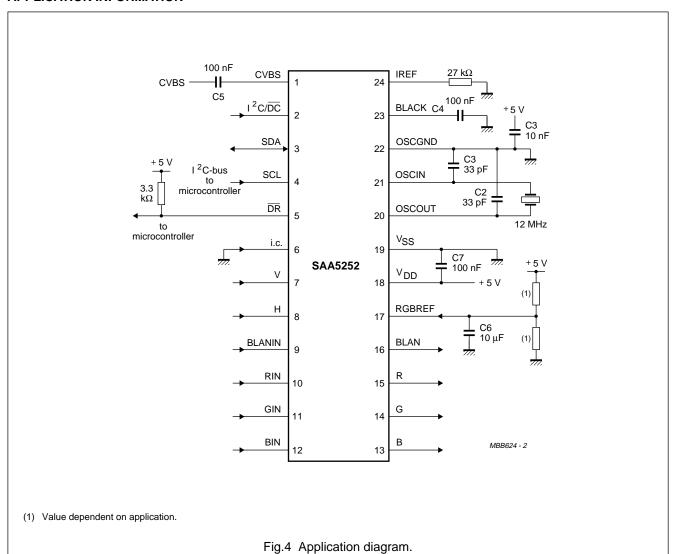

### **APPLICATION INFORMATION**

### Line twenty-one acquisition and display (LITOD)

SAA5252

### **DISPLAY GENERATOR**

### **General description**

The displayed characters are defined on a 5-by-12 matrix within a 7-by-13 window, allowing one blank pixel either side of the character and a blank pixel row above. There are a number of display options available controlled by Register 1, or external pins in 'stand-alone' mode.

The three display modes are video, text and caption, the device is powered up in the video mode.

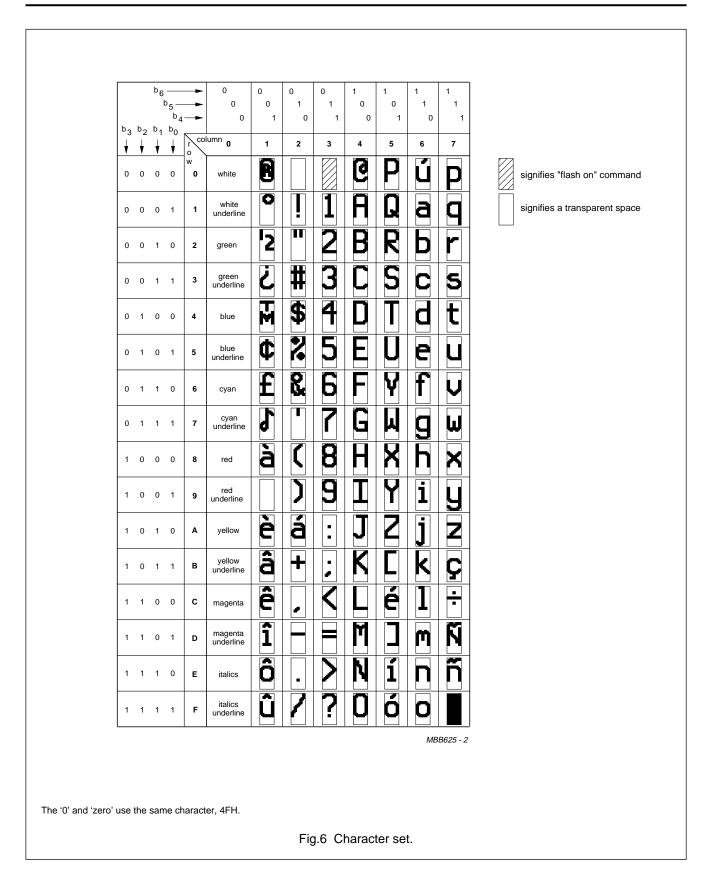

The display generator reads the Pre-amble Address Code (PAC) then the data associated with that row. Each character is then rounded after which it can be italicized and/or underlined, depending on the PAC or mid-row codes, before being passed on to the output circuitry. Figure 6 shows the character set.

### Display of external On-Screen Display (OSD) facilities

The R, G, B and BLAN outputs of the display have the capability to be put in a 3-state mode allowing other OSD devices to take control of the television R, G, B and BLAN signals.

When the BLANIN is held HIGH then the R, G, B and BLAN outputs from display are disabled and the R, G, B and BLAN signals come directly from the RGBIN and BLANIN inputs. This will allow On-Screen Display to be placed on top of the captioning without any corruption, leaving the captions intact when the On-Screen Display is switched off (BLANIN goes LOW). In this form of operation the RGBIN and RGBOUT pins can be considered transparent; BLANIN goes through the normal output buffer to BLAN.

Table 1 Register map (WRITE)

| REGISTER | D7    | D6                   | D5              | D4           | D3   | D2   | D1   | D0   |

|----------|-------|----------------------|-----------------|--------------|------|------|------|------|

| 00       | DF1/2 | RGB, BLAN<br>+ve/-ve | H<br>+ve/–ve    | V<br>+ve/–ve | H3   | H2   | H1   | H0   |

| 01       | CLEAR | CH 2/1               | NARROW/<br>WIDE | ACQ OFF      | EN1  | EN0  | M1   | МО   |

| 02       | _     | _                    | _               | _            | ROW3 | ROW2 | ROW1 | ROW0 |

| 03       | _     | _                    | _               | COL4         | COL3 | COL2 | COL1 | COL0 |

| 04       | _     | OSD6                 | OSD5            | OSD4         | OSD3 | OSD2 | OSD1 | OSD0 |

Table 2 Register map (READ)

| REGISTER | D7     | D6    | D5    | D4    | D3    | D2    | D1                 | D0            |

|----------|--------|-------|-------|-------|-------|-------|--------------------|---------------|

| 80       | POR    | 0     | 0     | 0     | F1/F2 | EDS   | PARITY<br>SHUTDOWN | DATA<br>READY |

| 81       | PARITY | DATA  | DATA  | DATA  | DATA  | DATA  | DATA               | DATA          |

|          | ERROR  | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2              | BIT 1         |

| 82       | PARITY | DATA  | DATA  | DATA  | DATA  | DATA  | DATA               | DATA          |

|          | ERROR  | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2              | BIT 1         |

1996 Jul 18

### Line twenty-one acquisition and display (LITOD)

SAA5252

### Line twenty-one acquisition and display (LITOD)

SAA5252

### I<sup>2</sup>C INTERFACE

### **Description of WRITE registers**

The write subaddresses auto increment from 0 through to 4 at which point they stay until a new write subaddress is sent. Registers are set to all logic 0 at power-up.

Table 3 Register 0 WRITE (Control Byte 1)

| BIT      | DESCRIPTION                                                                                                    |

|----------|----------------------------------------------------------------------------------------------------------------|

| D0 to D3 | H0 to H3 set the offset position from the start of the horizontal sync pulse, set to a nominal value on reset. |

| D4       | Vertical sync pulse expected to be negative going logic 0 or positive-going logic 1.                           |

| D5       | Horizontal sync pulse expected to be negative going logic 0 or positive-going logic 1.                         |

| D6       | Video outputs will be positive going logic 0 or negative-going logic 1.                                        |

| D7       | Data field select. When set to logic 0 Field 1 is decoded, when set to logic 1 Field 2 is decoded.             |

### Table 4 Register 1 WRITE (Control Byte 2)

| BIT    | DESCRIPTION                                                                                                                                                                                                 |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0, D1 | Display mode selection bits. Table 8 shows the possible display modes.                                                                                                                                      |

| D2, D3 | Enhanced caption mode selection bits. Table 9 shows the possible enhanced caption modes.                                                                                                                    |

| D4     | When set to logic 1 acquisition of caption data is inhibited to allow the display to be used for On-Screen Display purposes.                                                                                |

| D5     | Acquisition window selection. When set to logic 0 only Line 21 is checked for caption data. When set to logic 1, lines 19 to 23 of both fields are checked, allowing encrypted video signals to be handled. |

| D6     | User channel selection.                                                                                                                                                                                     |

| D7     | Clears the page memory when set HIGH. The page memory will be within two fields (30 ms).                                                                                                                    |

### Table 5 Register 2 WRITE (On-Screen Display data row address)

| BIT      | DESCRIPTION                                                                                                                        |

|----------|------------------------------------------------------------------------------------------------------------------------------------|

| D0 to D3 | Row 0 to 3 sets the row address for On-Screen Display. This stored value will be incremented by overflow increments of Register 3. |

### Table 6 Register 3 WRITE (On-Screen Display data column address)

| BIT | DESCRIPTION                                                                                                                  |

|-----|------------------------------------------------------------------------------------------------------------------------------|

|     | Columns 0 to 4 sets the column address for On-Screen Display. This stored value will be incremented by writes to Register 4. |

### Table 7 Register 4 WRITE (On-Screen Display data)

| BIT      | DESCRIPTION                                                                                                         |

|----------|---------------------------------------------------------------------------------------------------------------------|

| D0 to D6 | OSD0 to OSD6, On-Screen Display data bits writing to this register causes Register 3 to increment its stored value. |

### Line twenty-one acquisition and display (LITOD)

SAA5252

Table 8 Display modes

| DISPLAY MODE OPTIONS  | M1 | MO |

|-----------------------|----|----|

| Video only            | 0  | 0  |

| Text mode             | 0  | 1  |

| Normal caption mode   | 1  | 0  |

| Enhanced caption mode | 1  | 1  |

Table 9 Enhanced caption modes

| ENHANCED CAPTION MODES              | EN1 | EN0 |

|-------------------------------------|-----|-----|

| Enhanced caption modes              | EN1 | EN0 |

| Shadowed character/Video background | 0   | 0   |

| Shadowed character/Mesh background  | 0   | 1   |

| Normal character/Video background   | 1   | 0   |

| Normal character/Mesh background    | 1   | 1   |

### **Description of READ registers**

The read subaddresses auto increment from 80H through to 82H at which point they stay until a new read subaddress is sent.

All the bits in Table 10 are reset to logic 0 after the register is read.

Table 10 Register 80H READ (status)

| BIT | DESCRIPTION                                                                                                       |

|-----|-------------------------------------------------------------------------------------------------------------------|

| D0  | Data ready (new data has been acquired).                                                                          |

| D1  | Parity error shut-down, goes HIGH when SAA5252 has a parity shut-down condition.                                  |

| D2  | Indicates the following bytes are extended data service bytes.                                                    |

| D3  | Indicates Field 1 or Field 2 data bytes.                                                                          |

| D7  | Indicates Power-On Reset (POR) has occurred, all I <sup>2</sup> C-bus write registers have been reset to logic 0. |

Table 11 Register 81H READ (first data byte)

| BIT      | DESCRIPTION                                                            |

|----------|------------------------------------------------------------------------|

| D0 to D6 | Data Bit 1 to Data Bit 7 (see note 1).                                 |

| D7       | Parity error flag bit. Bit goes HIGH when a parity error has occurred. |

### Note

1. In the Line 21, specification data bits are numbered D1 to D8.

Table 12 Register 82H READ (second data byte)

| BIT      | DESCRIPTION                                                            |  |  |  |  |  |  |  |

|----------|------------------------------------------------------------------------|--|--|--|--|--|--|--|

| D0 to D6 | Data Bit 1 to Data Bit 7 (see note 1).                                 |  |  |  |  |  |  |  |

| D7       | Parity error flag bit. Bit goes HIGH when a parity error has occurred. |  |  |  |  |  |  |  |

### Note

1. In the Line 21, specification data bits are numbered D1 to D8.

### Line twenty-one acquisition and display (LITOD)

SAA5252

### Interface to microcontroller using I<sup>2</sup>C-bus

The interface to the microcontroller is via the two-wire serial  $I^2C$ -bus, and optionally by a Data-Ready signal  $(\overline{DR})$ . On power up the microcontroller initializes the device by an  $I^2C$ -bus WRITE to Registers 0 (Control Byte 1). The  $I^2C$ -bus subaddress is then auto incremented to point to Register 1 (Control Byte 2). These two registers configure the device to the users requirements.

If the device is to be used for data acquisition only, then there are three methods by which the microcontroller can be informed of the arrival of valid Line 21 data:

- It can poll the DR pin, if the function has been enabled, and wait for it to go LOW.

- It can use the negative edge of the DR signal to cause an interrupt.

- It can poll the Data Ready bit (bit D0 of the status byte, I<sup>2</sup>C-bus READ Register 0).

When valid data is detected, the microcontroller must initiate an I<sup>2</sup>C-bus READ of Registers 80H, 81H and 82H. The first and second data bytes from the most recently received Line 21 are in Register 81H and Register 82H respectively.

The  $\overline{DR}$  pin, and the Data Ready bit (Status bit D0) will be cleared after any register has been read. POR is reset after Register 80H has been read.

### 'STAND-ALONE' (NON I2C-BUS) OPERATION

To set the SAA5252 for 'stand-alone' operation pin 2 ( $I^2C/\overline{DC}$ ) is tied LOW. This will change the operation of the SCL, SDA and  $\overline{DR}$  pins to mode select inputs which will select as shown in Table 13.

In the caption mode the SAA5252 operates in the basic Normal character/Black background mode. This complies with the FCC ruling. In the Enhanced caption mode the set-up will be Shadowed character/Video background. SDA and SCL in the 'stand-alone' operation act as bits M0 and M1 in Table 8.

Table 13 Stand-alone modes

| DR | SCL | SDA | MODE OF<br>OPERATION | CHANNEL<br>RECEPTION |

|----|-----|-----|----------------------|----------------------|

| 0  | 0   | 0   | video mode           | Channel 1            |

| 0  | 0   | 1   | text mode            | Channel 1            |

| 0  | 1   | 0   | normal captions      | Channel 1            |

| 0  | 1   | 1   | enhanced captions    | Channel 1            |

| 1  | 0   | 0   | video mode           | Channel 2            |

| 1  | 0   | 1   | text mode            | Channel 2            |

| 1  | 1   | 0   | normal captions      | Channel 2            |

| 1  | 1   | 1   | enhanced captions    | Channel 2            |

# Line twenty-one acquisition and display (LITOD)

SAA5252

### **PACKAGE OUTLINES**

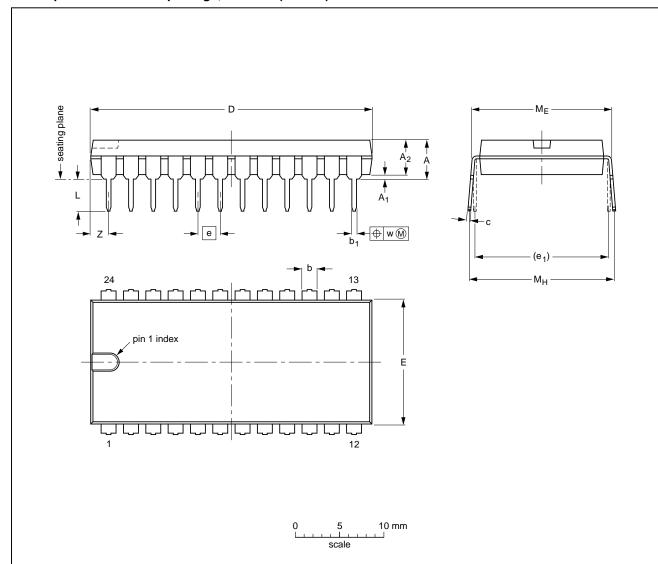

DIP24: plastic dual in-line package; 24 leads (600 mil)

SOT101-1

### DIMENSIONS (inch dimensions are derived from the original mm dimensions)

| UNIT   | A<br>max. | A <sub>1</sub><br>min. | A <sub>2</sub><br>max. | b              | b <sub>1</sub> | С              | D <sup>(1)</sup> | E <sup>(1)</sup> | е    | e <sub>1</sub> | L            | ME             | M <sub>H</sub> | w    | Z <sup>(1)</sup><br>max. |

|--------|-----------|------------------------|------------------------|----------------|----------------|----------------|------------------|------------------|------|----------------|--------------|----------------|----------------|------|--------------------------|

| mm     | 5.1       | 0.51                   | 4.0                    | 1.7<br>1.3     | 0.53<br>0.38   | 0.32<br>0.23   | 32.0<br>31.4     | 14.1<br>13.7     | 2.54 | 15.24          | 3.9<br>3.4   | 15.80<br>15.24 | 17.15<br>15.90 | 0.25 | 2.2                      |

| inches | 0.20      | 0.020                  | 0.16                   | 0.066<br>0.051 | 0.021<br>0.015 | 0.013<br>0.009 | 1.26<br>1.24     | 0.56<br>0.54     | 0.10 | 0.60           | 0.15<br>0.13 | 0.62<br>0.60   | 0.68<br>0.63   | 0.01 | 0.087                    |

### Note

1. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

| OUTLINE  |        | REFER    | EUROPEAN | ISSUE DATE |            |                                 |  |

|----------|--------|----------|----------|------------|------------|---------------------------------|--|

| VERSION  | IEC    | JEDEC    | EIAJ     |            | PROJECTION | ISSUE DATE                      |  |

| SOT101-1 | 051G02 | MO-015AD |          |            |            | <del>92-11-17</del><br>95-01-23 |  |

# Line twenty-one acquisition and display (LITOD)

SAA5252

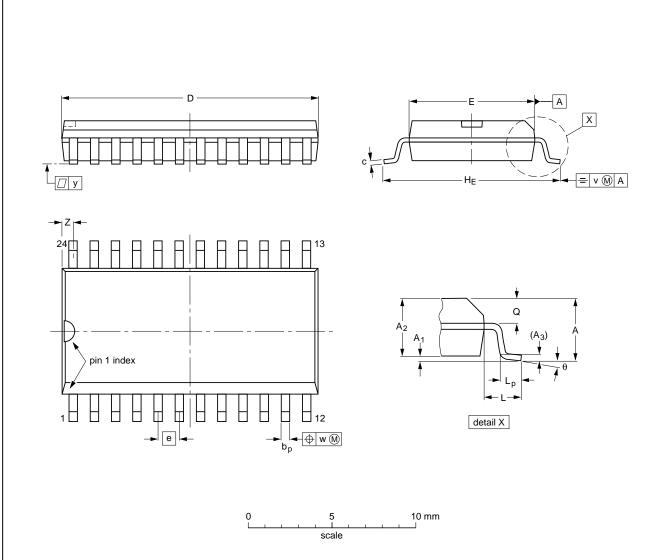

### SO24: plastic small outline package; 24 leads; body width 7.5 mm

SOT137-1

### **DIMENSIONS** (inch dimensions are derived from the original mm dimensions)

| UNIT   | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | A <sub>3</sub> | bp             | C              | D <sup>(1)</sup> | E <sup>(1)</sup> | е     | HE             | L     | Lp             | Ø              | v    | w    | у     | z <sup>(1)</sup> | θ  |

|--------|-----------|----------------|----------------|----------------|----------------|----------------|------------------|------------------|-------|----------------|-------|----------------|----------------|------|------|-------|------------------|----|

| mm     | 2.65      | 0.30<br>0.10   | 2.45<br>2.25   | 0.25           | 0.49<br>0.36   | 0.32<br>0.23   | 15.6<br>15.2     | 7.6<br>7.4       | 1.27  | 10.65<br>10.00 | 1.4   | 1.1<br>0.4     | 1.1<br>1.0     | 0.25 | 0.25 | 0.1   | 0.9<br>0.4       | 8° |

| inches | 0.10      | 0.012<br>0.004 | 0.096<br>0.089 | 0.01           | 0.019<br>0.014 | 0.013<br>0.009 | 0.61<br>0.60     | 0.30<br>0.29     | 0.050 | 0.42<br>0.39   | 0.055 | 0.043<br>0.016 | 0.043<br>0.039 | 0.01 | 0.01 | 0.004 | 0.035<br>0.016   | 0° |

### Note

1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

| OUTLINE  | REFERENCES |          |      |  | EUROPEAN   | ISSUE DATE                       |

|----------|------------|----------|------|--|------------|----------------------------------|

| VERSION  | IEC        | JEDEC    | EIAJ |  | PROJECTION | ISSUE DATE                       |

| SOT137-1 | 075E05     | MS-013AD |      |  |            | <del>-92-11-17</del><br>95-01-24 |

### Line twenty-one acquisition and display (LITOD)

SAA5252

### **SOLDERING**

### Introduction

There is no soldering method that is ideal for all IC packages. Wave soldering is often preferred when through-hole and surface mounted components are mixed on one printed-circuit board. However, wave soldering is not always suitable for surface mounted ICs, or for printed-circuits with high population densities. In these situations reflow soldering is often used.

This text gives a very brief insight to a complex technology. A more in-depth account of soldering ICs can be found in our "IC Package Databook" (order code 9398 652 90011).

### DIP

### SOLDERING BY DIPPING OR BY WAVE

The maximum permissible temperature of the solder is 260 °C; solder at this temperature must not be in contact with the joint for more than 5 seconds. The total contact time of successive solder waves must not exceed 5 seconds.

The device may be mounted up to the seating plane, but the temperature of the plastic body must not exceed the specified maximum storage temperature (T<sub>stg max</sub>). If the printed-circuit board has been pre-heated, forced cooling may be necessary immediately after soldering to keep the temperature within the permissible limit.

### REPAIRING SOLDERED JOINTS

Apply a low voltage soldering iron (less than 24 V) to the lead(s) of the package, below the seating plane or not more than 2 mm above it. If the temperature of the soldering iron bit is less than 300 °C it may remain in contact for up to 10 seconds. If the bit temperature is between 300 and 400 °C, contact may be up to 5 seconds.

### SO

### REFLOW SOLDERING

Reflow soldering techniques are suitable for all SO packages.

Reflow soldering requires solder paste (a suspension of fine solder particles, flux and binding agent) to be applied to the printed-circuit board by screen printing, stencilling or pressure-syringe dispensing before package placement. Several techniques exist for reflowing; for example, thermal conduction by heated belt. Dwell times vary between 50 and 300 seconds depending on heating method. Typical reflow temperatures range from 215 to 250 °C.

Preheating is necessary to dry the paste and evaporate the binding agent. Preheating duration: 45 minutes at  $45\,^{\circ}\text{C}$ .

### WAVE SOLDERING

Wave soldering techniques can be used for all SO packages if the following conditions are observed:

- A double-wave (a turbulent wave with high upward pressure followed by a smooth laminar wave) soldering technique should be used.

- The longitudinal axis of the package footprint must be parallel to the solder flow.

- The package footprint must incorporate solder thieves at the downstream end.

During placement and before soldering, the package must be fixed with a droplet of adhesive. The adhesive can be applied by screen printing, pin transfer or syringe dispensing. The package can be soldered after the adhesive is cured.

Maximum permissible solder temperature is 260 °C, and maximum duration of package immersion in solder is 10 seconds, if cooled to less than 150 °C within 6 seconds. Typical dwell time is 4 seconds at 250 °C.

A mildly-activated flux will eliminate the need for removal of corrosive residues in most applications.

### REPAIRING SOLDERED JOINTS

Fix the component by first soldering two diagonally-opposite end leads. Use only a low voltage soldering iron (less than 24 V) applied to the flat part of the lead. Contact time must be limited to 10 seconds at up to 300 °C. When using a dedicated tool, all other leads can be soldered in one operation within 2 to 5 seconds between 270 and 320 °C.

1996 Jul 18

### Line twenty-one acquisition and display (LITOD)

SAA5252

### **DEFINITIONS**

| Data sheet status         | rta sheet status                                                                      |  |  |  |  |

|---------------------------|---------------------------------------------------------------------------------------|--|--|--|--|

| Objective specification   | This data sheet contains target or goal specifications for product development.       |  |  |  |  |

| Preliminary specification | This data sheet contains preliminary data; supplementary data may be published later. |  |  |  |  |

| Product specification     | This data sheet contains final product specifications.                                |  |  |  |  |

| Limiting values           |                                                                                       |  |  |  |  |

### **Limiting values**

Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

### **Application information**

Where application information is given, it is advisory and does not form part of the specification.

### LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such improper use or sale.

### PURCHASE OF PHILIPS I2C COMPONENTS

Purchase of Philips I<sup>2</sup>C components conveys a license under the Philips' I<sup>2</sup>C patent to use the components in the I<sup>2</sup>C system provided the system conforms to the I<sup>2</sup>C specification defined by Philips. This specification can be ordered using the code 9398 393 40011.