PTB78560A, PTB78560B PTB78560C SLTS249-JUNE 2005

# 30-W, 24-V/48-V INPUT DC/DC CONVERTERS WITH AUTO-TRACK<sup>™</sup> SEQUENCING

## **FEATURES**

- Input Voltage: 18 V to 60 V

- **30-W Total Output Power**

- Output Voltages: 3.3 V, 5 V, and 12 V

- Wide-Output Adjust/Trim

- Up To 88% Efficiency •

- **Overcurrent Protection**

- **Overtemperature Shutdown** •

- Undervoltage Lockout •

- **Input Overvoltage Protection**

- Auto-Track<sup>™</sup> Power-Up Sequencing (Includes Sequenced Output with PTB78560B)

- Smart-Sense Remote Sensing (PTB78560B)

- **Dual-Logic Enable Control**

- Space-Saving 1x2 Footprint •

- Surface Mount Package

- Lead (Pb) Free Option Available •

- 1500-Vdc Isolation

- Agency Approvals (Pending): UL/cUL 60950, EN 60950

## APPLICATIONS

- Intermediate Bus Architectures

- **Telecom, High-End Computing Platforms**

- Multi-Rail Power Systems with **Power-Up Sequencing**

## DESCRIPTION

The PTB78560x is a series of 30–W rated isolated dc/dc converters, designed to operate from a standard 24–V or 48-V telecom central office (CO) supply. Housed in a 1x2 package, each model has a wide-adjust output voltage that can be set to one of the common intermediate bus voltages of 3.3 V, 5 V, or 12 V.

The PTB78560 series incorporates Auto-Track™, a feature that simplifies the power-up sequencing of multiple power modules that operate from the same intermediate bus. During a power-up cycle, modules with this feature have the capability of following a common ramp voltage applied to an input called Track. The PTB78560 series is specifically designed to control the Track voltage of any number of nonisolated downstream modules powered from its output. This ensures that the outputs of the downstream modules all rise simultaneously during power up. The PTB78560B (3.3 V) has an additional sequenced output, Vo Seq, which also rises with the Track voltage. This allows the Vo Seq output to power up simultaneously with the outputs from other power modules under the control of Auto-Track.

Whether used to facilitate power-up sequencing, or operated as a stand-alone module, the PTB78560 series includes many other features expected of high-performance dc/dc converter modules. Precise output voltage regulation is ensured with a differential remote sense. Operational features include an input undervoltage lockout (UVLO) and a dual-logic output enable control. Overcurrent and overtemperature protection ensure survival against load faults.

Typical applications include distributed power architectures in both telecom and computing environments, particularly complex digital systems requiring power sequencing of multiple power supply rails.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. Auto-Track is a trademark of Texas Instruments.

## PTB78560A, PTB78560B PTB78560C

SLTS249-JUNE 2005

Real Providence

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

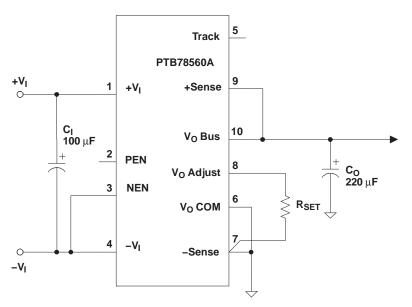

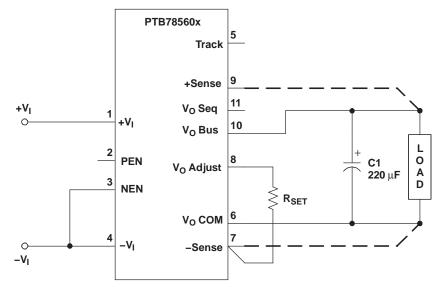

**Typical Circuit**

Notes:

† Sequenced output is available in the PTB78560B model only.

<sup>\*</sup> The +Sense may be connected to either V<sub>O</sub>Seq or V<sub>O</sub>Bus output of the PTB78560B.

<sup>‡</sup> R<sub>SET</sub> is required to set the output voltage higher than the minimum value. See the *Application Information* section for values.

<sup>#</sup> The PTB78560x modules require a minimum of 220 μF total output capacitance for proper operation.

A minimum of 100  $\mu F$  input capacitance is recommended for proper operation.

### **ORDERING INFORMATION**

| PTB78560 (Base Pt. No.) |                            |                              |                  |  |  |  |  |

|-------------------------|----------------------------|------------------------------|------------------|--|--|--|--|

| Output Voltage Range    | Part Number                | DESCRIPTION                  | Package Ref. (1) |  |  |  |  |

|                         | PTB78560AAH                | Horizontal T/H               | ERW              |  |  |  |  |

| 3.6 V to 5.5 V          | PTB78560AAS                | SMD, Standard <sup>(2)</sup> | 50)/             |  |  |  |  |

| -                       | PTB78560AAZ                | SMD, Standard (3)            | ERY              |  |  |  |  |

|                         | PTB78560BAH (4)            | Horizontal T/H               | ERW              |  |  |  |  |

| 1.8 V to 3.6 V          | PTB78560BAS (4)            | SMD, Standard <sup>(2)</sup> | FDV              |  |  |  |  |

| -                       | PTB78560BAZ <sup>(4)</sup> | SMD, Standard <sup>(3)</sup> | ERY              |  |  |  |  |

|                         | PTB78560CAH                | Horizontal T/H               | ERW              |  |  |  |  |

| 9 V to 13.2 V           | PTB78560CAS                | SMD, Standard <sup>(2)</sup> | FDV              |  |  |  |  |

| -                       | PTB78560CAZ                | SMD, Standard <sup>(3)</sup> | ERY              |  |  |  |  |

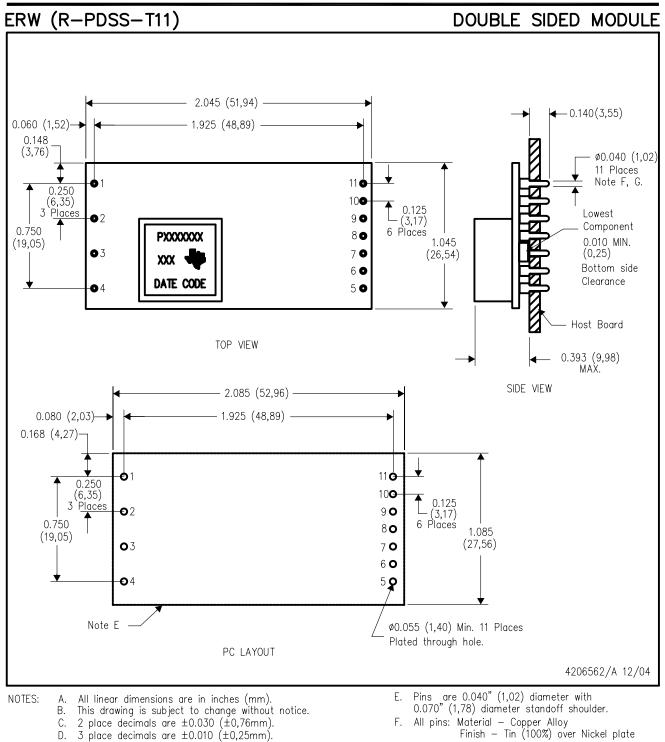

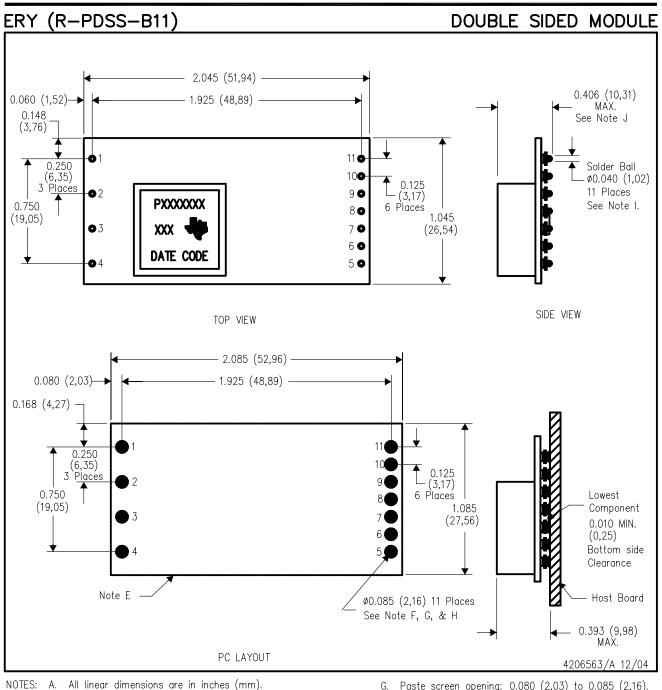

(1) See the applicable package reference drawing for the dimensions and PC board layout.

(2) Standard option specifies 63/37, Sn/Pb pin solder material.

(3) Lead-free (Pb-free) option specifies Sn/Ag pin solder material.

(4) Includes an Auto-Track compatible output, V<sub>Q</sub> Seq, which sequences with the Track control during power up.

## **ABSOLUTE MAXIMUM RATINGS**

|                          |                             |                               |                | UNIT                              |

|--------------------------|-----------------------------|-------------------------------|----------------|-----------------------------------|

| Vi                       | Input Voltage               |                               | Continuous     | 60 V                              |

| vI                       | input voltage               |                               | Surge, 1 s max | 100 V <sup>(1)</sup>              |

| V <sub>(Track)</sub>     | Track input voltage         |                               |                | 0 V to V <sub>O</sub> Bus + 0.3 V |

| I <sub>(Track)</sub> max | Track input current         | From external source          |                | 10 mA <sup>(2)</sup>              |

| T <sub>A</sub>           | Operating temperature range | Over V <sub>I</sub> range     |                | –40°C to 85°C                     |

|                          | Overtemperature protection  | PCB temperature (near pin 1)  |                | 115°C                             |

| т                        | Colder reflew to magneture  | Surface temperature of module | PTB78560xAS    | 235°C <sup>(3)</sup>              |

| (REFLOW)                 | Solder reflow temperature   | or pins PTB78560xAZ           |                | 260°C <sup>(4)</sup>              |

| T <sub>stg</sub>         | Storage temperature         |                               |                | -40°C to 125°C                    |

(1) The converter's internal protection circuitry may cause the output to turn off when the applied input voltage is greater than 60 V.

(2) When the Track input is fed from an external voltage source, the input current must be limited. A 2.74-kΩ value series resistor is recommended.

(3) During solder reflow of standard SMD package version, do not elevate the module PCB, pins, or internal component temperatures above a peak of 235°C.

(4) During solder reflow of Pb - free SMD package version, do not elevate the module PCB, pins, or internal component temperatures above a peak of 260°C.

## PACKAGE SPECIFICATIONS

| PTB78560x (Suffixes AH, AS, and AZ) |                                                         |                                   |                      |  |  |  |  |  |

|-------------------------------------|---------------------------------------------------------|-----------------------------------|----------------------|--|--|--|--|--|

| Weight                              |                                                         |                                   | 13.6 grams           |  |  |  |  |  |

| Flammability                        | Meets UL94V-O                                           |                                   |                      |  |  |  |  |  |

| Machanical shask                    | Per Mil-STD-883D, Method 2002.3, 1 ms,                  | Horizontal T/H (Suffix AH)        | 500 G <sup>(1)</sup> |  |  |  |  |  |

| Mechanical shock                    | 1/2 Sine, mounted                                       | Horizontal SMD (Suffix AS)        | 250 G <sup>(1)</sup> |  |  |  |  |  |

|                                     | Mil CTD 992D, Method 2007 0, 20 2000 Ltz                | Horizontal T/H (Suffix AH)        | 20 G <sup>(1)</sup>  |  |  |  |  |  |

| Mechanical vibration                | Mil-STD-883D, Method 2007.2, 20-2000 Hz,<br>PCB mounted | Horizontal SMD (Suffix AS and AZ) | 5 G <sup>(1)</sup>   |  |  |  |  |  |

(1) Qualification limit.

# PTB78560A, PTB78560B PTB78560C

SLTS249-JUNE 2005

## PTB78560B ELECTRICAL CHARACTERISTICS

(Unless otherwise stated,  $T_A = 25^{\circ}$ C,  $V_I = 24$  V,  $V_O = 3.3$  V,  $C_O = 330 \mu$ F, and  $I_O = I_O$ max)

|                      | DADAMETER                            | TEO                                                            | P1                                                   |          |                   |                    |                   |

|----------------------|--------------------------------------|----------------------------------------------------------------|------------------------------------------------------|----------|-------------------|--------------------|-------------------|

|                      | PARAMETER                            | IES                                                            |                                                      | MIN      | TYP               | MAX                | UNIT              |

|                      |                                      | Over V <sub>I</sub> range                                      | I <sub>O</sub> Bus                                   | 0.25 (1) |                   | 8 (2)              |                   |

| 0                    | Output current                       |                                                                | I <sub>O</sub> Seq                                   | 0        |                   | 4 (3)              | А                 |

|                      |                                      |                                                                | Sum total, (I <sub>O</sub> Bus + I <sub>O</sub> Seq) | 0.25     |                   | 8                  |                   |

| VI                   | Input voltage range                  | Over I <sub>O</sub> range                                      |                                                      | 18       | 24                | 60                 | V                 |

|                      | Set-point voltage tolerance          |                                                                |                                                      |          | ±1 <sup>(4)</sup> |                    | %V <sub>O</sub>   |

|                      | Temperature variation                | $-40^\circ C \leq T_A \leq 85^\circ C$                         |                                                      |          | ±0.5              |                    | %V <sub>O</sub>   |

|                      | Line regulation                      | Over V <sub>I</sub> range                                      |                                                      |          | ±7                | ±33                | mV                |

| Vo                   | Load regulation                      | Over I <sub>O</sub> range                                      |                                                      |          | ±13               | ±33                | mV                |

|                      | Total output voltage variation       | Includes set-point, li                                         | ne, load, $-40^{\circ}C \le T_A \le 85^{\circ}C$     |          | ±2                | ±3 <sup>(4)</sup>  | %V <sub>C</sub>   |

|                      | Adjust range                         | Over V <sub>I</sub> range                                      |                                                      | 1.8      |                   | 3.6                | V                 |

|                      |                                      |                                                                | $R_{SET}$ = 5.36 k $\Omega$ , V <sub>O</sub> = 3.3 V |          | 80%               |                    |                   |

| η                    | Efficiency                           |                                                                | $R_{SET}$ = 40.2 k $\Omega$ , $V_{O}$ = 2.5 V        |          | 77%               |                    |                   |

|                      |                                      |                                                                |                                                      | 73%      |                   |                    |                   |

|                      | V <sub>O</sub> Ripple (peak-to-peak) | 20-MHz bandwidth                                               |                                                      |          | 50                |                    | mV <sub>pl</sub>  |

|                      |                                      | 0.1 A/µs load step,                                            | Recovery time                                        |          | 100               |                    | μs                |

|                      | Transient response                   | 50% to 100%<br>I <sub>O</sub> max , C <sub>O</sub> = 330<br>μF | V <sub>O</sub> over/undershoot                       |          | ±150              |                    | mV                |

|                      |                                      | Input current                                                  | Track connected to -Sense                            |          | -0.13             |                    | mA                |

|                      | Track input (pin 5)                  | Open-circuit voltage                                           |                                                      | 0        |                   | V <sub>O</sub> Bus |                   |

|                      |                                      | Input slew rate limits                                         | 0.1 <sup>(5)</sup>                                   |          | 1                 | V/ms               |                   |

|                      |                                      | Referenced to -V <sub>I</sub>                                  | Input high voltage (V <sub>IH</sub> )                | 2        |                   | Open (6)           | V                 |

|                      | Output enable inputs (pins 2, 3)     |                                                                | Input low voltage (V <sub>IL</sub> )                 | -0.2     |                   | 0.8                |                   |

|                      |                                      |                                                                | Input low current (IIL)                              |          | -0.8              |                    | mA                |

|                      | Standby input current                | Pins 2 and 3 open                                              |                                                      |          | 8                 | 16                 | mA                |

| I <sub>O</sub> (tot) | Overcurrent threshold                | Shutdown, followed                                             | by autorecovery                                      |          | 12                |                    | Α                 |

| UVLO                 | Linder voltage leakeut               |                                                                | V <sub>I</sub> increasing                            |          | 17                |                    | V                 |

| UVLO                 | Undervoltage lockout                 |                                                                | V <sub>I</sub> decreasing                            |          | 16                |                    | v                 |

| fs                   | Switching frequency                  | Over V <sub>I</sub> range                                      |                                                      | 400      | 500               | 600                | kHz               |

|                      | Internal input capacitance           |                                                                |                                                      |          | 1                 |                    | μF                |

|                      | External input capacitance           | Between +V <sub>I</sub> and -V                                 | 1                                                    | 100      |                   |                    | μF                |

|                      | External output capacitance          | Between both output                                            | ts and V <sub>O</sub> COM                            | 220      | 330               | 5,000              | μF                |

|                      | Isolation voltage                    | Input-output                                                   |                                                      | 1,500    |                   |                    | Vdc               |

|                      | Isolation capacitance                | Input-output                                                   |                                                      |          | 2,000             |                    | pF                |

|                      | Isolation resistance                 | Input-output                                                   | 10                                                   |          |                   | MΩ                 |                   |

| MTBF                 | Reliability                          | Telcordia SR-332 50<br>benign                                  | $0\%$ stress, $T_A = 40^{\circ}C$ , ground           | 3.6      |                   |                    | 10 <sup>6</sup> H |

The converter requires a minimum load current at either the V<sub>O</sub> Seq or V<sub>O</sub> Bus output for proper operation. The converter is not (1) damaged when operated under a no-load condition.

See temperature derating curves for safe operating area (SOA), to determine output current derating at elevated ambient temperatures. (2)

(3) When load current is supplied from the Vo Seq output, the module exhibits higher power dissipation and slightly lower operating efficiency.

The set-point voltage tolerance is affected by the tolerance and stability of R<sub>SET</sub>. The stated limit is unconditionally met if R<sub>SET</sub> has a (4) tolerance of 1%, with 100 ppm/°C temperature stability.

When controlling the Track input from an external source, the slew rate of the applied signal must be greater than the minimum limit. (5) Failure to allow the voltage to completely rise to the voltage at the V<sub>O</sub> (bus) output, at no less than the minimum specified rate, may thermally overstress the converter.

The PEN and NEN inputs each have an internal pullup resistor. If the enable feature is not used, the PEN input (pin 2) should be left (6) open circuit and the NEN input (pin 3) permanently connected to -V<sub>I</sub>. A discrete MOSFET or bipolar transistor is recommended for the enable control. The open-circuit voltage is less than 10 V. See the Application Information for a more detailed description.

PTB78560A, PTB78560B PTB78560C SLTS249-JUNE 2005

## PTB78560A ELECTRICAL CHARACTERISTICS

(Unless otherwise stated,  $T_A = 25^{\circ}$ C,  $V_I = 24$  V,  $V_O = 5$  V,  $C_O = 220 \mu$ F, and  $I_O = I_O$ max)

| PARAMETER          |                                      | тсет                                     | P1                                               | UNIT     |                    |                   |                   |

|--------------------|--------------------------------------|------------------------------------------|--------------------------------------------------|----------|--------------------|-------------------|-------------------|

|                    |                                      | IESI                                     |                                                  | MIN      | TYP                | MAX               | UNI               |

| I <sub>O</sub>     | Output current                       | Over V <sub>I</sub> range                | I <sub>O</sub> Bus                               | 0.25 (1) |                    | 6 (2)             | А                 |

| VI                 | Input voltage range                  | Over I <sub>O</sub> range                |                                                  | 18       | 24                 | 60                | V                 |

|                    | Set-point voltage tolerance          |                                          |                                                  |          | ±1 <sup>(3)</sup>  |                   | %V <sub>C</sub>   |

|                    | Temperature variation                | $-40^{\circ}C \leq T_A \leq 85^{\circ}C$ |                                                  |          | ±0.5               |                   | %V <sub>C</sub>   |

| V                  | Line regulation                      | Over V <sub>I</sub> range                |                                                  |          | ±0.2               | ±1                | %V <sub>C</sub>   |

| Vo                 | Load regulation                      | Over I <sub>O</sub> range                |                                                  |          | ±0.4               | ±1                | %V <sub>C</sub>   |

|                    | Total output voltage variation       | Includes set-point, lir                  | ne, load, $-40^{\circ}C \le T_A \le 85^{\circ}C$ |          | ±2                 | ±3 <sup>(3)</sup> | %V <sub>C</sub>   |

|                    | Adjust range                         | Over V <sub>I</sub> range                |                                                  | 3.6      |                    | 5.5               | V                 |

| η                  | Efficiency                           |                                          | R <sub>SET</sub> = 14.3 kΩ, V <sub>O</sub> =5 V  |          | 83%                |                   |                   |

|                    | V <sub>O</sub> Ripple (peak-to-peak) | 20-MHz bandwidth                         |                                                  |          | 1                  |                   | %V <sub>C</sub>   |

|                    |                                      | 0.1 A/µs load step,                      | Recovery time                                    |          | 100                |                   | μs                |

|                    | Transient response                   | 50% to 100%<br>I <sub>O</sub> max        | V <sub>O</sub> over/undershoot                   |          | ±200               |                   | mV                |

|                    | Trock input (pip 5)                  | Input current                            | Track connected to -Sense                        |          | -0.2               |                   | mA                |

|                    | Track input (pin 5)                  | Open-circuit voltage                     | 0                                                |          | V <sub>O</sub> Bus |                   |                   |

|                    |                                      | Referenced to -VI                        | Input high voltage (V <sub>IH</sub> )            | 2        |                    | Open (4)          | V                 |

|                    | Output enable inputs (pins 2, 3)     |                                          | Input low voltage ( $V_{IL}$ )                   | -0.2     |                    | 0.8               | v                 |

|                    |                                      |                                          | Input low current (IIL)                          |          | -0.8               |                   | mA                |

|                    | Standby input current                | Pins 2 and 3 open                        |                                                  |          | 8                  | 16                | mA                |

| I <sub>O</sub> Bus | Overcurrent threshold                | Shutdown, followed I                     | by autorecovery                                  |          | 9                  |                   | А                 |

| UVLO               | Undervoltage lockout                 | V <sub>I</sub> increasing                |                                                  |          | 17                 |                   | V                 |

| UVLO               | Undervoltage lockout                 |                                          | V <sub>I</sub> decreasing                        |          | 16                 |                   | v                 |

| fs                 | Switching frequency                  | Over V <sub>I</sub> range                |                                                  | 400      | 500                | 600               | kHz               |

|                    | Internal input capacitance           |                                          |                                                  |          | 1                  |                   | μF                |

|                    | External input capacitance           | Between $+V_I$ and $-V$                  | 1                                                | 100      |                    |                   | μF                |

|                    | External output capacitance          | Between both output                      | is and V <sub>O</sub> COM                        | 220      |                    | 5,000             | μF                |

|                    | Isolation voltage                    | Input-output                             |                                                  | 1,500    |                    |                   | Vdc               |

|                    | Isolation capacitance                | Input-output                             |                                                  | 2,000    |                    | pF                |                   |

|                    | Isolation resistance                 | Input-output                             | 10                                               |          |                    | MΩ                |                   |

| MTBF               | Reliability                          | Telcordia SR-332 50<br>benign            | % stress, $T_A = 40^{\circ}C$ , ground           | 3.6      |                    |                   | 10 <sup>6</sup> ⊢ |

|                    |                                      |                                          |                                                  |          |                    |                   |                   |

(1) The converter requires a minimum load current for proper operation. The converter is not damaged when operated under a no-load condition.

(2) See temperature derating curves for safe operating area (SOA), to determine output current derating at elevated ambient temperatures.

(3) The set-point voltage tolerance is affected by the tolerance and stability of R<sub>SET</sub>. The stated limit is unconditionally met if R<sub>SET</sub> has a tolerance of 1%, with 100 ppm/°C temperature stability.

(4) The PEN and NEN inputs each have an internal pullup resistor. If the enable feature is not used, the PEN input (pin 2) should be left open circuit and the NEN input (pin 3) permanently connected to -V<sub>1</sub>. A discrete MOSFET or bipolar transistor is recommended for the enable control. The open-circuit voltage is less than 10 V. See the *Application Information* for a more detailed description.

# PTB78560A, PTB78560B PTB78560C

## PTB78560C ELECTRICAL CHARACTERISTICS

(Unless otherwise stated,  $T_A = 25^{\circ}C$ ,  $V_I = 24$  V,  $V_O = 12$  V,  $C_O = 100 \ \mu$ F, and  $I_O = I_Omax$ )

| DADAMETED          |                                      | TEO                                          | PT                                                             |                    |                   |                     |                    |

|--------------------|--------------------------------------|----------------------------------------------|----------------------------------------------------------------|--------------------|-------------------|---------------------|--------------------|

|                    | PARAMETER                            | IES                                          |                                                                | MIN                | TYP               | MAX                 | UNIT               |

| I <sub>O</sub>     | Output current                       | Over V <sub>I</sub> range I <sub>O</sub> Bus |                                                                | 0.1 <sup>(1)</sup> |                   | 2.5 (2)             | А                  |

| VI                 | Input voltage range                  | Over I <sub>O</sub> range                    |                                                                | 18                 | 24                | 60                  | V                  |

|                    | Set-point voltage tolerance          |                                              |                                                                |                    | ±1 <sup>(3)</sup> |                     | %V <sub>O</sub>    |

|                    | Temperature variation                | $-40^\circ C \leq T_A \leq 85^\circ C$       |                                                                |                    | ±0.5              |                     | %V <sub>O</sub>    |

| <i></i>            | Line regulation                      | Over V <sub>I</sub> range                    |                                                                |                    | ±0.2              | ±1                  | %V <sub>O</sub>    |

| Vo                 | Load regulation                      | Over I <sub>O</sub> range                    |                                                                |                    | ±0.4              | ±1                  | %V <sub>O</sub>    |

|                    | Total output voltage variation       | Includes set-point, li                       | ne, load, $-40^{\circ}C \le T_A \le 85^{\circ}C$               |                    | ±2                | ±3 <sup>(3)</sup>   | %V <sub>O</sub>    |

|                    | Adjust range                         | Over V <sub>I</sub> range                    |                                                                | 9                  |                   | 13.2                | V                  |

|                    | <b>F</b> #isionay                    |                                              | $R_{SET} = 9.09 \text{ k}\Omega, \text{ V}_{O} = 12 \text{ V}$ |                    | 88%               |                     |                    |

| η                  | Efficiency                           |                                              | $R_{SET}$ = open, $V_{O}$ = 9 V                                |                    | 86%               |                     |                    |

|                    | V <sub>O</sub> Ripple (peak-to-peak) | 20-MHz bandwidth                             |                                                                |                    | 1                 |                     | %V <sub>O</sub>    |

|                    |                                      | 0.1 A/µs load step,                          | Recovery time                                                  |                    | 100               |                     | μs                 |

|                    | Transient Response                   | 50% to 100%<br>I <sub>O</sub> max            | V <sub>O</sub> over/undershoot                                 |                    | ±150              |                     | mV                 |

|                    | Trock input (nin 5)                  | Input current                                | Track connected to -Sense                                      |                    | -0.48             |                     | mA                 |

|                    | Track input (pin 5)                  | Open-circuit voltage                         |                                                                | 0                  |                   | V <sub>O</sub> Bus  |                    |

|                    |                                      | Referenced to -VI                            | Input high voltage (V <sub>IH</sub> )                          | 2                  |                   | Open <sup>(4)</sup> | V                  |

|                    | Output enable inputs (pins 2, 3)     |                                              | Input low voltage ( $V_{IL}$ )                                 | -0.2               |                   | 0.8                 | v                  |

|                    |                                      |                                              | Input low current (I <sub>IL</sub> )                           |                    | -0.8              |                     | mA                 |

|                    | Standby input current                | Pins 2 and 3 open                            |                                                                |                    | 8                 | 16                  | mA                 |

| I <sub>O</sub> Bus | Overcurrent threshold                | Shutdown, followed                           | by autorecovery                                                |                    | 3.75              |                     | А                  |

| UVLO               | Lindon voltago, lookout              |                                              | V <sub>I</sub> increasing                                      |                    | 17                |                     | V                  |

| UVLO               | Undervoltage lockout                 |                                              | V <sub>I</sub> decreasing                                      |                    | 16                |                     | v                  |

| fs                 | Switching frequency                  | Over V <sub>I</sub> range                    |                                                                | 400                | 500               | 600                 | kHz                |

|                    | Internal input capacitance           |                                              |                                                                |                    | 1                 |                     | μF                 |

|                    | External input capacitance           | Between +V <sub>I</sub> and -V               | 1                                                              | 100                |                   |                     | μF                 |

|                    | External output capacitance          | Between both output                          | ts and V <sub>O</sub> COM                                      | 100                |                   | 1,500               | μF                 |

|                    | Isolation voltage                    | Input-output                                 |                                                                | 1,500              |                   |                     | Vdc                |

|                    | Isolation capacitance                | Input-output                                 |                                                                |                    | 2,000             |                     | pF                 |

|                    | Isolation resistance                 | Input-output                                 |                                                                | 10                 |                   |                     | MΩ                 |

| MTBF               | Reliability                          | Telcordia SR-332 50<br>benign                | 0% stress, $T_A = 40^{\circ}C$ , ground                        | 3.4                |                   |                     | 10 <sup>6</sup> Hi |

(1) The converter requires a minimum load current for proper operation. The converter is not damaged when operated under a no-load condition.

See temperature derating curves for safe operating area (SOA), to determine output current derating at elevated ambient temperatures. (2) (3) The set-point voltage tolerance is affected by the tolerance and stability of R<sub>SET</sub>. The stated limit is unconditionally met if R<sub>SET</sub> has a tolerance of 1%, with 100 ppm/°C temperature stability.

The PEN and NEN enable inputs each have an internal pullup resistor. If the enable feature is not used, the PEN input (pin 2) should be (4) left open circuit and the NEN input (pin 3) permanently connected to -V<sub>1</sub>. A discrete MOSFET or bipolar transistor is recommended for the enable control. The open-circuit voltage is less than 10 V. See the Application Information for a more detailed description.

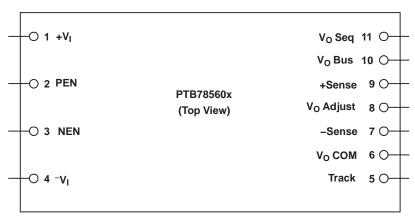

#### **TERMINAL FUNCTIONS**

| TERMINAL                       |     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                           | NO. | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| +V <sub>1</sub> <sup>(1)</sup> | 1   | The positive input for the module with respect to $-V_1$ . When powering the module from a negative input voltage, this input is connected to the input source ground.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| -V <sub>1</sub> <sup>(1)</sup> | 4   | The negative input supply for the module, and the 0-V reference for the <i>PEN</i> and <i>NEN</i> enable inputs. When powering the module from a positive source, this input is connected to the input source return.                                                                                                                                                                                                                                                                                                                                                                                         |

| PEN <sup>(1)</sup>             | 2   | An open-collector (open-drain) positive logic input that is referenced to $-V_1$ . When this input is pulled to $-V_1$ potential the converter output is disabled. This input must be open circuit for the converter to operate. The converter then produces an output whenever a valid input source is applied.                                                                                                                                                                                                                                                                                              |

| NEN <sup>(1)(2)</sup>          | 3   | An open-collector (open-drain) negative logic input that is referenced to $-V_1$ . This input must be pulled to $-V_1$ potential to enable the converter. When the input is open circuit, the converter output is disabled. If the enable feature is not used, this input should be permanently connected to $-V_1$ . The module then produces an output whenever a valid input source is applied.                                                                                                                                                                                                            |

| V <sub>O</sub> Bus             | 10  | This is the positive power output with respect to $V_0$ COM, and the main output from the converter. It is dc isolated from the input power pins and produces a valid output voltage approximately 20 ms before the voltage at the <i>Track</i> terminal is allowed to rise. This provides the required standby power source to any <i>downstream</i> nonisolated modules in power-up sequencing applications.                                                                                                                                                                                                |

| V <sub>O</sub> Seq             | 11  | This is a sequenced output voltage from the converter that is controlled by the <i>Track</i> terminal during power-up transitions. It is only available to the PTB78560B, and used with the output voltage set to 3.3 V (an I/O supply voltage). During power up, the voltage at $V_0$ Seq rises with the <i>Track</i> terminal, typically 20 ms after the $V_0$ Bus output has reached regulation.                                                                                                                                                                                                           |

| V <sub>O</sub> COM             | 6   | This is the output power return for both the $V_O$ Bus and $V_O$ Seq output voltages. This terminal should be connected to the common of the load circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Track                          | 5   | This terminal is used in power-up sequencing applications to control the output voltage of Auto-Track compatible modules, powered from the converter $V_OBus$ output. This includes the converter $V_OSeq$ output on the PTB78560B. The converter <i>Track</i> control has an internal transistor, which holds the voltage close to $V_OCOM$ potential for approximately 20 ms (40 ms with the PTB78560C) after the $V_OBus$ output is in regulation. Following this delay, the <i>Track</i> voltage and $V_OSeq$ rises simultaneously with the output voltage of all other modules controlled by Auto-Track. |

| -Sense                         | 7   | Provides the converter with a remote sense capability when used with + <i>Sense</i> . For optimum output voltage accuracy, this pin should always be connected to $V_0COM$ , close to the load circuit. This terminal is also the reference connection for both the output voltage set-point resistor and <i>Track</i> control.                                                                                                                                                                                                                                                                               |

| V <sub>O</sub> Adjust          | 8   | A resistor must be connected between this terminal and -Sense to set the converter output voltage. A 0.05-W rated resistor may be used, with tolerance and temperature stability of 1% and 100 ppm/°C, respectively. If left open circuit, the converter output voltage defaults to its lowest value. The specification table gives the standard resistor values for the most common output voltages.                                                                                                                                                                                                         |

| +Sense                         | 9   | The +Sense pin can be connected to $V_OBus$ (or $V_OSeq$ ) output. When connected to $V_OSeq$ , remote sense compensation is delayed until the converter's power-up sequence is complete. The voltage at $V_OBus$ is also raised slightly. The +Sense input may be left open circuit, but connecting it to one of the output terminals improves load regulation of that output.                                                                                                                                                                                                                               |

#### **Terminal Locations**

## **TYPICAL CHARACTERISTICS**

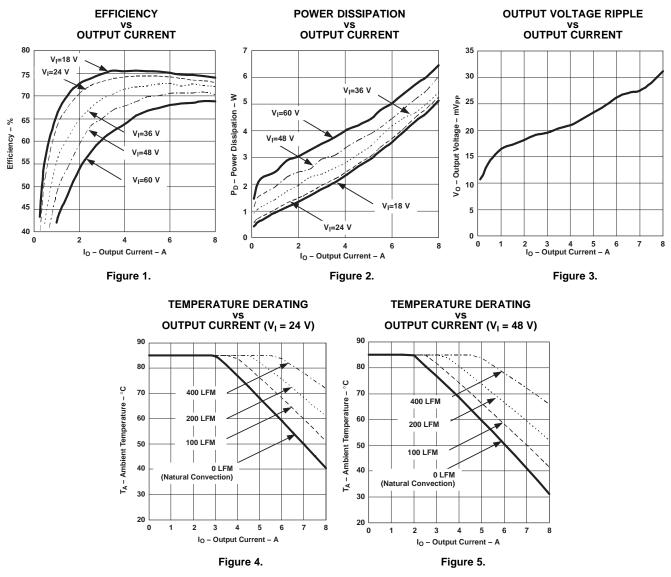

## PTB78560B Characteristic Data (V<sub>o</sub> = 1.8 V) <sup>(1)(2)</sup>

- (1) All data listed in Figure 1, Figure 3, and have been developed from actual products tested at 25°C. This data is considered typical data for the dc-dc converter.

- (2) All data listed in Figure 1, Figure 3, and have been developed from actual products tested at 25°C. This data is considered typical data for the dc-dc converter.

## **TYPICAL CHARACTERISTICS (continued)**

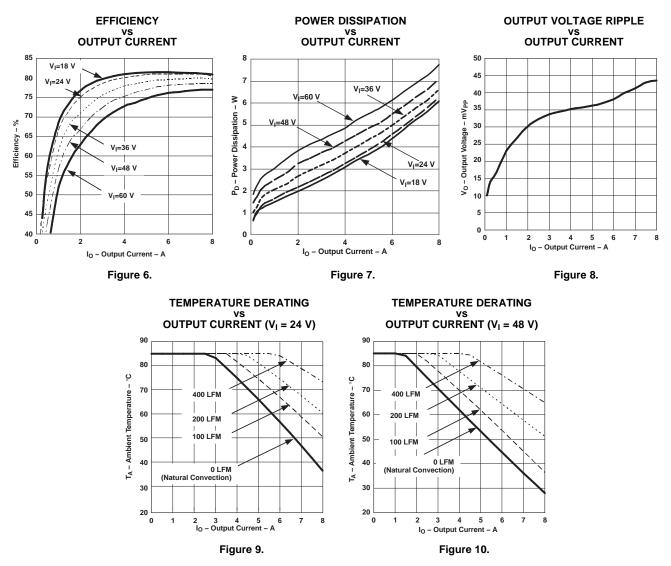

## PTB78560B Characteristic Data (V<sub>o</sub> = 3.3 V) <sup>(3)(4)</sup>

- (3) All data listed in Figure 6, Figure 8, and Figure 7 have been developed from actual products tested at 25°C. This data is considered typical data for the dc-dc converter.

- (4) The temperature derating curves represent operating conditions at which internal components are at or below manufacturer's maximum rated operating temperature. Derating limits apply to modules soldered directly to a 100-mm × 100-mm, double-sided PCB with 2 oz. copper. Applies to Figure 9, and Figure 10.

## **TYPICAL CHARACTERISTICS (continued)**

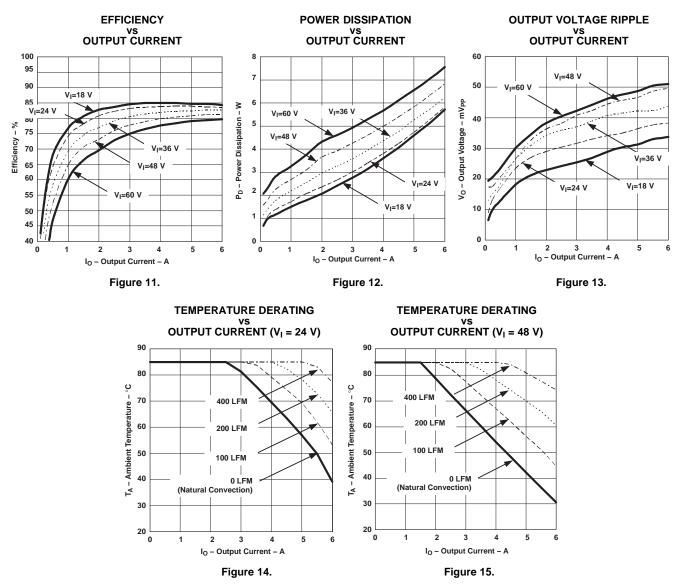

## PTB78560A Characteristic Data ( $V_0 = 5 V$ ) <sup>(5)(6)</sup>

- (5) All data listed in Figure 11, , and Figure 12 have been developed from actual products tested at 25°C. This data is considered typical data for the dc-dc converter.

- (6) The temperature derating curves represent operating conditions at which internal components are at or below manufacturer's maximum rated operating temperature. Derating limits apply to modules soldered directly to a 100-mm × 100-mm, double-sided PCB with 2 oz. copper. Applies to Figure 14, and Figure 15.

## **TYPICAL CHARACTERISTICS (continued)**

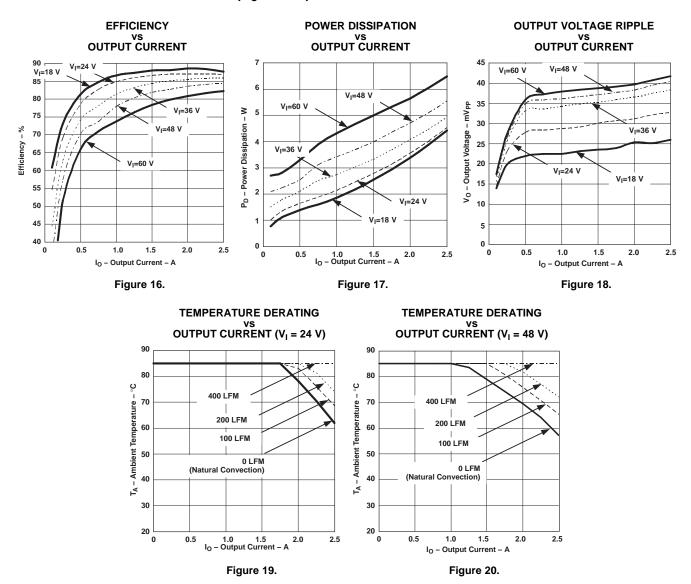

## PTB78560C Characteristic Data (V<sub>o</sub> = 12 V) <sup>(7)(8)</sup>

- (7) All data listed in Figure 16, Figure 18, and Figure 17 have been developed from actual products tested at 25°C. This data is considered typical data for the dc-dc converter.

- (8) The temperature derating curves represent operating conditions at which internal components are at or below manufacturer's maximum rated operating temperature. Derating limits apply to modules soldered directly to a 100-mm x 100-mm, double-sided PCB with 2 oz. copper. Applies to Figure 19.

## **APPLICATION INFORMATION**

#### **Operating Features and System Considerations for the PTB78560x DC/DC Converters**

#### **Primary-Secondary Isolation**

These converters incorporate electrical isolation between the input terminals (primary) and the output terminals (secondary). All converters are tested to a withstand voltage of 1500 VDC. This complies with UL/cUL 60950 and EN 60950 and the requirements for functional isolation. It allows the converter to be configured for either a positive or negative input voltage source. The data sheet *Terminal Functions* table provides guidance as to the correct reference that must be used for the external control signals.

#### **Undervoltage Lockout**

The undervoltage lockout (UVLO) is designed to prevent the operation of the converter until the input voltage is close to the minimum operating voltage. The converter is held off when the input voltage is below the UVLO threshold, and turns on when the input voltage rises above the threshold. This prevents high start-up current during normal power up of the converter, and minimizes the current drain from the input source during low input voltage conditions. The converter meets full specifications when the minimum specified input voltage is reached. The UVLO circuitry also overrides the operation of the *PEN* and *NEN* enable controls. Only when the input voltage is above the UVLO threshold do these inputs become functional.

#### Soft-Start Power Up

When the converter is first powered, the internal soft-start circuit limits how fast the output voltage can rise. The soft-start circuit functions whenever the converter output is enabled from the PEN and NEN inputs, or when a valid input source is first applied with the output enabled. It also functions on a recovery from a load fault, overtemperature, or input overvoltage condition. The purpose of the soft-start feature is to limit the surge of current drawn from the input source when the converter begins to operate. By limiting the rate at which the output voltage rises, the magnitude of current required to charge up the load circuit capacitance is significantly reduced.

Figure 21 shows the power-up characteristic of a PTB78560C converter. The output voltage is set to 12 V. The soft-start circuit introduces a short time delay (typically 10-15 ms) before allowing the output to rise. The output then progressively rises to the voltage set-point. The waveforms were recorded with a resistive load of 2.5 A.

Figure 21. Soft-Start Waveform

#### **Overcurrent Protection**

To protect against load faults, these converters incorporate output overcurrent protection. Applying a load to the

## APPLICATION INFORMATION (continued)

output that exceeds the converter overcurrent threshold (see applicable specification) causes the output voltage to momentarily fold back, and then shut down. Following shutdown, the module periodically attempts to automatically recover by initiating a soft-start power up. This is often described as a *hiccup* mode of operation, whereby the module continues in the cycle of successive shutdown and power up until the load fault is removed. Once the fault is removed, the converter automatically recovers and returns to normal operation.

#### Input Overvoltage Protection

The converter protects itself against input voltage surges and transients of up to 100 V. This is above the maximum continuous operating input voltage of 60 V. In order to protect itself, the converter output is disabled at some voltage above 60 V. This is to ensure that the converter internal components are not exposed to voltages above their stress ratings. The converter output remains off for some of the period that the input voltage is above the maximum continuous rating. Once the overvoltage event has passed, the output from the converter automatically restarts by executing a soft-start power up.

#### Differential Output Voltage Sense

A differential remote sense allows a converter regulation circuitry to compensate for limited amounts of IR drop, that may be incurred between the converter and load, in either the positive or return PCB traces. Connecting the +Sense and –Sense pins to the respective positive and ground reference of the load terminals improves the load regulation of the converter output voltage at that connection point. The –Sense pin should always be connected to the  $V_O$  COM. The +Sense pin may be connected to either the + $V_O$  Bus or + $V_O$  Seq outputs.

When the +Sense pin is connected to the  $V_0$  Seq output, the voltage at  $V_0$  Bus voltage regulates slightly higher. Depending on the load conditions on the  $V_0$  Seq output, the voltage at  $V_0$  Bus may be up to 100 mV higher than the converter set-point voltage. In addition, the Smart-Sense feature (incorporated into the converter) only engages sense compensation to the  $V_0$  Seq output when that output voltage is close to the set-point. During a power-up sequencing event, the sense circuit automatically defaults to sensing the  $V_0$  Bus voltage, internal to the converter.

Leaving the +Sense and –Sense pins open does not damage the converter or load circuit. The converter includes default circuitry that keeps the output voltage in regulation. However, if the remote sense feature is not used, the –Sense pin should still be connected to  $V_{O}COM$ .

**Note:** The remote sense feature is not designed to compensate for the forward drop of nonlinear or frequency-dependent components that may be placed in series with the converter output. Examples include OR-ing diodes, filter inductors, ferrite beads, and fuses. When these components are enclosed by the sense pin connections, they are effectively placed inside the regulation control loop, which can adversely affect the stability of the converter.

#### **Overtemperature Protection**

Overtemperature protection is provided by an internal temperature sensor, which monitors the temperature of the converter PCB (close to pin 1). If the PCB temperature exceeds a nominal 115°C, the converter shuts down. The converter then automatically restarts when the sensed temperature falls to approximately 105°C. When operated outside its recommended thermal derating envelope (see data sheet derating curves), the converter typcially cycles on and off at intervals from a few seconds to one or two minutes. This is to ensure that the internal components are not permanently damaged from excessive thermal stress.

#### **Output Voltage Adjustment**

An external resistor is required to set the nominal output voltage(s) of the converter to a voltage higher than its minimum value. The resistor,  $R_{SET}$ , must be connected directly between the  $V_O$  Adjust (pin 8) and -Sense (pin 7) terminals. A 0.05-W rated resistor can be used. The tolerance should be 1%, with a temperature stability of 100 ppm/°C (or better). Place the resistor close to the converter and connect it using dedicated PCB traces (see Figure 22). Table 1 gives the nearest standard value of external resistor for the common voltages within each model's adjust range. The actual output voltage that the resistor value provides is also provided.

| Table 1. Standard Values of R <sub>SET</sub> for Common Output Voltages |                  |                         |                  |                         |                  |                         |  |  |

|-------------------------------------------------------------------------|------------------|-------------------------|------------------|-------------------------|------------------|-------------------------|--|--|

|                                                                         | PTB78560A        |                         | PTB              | 78560B                  | PTB              | 78560C                  |  |  |

| V <sub>O</sub> (Required)                                               | R <sub>SET</sub> | V <sub>O</sub> (Actual) | R <sub>SET</sub> | V <sub>O</sub> (Actual) | R <sub>SET</sub> | V <sub>O</sub> (Actual) |  |  |

| 1.8 V                                                                   | _                | _                       | Open             | 1.802 V                 | _                | -                       |  |  |

| 2 V                                                                     | _                | _                       | 200 kΩ           | 2.004 V                 | _                | -                       |  |  |

| 2.5 V                                                                   | -                | _                       | 40.2 kΩ          | 2.498 V                 | _                | -                       |  |  |

| 3.3 V                                                                   | -                | _                       | 5.36 kΩ          | 3.300 V                 | _                | -                       |  |  |

| 3.6 V                                                                   | Open             | 3.611 V                 | 309 Ω            | 3.600 V                 | _                | -                       |  |  |

| 5 V                                                                     | 14.3 kΩ          | 5.005 V                 | -                | _                       | _                | -                       |  |  |

| 9 V                                                                     | -                | _                       | _                | -                       | Open             | 9.015 V                 |  |  |

| 10 V                                                                    | -                | _                       | _                | -                       | 73.2 kΩ          | 9.993 V                 |  |  |

| 12 V                                                                    | _                | _                       | -                | _                       | 9.09 kΩ          | 12 V                    |  |  |

| 13.2 V                                                                  | _                | _                       | -                | _                       | 0 Ω              | 13.23 V                 |  |  |

For other output voltages, the value of the required adjust resistor may be calculated using Equation 1.

$$R_{SET} = R_{O} \times \frac{V_{R}}{V_{O} - V_{MIN}} - R_{P}$$

(1)

Table 2 gives the output voltage adjust range and the required equation constants for the converter model selected. To calculate the required value of R<sub>SET</sub>, simply locate the applicable constants and substitute these into the formula along with the desired output voltage.

#### **Table 2. Adjust Ranges and Equation Constants**

| Model #          | PTB78560A | PTB78560B | PTB78560C |

|------------------|-----------|-----------|-----------|

| V <sub>R</sub>   | 1.24 V    | 1.24 V    | 2.5 V     |

| R <sub>O</sub>   | 49.91 kΩ  | 36.55 kΩ  | 37.27 kΩ  |

| R <sub>P</sub>   | 30.1 kΩ   | 24.9 kΩ   | 22.1 kΩ   |

| V <sub>MIN</sub> | 3.61 V    | 1.8 V     | 9.02 V    |

| V <sub>MAX</sub> | 5.5 V     | 3.6 V     | 13.2 V    |

Figure 22. Output Voltage Adjustment

## **Input Current Limiting**

**The converter is not internally fused.** For safety and overall system protection, the maximum input current to the converter must be limited. Active or passive current limiting can be used. Passive current limiting can be a fast-acting fuse. A 125-V fuse, rated no more than 5 A, is recommended. Active current limiting can be implemented with a current limited *Hot-Swap* controller.

## Thermal Considerations

Airflow may be necessary to ensure that the module can supply the desired load current in environments with elevated ambient temperatures. The required airflow rate is determined from the safe operating area (SOA). The SOA is the area beneath the applicable airflow rate curve on the graph of temperature derating vs output current. (See the Typical Characteristics.) Operating the converter within the SOA limits ensures that all the internal components are at or below their stated maximum operating temperatures.

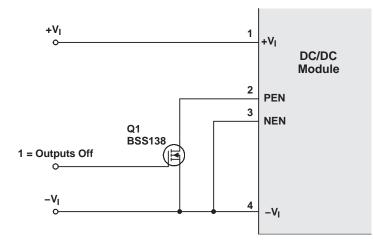

## Using the On/Off Enable Controls on the PTB78560x Auto-Track Compatible DC/DC Converters

The converter incorporates two output enable controls. PEN (pin 2) is the positive enable input, and NEN (pin 3) is the negative enable input. Both inputs are electrically referenced to  $-V_1$  (pin 4) on the primary or input side of the converter. The enable pins are ideally controlled with an open-collector (or open-drain) discrete transistor. Each input has an internal pullup resistor to a reference. There is no benefit to adding pullup resistors external to the module. If they are added, the maximum input voltage for these inputs must be limited to a maximum of 60 V.

### Automatic (UVLO) Power Up

Connecting NEN (pin 3) to  $-V_1$  (pin 4) and leaving PEN (pin 2) open-circuit, configures the converter for automatic power up. The converter control circuitry incorporates an undervoltage lockout (UVLO) function, which disables the converter until the minimum specified input voltage is present at  $\pm V_1$  (see the Electrical Characteristics table). The UVLO circuitry ensures a clean transition during power up and power down, allowing the converter to tolerate a slow rising input voltage. For most applications, the PEN and NEN enable controls can be configured for automatic power up.

#### Positive Output Enable (Negative Inhibit)

To configure the converter for a positive enable function, connect NEN (pin 3) to  $-V_1$  (pin 4), and apply the system On/Off control signal to PEN (pin 2). In this configuration, applying less than 0.8 V (with respect to  $-V_1$  potential) to pin 2 disables the converter output. Figure 23 gives an example circuit that uses a MOSFET transistor.

Figure 23. Positive Enable Configuration

# PTB78560A, PTB78560B PTB78560C

SLTS249-JUNE 2005

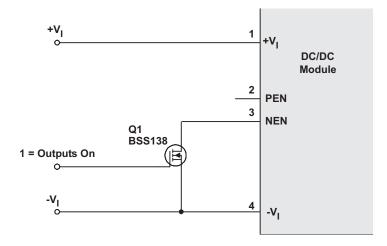

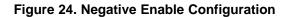

### **Negative Output Enable (Positive Inhibit)**

To configure the converter for a negative enable function, PEN (pin 2) is left open circuit, and the system On/Off control signal is applied to NEN (pin 3). A low-level control signal (less than 0.8 V) must then be applied to pin 3 to enable an output from the converter. An example of this configuration is detailed in Figure 24.

#### **On/Off Enable Turn-On Time**

Once enabled, the converter executes a soft-start power up. The converter exibits a short delay of approximately 7 ms, measured from the transition of the enable signal to the instance the Vo Bus output begins to rise. The output is in regulation within 20 ms.

Figure 25. Output Enable Power-Up Characteristic

## Sequenced Power Up with POL Modules

#### Overview

The main output from the PTB78560x converters is V<sub>o</sub>Bus. In power sequencing applications, V<sub>o</sub>Bus is used as the intermediate supply voltage for powering one or more *downstream* nonisolated power modules that incorporate Auto-Track<sup>TM1</sup>. The output voltage from Auto-Track compliant modules can be sequenced using a control input called Track. The Track input directly controls the output of a module from zero to its set-point voltage. The control is on a *volt-for-volt* basis, and allows multiple modules to follow a common analog signal during power-up events.

The Track signal attempts to start rising when the nonisolated modules are first powered from  $V_OBus$ . However, for proper sequencing, the voltage must be held at ground potential for at least 20 ms (40 ms for 12-V input modules) after  $V_OBus$  is in regulation. This is necessary to allow time for the nonisolated modules to complete their power-up initialization. The Track pin of each PTB78560x converter has an internal open-drain transistor that automatically holds the Track signal at ground potential to comply with this requirement.

The PTB78560B (1.8 V to 3.6 V) has a  $V_0$ Seq output.  $V_0$ Seq is internally derived from  $V_0$ Bus and regulated to the same set-point voltage. It has the added feature of being controlled by the Track input. During power up, this output can sequence with the outputs of the nonisolated modules powered from  $V_0$ Bus.

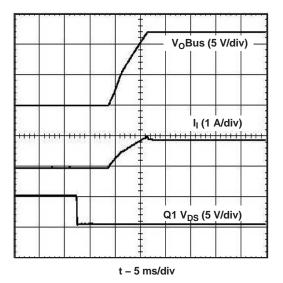

#### Auto-Track Features

Figure 26 shows a block diagram of the converter Auto-Track features. The components shaded are only present in the PTB78560B. During power up,  $V_0$ Bus rises promptly, after the converter is connected to a valid input source and its output is enabled.  $V_0$ Seq (PTB78560B) is the Auto-Track compatible output that is controlled by the voltage presented at the Track terminal. The control is active from 0 V up to a voltage just below the  $V_0$ Bus output. Between these limits, the voltage at  $V_0$ Seq follows that at the Track terminal. Once the Track voltage is at the  $V_0$ Bus voltage, raising it higher has no further effect. The voltage at  $V_0$ Seq cannot go higher than  $V_0$ Bus, and if connected to +Sense, it regulates at the set-point voltage.<sup>2</sup>

The Track input to the PTB78560x series of converters include a pullup resistor ( $R_{TRK}$ ) to  $V_OBus$ , and a 1-µF capacitor ( $C_{TRK}$ ) to -Sense. These components are standard on all Auto-Track compatible modules. They form an R–C time constant that cause the Track voltage to rise when the internal MOSFET is turned off. The unity-gain relationship between  $V_OSeq$  and the Track input is the same as all other Auto-Track compliant outputs.<sup>3</sup> The  $V_OSeq$  output also follows a compatible external ramp waveform applied to the Track pin.<sup>4, 5</sup> The internal MOSFET is designed to hold the Track voltage at ground potential for the required period after the  $V_OBus$  output is in regulation.

Note: Shaded functions are available only with the PTB78560B (3.3–V output)

Figure 26. Block Diagram of Auto-Track Features

#### Notes:

- Auto-Track compatible modules incorporate a Track input that can take direct control of the output voltage during power-up transistions. The control relationship is on a volt-for-volt basis and is active between the 0 V and the module set-point voltage. Once the Track input is above the set-point voltage, the module remains at its set-point. Connecting the Track input of a number of such modules together allows their outputs to follow a common control voltage during power up.

- 2. When +Sense is connected to the V<sub>O</sub>Seq output of the PTB78560B, the V<sub>O</sub>Seq output is tightly regulated to the set-point voltage. In this configuration, the voltage at the V<sub>O</sub>Bus output is up to 100 mV higher.

- 3. The V<sub>O</sub>Seq output on the PTB78560B cannot sink load current. This constraint does not allow the module to coordinate a sequenced power down.

- 4. The slew rate for the Track input signal must be between 0.1 V/ms and 1 V/ms. Above this range, the V<sub>o</sub>Seq output may no longer accurately follow the Track input voltage. A slew rate below this range may thermally stress the converter. These slew rate limits are automatically met whenever the Track voltage is controlled by the internal R-C time constant of the modules being sequenced.

- 5. If an external voltage is used to control the Track terminal, the source current **must** be limited. A resistance value of 2.74-k $\Omega$  is recommended for this purpose. This is necessary to protect the internal transistor to the converter. This transistor holds the track control voltage at ground potential for at least 20 ms after the V<sub>o</sub>Bus output is in regulation.

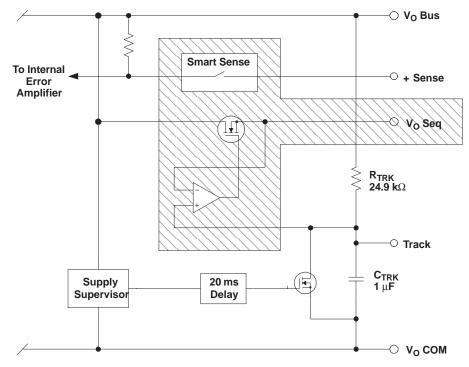

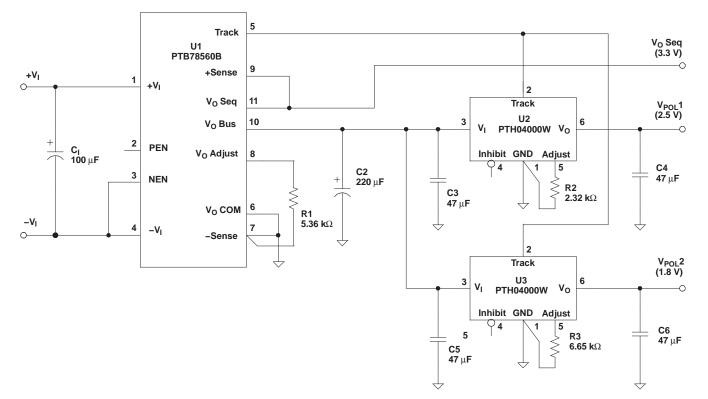

## Power-Up Sequencing With A Vo SEQ Output (PTB78560B)

Figure 28 shows the PTB78560B converter (U1) providing two 3.3-V sources. This allows it to both power and sequence with one or more *downstream* nonisolated modules. The example shows two 3.3-V input PTH04000W modules (U2 and U3), each rated for up to 3 A of output current. The selection and current rating of the nonisolated modules depends on the requirements of a specific application. The number of modules, their respective output voltage, and load current rating combine with the load required at the V<sub>O</sub>Seq output. The total must be supplied by the PTB78560B, and cannot exceed that available at the V<sub>O</sub>Bus output.

The output voltage adjust range of the PTB78560B is 1.8 V to 3.6 V. In these applications, the output voltage

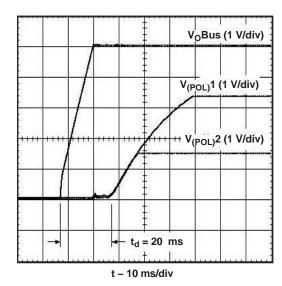

must always be set to 3.3 V (R1 = 5.36 k $\Omega$ ). This sets the output voltage of both the V<sub>O</sub>Bus and V<sub>O</sub>Seq outputs. The output voltage of the 3.3-V input (nonisolated) modules, U2 and U3, can be set to any voltage over the range, 0.8 V to 2.5 V. In this example, they are set to 2.5 V (R2 = 2.32 k $\Omega$ ) and 1.8 V (R3 = 6.65 k $\Omega$ ), respectively. Figure 27 shows the power-up waveforms from Figure 28 when the Track input to all three modules are simply connected together.

The converter provides input power to the downstream nonisolated modules via the V<sub>O</sub>Bus output. This output rises first to allow the nonisolated modules to complete their power-up initialization. The V<sub>O</sub>Seq (3.3 V), V<sub>(POL)</sub>1 (2.5 V) and V<sub>(POL)</sub>2 (1.8 V), outputs supply the load circuit, and rise simultaneously when the converter removes the internal ground signal to its own Track input. The V<sub>O</sub>Seq output rises with the outputs from the nonisolated modules, until it reaches its set-point voltage.

Figure 27. Power-Up Waveforms with POL Modules

♥ Texas Instruments

www.ti.com

Figure 28. Power-Up Sequencing With Nonisolated POL Modules

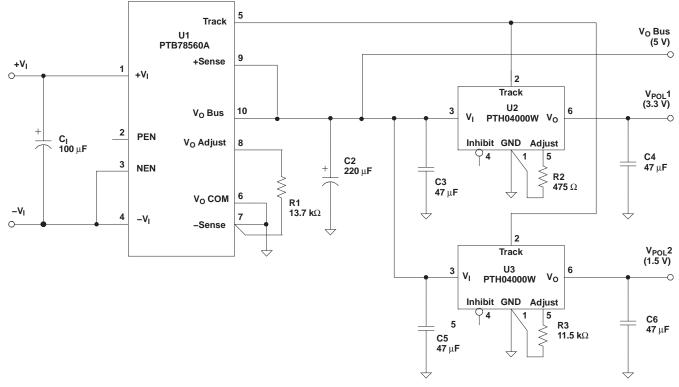

## Power-Up Sequencing Without A VoSEQ Output (PTB78560A/C)

Although the PTB78560A or PTB78560C do not have a  $V_0$ Seq output, they can provide the input power and coordinate the power-up sequencing to two or more nonisolated, Auto-Track compliant power modules. Figure 30 shows the PTB78560A (5 V) converter (U1) configured to provide both the input source and the power-up sequence timing to two 5-V input nonisolated modules. The example shows two PTH04000W modules (U2 and U3), each rated for up to 3 A of output current. In this case, the number of downstream modules, and their respective output voltage and load current rating, is only limited by the amount of current available at the  $V_0$ Bus output.

The output voltage of the PTB78560 must be set to a valid intermediate supply voltage. This depends on the input voltage requirements of the downstream modules. For 5-V input modules, the PTB78560A is selected and adjusted for an output of 5 V. For 12-V input modules, the PTB78560C is used and adjusted for an output of 12 V. U2 and U3, can be set to any voltage over their applicable adjustment range. In this example, they are again set to 2.5 V (R2 =  $2.32 \text{ k}\Omega$ ) and 1.8 V (R3 =  $6.65 \text{ k}\Omega$ ), respectively. Figure 29 shows the power-up waveforms from Figure 30 when the Track control of all three modules are simply connected together.

The PTB78560 converter (U1) provides the required intermediate voltage from the  $V_0Bus$  output to power the downstream modules, while holding the common Track control at ground potential. After allowing times for U2 and U3 to initialize, U1 removes the ground from the Track control, allowing this voltage to rise. The outputs from the two nonisolated modules then rise simultaneously to their respective set-point voltages.

Figure 29. Power-Up Waveform

Figure 30. Power-Up Sequencing With Nonisolated POL Modules

## **Stand-Alone Operation**

The wide output voltage adjust range makes either model of the PTB78560 series of converters an attractive product as a stand-alone dc/dc converter. In these applications, it is not required to power up or sequence with any nonisolated POL modules. The output voltage can be adjusted to any value within the applicable adjust range. The Auto-Track features are simply not used.

Figure 31 shows the recommended configuration when these converters are used as a stand-alone regulator. The main output ( $V_O$  Bus) can be used to supply the load directly. Both the Track pin and the  $V_O$  Seq output (PTB78560B) are simply left open circuit. The +Sense pin should be connected to the  $V_O$  Bus output for improved load regulation.

When the converter is operated in this mode, the output from V<sub>O</sub> Bus rises promptly on power up.

Figure 31. Stand-Alone Configuration

www.ti.com

## **PACKAGING INFORMATION**

| Orderable Device | Status <sup>(1)</sup> | Package Type            | Package<br>Drawing | Pins | Package Qty | Eco Plan <sup>(2)</sup> | Lead/<br>Ball Finish | MSL Peak Temp <sup>(3)</sup>               | Samples<br>(Requires Login) |

|------------------|-----------------------|-------------------------|--------------------|------|-------------|-------------------------|----------------------|--------------------------------------------|-----------------------------|

| PTB78560AAH      | ACTIVE                | Through-<br>Hole Module | ERW                | 11   | 12          | Pb-Free (RoHS)          | SN                   | N / A for Pkg Type                         | Request Free Samples        |

| PTB78560AAS      | ACTIVE                | Surface<br>Mount Module | ERY                | 11   | 12          | TBD                     | SNPB                 | Level-1-235C-UNLIM/<br>Level-3-260C-168HRS | Request Free Samples        |

| PTB78560AAZ      | ACTIVE                | Surface<br>Mount Module | ERY                | 11   | 12          | Pb-Free (RoHS)          | SNAGCU               | Level-3-260C-168 HR                        | Request Free Samples        |

| PTB78560BAH      | ACTIVE                | Through-<br>Hole Module | ERW                | 11   | 12          | Pb-Free (RoHS)          | SN                   | N / A for Pkg Type                         | Request Free Samples        |

| PTB78560BAS      | ACTIVE                | Surface<br>Mount Module | ERY                | 11   | 12          | TBD                     | SNPB                 | Level-1-235C-UNLIM/<br>Level-3-260C-168HRS | Request Free Samples        |

| PTB78560BAZ      | ACTIVE                | Surface<br>Mount Module | ERY                | 11   | 12          | Pb-Free (RoHS)          | SNAGCU               | Level-3-260C-168 HR                        | Request Free Samples        |

| PTB78560CAH      | ACTIVE                | Through-<br>Hole Module | ERW                | 11   | 12          | Pb-Free (RoHS)          | SN                   | N / A for Pkg Type                         | Request Free Samples        |

| PTB78560CAS      | ACTIVE                | Surface<br>Mount Module | ERY                | 11   | 12          | TBD                     | SNPB                 | Level-1-235C-UNLIM/<br>Level-3-260C-168HRS | Request Free Samples        |

| PTB78560CAZ      | ACTIVE                | Surface<br>Mount Module | ERY                | 11   | 12          | Pb-Free (RoHS)          | SNAGCU               | Level-3-260C-168 HR                        | Request Free Samples        |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.