## PCM78P

# 16-Bit Audio ANALOG-TO-DIGITAL CONVERTER

### **FEATURES**

- LOW COST/HIGH PERFORMANCE 16-BIT AUDIO A/D CONVERTER

- FAST 5µs MAX CONVERSION TIME (4µs typ)

- VERY LOW THD+N (typ -88dB at FS; max -82dB)

- ±3V INPUT RANGE

- TWO SERIAL OUTPUT MODES PROVIDE VERSATILE INTERFACING

- COMPLETE WITH INTERNAL REFERENCE AND CLOCK IN 28-PIN PLASTIC DIP

- ±5V TO ±15V SUPPLY RANGE (600mW Power Dissipation)

## DESCRIPTION

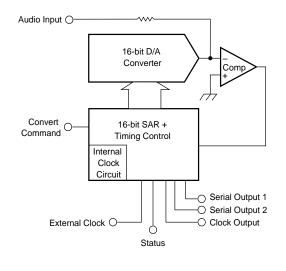

The PCM78P is a low-cost 16-bit analog-to-digital converter which is specifically designed and tested for dynamic applications. It features very fast, low distortion performance ( $4\mu$ s/–88dB THD+N typical) and is complete with internal clock and reference circuitry. The PCM78P is packaged in a reliable, low-cost 28-pin plastic DIP and data output is available in user-selectable serial output formats. The PCM78P is ideal for digital audio tape (DAT) recorders. Many similar applications such as digital signal processing and telecom applications are equally well served by the PCM78P.

The PCM78P uses a SAR technique. Analog and digital portions are efficiently partitioned into a high-speed, bipolar section and a low-power CMOS section. The PCM78P has been optimized for excellent dynamic performance and low cost.

### APPLICATIONS

- DSP DATA ACQUISITION

- TEST INSTRUMENTATION

- SAMPLING KEYBOARD SYNTHESIZERS

- DIGITAL AUDIO TAPE

- BROADCAST AUDIO PROCESSING

- TELECOMMUNICATIONS

International Airport Industrial Park • Mailing Address: PO Box 11400 • Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd. • Tucson, AZ 85706 Tel: (520) 746-1111 • Twx: 910-952-1111 • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

©1989 Burr-Brown Corporation

PDS-989A

## SPECIFICATIONS

### ELECTRICAL

At  $T_C = +25^{\circ}C$ ,  $+V_{DD} = +5V$ , and  $\pm V_{CC} = \pm 12V$ , and one minute warm-up in convection environment, unless otherwise noted.

|                                                  |                                                                 |                | PCM78P         |                |                         |

|--------------------------------------------------|-----------------------------------------------------------------|----------------|----------------|----------------|-------------------------|

| PARAMETER                                        | CONDITIONS                                                      | MIN            | TYP            | MAX            | UNITS                   |

| RESOLUTION                                       |                                                                 |                |                | 16             | Bits                    |

| INPUT/OUTPUT                                     |                                                                 |                |                |                | -                       |

| ANALOG INPUT                                     |                                                                 |                |                |                |                         |

| Input Range                                      |                                                                 | -3             |                | +3             | V                       |

| Input Impedance                                  |                                                                 |                | 1.5            |                | kΩ                      |

| DIGITAL INPUT/OUTPUT                             |                                                                 |                |                |                |                         |

| Logic Family                                     |                                                                 |                | Compatible C   |                |                         |

| Logic Level: V <sub>IH</sub>                     | I <sub>IH</sub> = +40μA<br>I <sub>II</sub> = -100μA             | +2<br>0        |                | +5.5<br>+0.8   | V<br>V                  |

| V <sub>IL</sub><br>V <sub>OH</sub>               | $I_{\rm IL} = -100\mu A$<br>$I_{\rm OH} = 2TTL \text{ Loads}$   | +2.4           |                | +0.0           | V V                     |

| V <sub>OL</sub>                                  | $I_{OI} = 2TTL Loads$                                           |                |                | +0.4           | v                       |

| Data Format                                      | 02                                                              | Se             | erial BOB or B | тс             |                         |

| Convert Command                                  |                                                                 |                | egative Edge   | (1)            |                         |

| Pulse Width                                      |                                                                 | 25             | 50             |                | ns                      |

| CONVERSION TIME                                  |                                                                 |                | 4              | 5              | μs                      |

| DYNAMIC CHARACTERISTICS                          |                                                                 |                |                |                | -                       |

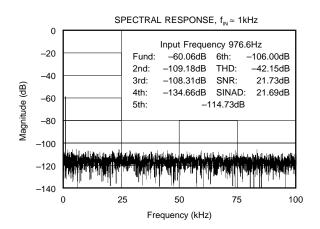

| SIGNAL-TO-NOISE RATIO (SNR) <sup>(2)</sup>       | $f_{S} = 200 \text{kHz}/\text{T}_{\text{CONV}} = 4 \mu s^{(3)}$ |                |                |                |                         |

| f = 1 kHz (0 dB)                                 | BW = 20kHz                                                      |                | 90             |                | dB <sup>(4)</sup>       |

| f = 10kHz (0dB)                                  | BW = 100kHz                                                     |                | 80             |                | dB                      |

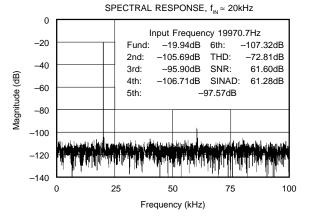

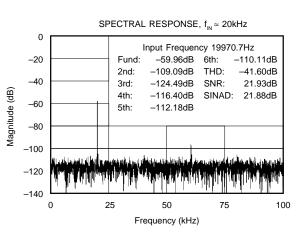

| TOTAL HARMONIC DISTORTION <sup>(5)</sup>         | $f_S = 200 \text{kHz}/\text{T}_{CONV} = 4 \mu \text{s}$         |                |                |                |                         |

| f = 1  kHz (0  dB)                               | BW = 20kHz                                                      |                | -91            |                | dB                      |

| f = 19kHz (0dB)<br>f = 10kHz (0dB)               | BW = 20kHz<br>BW = 100kHz                                       |                | -90<br>-90     |                | dB<br>dB                |

| f = 90 kHz (0 dB)                                | BW = 100 kHz                                                    |                | -89            |                | dB                      |

| TOTAL HARMONIC DISTORTION + NOISE <sup>(6)</sup> | $f_{S} = 200 \text{kHz/T}_{CONV} = 4 \mu \text{s}$              |                |                |                |                         |

| f = 1 kHz (0 dB)                                 | BW = 20 kHz                                                     |                | -88            | -82            | dB                      |

| f = 1kHz (-20dB)                                 | BW = 20kHz                                                      |                | -74            | -68            | dB                      |

| f = 1kHz (-60dB)                                 | BW = 20kHz                                                      |                | -34            |                | dB                      |

| f = 19kHz (0dB)                                  | BW = 20kHz<br>BW = 100kHz                                       |                | 87<br>82       |                | dB                      |

| f = 10kHz (0dB)<br>f = 90kHz (0dB)               | BW = 100 kHz $BW = 100 kHz$                                     |                | -82            |                | dB<br>dB                |

|                                                  |                                                                 |                |                |                |                         |

| ACCURACY                                         |                                                                 |                |                |                |                         |

| Gain Error                                       |                                                                 |                | ±2             |                | %                       |

| Bipolar Zero Error                               |                                                                 |                | ±20            |                | mV                      |

| Differential Linearity Error                     |                                                                 |                | ±0.002         |                | % of FSR <sup>(7)</sup> |

| Integral Linearity Error                         |                                                                 |                | ±0.003         |                | % of FSR                |

| Missing Codes                                    |                                                                 |                | None           |                | 14 Bits <sup>(8)</sup>  |

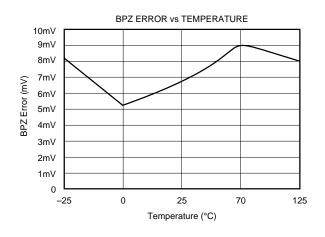

| DRIFT<br>Gain                                    | 0°C to +70°C                                                    |                | ±25            |                | nnm/%C                  |

| Bipolar Zero                                     | 0°C to +70°C                                                    |                | ±4             |                | ppm/°C<br>ppm of FSR/°C |

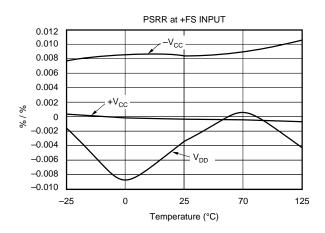

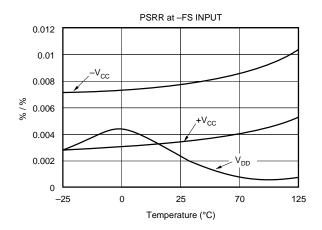

| POWER SUPPLY SENSITIVITY                         |                                                                 |                |                |                |                         |

| +V <sub>CC</sub>                                 |                                                                 |                | ±0.008         |                | %FSR/%V <sub>CC</sub>   |

| -V <sub>CC</sub>                                 |                                                                 |                | ±0.003         |                | %FSR/%V <sub>CC</sub>   |

| +V <sub>DD</sub>                                 |                                                                 |                | ±0.003         |                | %FSR/%V <sub>DD</sub>   |

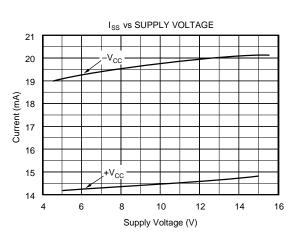

| POWER SUPPLY REQUIREMENTS                        |                                                                 |                |                | I              | <b>.</b>                |

| Voltage Range: +V <sub>CC</sub>                  |                                                                 | +4.75<br>-4.75 |                | +15.6<br>-15.6 | V<br>V                  |

| -V <sub>CC</sub><br>+V <sub>DD</sub>             |                                                                 | -4.75<br>+4.75 |                | +5.25          | V V                     |

| Current: +V <sub>CC</sub>                        | $+V_{CC} = +12V$                                                |                | +15            |                | mA                      |

| -V <sub>cc</sub>                                 | $-V_{CC} = -12V$                                                |                | -21            |                | mA                      |

| +V <sub>DD</sub>                                 | $+V_{DD} = +5V$                                                 |                | +7             |                | mA                      |

| Power Dissipation                                | $\pm V_{CC} = \pm 12V$                                          |                | 575            |                | mW                      |

| TEMPERATURE RANGE                                |                                                                 | 0              |                | 170            | 00                      |

| Specification                                    |                                                                 | 0              |                | +70            | °C                      |

| Storage                                          |                                                                 | -50            |                | +100           | °C                      |

NOTES: (1) When convert command is high, converter is in a halt/reset mode. Actual conversion begins on negative edge. See detailed text on timing for convert command description when using external clock. (2) Ratio of Noise rms/Signal rms. (3) f = input frequency;  $f_S =$  sample frequency (PCM78P and SHC702 in combination); BW = bandwidth of output (based on FFT or actual analog reconstruction using a 20kHz low-pass filter). (4) Referred to input signal level. (5) Ratio of Distortion rms/Signal rms. (7) FSR: Full-Scale Range = 6Vp-p. (8) Typically no missing Codes at 14-bit resolution.

### **PIN ASSIGNMENTS**

| 2<br>3<br>4 | Analog In<br>–V <sub>CC</sub><br>MSB Adjust<br>+V <sub>DD</sub> |   | Analog Signal Input (1.5kΩ impedance).<br>Analog power supply (–5V to –15V).                                                                        |

|-------------|-----------------------------------------------------------------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 3<br>4      | MSB Adjust<br>+V <sub>DD</sub>                                  | 1 | Analog power supply $(-5)/(to-15)/($                                                                                                                |

| 4           | +V <sub>DD</sub>                                                |   | A Analog power supply (-5 v to - 15 v).                                                                                                             |

|             |                                                                 |   | Internal adjustment point to allow adjustment of MSB major carry.                                                                                   |

| 5           |                                                                 | 1 | Power connection for comparator (+5V).                                                                                                              |

|             | No Connection                                                   | — | No internal connection.                                                                                                                             |

| 6           | Comparator Common                                               | 1 | Comparator common connection. Connect to ground.                                                                                                    |

| 7           | MSB                                                             | 0 | Parallel output of bit 1 (MSB) inverted.                                                                                                            |

| 8           | BTC/BOB Select                                                  | 1 | Two's complement (open) or straight binary (grounded) data output format selection.                                                                 |

| 9           | Status                                                          | 0 | Output signal held high until conversion is complete.                                                                                               |

| 10          | Clock Out                                                       | 0 | Internal clock output generated from RC network on pins 11 and 12 (also present when external clock is used lagging                                 |

|             |                                                                 |   | external clock by ~24ns and same duty cycle).                                                                                                       |

| 11          | R <sub>1</sub> C <sub>1</sub>                                   | 1 | RC connection point used to generate internal clock. Sets clock high time. See text for details.                                                    |

| 12          | $R_2C_2$                                                        | 1 | RC connection point used to generate internal clock. Sets clock low time. See text for details.                                                     |

| 13          | S <sub>OUT2</sub>                                               | 0 | Internal shift register containing the previous conversion result. (Alternate latched data output mode).                                            |

| 14          | +V <sub>DD</sub>                                                | 1 | Power connection for +5V logic supply.                                                                                                              |

| 15          | S <sub>OUT1</sub>                                               | 0 | Primary real-time data output synchronized to clock out.                                                                                            |

| 16          | External Clock                                                  | 1 | External clock input point (internal clock must be disabled).                                                                                       |

| 17          | Int/Ext Clock Select                                            | 1 | Selects either internal or external clock mode (low = internal; open = external).                                                                   |

| 18          | Short Cycle                                                     | 1 | Terminates conversion at less than 16 bits (open for 16-bit mode). See text for details.                                                            |

| 19          | Convert Command                                                 | 1 | Starts conversion process (can optionally be generated internally).                                                                                 |

| 20          | S <sub>OUT2</sub> Latch                                         | I | Latches previous conversion result for readout (must be issued with the S <sub>OUT2</sub> clock to initiate latch and an internal convert command). |

| 21          | S <sub>OUT2</sub> Clock                                         | 1 | Used to read out internally latched data from previous conversion.                                                                                  |

| 22          | Digital Common                                                  | 1 | Digital grounding pin.                                                                                                                              |

| 23          | +V <sub>CC</sub>                                                | 1 | Analog supply connection (+5V to +15V).                                                                                                             |

| 24          | V <sub>POT</sub>                                                | 0 | Voltage output (~2.5V) for optional adjustment of MSB transition.                                                                                   |

| 25          | Reference Decouple                                              | 1 | Reference decoupling point.                                                                                                                         |

| 26          | Analog Common                                                   |   | Analog grounding pin.                                                                                                                               |

| 27          | Reference Out                                                   | 0 | 2V reference out. Should not be used except as shown in connection diagram.                                                                         |

| 28          | Speed Up                                                        | Т | Connection point for a capacitor to speed reference settling. See text for details.                                                                 |

NOTE: Analog and digital commons are connected internally.

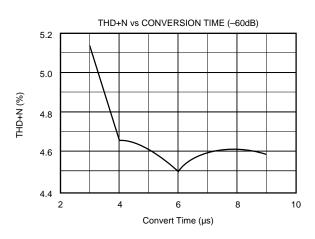

### **INPUT/OUTPUT RELATIONSHIPS**

|                                                     |                                                           | DIGITAL OUTPUT                               |                                              |

|-----------------------------------------------------|-----------------------------------------------------------|----------------------------------------------|----------------------------------------------|

| ANALOG INPUT                                        | CONDITION                                                 | BTC                                          | BOB                                          |

| +2.999908V<br>-3.000000V<br>0.000000V<br>-0.000092V | + Full Scale<br>–Full Scale<br>Bipolar Zero<br>Zero-1 LSB | 7FFF Hex<br>8000 Hex<br>0000 Hex<br>FFFF Hex | FFFF Hex<br>0000 Hex<br>8000 Hex<br>7FFF Hex |

### PACKAGE INFORMATION

| MODEL  | PACKAGE            | PACKAGE DRAWING<br>NUMBER <sup>(1)</sup> |

|--------|--------------------|------------------------------------------|

| PCM78P | 28-Pin Plastic DIP | 215                                      |

NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix D of Burr-Brown IC Data Book.

### **ABSOLUTE MAXIMUM RATINGS**

| +V <sub>CC</sub> to Analog Common            | 0 to +16.5V                     |

|----------------------------------------------|---------------------------------|

| -V <sub>CC</sub> to Analog Common            | 0 to -16.5V                     |

| -V <sub>DD</sub> to Analog Common            | 0 to +7V                        |

| Analog Common to Digital Common              | ±0.5V                           |

| Logic Inputs to Digital Common               | –0.3V to V <sub>DD</sub> + 0.5V |

| Analog Inputs to Analog Common               | ±16.5V                          |

| Lead Temperature (soldering, 10s)            | +300°C                          |

| Stresses above these ratings may permanently | damage the device.              |

|                                              |                                 |

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

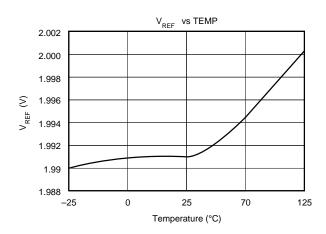

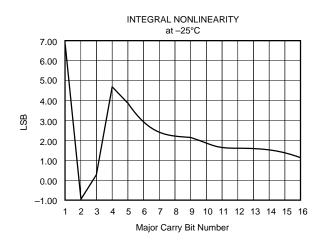

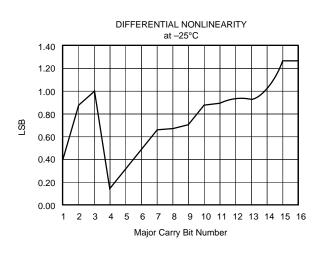

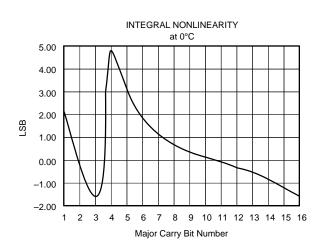

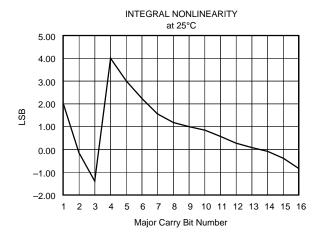

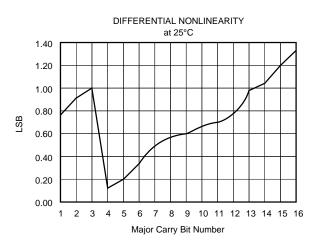

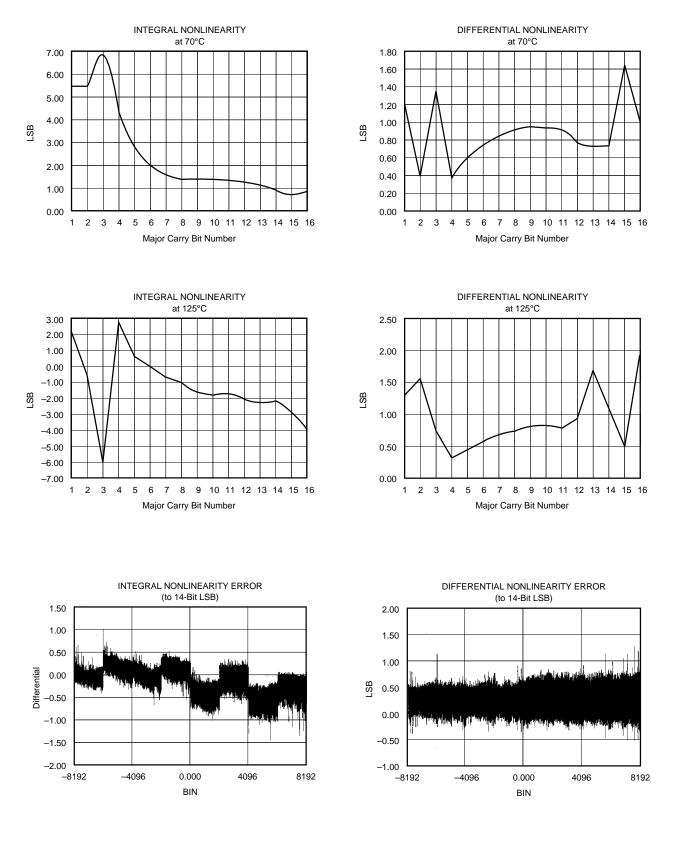

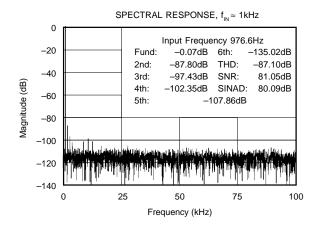

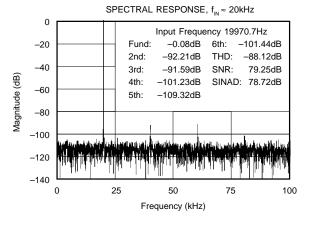

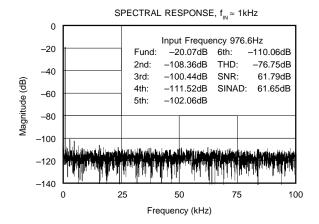

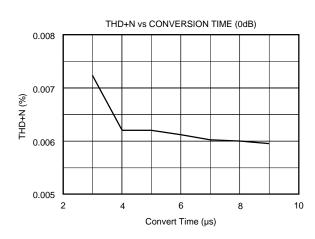

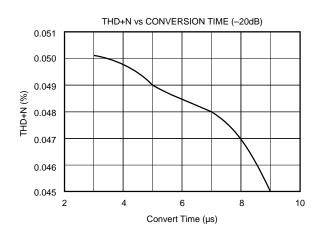

## **TYPICAL PERFORMANCE CURVES**

At T<sub>A</sub> = +25°C, V<sub>CC</sub> =  $\pm$ 15V, unless otherwise noted.

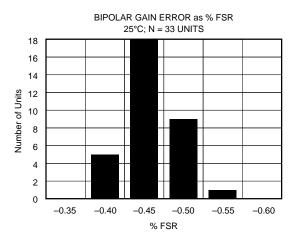

# **TYPICAL PERFORMANCE CURVES (CONT)**

At T<sub>A</sub> = +25°C, V<sub>CC</sub> =  $\pm$ 15V, unless otherwise noted.

## **TYPICAL PERFORMANCE CURVES (CONT)**

At  $T_A = +25^{\circ}C$ ,  $V_{CC} = \pm 15V$ , unless otherwise noted. Histograms done with conversion time = 8µs.

## **TYPICAL PERFORMANCE CURVES (CONT)**

At  $T_A = +25^{\circ}$ C,  $V_{CC} = \pm 15$ V, unless otherwise noted. Histograms done with Conversion Time = 8µs.

### TYPICAL PERFORMANCE CURVES (CONT)

At  $T_A = +25^{\circ}C$ ,  $V_{CC} = \pm 15V$ , unless otherwise noted.

## THEORY OF OPERATION

The PCM78P is a successive approximation A/D converter; this type of converter is well suited to high speed and resolution. The accuracy of a successive approximation converter is described by the transfer function shown in Figure 1. All successive-approximation A/D converters have an inherent quantization error of  $\pm 1/2$ LSB. The remaining errors in the A/D converter are combinations of analog errors due to the linear circuitry, matching and tracking properties of the ladder and scaling networks, power supply rejection, and reference errors. In summary, these errors consist of initial errors including Gain, Offset, Linearity, Differential Linearity, and Power Supply Sensitivity. Gain drift over temperature rotates the line (Figure 1) about zero, and Offset drift shifts the line left or right over the operating temperature range. Total Harmonic Distortion + Noise (THD+N) is a measure of the magnitude and distribution of the Linearity Error, Differential Linearity Error, and Noise, as well as quantization errors. The THD+N specification is most useful in audio or dynamic signal processing applications. To be useful, THD+N should be specified for both high level and low level input signals. This error is unadjustable and is the most meaningful indicator of A/D converter accuracy for dynamic applications.

### DYNAMIC RANGE

Dynamic range is a measure of the ratio of the smallest signals the converter can resolve to the full scale range and is usually expressed in decibels. The theoretical dynamic range of a converter is approximately  $6 \times n$ , where *n* is the number of bits of resolution. A 16-bit converter would thus have a theoretical dynamic range of 96dB. The actual useful dynamic range is limited by noise and linearity errors and is therefore somewhat less than the theoretical limit.

FIGURE 1. Input vs Output for Ideal Bipolar A/D Converter.

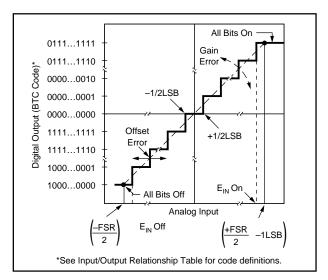

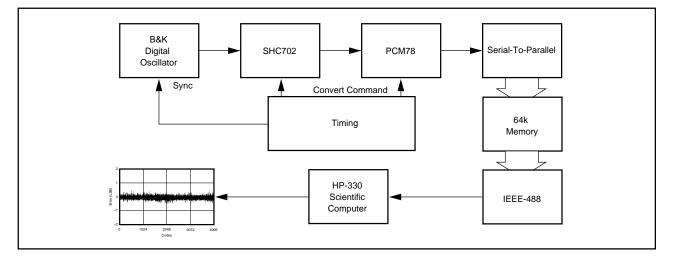

FIGURE 2. Block Diagram of Distortion Test Circuit.

### DISCUSSION OF SPECIFICATIONS

### TOTAL HARMONIC DISTORTION

Evaluating distortion specifications can be a difficult task, as distortion is often specified in different ways. Total Harmonic Distortion (THD) is defined as the ratio of the square root sum of the squares of the value of rms harmonics to the value of the rms fundamental and is expressed in percent or dB. Note that this measurement only includes energy present in those frequencies which would contain harmonics, and therefore is less than Total Harmonic Distortion plus Noise.

The Total Harmonic Distortion plus Noise (THD+N) is defined as the ratio of the square root of the sum of the squares of the value of the rms harmonics and rms noise to the value of the rms fundamental and is expressed in percent or dB. This is the most meaningful measurement of a dynamic converter's performance because it includes all energy present in the signal that is not fundamental. A block diagram of the test circuit used to measure the THD and THD+N of the PCM78 is shown in Figure 2. This digital system is capable of differentiating harmonic energy and noise; conventional distortion analyzers which operate on a tracking notch filter principle cannot distinguish this energy, and therefore only measure THD+N. Unfortunately, in the past, these systems were used for measuring distortion performance of converters, and the distortion was often simply specified as "THD", when in fact it was really THD+N. For this reason, it is often confusing to compare specifications of converters unless one knows exactly what was being measured.

If we assume that the error due to the test circuit of Figure 2 is negligible, then the rms value of the PCM78 error referred to the input can be shown to be

THD+N =

$$\frac{\sqrt{\frac{1}{N}\sum_{i=1}^{N} \left[E_{L}(i) + E_{Q}(i) + E_{N}(i)\right]^{2}}}{E_{rms}} X \ 100\%$$

where N is the number of samples,  $E_L(i)$  is the linearity error at each sample,  $E_Q(i)$  is the quantization error at each

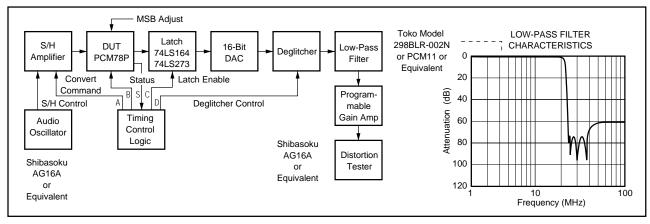

FIGURE 3. Block Diagram of Histogram Test.

FIGURE 4. Production Distortion + Noise Test System Block Diagram.

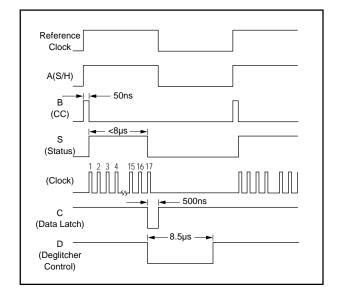

FIGURE 5. Timing Diagram for Figure 4.

sample, and  $E_{N}(i)$  is the residual noise energy present at each sample. Similarly, THD alone can be expressed as

$$THD = \frac{\sqrt{\frac{1}{N}\sum_{i=1}^{N} \left[E_{L}(i)\right]^{2}}}{E_{ms}} X 100\%$$

These expressions indicate that there is a correlation between THD+N and the square root of the sum of the squares of the linearity errors at each digital word of interest. In order to find this error at each code, a histogram test must be performed on the PCM78, as illustrated in Figure 3. The histogram for every converter is unique, as the linearity errors from converter to converter will vary in their placement along the transfer function. Typical histogram data is shown in the Typical Curves.

However, this expression for THD+N does not mean that the worst case linearity error of the A/D is directly correlated to the THD+N because the digital output words from theA/D vary according to the amplitude and frequency of the sine wave input as well as the sampling frequency. For the PCM78 the test sampling frequency was chosen to be 200kHz, near the PCM78's fastest rate of conversion. The test frequencies used vary within the audio range, and are stepped in amplitude from 0dB, to -20dB, to -60dB.

In manufacturing the PCM78, the test system shown in Figure 4 is used to test for guaranteed THD+N.

### ACCURACY VS CONVERSION TIME AND INPUT SIGNAL LEVEL

The relationship of THD vs input signal level and THD vs conversion time is shown is the typical curves. Slowing the conversion time to more than  $8\mu s$  results in little added benefit in terms of THD+N.

For applications which are not as concerned with dynamic performance but require DC accuracy and linearity, it is best to use the PCM78 at the longest conversion time possible for the system requirements. Slowing the PCM78 to  $8\mu$ s- $10\mu$ s conversion time results in a substantial improvement in linearity. The typical curves show DNL and INL plots for a typical device, at an  $8\mu$ s conversion time. Due to the segmented architecture of the internal DAC used in the successive approximation conversion technique, significant differential linearity errors occur near bits 3 and 4. Allowing more settling time for the DAC (by slowing the conversion speed) will improve this differential linearity error and give equivalent performance to more costly DC-specified 12-bit to 14-bit A/D converters.

### SYSTEM DESIGN CONSIDERATIONS

### DIGITAL CIRCUIT CONNECTIONS

The PCM78 comes complete with an internal clock circuit, or it may be clocked by an external clock. Choosing which mode to operate with depends upon the application for which the PCM78 will be used. In an application where the sample rate may not be fixed (transient recording, etc.), using the internal clock set to give a very fast conversion may be the best solution. In systems where the sample rate is fixed, an external clock is probably the better choice since it will allow the digital system design to be synchronous.

In either case, the PCM78 requires 17 clock cycles to complete a conversion. To calculate the clock frequency necessary for a given conversion time, the following equation may be used:

$$f_{CLOCK} = \frac{17}{Conversion Time}$$

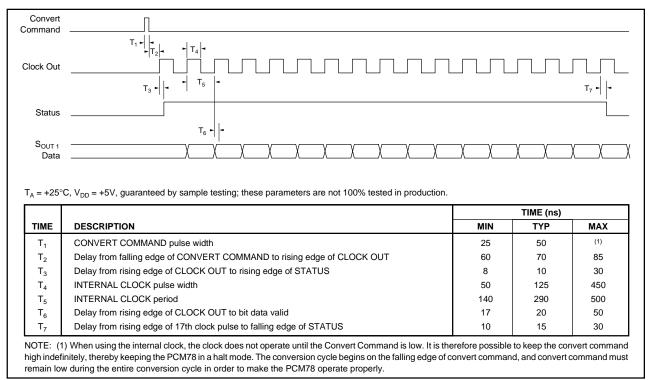

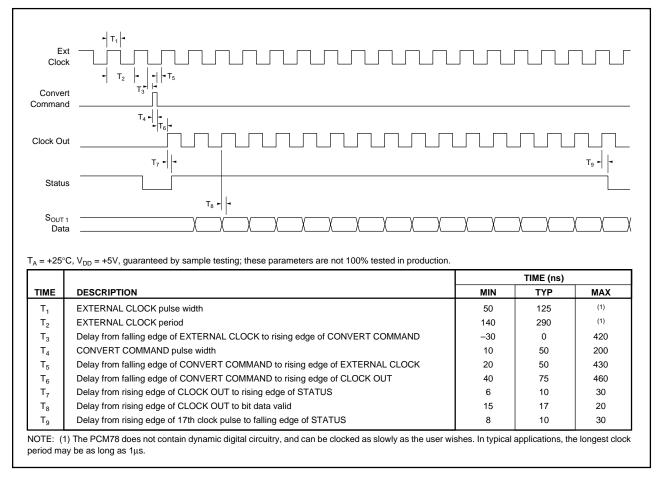

The internal clock operates only during a conversion, and is gated on by the falling edge of the convert command. See Figure 6. The internal clock is available on pin 10, Clock Out. The high and low time of this clock is set by  $R_1C_1$  and  $R_2C_2$  respectively. The duty cycle of the clock should be between 20% to 80%, and may be set to 50% for simplicity.

Clock High Time (in ns) =

$$1.32R_1C_1$$

Clock Low Time (in ns) =  $1.32R_2C_2$

R in k $\Omega$ ; C in pF.

These equations are approximate  $(\pm 5\%)$ ; they should be used for determining an initial part value which will then need to be "tweaked" for accurate timing. If highly accurate time bases are required, use of an external clock is recommended.

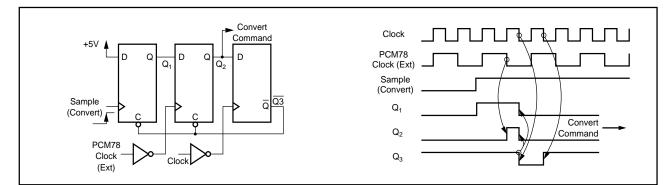

The external clock is applied at pin 16, and the Int/Ext Clock select (pin 17) should be left open (an internal pullup resistor assures that the logical state of an open pin is "1"). Using the external clock requires careful placement in time of the convert command. Figure 7 diagrams the recommended timing with an external clock. A simple circuit which assures the proper timing of the convert command is shown in Figure 8.

Due to the design of the Clock/Logic chip in the PCM78, a conversion is begun inside the PCM78 by an asynchronous

state machine. This places stringent requirements on the timing of the convert command, as improper timing can cause metastable states within this state machine. Using the circuitry shown in Figure 8, the user is assured of consistent operation, and these invalid states within the state machine are entirely avoided. (Note that this is not a consideration when using an internal clock, as nothing is being clocked when a convert command is presented to the PCM78).

The Clock Out function is a gated form of the external clock, i.e. the 17 clock cycles used in the conversion are present on this pin during conversion. This allows use of a continuous external clock, with Clock Out being the clock that the converter is actually using for conversion. Note that this is simply a delayed (~24ns) version of the external clock, and will have the same frequency and duty cycle.

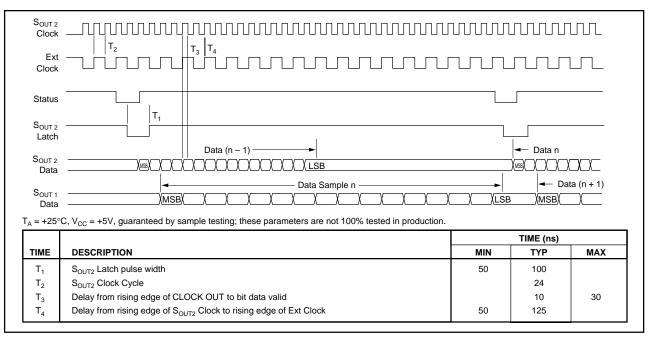

The  $S_{OUT2}$  Latch enables the user to latch data from the previous conversion and read it out at a higher speed than the convert clock. This feature allows the converter to easily interface to digital filtering necessary for oversampling. See Figure 9 for timing information in this mode.

In this mode, the PCM78 generates its own internal convert command when the  $S_{OUT2}$  Clock goes high within ±50ns of  $S_{OUT2}$  Latch going low; the external convert command may not be used, and pin 19 must be grounded. The timing diagram shows the recommended timing for using this mode. After the  $S_{OUT2}$  Latch control signal goes low, data from the SAR is loaded into the  $S_{OUT2}$  latch on the next rising edge of the  $S_{OUT2}$  Clock. This clock edge should occur prior to the next rising edge of the conversion clock (internal or external), since the SAR will reset itself prior to the latching

FIGURE 6. Conversion Timing when using Internal Clock.

FIGURE 7. Conversion Timing when using External Clock.

if the convert clock rises before the  $S_{OUT2}$  Clock. This condition is avoided as long as the frequency of  $S_{OUT2}$  Clock is at least 1.5 times that of the conversion clock.

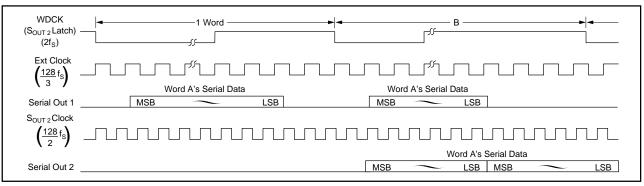

The internal convert command is generated upon  $S_{OUT2}$ Latch going low, and its falling edge occurs upon the first falling edge of  $S_{OUT2}$  Clock after  $S_{OUT2}$  Latch goes low.  $S_{OUT2}$  Latch should remain low for at least 2 cycles of  $S_{OUT2}$ Clock to insure proper latching. In many applications, the  $S_{OUT2}$  Latch can be the  $2f_S$  signal present in many digital audio systems, typically known as WDCK. Figure 10 includes an example of this application. The data read out on  $S_{OUT2}$  is from the conversion previously performed, while the data that is present on  $S_{OUT1}$  is the real time readout of the successive approximation as it occurs.

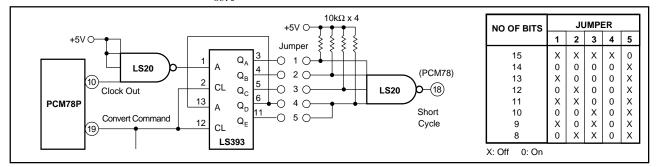

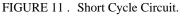

### SHORT CYCLE

The PCM78 has the ability to be short cycled to a resolution less than 16 bits. This is accomplished by driving the Short Cycle pin (pin 18) low when the conversion is to be terminated, and holding it low until the next convert command is given. The circuit in Figure 11 will accomplish this function.

FIGURE 8. Convert Command Timing Circuit for Use with External Clock.

FIGURE 9. Timing when using  $S_{OUT2}$  Latch.

FIGURE 10. Application Example of  $S_{OUT 2}$  Operation.

PCM78

If Short Cycle is not held low until the next convert command is issued, the Status line will go high in synchronization with Short Cycle. This is because the operation of the Status line becomes invalid after Short Cycle is asserted. An example of the Short Cycle operation is shown in Figure 12.

In those systems where a user may not be using a continuous external clock, it is necessary to assure that a falling edge of external clock occurs after short cycle goes low. This is because conversion actually stops on the first falling edge of external clock after Short Cycle goes low.

### ANALOG CIRCUIT CONSIDERATIONS

#### **Layout Precautions**

Analog and Digital Common are connected internally in the PCM78, and should be connected together as close to the unit as possible, preferably to a large ground plane under the ADC. Low impedance analog and digital common returns are essential for low noise performance. Coupling between analog inputs and digital lines should be minimized by careful layout. The input pin (pin 1) and the MSB adjust pin (pin 3) are both extremely sensitive to noise; digital lines should be kept away from these pins to avoid coupling digital noise into the sensitive analog circuitry.

Contact factory for a recommended PCB layout for the PCM78.

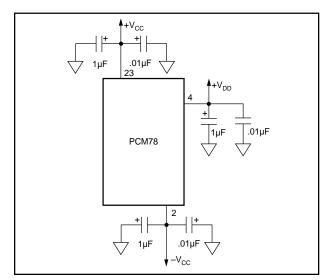

#### **Power Supply Decoupling**

The power supplies should be bypassed with tantalum or electrolytic capacitors as shown in Figure 13 to obtain noise free operation. These capacitors should be located as close to the ADC as possible. Bypass the 1 $\mu$ F electrolytic capacitors with 0.01 $\mu$ F ceramic or polystyrene capacitors for improved high frequency performance.

### **Reference Decoupling and Speed Up**

In order to assure the lowest noise operation of the PCM78, the reference may be bypassed by three different capacitors. Pin 25 is a decoupling point for the reference to  $-V_{CC}$ . The

decoupling capacitor should range from  $0.1\mu$ F to  $4.7\mu$ F; larger values can cause reference settling problems which may manifest themselves as missing codes. This capacitor should be as close to the PCM78 as possible, to minimize the potential for coupling noise into the device; with a good board layout it may be best to leave this capacitor out of the circuit altogether, as the extra lead length may only cause more noise in the reference.

Pin 27 is a decoupling point to ground, as well as the output of the 2V reference. This point should not be used to supply reference voltage to external circuitry unless it is buffered. A 2.2 $\mu$ F capacitor is recommended, and the capacitor used here should not exceed 4.7 $\mu$ F.

Pin 28, the Speed Up pin, allows a capacitor to be connected to ground to facilitate reference settling. This does not speed up the conversion time, but it does reduce odd order harmonic distortion. As with the decoupling capacitor on pin 25, this may also contribute to noise; if harmonic content is most important in an application, this capacitor  $(0.1\mu F - 10\mu F)$  should be connected. In all other cases, it is best to leave the capacitor out of the circuit.

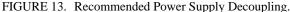

#### **Input Scaling**

The analog input should be scaled as close to the maximum input signal range as possible in order to utilize the maximum signal resolution of the A/D converter. The DAC inside the PCM78 has a  $\pm 2$ mA range, and the nominal  $\pm 3$ V input is scaled by a 1.5k $\Omega$  resistor. In order to scale to other ranges, see Table I for recommended scaling resistor values, connected as shown in Figure 14.

| INPUT RANGE | R     |  |  |  |

|-------------|-------|--|--|--|

| ±10V        | 8.2kΩ |  |  |  |

| ±5V         | 3.3kΩ |  |  |  |

|             |       |  |  |  |

NOTE: R values shown assume use of 1k trim pot to adjust for scale accuracy.

TABLE I. PCM78 Input Scaling Resistor Values.

FIGURE 14. PCM78 Input Scaling Circuit.

#### **INPUT IMPEDANCE**

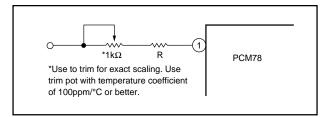

The input signal to the PCM78 should come from a low impedance source, such as the output of an op amp, to avoid any errors due to the dynamic input impedance that a successive-approximation converter presents to the outside world because of the changing currents in this circuit during conversion as the converter steps through its approximations.

If the driving circuit output impedance is not low, a buffer amplifier should be added between the input signal and the direct input to the PCM78 as shown in Figure 15.

FIGURE 15. Buffer Amplifier for PCM78 Input.

### **MSB** Adjustment

Differential Linearity errors at bipolar zero and THD are guaranteed to meet data sheet specifications without any external adjustment. However, a provision has been made for an optional adjustment of the MSB linearity point which makes it possible to eliminate DLE error at BPZ. This is important when the signal level is very low, because zero crossing noise (DLE at BPZ) becomes very significant when compared to the small codes changes occurring in the LSB portion of the converter.

The PCM78 is laser trimmed for best performance at the factory without the MSB adjust circuitry installed; if better performance can be obtained it would be by the addition of the MSB adjust circuitry shown in Figure 16.

The best method of adjusting the MSB is by using a real time FFT routine to monitor the levels of odd order harmonics when a sine-wave is being digitized by the PCM78. Adjusting the potentiometer in Figure 16 will allow the user to reduce the magnitude of odd-order harmonics.

An alternate method is to reconstruct the data out of the PCM78 through a DAC, and measure THD+N on a conventional distortion analyzer. Adjust the potentiometer for minimum THD+N.

FIGURE 16. MSB Adjust Circuit.

### **APPLICATIONS INFORMATION**

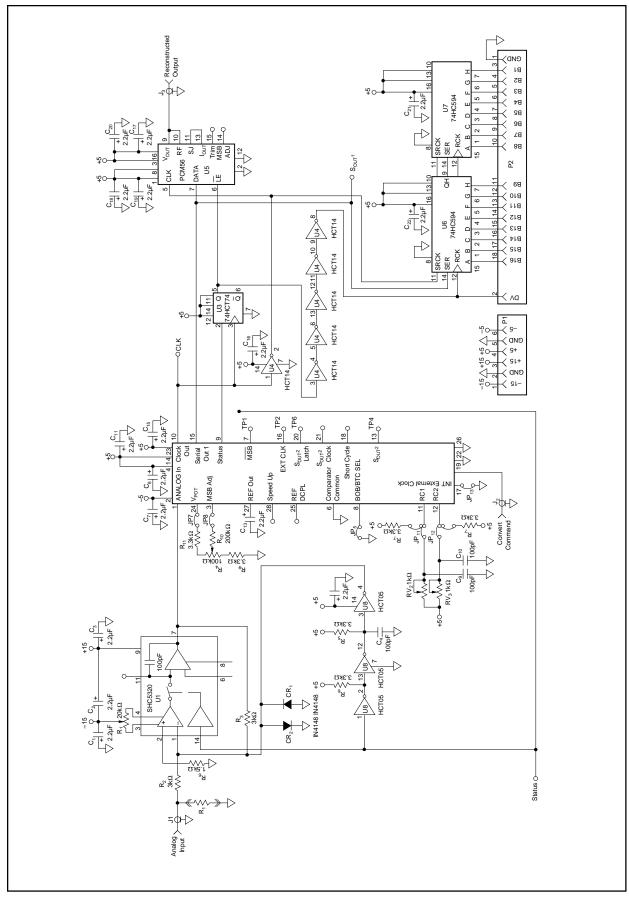

A typical digitization circuit, used on the demonstration board available for the PCM78, is shown in Figure 20. The connections and part values shown in this circuit have been optimized for the best THD+N performance at a 200kHz sample rate.

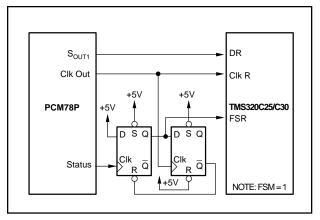

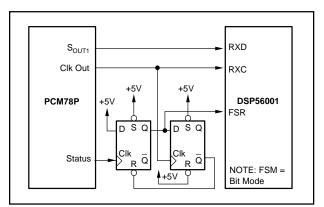

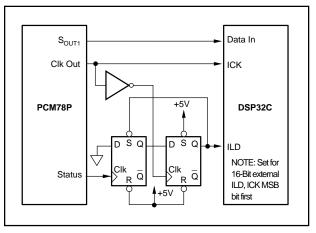

The PCM78 may be interfaced to many popular digital signal processors, such as the TMS320, DSP56001, and the DSP32. Suggested interface circuits for these processors are shown in Figures 17-19.

FIGURE 17. PCM78 Interface to TMS320C25/C30 DSP Processors.

FIGURE 18. PCM78 Interface to Motorola DSP56001 DSP Processor.

FIGURE 19. PCM78 Interface to AT&T DSP16 & DSP32C Processors.

FIGURE 20. Schematic for Demonstration Board (DEM1122).

### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 2000, Texas Instruments Incorporated