SBAS407C-DECEMBER 2006-REVISED AUGUST 2009

# High-Performance, Two-Channel, 24-Bit, 216kHz Sampling Multi-Bit Delta-Sigma Analog-to-Digital Converter

#### **FEATURES**

- Supports Linear PCM Output Data

- Output Sampling Rates from 8kHz to 216kHz

- Differential Voltage Inputs

- On-Chip Voltage Reference Improves Power-Supply Noise Rejection

- Dynamic Performance (24-bit word length)

- Dynamic Range (–60dB input, A-weighted):

123dB typical

- Dynamic Range (-60dB input, 20kHz bandwidth): 121dB typical

- Total Harmonic Distortion + Noise (-1dB input, 20kHz bandwidth):

-108dB typical

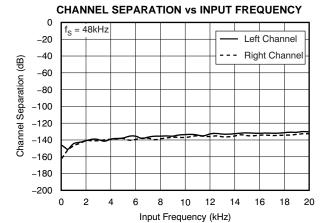

- Channel Separation: 135dB

- Low Power Dissipation:

- 305mW typical for 48kHz sampling rate

- 330mW typical for 96kHz sampling rate

- 340mW typical for 192kHz sampling rate

- Linear Phase Digital Decimation Filtering

- Select from Classic or Low Group Delay Filter Responses

- Low Passband Ripple Classic: ±0.00015dB

Low Group Delay: ±0.001dB

- Digital High-Pass Filtering Removes DC Offset

- Left and Right Channel Filters May Be Disabled Independently

- Audio Serial Port Interface

- Master or Slave Mode Operation

- Supports Left-Justified, I<sup>2</sup>S™, and TDM Data Formats

- Output Word Length Reduction

- Overflow Indicators for the Left and Right Channels

- Analog Power Supply: +4.0V nominal

- Digital Power Supply: +3.3V nominal

- Power-Down Mode: 4mW typical

- Package: TQFP-48, RoHS compliant

#### **APPLICATIONS**

- Digital Audio Recorders and Mixing Desks

- Digital Live Sound Consoles

- Digital Audio Effects Processors

- Surround Sound Encoders

- Broadcast Studio Equipment

- Data Acquisition and Measurement Systems

- Audio Test Systems

- Sonar

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Windows is a registered trademark of Microsoft Corporation. I2S is a trademark of NXP Semiconductor.

All other trademarks are the property of their respective owners.

#### **DESCRIPTION**

The PCM4220 is a high-performance, two-channel analog-to-digital (A/D) converter designed for use in professional audio applications. Offering outstanding dynamic performance, the PCM4220 provides 24-bit linear PCM output data, with support for output word length reduction to 20-, 18-, or 16-bits. The PCM4220 includes three sampling modes, supporting output sampling rates from 8kHz to 216kHz. The PCM4220 is ideal for a variety of digital audio recording and processing applications.

A linear phase digital decimation filtering engine supports Classic and Low Group Delay filter responses, allowing optimization for either studio or live sound applications. In addition, digital high-pass filtering is provided for DC offset removal. The The PCM4220 is configured using dedicated control pins for selection of sampling modes, audio data formats and word length, decimation filter response, high-pass filter disable, and reset/power-down functions.

While providing uncompromising performance, the PCM4220 addresses power concerns with just over 300mW typical total power dissipation, making the device suitable for multi-channel audio systems. The PCM4220 is typically powered from a +4.0V analog supply and a +3.3V digital supply. The digital I/O is logic-level compatible with common digital signal processors, digital interface transmitters, and programmable logic devices. The PCM4220 is available in a TQFP-48 package, which is RoHS-compliant.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### ORDERING INFORMATION

For the most current package and ordering information, see the Package Option Addendum at the end of this data sheet, or see the TI website at www.ti.com

#### **ABSOLUTE MAXIMUM RATINGS**(1)

Over operating free-air temperature range, unless otherwise noted.

|                                                  | VALUE                        |

|--------------------------------------------------|------------------------------|

| Power supplies                                   |                              |

| VCC1, VCC2                                       | -0.3V to +6.0V               |

| VDD                                              | -0.3V to +4.0V               |

| Digital input voltage                            |                              |

| All digital input and I/O pins                   | -0.3V < (VDD + 0.3V) < +4.0V |

| Analog input voltage                             |                              |

| VINL+, VINL-, VINR+, VINR-                       | -0.3V < (VCC + 0.3V) < +6.0V |

| Input current (all pins except power and ground) | ±10mA                        |

| Ambient operating temperature                    | -40°C to +85°C               |

| Storage temperature                              | −65°C to +150°C              |

(1) These limits are stress ratings only. Stresses beyond these limits may result in permanent damage. Extended exposure to absolute maximum ratings may degrade device reliability. Normal operation or performance at or beyond these limits is not specified or ensured.

www.ti.com

#### **ELECTRICAL CHARACTERISTICS: DIGITAL AND DYNAMIC PERFORMANCE**

All specifications are at  $T_A = +25$ °C, VCC1 = VCC2 = +4.0V, and VDD = +3.3V, unless otherwise noted.

|                                                              |                        |           | PCM4220 |                  |      |

|--------------------------------------------------------------|------------------------|-----------|---------|------------------|------|

| PARAMETER                                                    | CONDITIONS             | MIN       | TYP     | MAX              | UNIT |

| DIGITAL I/O CHARACTERISTICS<br>(Applies to all digital pins) |                        |           |         |                  |      |

| High-level input voltage, V <sub>IH</sub>                    |                        | 0.7 × VDD |         | VDD              | V    |

| Low-level input voltage, V <sub>IL</sub>                     |                        | 0         |         | $0.3 \times VDD$ | V    |

| High-level input current, I <sub>IH</sub>                    |                        |           | 1       | 10               | μА   |

| Low-level input current, I <sub>IL</sub>                     |                        |           | 1       | 10               | μΑ   |

| High-level output voltage, V <sub>OH</sub>                   | $I_O = -2mA$           | 0.8 × VDD |         | VDD              | V    |

| Low-level output voltage, V <sub>OL</sub>                    | I <sub>O</sub> = +2mA  | 0         |         | 0.2 × VDD        | V    |

| Input capacitance, C <sub>IN</sub>                           |                        |           | 3       |                  | pF   |

| PCM OUTPUT SAMPLING RATE, f <sub>S</sub>                     |                        |           |         |                  |      |

|                                                              | Normal mode            | 8         |         | 54               | kHz  |

|                                                              | Double Speed mode      | 54        |         | 108              | kHz  |

|                                                              | Quad Speed mode        | 108       |         | 216              | kHz  |

| MASTER CLOCK INPUT                                           |                        |           |         |                  |      |

| Normal mode, MCKI = 256f <sub>S</sub>                        |                        | 2.048     |         | 13.824           | MHz  |

| Double Speed mode, MCKI = 128f <sub>S</sub>                  |                        | 6.912     |         | 13.824           | MHz  |

| Quad Speed mode, MCKI = 64f <sub>S</sub>                     |                        | 6.912     |         | 13.824           | MHz  |

| DYNAMIC PERFORMANCE <sup>(1)</sup>                           |                        |           |         |                  |      |

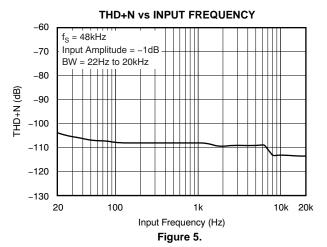

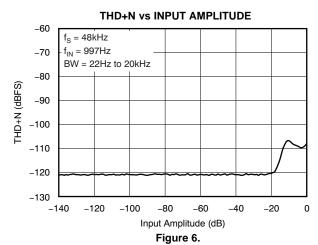

| PCM Output, Normal Mode, f <sub>S</sub> = 48kHz              | BW = 22Hz to 20kHz     |           |         |                  |      |

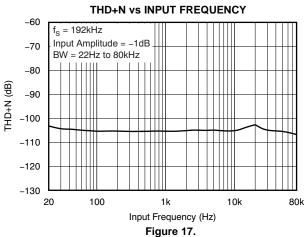

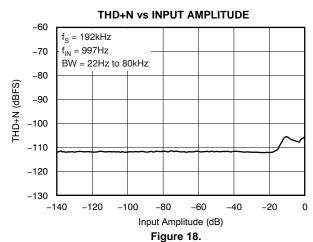

| Total harmonic distortion + noise (THD+N)                    | f = 997Hz, -1dB input  |           | -108    | -100             | dB   |

|                                                              | f = 997Hz, -20dB input |           | -100    |                  | dB   |

|                                                              | f = 997Hz, -60dB input |           | -61     |                  | dB   |

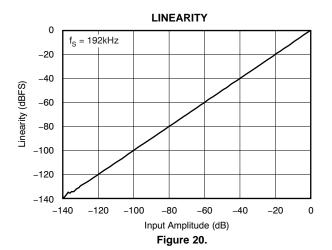

| Dynamic range, no weighting                                  | f = 997Hz, -60dB input |           | 121     |                  | dB   |

| Dynamic range, A-weighted                                    | f = 997Hz, -60dB input | 118       | 123     |                  | dB   |

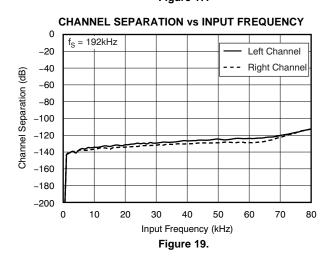

| Channel separation                                           | f = 10kHz, -1dB input  | 115       | 135     |                  | dB   |

| PCM Output, Double Speed Mode, f <sub>S</sub> = 96kHz        | BW = 22Hz to 40kHz     |           |         |                  |      |

| Total harmonic distortion + noise (THD+N)                    | f = 997Hz, -1dB input  |           | -108    |                  | dB   |

|                                                              | f = 997Hz, -20dB input |           | -98     |                  | dB   |

|                                                              | f = 997Hz, -60dB input |           | -58     |                  | dB   |

| Dynamic range, no weighting                                  | f = 997Hz, -60dB input |           | 118     |                  | dB   |

| Dynamic range, A-weighted                                    | f = 997Hz, -60dB input |           | 123     |                  | dB   |

| Channel separation                                           | f = 10kHz, -1dB input  |           | 135     |                  | dB   |

| PCM Output, Quad Speed Mode, f <sub>S</sub> = 192kHz         | BW = 22Hz to 40kHz     |           |         |                  |      |

| Total harmonic distortion + noise (THD+N)                    | f = 997Hz, -1dB input  |           | -107    |                  | dB   |

|                                                              | f = 997Hz, -20dB input |           | -98     |                  | dB   |

|                                                              | f = 997Hz, -60dB input |           | -58     |                  | dB   |

| Dynamic range, no weighting                                  | f = 997Hz, -60dB input |           | 118     |                  | dB   |

| Dynamic range, A-weighted                                    | f = 997Hz, -60dB input |           | 123     |                  | dB   |

| Channel separation                                           | f = 10kHz, -1dB input  |           | 135     |                  | dB   |

| PCM Output, Quad Speed Mode, f <sub>S</sub> = 192kHz         | BW = 22Hz to 80kHz     |           |         |                  |      |

| Total harmonic distortion + noise (THD+N)                    | f = 997Hz, -1dB input  |           | -106    |                  | dB   |

|                                                              | f = 997Hz, -20dB input |           | -91     |                  | dB   |

|                                                              | f = 997Hz, -60dB input |           | -52     |                  | dB   |

| Dynamic range, no weighting                                  | f = 997Hz, -60dB input |           | 112     |                  | dB   |

| Dynamic range, A-weighted                                    | f = 997Hz, -60dB input |           | 123     |                  | dB   |

| Channel separation                                           | f = 10kHz, -1dB input  |           | 135     |                  | dB   |

<sup>(1)</sup> Typical PCM output performance is measured and characterized with an Audio Precision SYS-2722 192kHz test system and a PCM4222EVM evaluation module modified for use with the PCM4220. Measurement bandwidth and weighting settings are noted in the *Parameter* and *Conditions* columns. THD+N is measured without the use of weighting filters. Master mode operation is utilized for all typical performance parameters, with the master clock input frequency (MCKI) set to 12.288MHz.

Copyright © 2006–2009, Texas Instruments Incorporated

#### **ELECTRICAL CHARACTERISTICS: DIGITAL AND DYNAMIC PERFORMANCE (continued)**

All specifications are at  $T_A = +25$ °C, VCC1 = VCC2 = +4.0V, and VDD = +3.3V, unless otherwise noted.

|                                                                        |                          |                         | PCM4220           |                       |         |

|------------------------------------------------------------------------|--------------------------|-------------------------|-------------------|-----------------------|---------|

| PARAMETER                                                              | CONDITIONS               | MIN                     | TYP               | MAX                   | UNIT    |

| Digital Decimation Filter Characteristics:<br>Classic Response         |                          |                         |                   |                       |         |

| Passband                                                               |                          |                         |                   | $0.4535 \times f_S$   | Hz      |

| Passband ripple                                                        |                          |                         |                   | ±0.00015              | dB      |

| Stop band                                                              |                          | 0.5465 × f <sub>S</sub> |                   |                       | Hz      |

| Stop band attenuation                                                  |                          | -100                    |                   |                       | dB      |

| Group delay                                                            |                          |                         | 39/f <sub>S</sub> |                       | Seconds |

| Digital Decimation Filter Characteristics:<br>Low Group Delay Response |                          |                         |                   |                       |         |

| Passband                                                               |                          |                         |                   | $0.4167 \times f_{S}$ | Hz      |

| Passband ripple                                                        |                          |                         |                   | ±0.001                | dB      |

| Stop band                                                              |                          | 0.5833 × f <sub>S</sub> |                   |                       | Hz      |

| Stop band attenuation                                                  |                          | -90                     |                   |                       | dB      |

| Group delay                                                            |                          |                         | 21/f <sub>S</sub> |                       | Seconds |

| Digital High-Pass Filter Characteristics                               |                          |                         |                   |                       |         |

| -3dB corner frequency                                                  | High-pass filter enabled |                         |                   | f <sub>S</sub> /48000 | Hz      |

#### **ELECTRICAL CHARACTERISTICS: ANALOG INPUTS, OUTPUTS, AND DC ERROR**

All specifications are at  $T_A$  = +25°C, VCC1 = VCC2 = +4.0V, and VDD = +3.3V, unless otherwise noted.

|                            |                                                   | PCM4220           CONDITIONS         MIN         TYP |               |     |                 |

|----------------------------|---------------------------------------------------|------------------------------------------------------|---------------|-----|-----------------|

| PARAMETER                  | CONDITIONS                                        |                                                      |               | MAX | UNIT            |

| ANALOG INPUTS              |                                                   |                                                      |               |     |                 |

| Full-scale input range     |                                                   |                                                      |               |     |                 |

| Differential input         | Referenced from VINL+ to VINL-, or VINR+ to VINR- |                                                      | 5.6           |     | V <sub>PP</sub> |

| Per input pin              | Applies to VINL+, VINL-, VINR+, or VINR-          |                                                      | 2.8           |     | $V_{PP}$        |

| Input impedance            | Applies to VINL+, VINL-, VINR+, or VINR-          |                                                      | 2.8           |     | kΩ              |

| Common-mode rejection      |                                                   |                                                      | 100           |     | dB              |

| ANALOG OUTPUTS             |                                                   |                                                      |               |     |                 |

| Common-mode output voltage |                                                   |                                                      |               |     |                 |

| Left channel, VCOML        | Measured from VCOML to AGND                       |                                                      | 0.4875 × VCC2 |     | V               |

| Right channel, VCOMR       | Measured from VCOMR to AGND                       |                                                      | 0.4875 × VCC1 |     | V               |

| Common-mode output current | Applies to VCOML or VCOMR                         |                                                      |               | 200 | μА              |

| DC ERROR                   |                                                   |                                                      |               |     |                 |

| Output offset error        | Digital high-pass filter disabled                 |                                                      | 3             |     | mV              |

| Offset drift               | Digital high-pass filter disabled                 |                                                      | 3.5           |     | μV/°C           |

#### **ELECTRICAL CHARACTERISTICS: POWER SUPPLIES**

All specifications are at  $T_A = +25$ °C, VCC1 = VCC2 = +4.0V, VDD = +3.3V, and MCKI = 12.288MHz, unless otherwise noted.

|                                                  |                                              |      |             | PCM4220 |      |

|--------------------------------------------------|----------------------------------------------|------|-------------|---------|------|

| PARAMETER                                        | CONDITIONS                                   | MIN  | MIN TYP MAX |         | UNIT |

| POWER SUPPLIES                                   |                                              |      |             |         |      |

| Recommended supply voltage range                 |                                              |      |             |         |      |

| VCC1, VCC2                                       | 0°C <t<sub>A ≤ +85°C</t<sub>                 | +3.8 | +4.0        | +4.2    | V    |

| VCC1, VCC2                                       | -40°C ≤ T <sub>A</sub> ≤ 0°C                 | +3.9 | +4.0        | +4.2    | V    |

| VDD                                              | -40°C ≤ T <sub>A</sub> ≤ +85°C               | +2.4 | +3.3        | +3.6    | V    |

| Supply current: power-down                       | RST (pin 36) held low with no clocks applied |      |             |         |      |

| ICC1 + ICC2                                      | VCC1 = VCC2 = +4.0V                          |      | 600         |         | μΑ   |

| IDD                                              | VDD = +3.3V                                  |      | 325         |         | μΑ   |

| Supply current: f <sub>S</sub> = 48kHz           |                                              |      |             |         |      |

| ICC1 + ICC2                                      | VCC1 = VCC2 = +4.0V                          |      | 65          | 75      | mA   |

| IDD                                              | VDD = +3.3V                                  |      | 14          | 18      | mA   |

| Supply current: f <sub>S</sub> = 96kHz           |                                              |      |             |         |      |

| ICC1 + ICC2                                      | VCC1 = VCC2 = +4.0V                          |      | 65          |         | mA   |

| IDD                                              | VDD = +3.3V                                  |      | 21          |         | mA   |

| Supply current: f <sub>S</sub> = 192kHz          |                                              |      |             |         |      |

| ICC1 + ICC2                                      | VCC1 = VCC2 = +4.0V                          |      | 65          |         | mA   |

| IDD                                              | VDD = +3.3V                                  |      | 24          |         | mA   |

| Total power dissipation: power-down              |                                              |      | 3.5         |         | mW   |

| Total power dissipation: f <sub>S</sub> = 48kHz  |                                              |      | 305         | 360     | mW   |

| Total power dissipation: f <sub>S</sub> = 96kHz  |                                              |      | 330         |         | mW   |

| Total power dissipation: f <sub>S</sub> = 192kHz |                                              |      | 340         |         | mW   |

#### **ELECTRICAL CHARACTERISTICS: AUDIO INTERFACE TIMING**

All specifications are at  $T_A = +25$ °C, VCC1 = VCC2 = +4.0V, and VDD = +3.3V, unless otherwise noted.

|                                                               |                                                  | PCM422                  |         |                           |      |  |

|---------------------------------------------------------------|--------------------------------------------------|-------------------------|---------|---------------------------|------|--|

| PARAMETER                                                     | CONDITIONS                                       | MIN                     | MIN TYP |                           | UNIT |  |

| AUDIO SERIAL PORT                                             |                                                  |                         |         |                           |      |  |

| LRCK period, t <sub>LRCKP</sub>                               | All data formats                                 | 4.62                    |         | 125                       | μs   |  |

| LRCK high/low time, t <sub>LRCKHL</sub>                       |                                                  |                         |         |                           |      |  |

| Left-Justified, I <sup>2</sup> S, and TDM Master mode formats |                                                  | $0.45 \times t_{LRCKP}$ |         | 0.55 × t <sub>LRCKP</sub> | μs   |  |

| TDM slave mode formats                                        |                                                  | t <sub>BCKP</sub>       |         | $0.55 \times t_{LRCKP}$   | μs   |  |

| BCK period, t <sub>BCKP</sub>                                 | Left-Justified and I <sup>2</sup> S data formats |                         |         |                           |      |  |

| Normal sampling mode                                          |                                                  | t <sub>LRCKP</sub> /128 |         |                           | ns   |  |

| Double Speed sampling mode                                    |                                                  | t <sub>LRCKP</sub> /64  |         |                           | ns   |  |

| Quad Speed sampling mode                                      |                                                  | t <sub>LRCKP</sub> /64  |         |                           | ns   |  |

| BCK period, t <sub>BCKP</sub>                                 | TDM data formats                                 |                         |         |                           |      |  |

| Normal sampling mode                                          |                                                  | t <sub>LRCKP</sub> /256 |         |                           | ns   |  |

| Double Speed sampling mode                                    |                                                  | t <sub>LRCKP</sub> /128 |         |                           | ns   |  |

| Quad Speed sampling mode                                      |                                                  | t <sub>LRCKP</sub> /64  |         |                           | ns   |  |

| BCK high/low time, t <sub>BCKHL</sub>                         | All data formats                                 | $0.45 \times t_{BCKP}$  |         | $0.55 \times t_{BCKP}$    | ns   |  |

| Data output delay, t <sub>DO</sub>                            | All data formats                                 |                         |         | 10                        | ns   |  |

Copyright © 2006–2009, Texas Instruments Incorporated

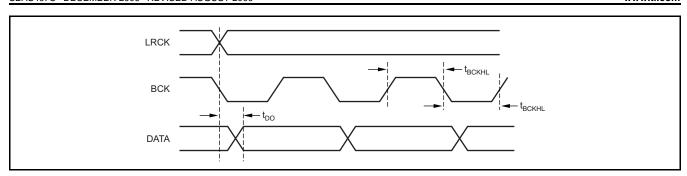

Figure 1. Audio Serial Port Timing: Left-Justified and I<sup>2</sup>S Data Formats

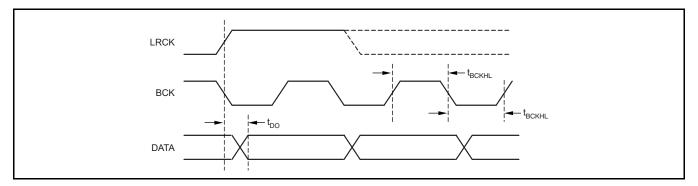

Figure 2. Audio Serial Port Timing: TDM Data Formats

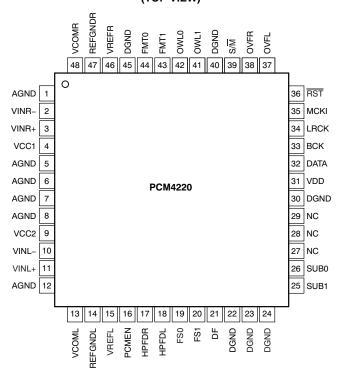

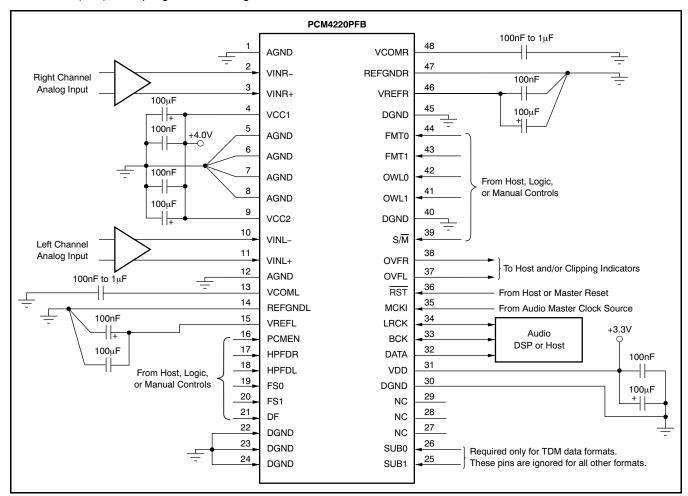

#### **PIN CONFIGURATION**

#### PFB PACKAGE TQFP-48 (TOP VIEW)

#### **TERMINAL FUNCTIONS**

| PI      | PIN |        |                                                                   |

|---------|-----|--------|-------------------------------------------------------------------|

| NAME    | NO. | I/O    | DESCRIPTION                                                       |

| AGND    | 1   | Ground | Analog ground                                                     |

| VINR-   | 2   | Input  | Right channel inverting, 2.8V <sub>PP</sub> nominal full-scale    |

| VINR+   | 3   | Input  | Right channel noninverting, 2.8V <sub>PP</sub> nominal full-scale |

| VCC1    | 4   | Power  | Analog supply, +4.0V nominal                                      |

| AGND    | 5   | Ground | Analog ground                                                     |

| AGND    | 6   | Ground | Analog ground                                                     |

| AGND    | 7   | Ground | Analog ground                                                     |

| AGND    | 8   | Ground | Analog ground                                                     |

| VCC2    | 9   | Power  | Analog supply, +4.0V nominal                                      |

| VINL-   | 10  | Input  | Left channel inverting, 2.8V <sub>PP</sub> nominal full-scale     |

| VINL+   | 11  | Input  | Left channel noninverting, 2.8V <sub>PP</sub> nominal full-scale  |

| AGND    | 12  | Ground | Analog ground                                                     |

| VCOML   | 13  | Output | Left channel common-mode voltage, (0.4875 x VCC2) nominal         |

| REFGNDL | 14  | Ground | Left channel reference ground, connect to analog ground           |

| VREFL   | 15  | Output | Left channel reference output for decoupling purposes only        |

| PCMEN   | 16  | Input  | PCM output enable (active high)                                   |

| HPFDR   | 17  | Input  | Right channel high-pass filter disable (active high)              |

| HPFDL   | 18  | Input  | Left channel high-pass filter disable (active high)               |

Copyright © 2006–2009, Texas Instruments Incorporated

#### **TERMINAL FUNCTIONS (continued)**

| PIN          |          |        |                                                                                                                                                                               |  |  |

|--------------|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|              |          | 1/0    | DESCRIPTION                                                                                                                                                                   |  |  |

| FS0<br>FS1   | 19<br>20 | Input  | Sampling modes: FS0 = 0 and FS1 = 0: Normal mode FS0 = 1 and FS1 = 0: Double Speed mode FS0 = 0 and FS1 = 1: Quad Speed mode FS0 = 1 and FS1 = 1: Reserved Sampling mode      |  |  |

| DF           | 21       | Input  | Digital decimation filter response: DF = 0: Classic filter response DF = 1: Low Group Delay response                                                                          |  |  |

| DGND         | 22       | Ground | Digital ground                                                                                                                                                                |  |  |

| DGND         | 23       | Ground | Digital ground                                                                                                                                                                |  |  |

| DGND         | 24       | Ground | Digital ground                                                                                                                                                                |  |  |

| SUB1<br>SUB0 | 25<br>26 | Input  | TDM active sub-frame: SUB0 = 0 and SUB1 = 0: Sub-frame 0 SUB0 = 1 and SUB1 = 0: Sub-frame 1 SUB0 = 0 and SUB1 = 1: Sub-frame 2 SUB0 = 1 and SUB1 = 1: Sub-frame 3             |  |  |

| NC           | 27       | _      | No external connection, internally bonded to ESD pad                                                                                                                          |  |  |

| NC           | 28       | _      | No external connection, internally bonded to ESD pad                                                                                                                          |  |  |

| NC           | 29       | _      | No external connection, internally bonded to ESD pad                                                                                                                          |  |  |

| DGND         | 30       | Ground | Digital ground                                                                                                                                                                |  |  |

| VDD          | 31       | Power  | Digital supply, +3.3V nominal                                                                                                                                                 |  |  |

| DATA         | 32       | Output | Audio serial port data                                                                                                                                                        |  |  |

| BCK          | 33       | I/O    | Audio serial port bit clock                                                                                                                                                   |  |  |

| LRCK         | 34       | I/O    | Audio serial port left/right word clock                                                                                                                                       |  |  |

| MCKI         | 35       | Input  | Master clock                                                                                                                                                                  |  |  |

| RST          | 36       | Input  | Reset and power-down (active low)                                                                                                                                             |  |  |

| OVFL         | 37       | Output | Left channel overflow flag (active high)                                                                                                                                      |  |  |

| OVFR         | 38       | Output | Right channel overflow flag (active high)                                                                                                                                     |  |  |

| S/M          | 39       | Input  | Audio serial port Slave/Master mode: $S/\overline{M} = 0$ : Master mode $S/\overline{M} = 1$ : Slave mode                                                                     |  |  |

| DGND         | 40       | Output | Digital ground                                                                                                                                                                |  |  |

| OWL1<br>OWL0 | 41<br>42 | Input  | Output word length:  OWL0 = 0 and OWL1 = 0: 24-bits  OWL0 = 1 and OWL1 = 0: 18-bits  OWL0 = 0 and OWL1 = 1: 20-bits  OWL0 = 1 and OWL1 = 1: 16-bits                           |  |  |

| FMT1<br>FMT0 | 43<br>44 | Input  | Audio data format:  FMT0 = 0 and FMT1 = 0: Left-justified  FMT0 = 1 and FMT1 = 0: I <sup>2</sup> S  FMT0 = 0 and FMT1 = 1: TDM  FMT0 = 1 and FMT1 = 1: TDM with one BCK delay |  |  |

| DGND         | 45       | Ground | Digital ground                                                                                                                                                                |  |  |

| VREFR        | 46       | Output | Right channel reference output for decoupling purposes only                                                                                                                   |  |  |

| REFGNDR      | 47       | Ground | Right channel reference ground, connect to analog ground                                                                                                                      |  |  |

| VCOMR        | 48       | Output | Right channel common-mode voltage (0.4875 x VCC1 nominal)                                                                                                                     |  |  |

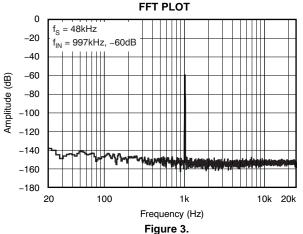

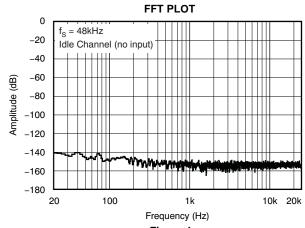

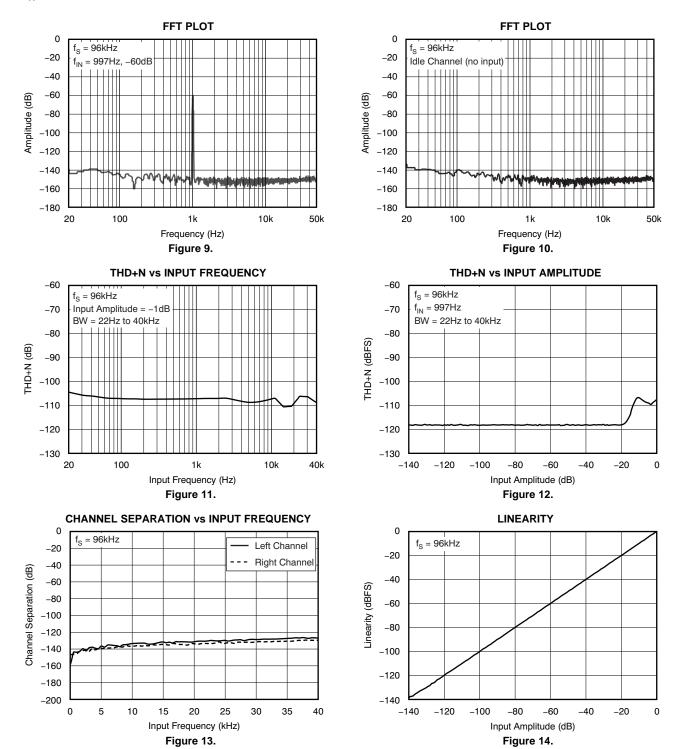

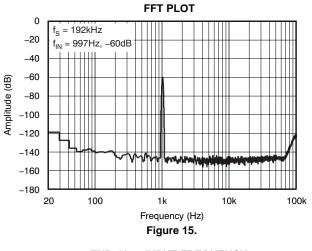

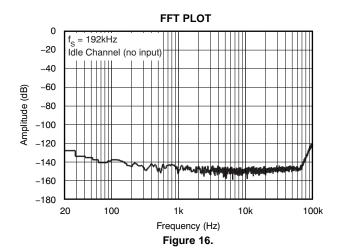

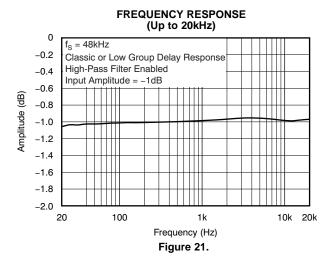

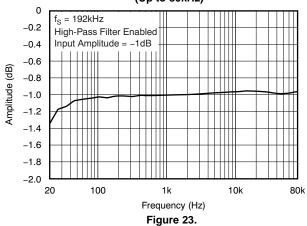

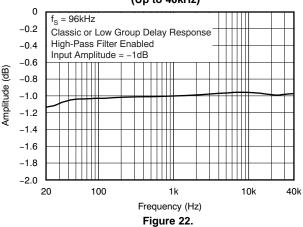

#### **TYPICAL CHARACTERISTICS**

At  $T_A = +25$ °C, VCC1 = VCC2 = +4.0V, and VDD = +3.3V, unless otherwise noted.

Figure 4.

Figure 7.

At  $T_A = +25$ °C, VCC1 = VCC2 = +4.0V, and VDD = +3.3V, unless otherwise noted.

At  $T_A = +25$ °C, VCC1 = VCC2 = +4.0V, and VDD = +3.3V, unless otherwise noted.

Copyright © 2006–2009, Texas Instruments Incorporated

At  $T_A = +25$ °C, VCC1 = VCC2 = +4.0V, and VDD = +3.3V, unless otherwise noted.

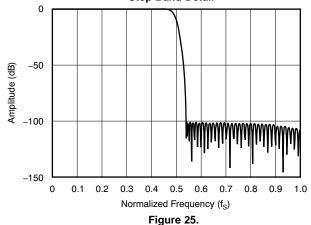

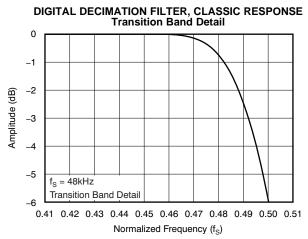

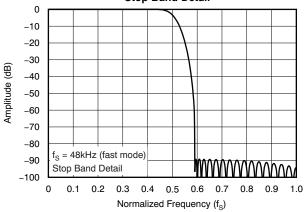

DIGITAL DECIMATION FILTER, CLASSIC RESPONSE Stop Band Detail

#### FREQUENCY RESPONSE (Up to 40kHz)

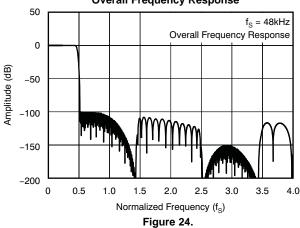

## DIGITAL DECIMATION FILTER, CLASSIC RESPONSE Overall Frequency Response

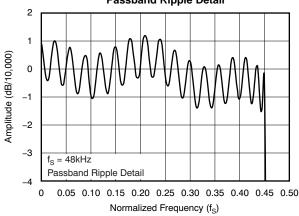

DIGITAL DECIMATION FILTER, CLASSIC RESPONSE Passband Ripple Detail

Figure 26.

At  $T_A = +25$ °C, VCC1 = VCC2 = +4.0V, and VDD = +3.3V, unless otherwise noted.

Figure 27.

# DIGITAL DECIMATION FILTER, LOW GROUP DELAY RESPONSE Stop Band Detail

Figure 29.

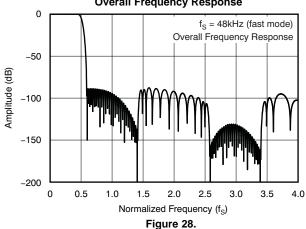

#### DIGITAL DECIMATION FILTER, LOW GROUP DELAY RESPONSE Overall Frequency Response

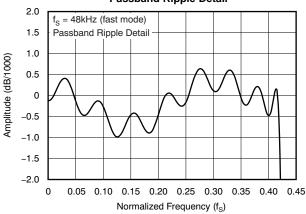

DIGITAL DECIMATION FILTER, LOW GROUP DELAY RESPONSE

Passband Ripple Detail

Figure 30.

At  $T_A = +25$ °C, VCC1 = VCC2 = +4.0V, and VDD = +3.3V, unless otherwise noted.

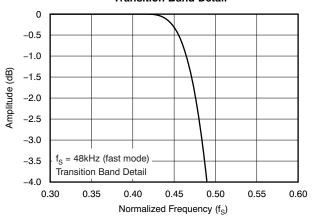

## DIGITAL DECIMATION FILTER, LOW GROUP DELAY RESPONSE Transition Band Detail

Figure 31.

# 0.6 | High-Pass Filter Passband | O.2 | O.2 | O.4 | O.2 | O.4 | O.2 | O.4 | O.5 | O.

**DIGITAL HIGH-PASS FILTER**

Figure 32.

2.0

Normalized Frequency (f<sub>S</sub>/1000)

2.5

3.0

4.0

1.5

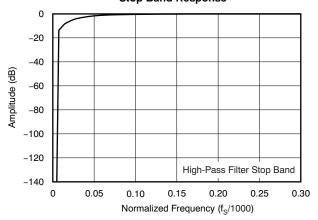

## DIGITAL HIGH-PASS FILTER Stop Band Response

-0.8

-0.5

0

0.5

1.0

Figure 33.

#### PRODUCT OVERVIEW

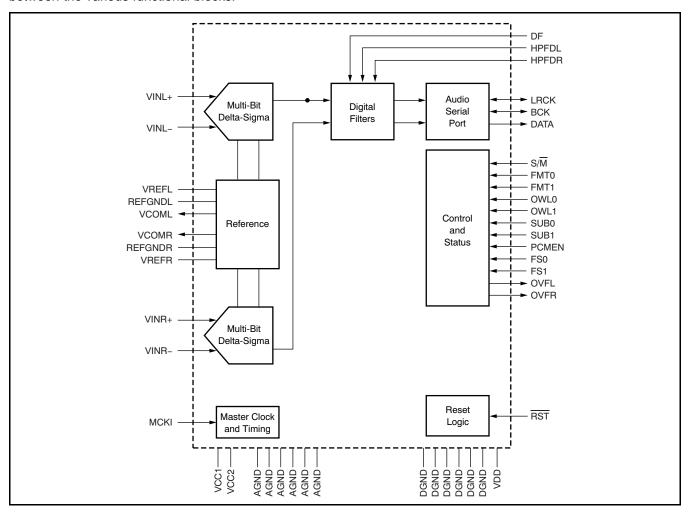

The PCM4220 is a two-channel, multi-bit delta-sigma ( $\Delta\Sigma$ ) A/D converter. The 6-bit output from the delta-sigma modulators is routed to the digital decimation filter, where the output of the filter provides linear PCM data. The linear PCM data are output at the audio serial port interface for connection to external processing and logic circuitry.

Figure 34 shows a simplified functional block diagram for the PCM4220, highlighting the interconnections between the various functional blocks.

Figure 34. Functional Block Diagram

#### **ANALOG INPUTS**

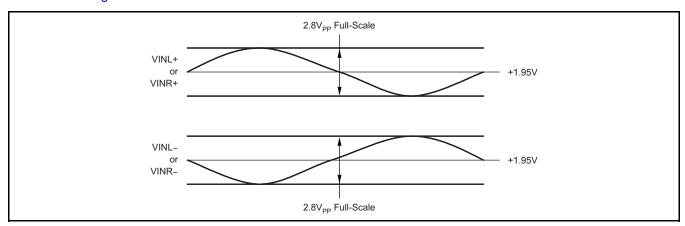

The PCM4220 includes two analog inputs, referred to as the *left* and *right* channels. Each channel includes a pair of differential voltage input pins. The left channel inputs are named VINL– (pin 10) and VINL+ (pin 11), respectively. The right channel inputs are named VINR– (pin 2) and VINR+ (pin 3), respectively. Each pin of an input pair has a nominal full-scale input of 2.8V<sub>PP</sub>. The full-scale input for a given pair is specified as 5.6V<sub>PP</sub> differential in the Electrical Characteristics table. Figure 35 shows the full-scale input range of the PCM4220, with the input signals centered on the nominal common-mode voltage of +1.95V.

In a typical application, the front end is driven by a buffer amplifier or microphone/line level preamplifier. Examples are given in the *Input Buffer Circuits* section of this datasheet. The analog inputs of the PCM4220 may be driven up to the absolute maximum input rating without instability. If the analog input voltage is expected to exceed the absolute maximum input ratings in a given application, it is recommended that input clamping or limiting be added to the analog input circuitry prior to the PCM4220 in order to provide protection against damaging the device. Specifications for the analog inputs are given in the Electrical Characteristics and Absolute Maximum Ratings tables of this data sheet.

Figure 35. Full-Scale Analog Input Range

#### **VOLTAGE REFERENCE**

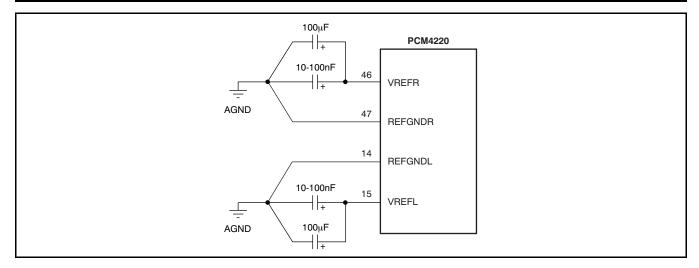

The PCM4220 includes an on-chip, band-gap voltage reference. The band-gap output voltage is buffered and then routed to the two delta-sigma modulators. The inclusion of an on-chip reference circuit enhances the power-supply noise rejection of the PCM4220. The buffered reference voltage for each channel is filtered using external capacitors. The capacitors are connected between VREFL (pin 15) and REFGNDL (pin 14) for the left channel, and VREFR (pin 46) and REFGNDR (pin 47) for the right channel. Figure 36 illustrates the recommend reference decoupling capacitor values and connection scheme.

The 10nF to 100nF capacitors in Figure 36 may be metal film or X7R/C0G ceramic chip capacitors. The 100μF capacitors may be polymer tantalum chip (Kemet T520 series or equivalent) or aluminum electrolytic.

The VREFL and VREFR pins are not designed for biasing external input circuitry. Two common-mode voltage outputs are provided for this purpose, and are discussed in the following section.

Figure 36. Recommended Reference Capacitor Connections and Values

#### **COMMON-MODE VOLTAGE OUTPUTS**

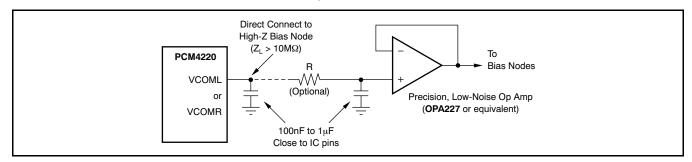

The PCM4220 includes two dc common-mode voltage outputs, VCOML (pin 13) and VCOMR (pin 48), which correspond to the left and right input channels, respectively. The common-mode voltage is utilized to bias internal op amps within the modulator section of the PCM4220, and may be used to bias external input circuitry when proper design guidelines are followed. The common-mode voltages are derived from the VCC1 and VCC2 analog power supplies using internal voltage dividers. The voltage divider outputs are buffered and then routed to internal circuitry and the VCOML and VCOMR outputs.

The common-mode output voltage is nominally equal to  $(0.4875 \times VCC1)$  for VCOMR and  $(0.4875 \times VCC2)$  for VCOML. Given an analog supply voltage of +4.0V connected to both VCC1 and VCC2, the resulting common-mode voltages are +1.95V.

The common-mode voltage outputs have limited drive capability. If multiple bias points are to be driven, or the external bias nodes are not sufficiently high impedance, an external output buffer is recommended. Figure 37 shows a typical buffer configuration using the OPA227. The op amp utilized in the buffer circuit should exhibit low dc offset and drift characteristics, as well as low output noise.

Figure 37. Common-Mode Output Connections

Copyright © 2006–2009, Texas Instruments Incorporated

#### **MASTER CLOCK INPUT**

The PCM4220 requires a master clock for operating the internal logic and modulator circuitry. The master clock is supplied from an external source, connected at the MCKI input (pin 35). Table 1 summarizes the requirements for various operating modes of the PCM4220. Referring to Table 1, the term  $f_S$  refers to the PCM4220 PCM output sampling rate (that is, 48kHz, 96kHz, 192kHz, etc.). Refer to the Electrical Characteristics table for timing specifications related to the master clock input.

For best performance, the master clock jitter should be maintained below 40ps peak amplitude.

| Table 1. Master C | ock Requirements |

|-------------------|------------------|

|-------------------|------------------|

| OPERATING MODE   | REQUIRED MASTER CLOCK (MCKI) RATE |

|------------------|-----------------------------------|

| PCM Normal       | 256f <sub>S</sub>                 |

| PCM Double Speed | 128f <sub>S</sub>                 |

| PCM Quad Speed   | 64f <sub>S</sub>                  |

#### **RESET AND POWER-DOWN OPERATION**

The PCM4220 includes an external reset input,  $\overline{RST}$  (pin 36), which may be utilized to force an internal reset initialization or power-down sequence. The reset input is active low. Figure 38 shows the required timing for an external forced reset.

A power-down state for the PCM422 may be initiated by forcing and holding the reset input low for the duration of the desired power-down condition. Minimum power is consumed during this state when all clock inputs for the PCM4220 are forced low. Before releasing the reset input by forcing a high state, the master clock should be enabled so that the PCM4220 can execute a reset initialization sequence.

While the RST pin is forced low, or during reset initialization, the audio serial port data and clock outputs are driven low.

Figure 38. External Reset Sequence

#### DISABLED STATES FOR THE PCM4220 AUDIO SERIAL PORT

When PCMEN (pin 16) is driven low, the PCM output is disabled. The audio serial port data and clocks are driven low.

#### PCM OUTPUT AND SAMPLING MODES

The PCM4220 supports 24-bit linear PCM output data when the PCMEN input (pin 16) is forced high. The PCM output is disabled when PCMEN is forced low. The 24-bit output data may be dithered to 20-, 18-, or 16-bits using internal word length reduction circuitry. Refer to the *Output Word Length Reduction* section of this data sheet for additional information.

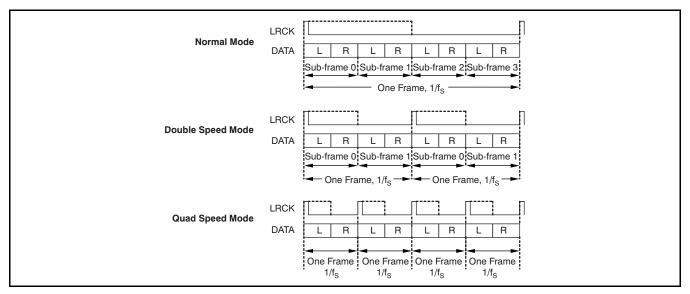

The PCM4220 supports three PCM sampling modes, referred to as Normal, Double Speed, and Quad Speed. The sampling mode is determined by the state of the FS0 and FS1 inputs (pins 19 and 20, respectively). Table 2 summarizes the sampling modes available for the PCM4220.

Normal sampling mode supports output sampling rates from 8kHz to 54kHz. The  $\Delta\Sigma$  modulator operates with 128x oversampling in this mode. Both the Classic and Low Group Delay decimation filter responses are available in Normal mode. The master clock (MCKI) rate must be 256x the desired output sampling rate for Normal operation.

The Double Speed sampling mode supports output sampling rates from 54kHz to 108kHz. The delta-sigma modulator operates with 64x oversampling in this mode. Both the Classic and Low Group Delay decimation filter responses are available in Double Speed mode. The master clock (MCKI) rate must be 128x the desired output sampling rate for Double Speed operation.

Quad Speed sampling mode supports output sampling rates from 108kHz to 216kHz. The delta-sigma modulator operates with 32x oversampling in this mode. Only the Low Group Delay decimation filter response is available in Quad Speed mode. The master clock (MCKI) rate must be 64x the desired output sampling rate for Quad Speed operation.

| FS1 (pin 20) | FS0 (pin 19) | SAMPLING MODE                                 |  |  |  |  |  |  |

|--------------|--------------|-----------------------------------------------|--|--|--|--|--|--|

| LO           | LO           | Normal, 8kHz ≤ f <sub>S</sub> ≤ 54kHz         |  |  |  |  |  |  |

| LO           | HI           | Double Speed, 54kHz < f <sub>S</sub> ≤ 108kHz |  |  |  |  |  |  |

| HI           | LO           | Quad Speed, 108kHz < f <sub>S</sub> ≤ 216kHz  |  |  |  |  |  |  |

| HI           | HI           | Reserved                                      |  |  |  |  |  |  |

**Table 2. PCM Sampling Mode Configuration**

#### **AUDIO SERIAL PORT INTERFACE**

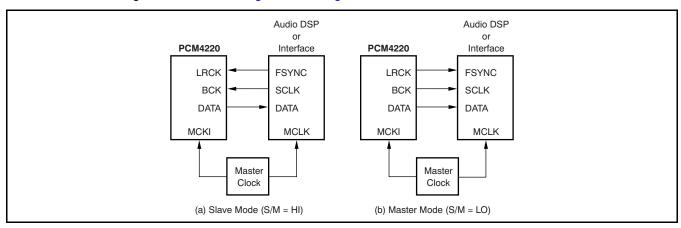

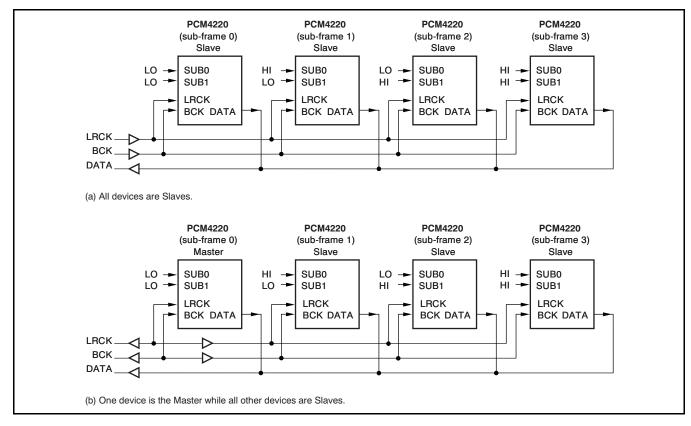

The PCM output mode supports a three-wire synchronous serial interface. This interface includes a serial data output (DATA, pin 32), a serial bit or data clock (BCK, pin 33), and a left/right word clock (LRCK, pin 34). The BCK and LRCK clock pins may be inputs or outputs, depending on the Slave or Master mode configuration. Figure 39 illustrates Slave and Master mode serial port connections to an external audio signal processor or host device.

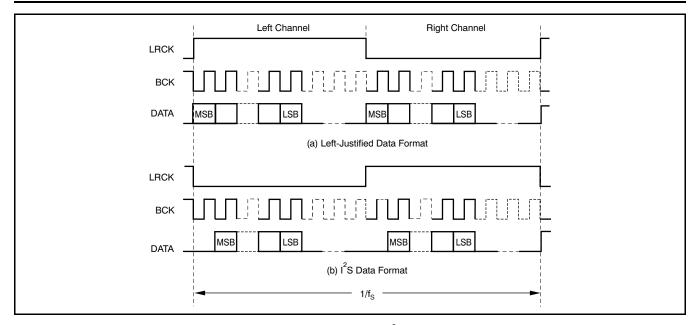

The audio serial port supports four data formats that are illustrated in Figure 40, Figure 42, and Figure 43. The I<sup>2</sup>S and Left-Justified formats support two channels of audio output data. The TDM data formats can support up to eight channels of audio output data on a single data line. The audio data format is selected using the FMT0 and FMT1 inputs (pins 44 and 43, respectively). Table 3 summarizes the audio data format options. For all formats, audio data are represented as two's complement binary data, with the MSB transmitted first. Regardless of the format selection, audio data are always clocked out of the port on the falling edge of the BCK clock.

FMT1 (pin 43)

FMT0 (pin 44)

AUDIO DATA FORMAT

LO

LO

Left-Justified

LO

HI

I<sup>2</sup>S

HI

LO

TDM

HI

HI

TDM with data delayed one BCK cycle from LRCK rising edge

**Table 3. PCM Audio Data Format Selection**

The LRCK clock rate should always be operated at the desired output sampling rate, or  $f_S$ . In Slave mode, the LRCK clock is an input, with the rate set by an external audio bus master (that is, a clock generator, digital signal processor, etc.). In Master mode, the LRCK clock is an output, derived from the master clock input using on-chip clock dividers (as is the BCK clock). The clock divider is configured using the FS0 and FS1 pins, which are discussed in the *PCM Output and Sampling Modes* section of this datasheet.

Copyright © 2006–2009, Texas Instruments Incorporated

For the I<sup>2</sup>S and Left-Justified data formats, the BCK clock output rate is fixed in Master mode, with the Normal mode being 128f<sub>S</sub> and the Double and Quad Speed modes being 64f<sub>S</sub>. In Slave Mode, a BCK clock input rate of 64f<sub>S</sub> or 128f<sub>S</sub> is recommended for Normal mode, while 64f<sub>S</sub> is recommended for Double and Quad Rate modes.

For the TDM data formats, the BCK rate depends upon the sampling mode for either Slave or Master operation. For Normal sampling, the BCK must be 256f<sub>S</sub>. Double Speed mode requires 128f<sub>S</sub>, while Quad Speed mode requires 64f<sub>S</sub>. This requirement limits the maximum number of channels carried by the TDM formats to eight for Normal mode, four for Double Rate mode, and two for Quad Rate mode.

When using the TDM formats, the sub-frame assignment for the device must be selected using the SUB0 and SUB1 inputs (pins 26 and 25, respectively). Table 4 summarizes the sub-frame selection options. A sub-frame contains two 32-bit time slots, with each time slot carrying 24 bits of audio data corresponding to either the left or right channel of the PCM4220. Refer to Figure 41 through Figure 43 for TDM interfacing connections and sub-frame formatting details. For the TDM format with one BCK delay, the serial data output is delayed by one BCK period after the rising edge of the LRCK clock.

| SUB1 (pin 25) | SUB0 (pin 26) | SUB-FRAME ASSIGNMENT |

|---------------|---------------|----------------------|

| LO            | LO            | Sub-frame 0          |

| LO            | HI            | Sub-frame 1          |

| HI            | LO            | Sub-frame 2          |

| HI            | HI            | Sub-frame 3          |

**Table 4. TDM Sub-frame Assignment**

When using TDM formats with Double Speed sampling, it is recommended that the SUB1 pin be forced low. When using TDM formats with Quad Speed sampling, it is recommended that both the SUB0 and SUB1 pins be forced low.

For all serial port modes and data formats, when driving capacitive loads greater than 30pF with the data and clock outputs, it is recommended that external buffers be utilized to ensure data and clock integrity at the receiving device(s).

For specifications regarding audio serial port operation, the reader is referred to the Electrical Characteristics: Audio Interface Timing table, as well as Figure 1 and Figure 2 in this data sheet.

Figure 39. Slave and Master Mode Operation

20

Figure 40. Left-Justified and I<sup>2</sup>S Data Formats

Figure 41. TDM Mode Interface Connections (PCM Normal Mode Shown)

NOTE: Each L or R channel time slot is 32 bits long, with 24-bit data Left-Justified in the time slot. Audio data is MSB first. Sub-frame assignments for each PCM4220 device are selected by the corresponding SUB0 and SUB1 pin settings.

**LRCK Normal Mode** DATA Sub-frame 0 Sub-frame 1 Sub-frame 2 Sub-frame 3 One Frame, 1/fs **LRCK Double Speed Mode** DATA R Sub-frame 0 Sub-frame 1 Sub-frame 0 Sub-frame 1 One Frame 1/f. **LRCK Quad Speed Mode** DATA One Frame One Frame One Frame

Figure 42. TDM Data Formats: Slave Mode

NOTE: Each L or R channel time slot is 32 bits long, with 24-bit data Left-Justified in the time slot. Audio data is MSB first. Sub-frame assignments for each PCM4220 device are selected by the corresponding SUB0 and SUB1 pin settings.

$1/f_S$

Figure 43. TDM Data Formats: Master Mode

$1/f_S$

$1/f_S$

#### **DIGITAL DECIMATION FILTER**

The PCM4220 digital decimation filter is a linear phase, multistage finite impulse response (FIR) design with two user-selectable filter responses. The decimation filter provides the digital downsampling and low-pass anti-alias filter functions for the PCM4220.

The Classic filter response is typical of traditional audio data converters, with Figure 24 through Figure 27 detailing the frequency response, and the related specifications given in the Electrical Characteristics table. The group delay for the Classic filter is  $39/f_S$ , or  $812.5\mu s$  for  $f_S = 48 kHz$  and  $406.25\mu s$  for  $f_S = 96 kHz$ . The Classic filter response is not available for the Quad Speed sampling mode.

www.ti.com

The Low Group Delay response provides a lower latency option for the decimation filter, and is detailed in Figure 28 through Figure 31, with the relevant specifications given in the Electrical Characteristics table. The Low Group Delay filter response is available for all sampling modes. The group delay for this filter is  $21/f_S$ , or  $437.5\mu s$  for  $f_S = 48kHz$ ,  $218.75\mu s$  for  $f_S = 96kHz$ , and  $109.375\mu s$  for  $f_S = 192kHz$ .

The decimation filter response is selected using the DF input (pin 21), with the settings summarized in Table 5. For Quad Speed sampling mode operation, the Low Group Delay filter is always selected, regardless of the DF pin setting.

**Table 5. Decimation Filter Response Selection**

| DF (pin 21) | DECIMATION FILTER RESPONSE                                     |

|-------------|----------------------------------------------------------------|

| LO          | Classic response, with group delay = 39/f <sub>S</sub>         |

| HI          | Low Group Delay response, with group delay = 21/f <sub>S</sub> |

#### **DIGITAL HIGH-PASS FILTER**

The PCM4220 incorporates digital high-pass filters for both the left and right audio channels, with the purpose of removing the  $\Delta\Sigma$  modulator dc offset from the audio output data. Figure 32 and Figure 33 detail the frequency response for the digital high-pass filter. The  $f_{-3dB}$  frequency is approximately  $f_S/48000$ , where  $f_S$  is the PCM output sampling rate.

Two inputs, HPFDR (pin 17) and HPFDL (pin 18), allow the digital high-pass filter to be enabled or disabled individually for the right and left channels, respectively. Table 6 summarizes the operation of the high-pass filter disable pins.

Table 6. Digital High-Pass Filter Configuration

| HPFDR (pin 17) or HPFDL (pin 18) | HIGH-PASS FILTER STATE                 |  |  |  |

|----------------------------------|----------------------------------------|--|--|--|

| LO                               | Enabled for the corresponding channel  |  |  |  |

| HI                               | Disabled for the corresponding channel |  |  |  |

#### PCM OUTPUT WORD LENGTH REDUCTION

The PCM4220 is typically configured to output 24-bit linear PCM audio data. However, internal word length reduction circuitry may be utilized to reduce the 24-bit data to 20-, 18-, or 16-bit data. This reduction is accomplished by using a Triangular PDF dithering function. The OWL0 (pin 42) and OWL1 (pin 41) inputs are utilized to select the output data word length. Table 7 summarizes the output word length configuration options.

Table 7. PCM Audio Data Word Length Selection

| OWL1 (pin 41) | OWL0 (pin 42) | OUTPUT WORD LENGTH |

|---------------|---------------|--------------------|

| LO            | LO            | 24 bits            |

| LO            | HI            | 18 bits            |

| HI            | LO            | 20 bits            |

| HI            | HI            | 16 bits            |

#### **OVERFLOW INDICATORS**

The PCM4220 includes two active-high digital overflow outputs, OVFL (pin 37) and OVFR (pin 38), corresponding to the left and right channels, respectively. These outputs are functional when the PCM output mode is enabled, as the overflow detection circuitry is incorporated into the digital filter engine. The overflow indicators are forced high whenever a digital overflow is detected for a given channel. The overflow indicators may be utilized as clipping flags, and monitored using a host processor or light-emitting diode (LED) indicators. When driving a LED, the overflow output may be buffered to ensure adequate drive for the LED. A recommended buffer is Texas Instruments' SN74LVC1G125. Equivalent buffers may be substituted

Copyright © 2006–2009, Texas Instruments Incorporated

#### TYPICAL CONNECTIONS

Figure 44 provides a typical connection diagram for the PCM4220. Recommended power-supply bypass and reference filter capacitors are shown. These components should be located as close to the corresponding PCM4220 package pins as physically possible. Larger power-supply bypass capacitors may be placed on the bottom side of the printed circuit board (PCB). However, reference decoupling capacitors should be located on the top side of the PCB to avoid issues with added via inductance.

As Figure 44 illustrates, the audio host device may be a digital signal processor (DSP), digital audio interface transmitter (DIT), or a programmable logic device.

Figure 44. Typical Connections for PCM and DSD Output Modes

#### INPUT BUFFER CIRCUITS

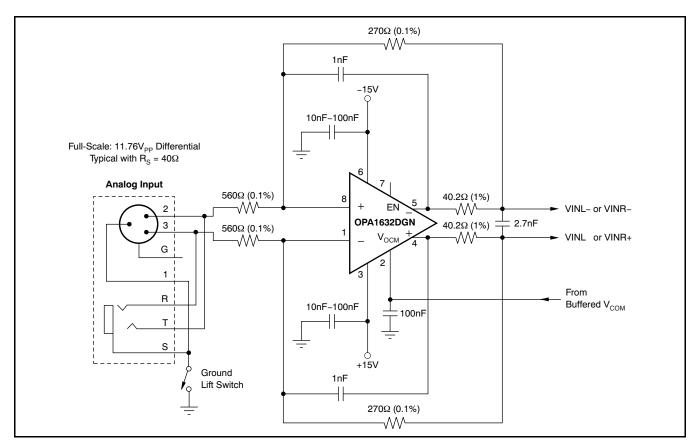

The PCM4220 is typically preceded in an application by an input buffer or preamplifier circuit. The input circuit is required to perform anti-aliasing filtering, in addition to application-specific analog gain scaling, limiting, or processing that may be needed. At a minimum, first-order, low-pass anti-aliasing filtering is necessary. The input buffer must be able to perform the input filtering requirement, in addition to driving the switched-capacitor inputs of the PCM4220 device. The buffer must have adequate bandwidth, slew rate, settling time, and output drive capability to perform these tasks.

Figure 45 illustrates the input buffer/filter circuit utilized on the PCM4222EVM evaluation module, where the PCM4222 analog input section is identical to the PCM4220. This circuit has been optimized for measurement purposes, so that it does not degrade the dynamic characteristics of the PCM4220. The resistors are primarily 0.1% metal film. The  $40.2\Omega$  resistor is 1% tolerance thick film. The 1nF and 2.7nF capacitors may be either PPS

film or COG ceramic capacitors; both types perform with equivalent results in this application. Surface-mount devices are utilized throughout because they provide superior performance when combined with a wideband amplifier such as the OPA1632. The DGN package version of the OPA1632 is utilized; this package includes a thermal pad on the bottom side. The thermal pad must be soldered to the PCB ground plane for heat sink and mechanical support purposes.

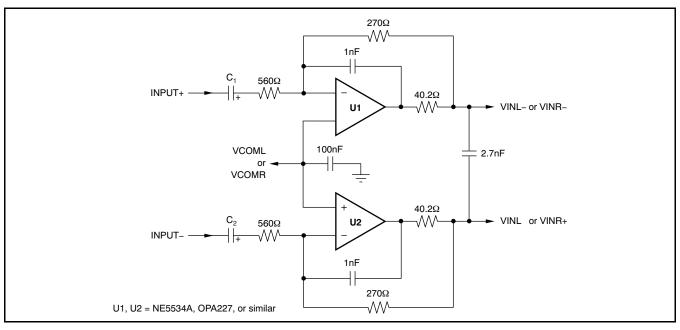

Figure 45. Differential Input Buffer Circuit Utilizing the OPA1632

Figure 46 demonstrates the same circuit topology of Figure 45, while using standard single or dual op amps. The noise level of this circuit is adequate for obtaining the typical A-weighted dynamic range performance for the PCM4220. However, unweighted performance may suffer, depending upon the op amp noise specifications. Near-typical THD+N can be achieved with this configuration, although this performance also depends on the op amps used for the application. The NE5534A and OPA227 (the lower cost 'A' version) are good candidates from a noise and distortion perspective, and are reasonably priced. More expensive lower-noise models, such as the OPA211, should also work well for this configuration. Feedback and input resistor values may be changed to alter circuit gain. However, it is recommended that all circuit changes be simulated and then tested on the bench using a working prototype to verify performance.

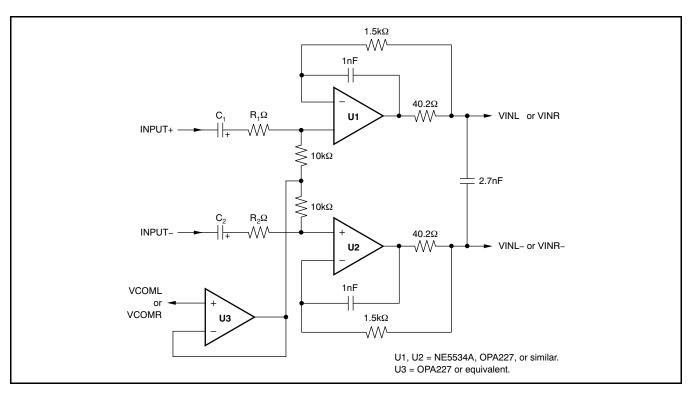

Figure 47 illustrates a differential input circuit that employs a noninverting architecture. The total noise and distortion is expected to be higher than that measured for Figure 45 and Figure 46. As with Figure 46, the NE5534A and OPA227 are good candidates for this circuit, although similar op amps should yield equivalent results.

A useful tool for simulating the circuits shown here is TINA-TI, a free schematic capture and SPICE-based simulator program available from the Texas Instruments web site. This tool includes macro models for many TI and Burr-Brown branded amplifiers and analog integrated circuits. TINA-TI runs on personal computers using Microsoft Windows® operating systems (Windows 2000 or newer).

Copyright © 2006–2009, Texas Instruments Incorporated

NOTE: C<sub>1</sub> and C<sub>2</sub> provide ac coupling. They may be removed if the dc offset from the circuit is negligible.

Figure 46. Alternative Buffer Circuit Using Standard Op Amps

NOTE:  $R_1$  and  $R_2$  are optional. When used, values may be selected for the desired attenuation.

NOTE: C<sub>1</sub> and C<sub>2</sub> provide ac coupling. They may be removed if the dc offset from the circuit is negligible.

Figure 47. Noninverting Differential Input Buffer Utilizing Standard Op Amps

#### INTERFACING TO DIGITAL AUDIO TRANSMITTERS (AES3, IEC60958-3, and S/PDIF)

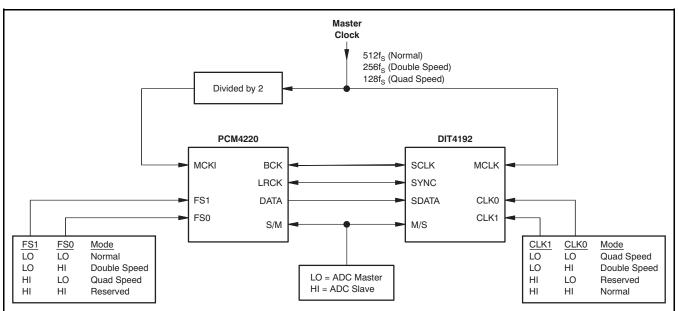

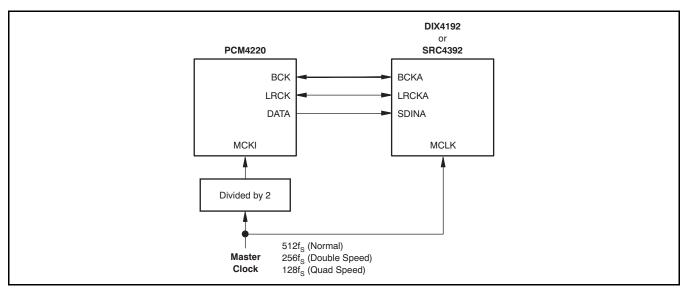

The serial output of audio analog-to-digital converters is oftentimes interfaced to transmitter devices that encode the serial output data to either the AES3 or IEC60958-3 (or S/PDIF) interface formats. Texas Instruments manufactures several devices that perform this encoding, including the DIT4192, DIX4192, SRC4382, and SRC4392. This section describes and illustrates the audio serial port interface connections required for communications between the PCM4220 and these devices. Register programming details for the DIX4192 and SRC4382/4392 are also provided.

Figure 48 shows the interface between a PCM4220 and a DIT4192 transmitter. This configuration supports sampling frequencies and encoded frame rates from 8kHz to 216kHz. For this example, the audio data format must be either Left-Justified or I<sup>2</sup>S; TDM formats are not supported by the DIT4192. In addition, the PCM4220 VDD supply and DIT4192 VIO supply must be the same voltage, to ensure logic level compatibility.

Figure 49 illustrates the audio serial port interface between the PCM4220 and either a DIX4192 transceiver or SRC4382/SRC4392 combo sample rate converter/transceiver device. Port A of the DIX4192 or SRC4382/SRC4392 is utilized for this example. Data acquired by Port A are sent on to the DIT function block within the interface device for AES3 encoding and transmission.

The DIX4192 and SRC4382/SRC4392 are software-configurable, with control register and data buffer settings that determine the operation of internal function blocks. Table 8 and Table 9 summarize the control register settings for the Port A and the DIT function blocks for both A/D Converter Master and Slave modes, respectively. Input sampling and encoded frame rates from 8kHz to 216kHz are supported with the appropriate register settings.

Figure 48. Interfacing the PCM4220 to a DIT4192

Copyright © 2006–2009, Texas Instruments Incorporated

NOTE: VDDPCM4220 = VIODIX4192 or SRC4392.

Audio data format if I<sup>2</sup>S or Left Justified.

Interface supports ADC Slave or Master configurations, depending on DIX4192, SRC4382, or SRC4392 register setup.

Figure 49. Interfacing the PCM4220 to a DIX4192, SRC4382, or SRC4392

Table 8. Register Configuration Sequence for an ADC Master Mode Interface

| REGISTER ADDRESS (hex) | REGISTER DATA (hex) | COMMENTS                                                                                                                                     |  |  |  |  |

|------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7F                     | 00                  | Select Register Page 0                                                                                                                       |  |  |  |  |

| 03                     | 00<br>01            | Port A is Slave mode with Left-Justified audio data format, or Port A is Slave mode with I <sup>2</sup> S Data format                        |  |  |  |  |

| 04                     | 00                  | Default for Port A Slave mode operation                                                                                                      |  |  |  |  |

| 07                     | 64<br>24<br>04      | Divide MCLK by 512 for Normal sampling, or<br>Divide MCLK by 256 for Double Speed Sampling, or<br>Divide MCLK by 128 for Quad Speed sampling |  |  |  |  |

| 08                     | 00                  | Line Driver and AESOUT buffer enabled                                                                                                        |  |  |  |  |

| 09                     | 01                  | Data buffers on Register Page 2 are the source for the DIT channel status (C) and user (U) data                                              |  |  |  |  |

| 01                     | 34                  | Power up Port A and the DIT                                                                                                                  |  |  |  |  |

Table 9. Register Configuration Sequence for an ADC Slave Mode Interface

| REGISTER ADDRESS (hex) | REGISTER DATA (hex) | COMMENTS                                                                                                                                     |

|------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 7F                     | 00                  | Select Register Page 0                                                                                                                       |

| 03                     | 08<br>09            | Port A is Master mode with Left-Justified audio data format, or<br>Port A is Master mode with I <sup>2</sup> S Data format                   |

| 04                     | 03<br>01<br>00      | Divide MCLK by 512 for Normal sampling, or<br>Divide MCLK by 256 for Double Speed sampling, or<br>Divide MCLK by 128 for Quad Speed sampling |

| 07                     | 64<br>24<br>04      | Divide MCLK by 512 for Normal sampling, or<br>Divide MCLK by 256 for Double Speed Sampling, or<br>Divide MCLK by 128 for Quad Speed sampling |

| 08                     | 00                  | Line Driver and AESOUT buffer enabled                                                                                                        |

| 09                     | 01                  | Data buffers on Register Page 2 are the source for the DIT channel status (C) and user (U) data                                              |

| 01                     | 34                  | Power up Port A and the DIT                                                                                                                  |

Submit Documentation Feedback

Copyright © 2006–2009, Texas Instruments Incorporated

www.ti.com

The DIT channel status (C) and user (U) data bits in register page 2 may be programmed after the DIT block has powered up. To program these bits, disable buffer transfers by setting the BTD bit in control register 0x08 to '1'. Then, select register page 2 using register address 0x7F. You can now load the necessary C and U data registers for the intended application by writing the corresponding data buffer addresses. When you have finished writing the C and U data, select register page 0 using register address 0x7F. Re-enable buffer transfers by setting the BTD bit in control register 0x08 to '0'.

Copyright © 2006–2009, Texas Instruments Incorporated

#### **Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from Revision B (October 2007) to Revision C                                   |      |  |  |  |

|----------------------------------------------------------------------------------------|------|--|--|--|

| Corrected statement concerning direction to drive PCMEN (pin 16) to disable PCM output | 18   |  |  |  |

| Changes from Revision A (May 2007) to Revision B                                       | Page |  |  |  |

| Changed Figure 26 y-axis value from (dB) to (db/10,000)                                | 12   |  |  |  |

|                                                                                        |      |  |  |  |

#### PACKAGE OPTION ADDENDUM

www.ti.com 24-Jul-2009

#### **PACKAGING INFORMATION**

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | e Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|------|----------------|---------------------------|------------------|------------------------------|

| PCM4220PFB       | ACTIVE                | TQFP            | PFB                | 48   | 250            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-3-260C-168 HR          |

| PCM4220PFBG4     | ACTIVE                | TQFP            | PFB                | 48   | 250            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-3-260C-168 HR          |

| PCM4220PFBR      | ACTIVE                | TQFP            | PFB                | 48   | 1000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-3-260C-168 HR          |

| PCM4220PFBRG4    | ACTIVE                | TQFP            | PFB                | 48   | 1000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-3-260C-168 HR          |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### PACKAGE MATERIALS INFORMATION

www.ti.com 14-Jul-2012

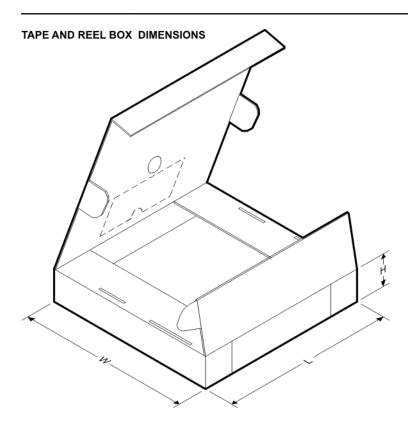

#### TAPE AND REEL INFORMATION

#### **REEL DIMENSIONS**

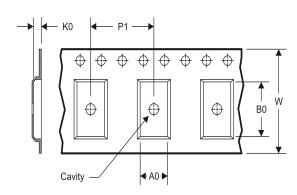

#### **TAPE DIMENSIONS**

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

#### TAPE AND REEL INFORMATION

#### \*All dimensions are nominal

| Device      | Package<br>Type | Package<br>Drawing |    |      | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| PCM4220PFBR | TQFP            | PFB                | 48 | 1000 | 330.0                    | 16.4                     | 9.6        | 9.6        | 1.5        | 12.0       | 16.0      | Q2               |

www.ti.com 14-Jul-2012

#### \*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| PCM4220PFBR | TQFP         | PFB             | 48   | 1000 | 367.0       | 367.0      | 38.0        |

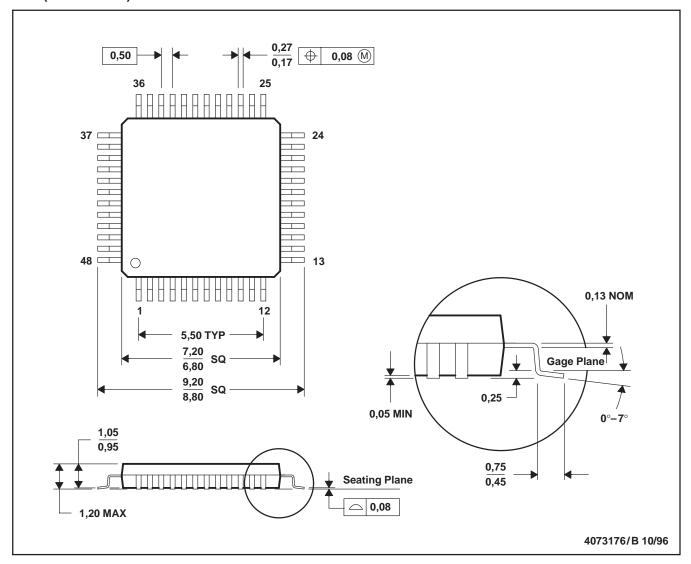

#### PFB (S-PQFP-G48)

#### PLASTIC QUAD FLATPACK

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Falls within JEDEC MS-026

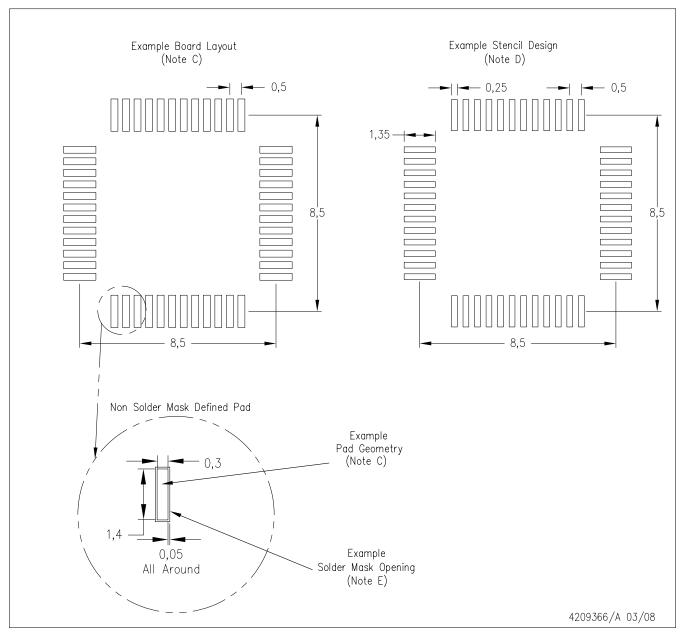

### PFB (S-PQFP-G48)

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525.

- E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46C and to discontinue any product or service per JESD48B. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.