# Signetics

#### **Linear Products**

### DESCRIPTION

The PCF8573 is a low threshold, monolithic CMOS circuit that functions as a real-time clock/calendar in the Inter IC (I<sup>2</sup>C) bus-oriented microcomputer systems. The device includes an addressable time counter and alarm register, both for minutes, hours, days and months. Three special control/status flags, COMP, POWF and NODA, are also available. Information is transferred serially via a two-lin bidirectional bus (I<sup>2</sup>C). Back-up for the clock during supply interruptions is provided by a 1.2V nickel cadmium battery. The time base is generated from a 32.768kHz crystalcontrolled oscillator.

# PCF8573 Clock/Calendar with Serial I/O

**Product Specification**

#### FEATURES

- Serial input/output bus (I<sup>2</sup>C) interface for minutes, hours, days and months

- Additional pulse outputs for seconds and minutes

- Alarm register for presetting a time for alarm or remote switching functions

- Battery back-up for clock function during supply interruption

- Crystal oscillator control (32.768kHz)

- APPLICATIONS

- Automotive

- Telephony

#### **ORDERING INFORMATION**

| DESCRIPTION                   | TEMPERATURE RANGE | ORDER CODE |

|-------------------------------|-------------------|------------|

| 16-Pin Plastic DIP (SOT-38)   | -40°C to +85°C    | PCF8573PN  |

| 16-Pin Plastic SOL (SOT-162A) | -40°C to +85°C    | PCF8573T   |

### ABSOLUTE MAXIMUM RATINGS

| SYMBOL                             | PARAMETER                                         | RATING      | UNIT |

|------------------------------------|---------------------------------------------------|-------------|------|

| V <sub>DD</sub> - V <sub>SS1</sub> | Supply voltage range (clock)                      | -0.3 to +8  | v    |

| V <sub>DD</sub> - V <sub>SS2</sub> | Supply voltage range (I <sup>2</sup> C interface) | -0.3 to +8  | V    |

| I <sub>IN</sub>                    | Input current                                     | 10          | mA   |

| lout                               | Output current                                    | 10          | mA   |

| PD                                 | Maximum power dissipation per package             | 200         | mW   |

| T <sub>A</sub>                     | Operating ambient temperature range               | -40 to +85  | °C   |

| T <sub>STG</sub>                   | Storage temperature range                         | -65 to +150 | °C   |

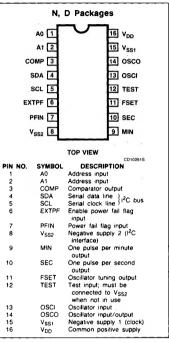

### **PIN CONFIGURATION**

# PCF8573

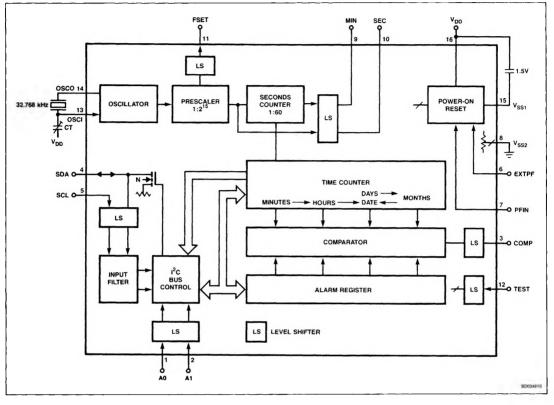

### **BLOCK DIAGRAM**

## PCF8573

# DC ELECTRICAL CHARACTERISTICS $V_{SS2} = 0V$ ; $T_A = -40$ to + 85°C, unless otherwise specified. Typical values at $T_A = +25$ °C.

| CYMDOL                                   | DADAMETER                                                                                                                       |                                                |         |                                       |          |  |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|---------|---------------------------------------|----------|--|

| SYMBOL                                   | PARAMETER                                                                                                                       | Min                                            | Max     | UNIT                                  |          |  |

| Supply                                   |                                                                                                                                 |                                                |         |                                       |          |  |

| V <sub>DD</sub> - V <sub>SS2</sub>       | Supply voltage (I <sup>2</sup> C interface)                                                                                     | 2.5                                            | 5       | 6.0                                   | V        |  |

| $V_{DD} - V_{SS1}$                       | Supply voltage (clock)                                                                                                          | 1.1                                            | 1.5     | (V <sub>DD</sub> ~ V <sub>SS2</sub> ) | v        |  |

| - I <sub>SS1</sub><br>- I <sub>SS1</sub> | Supply current V <sub>SS1</sub><br>at V <sub>DD</sub> - V <sub>SS1</sub> = 1.5V<br>at V <sub>DD</sub> - V <sub>SS1</sub> = 5V   |                                                | 3<br>12 | 10<br>50                              | μΑ<br>μΑ |  |

| -1 <sub>SS2</sub>                        | $ \begin{array}{l} Supply \ current \ V_{SS2} \\ at \ V_{DD} - V_{SS2} = 5V \\ (I_{O} = 0mA \ on \ all \ outputs) \end{array} $ |                                                |         | 50                                    | μA       |  |

| Inputs SCL,                              | SDA, A0, A1, TEST                                                                                                               |                                                |         |                                       |          |  |

| VIH                                      | Input voltage HIGH                                                                                                              | $0.7 	imes V_{DD}$                             |         |                                       | v        |  |

| V <sub>IL</sub>                          | Input voltage LOW                                                                                                               |                                                |         | $0.2 	imes V_{DD}$                    | v        |  |

| ±կ                                       | Input leakage current at $V_I = V_{SS2}$ to $V_{DD}$                                                                            |                                                |         | 1                                     | μA       |  |

| Inputs EXTP                              | F, PFIN                                                                                                                         |                                                |         |                                       |          |  |

| V <sub>IH</sub> – V <sub>SS1</sub>       | Input voltage HIGH                                                                                                              | 0.7	imes (V <sub>DD</sub> – V <sub>SS1</sub> ) |         |                                       | v        |  |

| V <sub>IL</sub> – V <sub>SS1</sub>       | Input voltage LOW                                                                                                               | 0                                              |         | $0.2 	imes (V_{DD} - V_{SS1})$        | v        |  |

| ±li                                      | Input leakage current<br>at $V_i = V_{SS1}$ to $V_{DD}$<br>at $T_A = 25^{\circ}C$ ;                                             |                                                |         | 1                                     | μA       |  |

| ± 11                                     | $V_{i} = V_{SS1}$ to $V_{DD}$                                                                                                   |                                                |         | 0.1                                   | μΑ       |  |

| Outputs SEC                              | , MIN, COMP, FSET (normal buffer outputs)                                                                                       |                                                | 1       | *                                     |          |  |

| V <sub>OH</sub><br>V <sub>OH</sub>       | Output voltage HIGH<br>at $V_{DD} - V_{SS2} = 2.5V;$<br>$-1_0 = 0.1mA$<br>at $V_{DD} - V_{SS2} = 4$ to 6V;<br>$-1_0 = 0.5mA$    | V <sub>DD</sub> - 0.4<br>V <sub>DD</sub> - 0.4 |         |                                       | v        |  |

|                                          | Output voltage LOW                                                                                                              |                                                |         |                                       |          |  |

| V <sub>OL</sub>                          | at $V_{DD} - V_{SS2} = 2.5V$ ;<br>$I_O = 0.3mA$<br>at $V_{DD} - V_{SS2} = 4$ to 6V;                                             |                                                |         | 0.4                                   | v        |  |

| VOL                                      | l <sub>O</sub> = 1.6mA                                                                                                          |                                                |         | 0.4                                   | V        |  |

| Output SDA                               | (N-Channel open drain)                                                                                                          |                                                |         | ,                                     |          |  |

| V <sub>OL</sub>                          | Output 'ON': $I_0 = 3mA$<br>at $V_{DD} - V_{SS2} = 2.5$ to 6V                                                                   |                                                |         | 0.4                                   | v        |  |

| lo                                       | Output 'OFF' (leakage current)<br>at $V_{DD} - V_{SS2} = 6V$ ; $V_0 = 6V$                                                       |                                                |         | 1                                     | μΑ       |  |

| Internal Thre                            | shold Voltage                                                                                                                   |                                                |         | ·                                     | ,        |  |

| V <sub>TH1</sub>                         | Power failure detection                                                                                                         | 1                                              | 1.2     | 1.4                                   | v        |  |

| V <sub>TH2</sub>                         | Power 'ON' reset<br>at V <sub>SCL</sub> = V <sub>SDA</sub> = V <sub>DD</sub>                                                    | 1.5                                            | 2.0     | 2.5                                   | v        |  |

-

## Clock/Calendar with Serial I/O

## PCF8573

# AC ELECTRICAL CHARACTERISTICS $V_{SS2} = 0V$ ; $T_A = -40$ to + 85°C, unless otherwise specified. Typical values at $T_A = +25^{\circ}C$ .

|                                  |                                                                                                                     |      | LIMITS               |          |          |  |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------|------|----------------------|----------|----------|--|

| SYMBOL                           | PARAMETER                                                                                                           | Min  | Тур                  | Max      | UNIT     |  |

| Rise and F                       | all Times of Input Signals                                                                                          |      |                      |          |          |  |

| t <sub>R</sub> , t <sub>F</sub>  | Input EXTPF                                                                                                         |      |                      | 1        | μs       |  |

| t <sub>R</sub> , t <sub>F</sub>  | Input PFIN                                                                                                          |      |                      | ~~~~     | μs       |  |

| t <sub>R</sub><br>t <sub>F</sub> | Input signals except EXTPF and PFIN<br>between V <sub>IL</sub> and V <sub>IH</sub> levels<br>rise time<br>fall time |      |                      | 1<br>0.3 | μs<br>μs |  |

| Frequency                        | at SCL                                                                                                              |      | 1 1                  |          | L        |  |

| t <sub>LOW</sub>                 | at $V_{DD} - V_{SS2} = 4$ to 6V<br>Pulse width LOW (see Figure 8)                                                   | 4.7  |                      |          | μs       |  |

| t <sub>HIGH</sub>                | Pulse width HIGH (see Figure 8)                                                                                     | 4    |                      |          | μs       |  |

| t <sub>i</sub>                   | Noise suppression time constant at SCL and SDA input                                                                | 0.25 | 1                    | 2.5      | μs       |  |

| CIN                              | Input capacitance (SCL, SDA)                                                                                        |      |                      | 7        | pF       |  |

| Oscillator                       |                                                                                                                     |      |                      |          |          |  |

| COUT                             | Integrated oscillator capacitance                                                                                   |      | 40                   |          | pF       |  |

| R <sub>F</sub>                   | Oscillator feedback resistance                                                                                      |      | 3                    |          | MΩ       |  |

| f/f <sub>OSC</sub>               | Oscillator stability for:                                                                                           |      | 2 × 10 <sup>-6</sup> |          |          |  |

|                                  | Quartz crystal parameters                                                                                           |      |                      | -        |          |  |

|                                  | Frequency = 32.768 kHz                                                                                              |      |                      |          |          |  |

| R <sub>S</sub>                   | Series resistance                                                                                                   |      |                      | 40       | kΩ       |  |

| CL                               | Parallel capacitance                                                                                                |      | 9                    |          | pF       |  |

| CT                               | Trimmer capacitance                                                                                                 | 5    |                      | 25       | pF       |  |

## PCF8573

### Table 1. Cycle Length of the Time Counter

| UNIT    | NUMBER OF BITS | COUNTING CYCLE | CARRY FOR FOLLOWING<br>UNIT | CONTENT OF MONTH COUNTER |

|---------|----------------|----------------|-----------------------------|--------------------------|

| Minutes | 7              | 00 to 59       | 59 → 00                     |                          |

| Hours   | 6              | 00 to 23       | $23 \rightarrow 00$         |                          |

| Days    | 6              | 01 to 28       | <b>28</b> → 01              |                          |

|         |                |                | or 29 → 01                  | 2 (see note)             |

|         |                | 01 to 30       | 30 → 01                     | 4, 6, 9, 11              |

|         |                | 01 to 31       | $31 \rightarrow 01$         | 1, 3, 5, 7, 8, 10, 12    |

| Months  | 5              | 01 to 12       | 12 → 01                     |                          |

NOTE: Day counter may be set to 29 by a write transmission with EXECUTE ADDRESS.

### FUNCTIONAL DESCRIPTION

#### Oscillator

The PCF8573 has an integrated crystal-controlled oscillator which provides the time base for the prescaler. The frequency is determined by a single 32.768kHz crystal connected between OSCI and OSCO. A trimmer is connected between OSCI and Von.

#### **Prescaler and Time Counter**

The prescaler provides a 128Hz signal at the FSET output for fine adjustment of the crystal oscillator without loading it. The prescaler also generates a pulse once a second to advance the seconds counter. The carry of the prescaler and the seconds counter are available at the outputs SEC and MIN, respectively, and are also readable via the I<sup>2</sup>C bus. The mark-to-space ratio of both signals is 1:1. The time counter is advanced one count by the falling edge of output signal MIN. A transition from HIGH to LOW of output signal SEC triggers MIN to change state. The time counter counts minutes, hours, days and months, and provides a full calendar function which needs to be corrected once every four years. Cycle lengths are shown in Table 1.

#### Alarm Register

The alarm register is a 24-bit memory. It stores the time-point for the next setting of the status flag COMP. Details of writing and reading of the alarm register are included in the description of the characteristics of the  $l^2C$  bus.

#### Comparator

The comparator compares the contents of the alarm register and the time counter, each

#### **Table 2. Power Fail Selection**

| EXTPF | PFIN | FUNCTION                        |  |  |  |  |  |

|-------|------|---------------------------------|--|--|--|--|--|

| 0     | 0    | Power fail is sensed internally |  |  |  |  |  |

| 0     | 1    | Test mode                       |  |  |  |  |  |

| 1     | 0    | Power fail is sensed externally |  |  |  |  |  |

| 1     | 1    | No power fail sensed            |  |  |  |  |  |

NOTE:

0: connected to V<sub>SS1</sub> (LOW)

1: connected to V<sub>DD</sub> (HIGH)

with a length of 24 bits. When these contents are equal, the flag COMP will be set 4ms after the falling edge of MIN. This set condition occurs once at the beginning of each minute. This information is latched, but can be cleared by an instruction via the I<sup>2</sup>C bus. A clear instruction may be transmitted immediately after the flag is set, and then it will be executed. Flag COMP information is also available at the output COMP. The comparison may be based upon hours and minutes only if the internal flag NODA (no date) is set. Flag NODA can be set and cleared by separate instructions via the I<sup>2</sup>C bus, but it is undefined until the first set or clear instruction has been received. Both COMP and NODA flags are readable via the I<sup>2</sup>C bus.

#### **Power On/Power Fail Detection**

If the voltage  $V_{DD} - V_{SS1}$  falls below a certain value, the operation of the clock becomes undefined. Thus, a warning signal is required to indicate that faultless operation of the clock is not guaranteed. This information is latched in a flag called POWF (Power Fail) and remains latched after restoration of the correct supply voltage until a write procedure with EXECUTIVE ADDRESS has been re-

ceived. The flag POWF can be set by an internally-generated power fail level-discriminator signal for application with ( $V_{DD} - V_{SS1}$ ) greater than  $V_{TH1}$ , or by an externally-generated power fail signal for application with ( $V_{DD} - V_{SS1}$ ) less than  $V_{TH1}$ . The external signal must be applied to the input PFIN. The input stage operates with signals of any slow rise and fall times. Internally-or externally-controlled POWF can be selected by input EXTPF as shown in Table 2.

The external power fail control operates by absence of the  $V_{DD} - V_{SS2}$  supply. Therefore, the input levels applied to PFIN and EXTPF must be within the range of  $V_{DD} - V_{SS1}$ . A LOW level at PFIN indicates a power fail. POWF is readable via the  $I^2C$  bus. A power-on reset for the  $I^2C$  bus control is generated on-chip when the supply voltage  $V_{DD} - V_{SS2}$  is less than  $V_{TH2}$ .

#### **Interface Level Shifters**

The level shifters adjust the 5V operating voltage ( $V_{DD} - V_{SS2}$ ) of the microcontroller to the internal supply voltage ( $V_{DD} - V_{SS1}$ ) of the clock/calendar. The oscillator and counter are not influenced by the  $V_{DD} - V_{SS2}$  supply

PCF8573

voltage. If the voltage  $V_{DD} - V_{SS2}$  is absent  $(V_{SS2} = V_{DD})$  the output signal of the level shifter is HIGH because  $V_{DD}$  is the common node of the  $V_{DD} - V_{SS2}$  and the  $V_{DD} - V_{SS1}$  supplies. Because the level shifters invert the input signal, the internal circuit behaves as if a LOW signal is present on the inputs. FSET, SEC, MIN and COMP are CMOS push-pull output stages. The driving capability of these outputs is lost when the supply voltage  $V_{DD} - V_{SS2} = 0$ .

# CHARACTERISTICS OF THE I<sup>2</sup>C BUS

The I<sup>2</sup>C bus is for 2-way, 2-line communication between different ICs or modules. The two lines are a serial data line (SDA) and a serial clock line (SCL). Both lines must be connected to a positive supply via a pull-up resistor when connected to the output stages of a device. Data transfer may be initiated only when the bus is not busy.

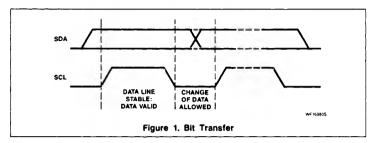

### Bit Transfer (see Figure 1)

One data bit is transferred during each clock pulse. The data on the SDA line must remain

stable during the HIGH period of the clock pulse as changes in the data line at this time will be interpreted as control signals.

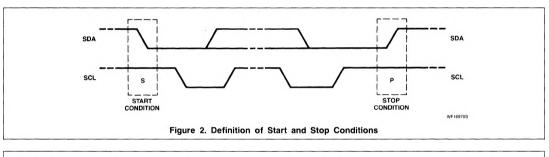

# Start and Stop Conditions (see Figure 2)

Both data and clock lines remain HIGH when the bus is not busy. A HIGH-to-LOW transition of the data line while the clock is HIGH is defined as the start condition (S). A LOW-to-HIGH transition of the data line while the clock is HIGH is defined as the stop condition (P).

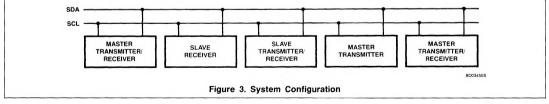

# System Configuration (see Figure 3)

A device generating a message is a "transmitter", a device receiving a message is the "receiver". The device that controls the message is the "master" and the devices which are controlled by the master are the "slaves".

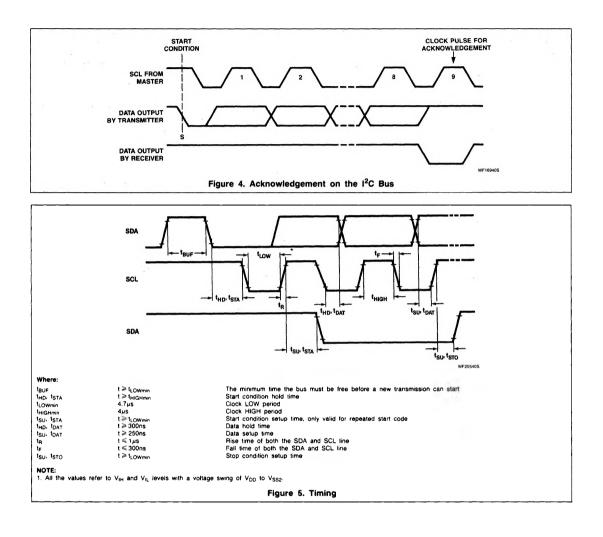

#### Acknowledge (see Figure 4)

The number of data bytes transferred between the start and stop conditions from transmitter to receiver is not limited. Each byte of eight bits is followed by one acknowledge bit. The acknowledge bit is a HIGH level put on the bus by the transmitter whereas the master generates an extra acknowledge-related clock pulse. A slave receiver which is addressed must generate an acknowledge after the reception of each byte. Also a master must generate an acknowledge after the reception of each byte that has been clocked out of the slave transmitter. The device that acknowledges has to pull down the SDA line during the acknowledge clock pulse. So that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse, setup and hold times must be taken into account. A master receiver must signal an end of data to the transmitter by not generating an acknowledge on the last byte that has been clocked out of the slave. In this event, the transmitter must leave the data line HIGH to enable the master to generate a stop condition.

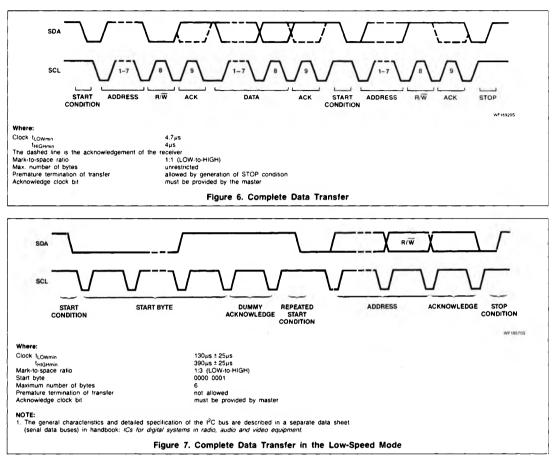

#### **Timing Specifications**

Masters generate a bus clock with a maximum frequency of 100kHz. Detailed timing is shown in Figure 5.

## PCF8573

## PCF8573

#### ADDRESSING

Before any data is transmitted on the  $i^2C$  bus, the device which should respond is addressed first. The addressing is always done with the first byte transmitted after the start procedure.

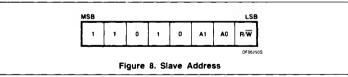

#### Slave Address

The clock/calendar acts as a slave receiver or slave transmitter. Therefore, the clock signal SCL is only an input signal, but the data signal SDA is a bidirectional line. The clock calendar slave address is shown in Figure 8.

The subaddress bits A0 and A1 correspond to the two hardware address pins A0 and A1 which allows the device to have 1 of 4 different addresses.

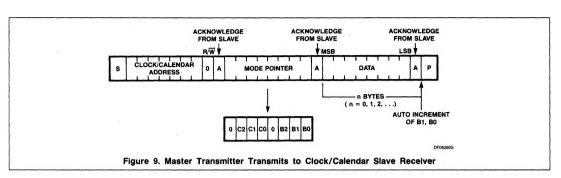

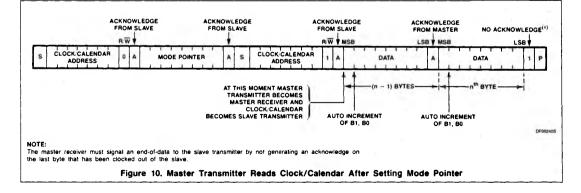

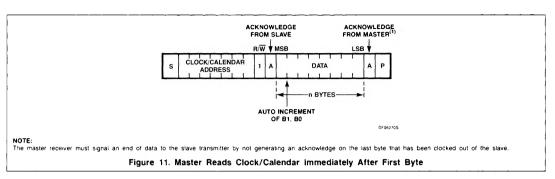

# Clock/Calendar READ/WRITE Cycles

The  $I^2C$  bus configuration for different clock/ calendar READ and WRITE cycles is shown in Figures 9 and 10.

The write cycle is used to set the time counter, the alarm register and the flags. The transmission of the clock/calendar address is

followed by the MODE-POINTER-WORD which contains a CONTROL-nibble (Table 3) and an ADDRESS-nibble (Table 4). The AD-DRESS-nibble is valid only if the preceding CONTROL-nibble is set to EXECUTE AD-DRESS. The third transmitted word contains the data to be written into the time counter or alarm register.

### Table 3. CONTROL-nibble

|   | C2 | C1 | C0 | FUNCTION                                                             |

|---|----|----|----|----------------------------------------------------------------------|

| 0 | 0  | 0  | 0  | Execute address                                                      |

| 0 | 0  | 0  | 1  | Read control/status flags                                            |

| 0 | 0  | 1  | 0  | Reset prescaler, including seconds counter; without carry for minute |

|   |    |    |    | counter                                                              |

| 0 | 0  | 1  | 1  | Time adjust, with carry for minute counter <sup>1</sup>              |

| 0 | 1  | 0  | 0  | Reset NODA flag                                                      |

| 0 | 1  | 0  | 1  | Set NODA flag                                                        |

| 0 | 1  | 1  | 0  | Reset COMP flag                                                      |

At the end of each data word the address bits B1, B0 will be incremented automatically provided the preceding CONTROL-nibble is set to EXECUTE ADDRESS. There is no carry to B2.

Table 5 shows the placement of the BCD upper and lower digits in the DATA byte for writing into the addressed part of the time counter and alarm register, respectively.

Acknowledgement response of the clock calendar as slave receiver is shown in Table 6.

#### NOTE:

1. If the seconds counter is below 30 there is no carry. This causes a time adjustment of max, -30 sec. From

the count 30 there is a carry which adjusts the time by max. + 30 sec.

#### Table 4. ADDRESS-nibble

|   |   | <b>B</b> 2 | <b>B</b> 1 | B0 | ADDRESSED TO:          |

|---|---|------------|------------|----|------------------------|

| C | ) | 0          | 0          | 0  | Time counter hours     |

| 0 | ) | 0          | 0          | 1  | Time counter minutes   |

| 0 | ) | 0          | 1          | 0  | Time counter days      |

| 0 | ) | 0          | 1          | 1  | Time counter months    |

| 0 | ) | 1          | 0          | 0  | Alarm register hours   |

| 0 | ) | 1          | 0          | 1  | Alarm register minutes |

| 0 | ) | 1          | 1          | 0  | Alarm register days    |

| 0 | ) | 1          | 1          | 1  | Alarm register months  |

## Table 5. Placement of BCD Digits in the DATA Byte

| MSB |       |       | DAT | Γ <b>A</b> |       |       | LSB |               |

|-----|-------|-------|-----|------------|-------|-------|-----|---------------|

|     | UPPER | DIGIT |     |            | LOWER | DIGIT |     |               |

| UD  | UC    | UB    | UA  | LD         | LC    | LB    | LA  | ADDRESSED TO: |

| х   | X     | D     | D   | D          | D     | D     | D   | Hours         |

| х   | D     | D     | D   | D          | D     | D     | D   | Minutes       |

| х   | X     | D     | D   | D          | D     | D     | D   | Days          |

| х   | X     | X     | D   | D          | D     | D     | D   | Months        |

NOTE:

1. Where "X" is the don't care bit and "D" is the data bit.

PCF8573

PCF8573

## Clock/Calendar with Serial I/O

To read the addressed part of the time counter and alarm register, plus information from specified control/status flags, the BCD

digits in the DATA byte are organized as shown in Table 7. The status of the MODE-POINTER-WORD concerning the CONTROL-nibble remains un-

changed until a write to MODE POINTER conditon occurs.

Table 6. Slave Receiver Acknowledgement

|   |              |    |    |   |            |    |         | ACK          | NOWLEDGE ON BYTE |     |

|---|--------------|----|----|---|------------|----|---------|--------------|------------------|-----|

|   | MODE POINTER |    |    |   |            |    | Address | Mode pointer | Data             |     |

|   | C2           | C1 | CO |   | <b>B</b> 2 | B1 | B0      |              |                  |     |

| 0 | 0            | 0  | 0  | 0 | Х          | Х  | X       | yes          | yes              | yes |

| 0 | 0            | 0  | 0  | 1 | X          | Х  | X       | yes          | no               | no  |

| 0 | 0            | 0  | 1  | Х | X          | Х  | X       | yes          | yes              | no  |

| 0 | 0            | 1  | 0  | Х | Х          | Х  | X       | yes          | yes              | no  |

| 0 | 0            | 1  | 1  | Х | X          | X  | X       | yes          | yes              | no  |

| 0 | 1            | 0  | 0  | Х | Х          | Х  | X       | yes          | yes              | no  |

| 0 | 1            | 0  | 1  | Х | X          | Х  | X       | yes          | yes              | no  |

| 0 | 1            | 1  | 0  | Х | X          | Х  | X       | yes          | yes              | no  |

| 0 | 1            | 1  | 1  | Х | X          | Х  | X       | yes          | no               | no  |

| 1 | X            | X  | X  | Х | X          | X  | X       | yes          | no               | no  |

NOTE:

1. Where "X" is the don't care bit.

Table 7. Organization of the BCD Digits in the DATA Byte

| MS | в    | D    | ATA |    | LSB  |         |      |                      |

|----|------|------|-----|----|------|---------|------|----------------------|

| U  | PPER | DIGI | т   |    | LOWE | R DIGIT |      | ADDRESSED TO:        |

| UD | UC   | UB   | UA  | LD | LC   | LB      | LA   |                      |

| 0  | 0    | D    | D   | D  | D    | D       | D    | Hours                |

| 0  | D    | D    | D   | D  | D    | D       | D    | Minutes              |

| 0  | 0    | D    | D   | D  | D    | D       | D    | Days                 |

| 0  | 0    | 0    | D   | D  | D    | D       | D    | Months               |

| 0  | 0    | 0    | •   | •• | NODA | COMP    | POWF | Control/status flags |

NOTES:

1. Where: "D" is the data bit, \* = minutes, \*\* = seconds.

# August 1, 1988

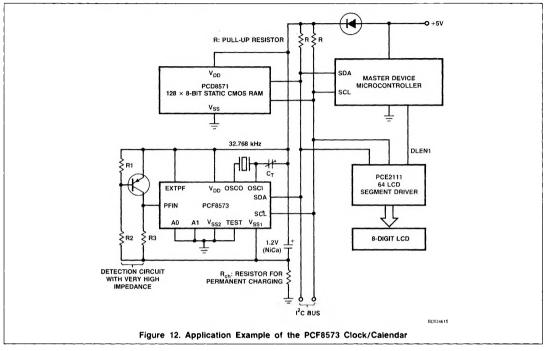

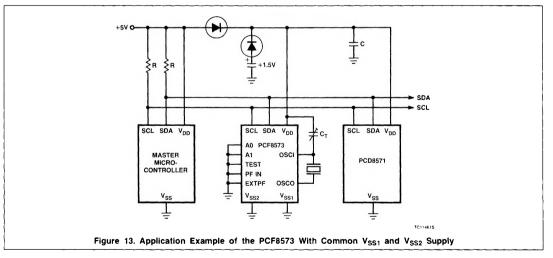

## APPLICATION INFORMATION

## PCF8573