# Signetics

# PCF8570 256 × 8 Static RAM

**Product Specification**

#### **Linear Products**

#### DESCRIPTION

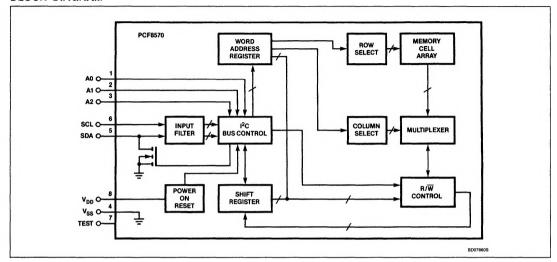

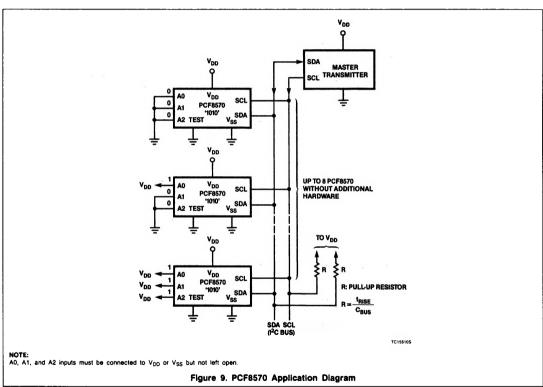

The PCF8570 is a low power 2048-bit static CMOS RAM organized as 256 words by 8-bits. Addresses and data are transferred serially via a two-line bidirectional bus (I<sup>2</sup>C). The built-in word address register is incremented automatically after each written or read data byte. Three address pins — A0, A1, and A2 — are used for programming the hardware address, allowing the use of up to eight devices connected to the bus without additional hardware.

#### **FEATURES**

- Operating supply voltage: 2.5V to 6V

- Low data retention voltage: min. 1.0V

- Low standby current: max. 5μA

- Power saving mode: typ. 50nA

- Serial input/output bus (I<sup>2</sup>C)

- Address by 3 hardware address pins

- Automatic word address incrementing

- 8-lead DIP package

#### **APPLICATIONS**

- Telephony RAM expansion for stored numbers in repertory dialing (e.g., PCD3343 applications)

- Radio and television channel presets

- Video cassette recorder

- General purpose RAM expansion for the microcomputer families MAB8400 and PCF84C00

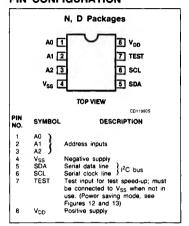

## PIN CONFIGURATION

#### ORDERING INFORMATION

| DESCRIPTION                       | TEMPERATURE RANGE | ORDER CODE |

|-----------------------------------|-------------------|------------|

| 8-Pin Plastic DIP (SOT-97A)       | -40°C to +85°C    | PCF8570PN  |

| 8-Pin Plastic SO (SO-8L; SOT-176) | -40°C to +85°C    | PCF8570TD  |

#### ABSOLUTE MAXIMUM RATINGS

| SYMBOL           | PARAMETER                           | RATING                       | UNIT |

|------------------|-------------------------------------|------------------------------|------|

| V <sub>DD</sub>  | Supply voltage range (Pin 8)        | -0.8 to +8.0                 | ٧    |

| Vı               | Voltage range on any input          | -0.8 to V <sub>DD</sub> +0.8 | ٧    |

| ± l <sub>1</sub> | DC input current (any input)        | 10                           | mA   |

| ± Io             | DC output current (any output)      | 10                           | mA   |

| ± IDD; Iss       | Supply current (Pin 4 or Pin 8)     | 50                           | mA   |

| P <sub>TOT</sub> | Power dissipation per package       | 300                          | mW   |

| Po               | Power dissipation per output        | 50                           | mW   |

| T <sub>STG</sub> | Storage temperature range           | -65 to +150                  | °C   |

| TA               | Operating ambient temperature range | -40 to +85                   | °C   |

PCF8570

#### **BLOCK DIAGRAM**

DC ELECTRICAL CHARACTERISTICS  $V_{DD}$  = 2.5 to 6V;  $V_{SS}$  = 0V;  $T_A$  = -40°C to +85°C, unless otherwise specified.

| SYMBOL                              | PARAMETER                                                                                                    |                     | LIMITS |                       |                |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------|---------------------|--------|-----------------------|----------------|

|                                     |                                                                                                              | Min                 | Тур    | Max                   | UNIT           |

| Supply                              |                                                                                                              |                     |        |                       |                |

| V <sub>DD</sub>                     | Supply voltage                                                                                               | 2.5                 |        | 6                     | ٧              |

| I <sub>DD</sub><br>I <sub>DDO</sub> | Supply current at $f_{SCL}$ = 100kHz; $V_1$ = $V_{SS}$ or $V_{DD}$ operating standby at $T_A$ = -25 to +70°C |                     |        | 200<br>15<br>5        | μΑ<br>μΑ<br>μΑ |

| V <sub>POR</sub>                    | Power-on reset voltage level <sup>1</sup>                                                                    | 1.5                 | 1.9    | 2.3                   | ٧              |

| Input SCL; i                        | input/output SDA                                                                                             |                     |        | ·                     |                |

| V <sub>IL</sub>                     | Input voltage LOW <sup>2</sup>                                                                               | -0.8                |        | $0.3 \times V_{DD}$   | ٧              |

| V <sub>IH</sub>                     | Input voltage HIGH <sup>2</sup>                                                                              | $0.7 \times V_{DD}$ |        | V <sub>DD</sub> + 0.8 | ٧              |

| loL                                 | Output current LOW at V <sub>OL</sub> = 0.4V                                                                 | 3                   | _      |                       | mA             |

| Іон                                 | Output leakage current HIGH at V <sub>OH</sub> = V <sub>DD</sub>                                             |                     |        | 250                   | nA             |

| ± I <sub>I</sub>                    | Input leakage current (A0, A1, A2) at V <sub>I</sub> = V <sub>DD</sub> or V <sub>SS</sub>                    |                     |        | 250                   | nA             |

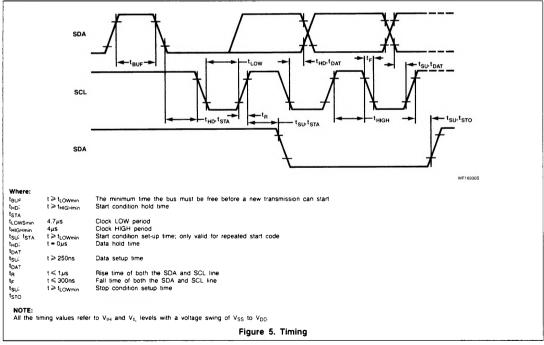

| f <sub>SCL</sub>                    | Clock frequency (Figure 5)                                                                                   | 0                   |        | 100                   | kHz            |

| Cı                                  | Input capacitance (SCL, SDA) at V <sub>I</sub> = V <sub>SS</sub>                                             |                     |        | 7                     | pF             |

| tsw                                 | Tolerable spike width on bus                                                                                 |                     |        | 100                   | ns             |

| LOW V <sub>DD</sub> d               | ata retention                                                                                                |                     |        |                       |                |

| V <sub>DDR</sub>                    | Supply voltage for data retention                                                                            | 1                   |        | 6                     | ٧              |

| I <sub>DDR</sub>                    | Supply current at V <sub>DDR</sub> = 1V                                                                      |                     |        | 5                     | μА             |

| IDDR                                | Supply current at V <sub>DDR</sub> = 1V; T <sub>A</sub> = -25 to +70°C                                       |                     |        | 2                     | μΑ             |

| Power savin                         | ng mode                                                                                                      |                     |        |                       |                |

| IDDR                                | Supply current at T <sub>A</sub> = 25°C; TEST = V <sub>DDR</sub>                                             |                     | 50     | 400                   | nA             |

### NOTES:

<sup>1.</sup> The power-on reset circuit resets the  $I^2C$  bus logic when  $V_{DD} < V_{POR}$ .

<sup>2.</sup> If the input voltages are a diode voltage above or below the supply voltage V<sub>OD</sub> or V<sub>SS</sub> an input current will flow; this current must not exceed ±0.5mA. August 1, 1988

PCF8570

# CHARACTERISTICS OF THE I<sup>2</sup>C BUS

The I<sup>2</sup>C bus is for 2-way, 2-line communication between different ICs or modules. The two lines are a serial data line (SDA) and a

serial clock line (SCL). Both lines must be connected to a positive supply via a pull-up resistor when connected to the output stages of a device. Data transfer may be initiated only when the bus is not busy.

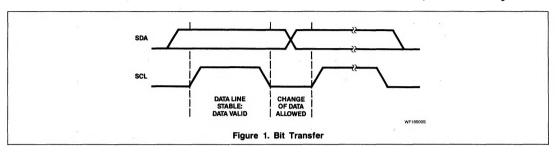

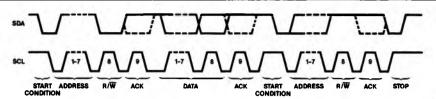

#### Bit Transfer

One data bit is transferred during each clock pulse. The data on the SDA line must remain stable during the HIGH period of the clock pulse, as changes in the data line at this time will be interpreted as control signals.

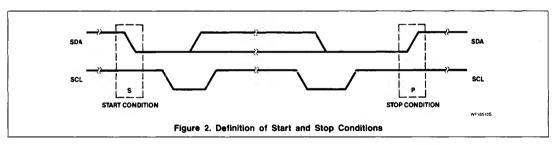

#### Start and Stop Conditions

Both data and clock lines remain HIGH when the bus is not busy. A HIGH-to-LOW transi-

tion of the data line while the clock is HIGH is defined as the start condition (S). A LOW-to-HIGH transition of the data line while the clock is HIGH is defined as the stop condition (P).

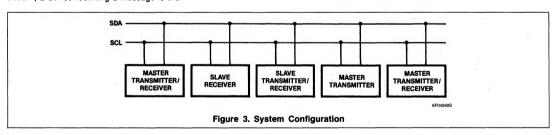

## **System Configuration**

A device generating a message is a "transmitter"; a device receiving a message is the

"receiver". The device that controls the message is the "master" and the devices which are controlled by the master are the "slaves".

### PCF8570

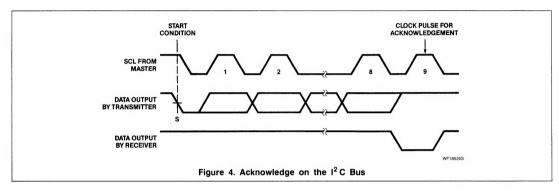

#### Acknowledge

The number of data bytes transferred between the start and stop conditions from transmitter to receiver is not limited. Each byte of eight bits is followed by one acknowledge bit. The acknowledge bit is a HIGH level put on the bus by the transmitter whereas the master generates an extra acknowledge re-

lated clock pulse. A slave receiver which is addressed must generate an acknowledge after the reception of each byte. Also a master must generate an acknowledge after the reception of each byte that has been clocked out of the slave transmitter. The device that acknowledges has to pull down the SDA line during the acknowledge clock pulse, so that the SDA line is stable LOW.

During the HIGH period of the acknowledge related clock pulse, setup and hold times must be taken into account. A master receiver must signal an end of data to the transmitter by not generating an acknowledge on the last byte that has been clocked out of the slave. In this event the transmitter must leave the data line HIGH to enable the master to generate a stop condition.

PCF8570

Where: Clock t<sub>LOWmin</sub>

4.7μs 4μs

Licking the distribution of the section of the sec

Figure 6. Complete Data Transfer in the High-Speed Mode

PCF8570

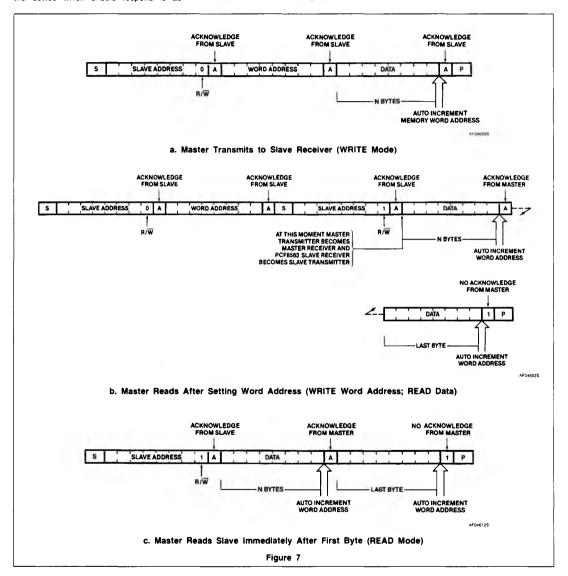

#### **Bus Protocol**

Before any data is transmitted on the I<sup>2</sup>C bus, the device which should respond is ad-

dressed first. The addressing is always done with the first byte transmitted after the start procedure. The I<sup>2</sup>C bus configuration for dif-

ferent PCF8570 READ and WRITE cycles is shown in Figure 7.

PCF8570

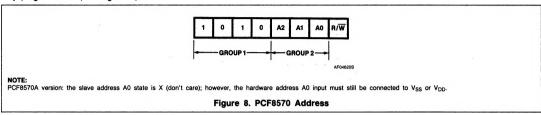

### **APPLICATION INFORMATION**

The PCF8570 slave address has a fixed combination 1010 as group 1, while group 2 is fully programmable (see Figure 8.)

9-36

PCF8570

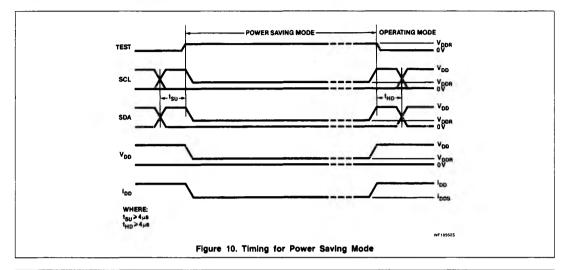

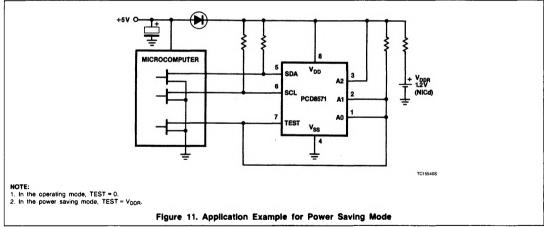

#### **POWER SAVING MODE**

With the condition TEST =  $V_{DDR}$ , the PCF8570 goes into the power saving mode.