# PAL10/10016RD8 ECL Registered Programmable Array Logic

#### **General Description**

The registered ECL PAL10/10016RD8 is offered in 10KH or 100K compatible versions. A maximum propagation delay of 6 ns (input to output) characterizes the performance of this ECL PAL® series. The ECL PAL family utilizes National Semiconductor's advanced oxide-isolated process and proven Titanium Tungsten (Ti-W) fuse technology to provide user-programmable logic to replace conventional ECL SSI/MSI gates and flip-flops. Typical chip count reduction gained by using PAL devices is greater than 4:1.

This family allows the system engineer to customize the chip by opening fuse links to configure AND and OR gates to perform the desired logic function. Complex interconnections that previously required time-consuming layout are thus transferred from PC board to silicon where they can easily be modified during prototype checkout or production.

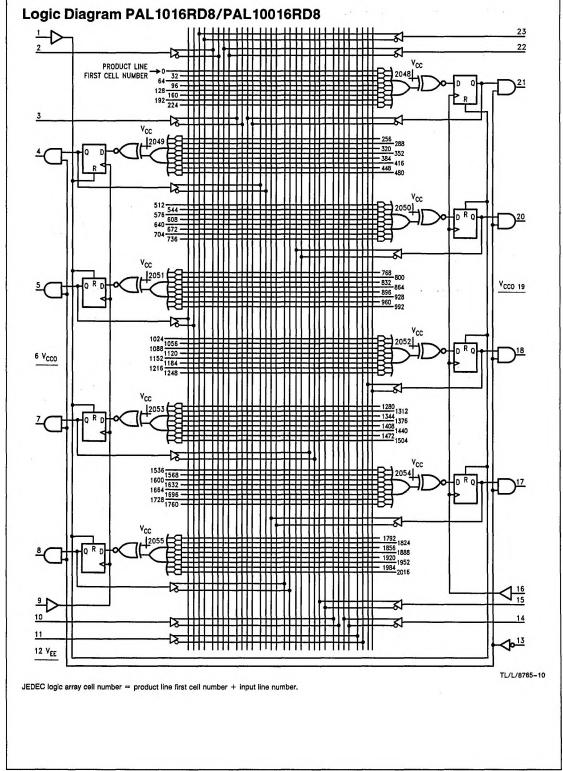

The PAL transfer function is the familiar sum-of-products implemented with a single array of fusible links. The PAL device incorporates a programmable AND array driving a fixed OR array. The AND term logic matrix incorporates 16 complementary inputs and 64 product terms. The 64 product terms are grouped into eight OR functions with eight product terms each. All devices in this family are provided with output polarity fuses. These fuses permit the designer to configure each output independently to produce either a logic high (by leaving the fuse intact) or a logic low (by programming the fuse) when the equation defining that output is satisfied. In addition, the ECL PAL family offers these options:

- Output registers

- · Dual (split) clocks

Product terms with all fuses programmed assume a logical high state, while product terms connected to both the true and complement of any input assume a logical low state. All product terms in an unprogrammed part are logically low. All input and I/O pins have on-chip 50 k $\Omega$  pull-down resistors. Registers consist of D-type flip-flops which are loaded in response to the low-to-high transition of the clock input(s).

Fuse symbols have been omitted from the logic diagrams to allow the designer use of the diagrams for logic editing.

These ECL PAL devices may be programmed on several TTL PLD programmers. Programming is accomplished with TTL voltage levels. Once the PAL is programmed and verified, an additional security fuse may be programmed to defeat verification. This feature gives the user a proprietary circuit which is difficult to copy.

#### **Features**

■ High speed:

Combinatorial outputs

tpd = 6 ns max

Registered outputs

$t_{su} = 5 \text{ ns min}$

$t_{clk} = 3.5 \text{ ns max}$

f<sub>max</sub> = 117 MHz max

- Both 10 KH and 100K I/O compatible versions

- Eight output functions with feedback; eight dedicated inputs

- Eight registered outputs

- Individually programmable polarity on all logic outputs

- Output enable gate on all registered outputs

- Reliable Titanium Tungsten fuses

- Security fuse to prevent direct copying

- Programmed on conventional TTL PLD programmers

- Fully Supported by PLAN™ Software

- Packaging:

24-pin thin DIP (0.300") 24-pin QUAD CERPAK

#### **Applications**

- Programmable replacement for ECL logic

- Programmable state machine

- Address or instruction decoding

#### **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Temperature Under Bias (Ambient) Storage Temperature Range

-55°C to +125°C

V<sub>EE</sub> Relative to V<sub>CC</sub>

Input Voltage

-65°C to +150°C -7V to +0.5V $V_{EE}$  to +0.5V **Output Current**

Lead Temperature (Soldering, 10 seconds)

**ESD Tolerance**

-50 mA 300°C 1000V

$C_{ZAP} = 100 pF$

$R_{ZAP} = 1500\Omega$

Test Method: Human Body Model Test Specification: NSC SOP-5-028

## Electrical Characteristics Over Recommended Operating Conditions (Note 1)

| Symbol          | Parameter                         | Conditions                                                     |                       | TA                      | Min                     | Max                     | Units |

|-----------------|-----------------------------------|----------------------------------------------------------------|-----------------------|-------------------------|-------------------------|-------------------------|-------|

| VIH             | High Level Input Voltage          | Guaranteed Input Voltage<br>High For All Inputs                |                       | + 25°C                  | -1170<br>-1130<br>-1070 | -840<br>-810<br>-735    | mV    |

|                 |                                   |                                                                | 100K                  | 0°C to +85°C            | -1165                   | -880                    |       |

| V <sub>IL</sub> | Low Level Input Voltage           | Guaranteed Input Voltage<br>Low For All Inputs                 | 10 KH                 | 0°C<br>+ 25°C<br>+ 75°C | -1950<br>-1950<br>-1950 | -1480<br>-1480<br>-1450 | mV    |

|                 |                                   |                                                                | 100K                  | 0°C to +85°C            | -1810                   | -1475                   |       |

| V <sub>OH</sub> | High Level Output Voltage         | $V_{IN} = V_{IH}$ Max. or $V_{IL}$ Min.                        | 10 KH                 | 0°C<br>+ 25°C<br>+ 75°C | -1020<br>-980<br>-920   | -840<br>-810<br>-735    | mV    |

|                 |                                   |                                                                | 100K                  | 0°C to +85°C            | -1025                   | -880                    |       |

| V <sub>OL</sub> | Low Level Output Voltage          | V <sub>IN</sub> = V <sub>IH</sub> Max. or V <sub>IL</sub> Min. | 10 KH                 | 0°C<br>+ 25°C<br>+ 75°C | -1950<br>-1950<br>-1950 | -1630<br>-1630<br>-1600 | mV    |

|                 |                                   | _                                                              | 100K                  | 0°C to +85°C            | -1810                   | -1620                   |       |

| ΊΗ              | High Level Input Current (Note 3) | V <sub>IN</sub> = V <sub>IH</sub> Max.                         | 10 KH                 | 0°C<br>+75°C            |                         | 220                     | μА    |

|                 |                                   |                                                                | 100K                  | 0°C to +85°C            |                         |                         | İ     |

| lıL .           | Low Level Input Current           | V <sub>IN</sub> = V <sub>IL</sub> Min. Except I/O Pins         | 10 KH                 | 0°C<br>+75°C            | 0.5                     |                         | μА    |

|                 |                                   |                                                                | 100K                  | 0°C to +85°C            |                         | _                       | l     |

| IEE             | Supply Current                    | V <sub>EE</sub> = Min.<br>All Inputs and                       | LD8, LD4,<br>RD4, RC4 |                         | -260                    |                         | mA    |

|                 |                                   | Outputs Open                                                   | RD8, RC8              |                         | -280                    |                         | l     |

## **Recommended Operating Conditions**

| Symbol | Parameter                       |       | Min   | Тур  | Max   | Units |

|--------|---------------------------------|-------|-------|------|-------|-------|

| VEE    | Supply Voltage                  | 10 KH | -5.46 | -5.2 | -4.94 | v     |

|        | <b>!</b>                        | 100K  | -4.73 | -4.5 | -4.27 | \     |

| Т      | Operating Temperature (Note 2)  | 10 KH | 0     |      | + 75  | °C    |

| :      |                                 | 100K  | 0     |      | +85   |       |

| RL     | Standard 10 KH/100K Load        |       |       | 50   |       | Ω_    |

| CL     | Standard 10 KH/100K Load        | -     |       | 5    |       | pF    |

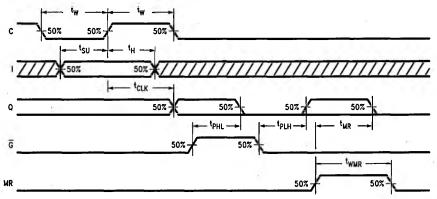

| tsu    | Setup Time of Input or Feedback |       | 5     |      |       | ns    |

| tн     | Input Hold Time                 |       | 0     |      |       | ns    |

| tw     | Clock or Enable Pulse Width     |       | 4     |      |       | ns    |

| twmR   | Master Reset Pulse Width        |       | 4     |      |       | ns    |

Note 1: This product family has been designed to meet the specification in the test table after thermal equilibrium has been established. The circuit is in a test socket or mounted on a printed circuit board and transverse air flow greater than 500 linear fpm is maintained.

Note 2: Operating temperatures for circuits in Dual-In-Line packages are specified as ambient temperatures (TA) with circuits mounted in socket or printed circuit board and transverse airflow exceeding 500 linear feet per minute. Operating temperatures for circuits packaged in QUAD CERPAK are specified as case temperatures (T<sub>C</sub>).

Note 3: Except for clock inputs (350  $\mu$ A) and MR (1 mA).

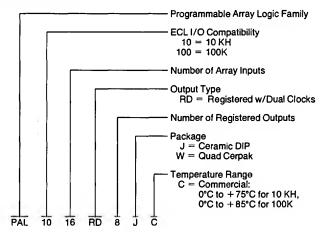

## **Ordering Information**

# Switching Characteristics Over Recommended Operating Conditions

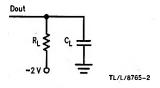

Output Load:  $R_L = 50\Omega$  to -2.0V,  $C_L = 5$  pF to GND

| Symbol                        | Parameter                   | Measured                            |          | Min | Max   | Units |

|-------------------------------|-----------------------------|-------------------------------------|----------|-----|-------|-------|

| - Cymbol                      | T drameto:                  | From                                | То       | ]   | Wax _ | Jints |

| t <sub>CLK</sub> (Note 1)     | Clock to Output or Feedback | C <sub>n</sub> ↑                    | Q        |     | 3.5   | ns    |

| tpD (Note 2)                  | Input or Feedback to Output |                                     | Q or I/O |     | 6     | ns    |

| t <sub>PLH</sub> (Note 1)     | Output Enable               | Ğ↓                                  | Q ↑      |     | 4.0   | ns    |

| t <sub>PHL</sub> (Note 1)     | Output Disable              | G↑                                  | αŢ       |     | 4.0   | ns    |

| t <sub>MR</sub> (Note 1)      | Master Reset to Output      | MR ↑                                | a↓       |     | 5.5   | ns    |

| f <sub>MAX</sub> (Notes 1, 3) | Maximum Frequency           |                                     |          |     | 117   | MHz   |

| t <sub>r</sub>                | Output Rise Time            | Measured Between 20% and 80% points |          | 0.5 | 2.5   | ns    |

| tı                            | Output Fall Time            |                                     |          | 0.5 | 2.5   | ns    |

Note 1: Applies to registered outputs.

Note 2: Applies to combinatorial outputs.

Note 3:  $f_{MAX} = (t_{SU} + t_{CLK})^{-1}$

#### **Test Load**

## **Timing Waveform—All Registered Outputs**

TL/L/8765-3

## **Connection Diagram**

24-Pin Dual-In-Line Package PAL1016RD8/PAL10016RD8

TL/L/8765-5

# **Pin Descriptions**

| Pin | Description                            |

|-----|----------------------------------------|

| ı   | Eight dedicated inputs to logic array. |

Q Eight outputs from registered logic functions.

C1 Clock input for registers on output pins\* 4, 5, 7 and 8 on dual-clock devices; Data is written into registers on rising edge of clock.

C2 Clock input for registers on output pins\* 17, 18, 20 and 21 on dual-clock devices; Data is written into registers on rising edge of clock.

MR Master Reset input. Asynchronously resets all registers to the low state while MR is high (overrides clock).

G Output enable input. Enables output drivers while G is low; forces all registered output drivers to the low state as long as G is high. Register contents and feedbacks are not affected. Combinatorial outputs are not affected.

V<sub>EE</sub> Supply voltage.

V<sub>CC</sub> Ground for internal circuitry.

V<sub>CCO</sub> Ground for output drivers (4 outputs per V<sub>CCO</sub>).

\*Corresponds to DIP pinout

## **Functional Testing**

As with all field-programmable devices, the user of ECL PAL devices provides the final manufacturing step. While National's PAL devices undergo extensive testing when they are manufactured, their logic function can be fully tested only after they have been programmed to the user's pattern.

To ensure that the programmed PAL devices will operate properly in your system, National Semiconductor (along with most other manufacturers of PAL devices) strongly recomends that PAL devices be functionally tested before they are installed in your system. Even though the number of

post-programming functional failures is small, testing the logic function of the PAL devices before they reach system assembly will save board debugging and rework costs. Refer to National Semiconductor's Application Note #351 and the *Programmable Logic Design Guide* for more information about the functional testing of PAL devices.

For a list of current programming support tools for ECL PAL devices, please contact your local National Semiconductor sales office.