# Signetics

#### **Linear Products**

#### DESCRIPTION

The NE5045 is a serial input, parallel output, decoder intended for applications in pulse width or pulse position modulation systems. The serial input pulse, either positive or negative, is shaped and amplified before being fed to the counter/decoder. An integrating type sync. separator detects pulses greater than t<sub>W</sub> = R<sub>S</sub>C<sub>S</sub>. The amplified input pulse triggers an internal one-shot (minimum pulse) which in turn clocks the counter-decoder, thereby enhancing system noise rejection. A missing pulse detector resets the decoder during the sync. pause. An internal voltage regulator supplies power for the radio receiver. providing excellent isolation from the power supply as well as the decoder logic.

#### **FEATURES**

- Decodes up to 7 channels

- High gain input amplifier

- Externally set sync. pause and minimum pulse

#### **BLOCK DIAGRAM**

# NE5045 Seven-Channel RC Decoder

**Product Specification**

- Wide supply voltage range, 3.6V - 8V

- Positive or negative pulse inputs

- Noise and flutter rejection

- Outputs reset to zero without inputs

- Compatible with all transmission mediums

#### **APPLICATIONS**

- Radio-controlled aircraft, cars, boats, trains

- Industrial controllers

- Remote-controlled entertainment systems

- Security systems

- Instrumentation recorders/ controls

- Remote analog/digital data transmission

- Automotive sensor systems

- Robotics

- Telemetry

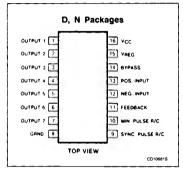

#### PIN CONFIGURATION

### NE5045

### ORDERING INFORMATION

| DESCRIPTION        | TEMPERATURE RANGE | ORDER CODE |

|--------------------|-------------------|------------|

| 16-Pin Plastic SO  | 0 to +70°C        | NE5045D    |

| 16-Pin Plastic DIP | 0 to +70°C        | NE5045N    |

#### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| SYMBOL           | PARAMETER                | RATING              | UNIT |

|------------------|--------------------------|---------------------|------|

| V <sub>CC</sub>  | Supply voltage           | 10                  | V    |

| lout             | Regulator output current | -25                 | mA   |

|                  | Decoded output current   | ± 5                 | mA   |

|                  | Pause input voltage      | 0 to V <sub>R</sub> | V    |

| V <sub>IN</sub>  | Input amplifier voltage  | 0 to V <sub>R</sub> | V    |

| T <sub>A</sub>   | Operating temperature    | 0 to +70            | °C   |

| T <sub>STG</sub> | Storage temperature      | -65 to +150         | °C   |

NOTE:

1.  $T_A = 25^{\circ}C$  unless otherwise stated.

# DC ELECTRICAL CHARACTERISTICS Standard conditions: $T_A = 25^{\circ}C$ , $V_{CC} = 5.0V$ , unless otherwise stated, using Test Circuit.

| Jircur | t. |

|--------|----|

|        |    |

| SYMBOL PARAMETER              |                            | LIMITS                       |     |      |      |      |

|-------------------------------|----------------------------|------------------------------|-----|------|------|------|

|                               | PARAMETER                  | TEST CONDITIONS              | Min | Тур  | Max  | UNIT |

| Power sup                     | ply requirements           |                              |     |      |      |      |

| V <sub>CC</sub>               | Power supply voltage range | Test circuit                 | 3.6 |      | 8.0  | V    |

| lcc                           | Power supply current       | Excluding input bias current |     | 9.0  | 14.0 | mA   |

| Voltage re                    | gulator                    |                              |     |      |      |      |

| V <sub>R</sub>                | Output voltage             |                              | 3.7 | 4.1  | 4.5  | V    |

| I <sub>R</sub> Output current | V <sub>R</sub> ≥3.7V       |                              |     | ~15  | mA   |      |

|                               | Line regulation            | $V_{CC} = 6V$ to $8V$        |     | 0.01 | 0.05 | V/\  |

|                               | Voltage drop               | $V_{CC} = 4V, I_{R} = -10mA$ |     |      | 1.3  | V    |

| Input ampl                    | lifier                     |                              |     |      |      |      |

| BIAS                          | Input bias current         |                              |     | 10   | 100  | nA   |

| VIN                           | Input voltage range        |                              | 2.0 |      | 4.0  | V    |

|                               | Open-loop gain             |                              |     | 60   |      | dB   |

|                               | Feedback current           |                              | 100 | 200  | 400  | μA   |

|                               | Detection threshold        | Test circuit, ΔV12 & 13      |     | 8    | 20   | m٧   |

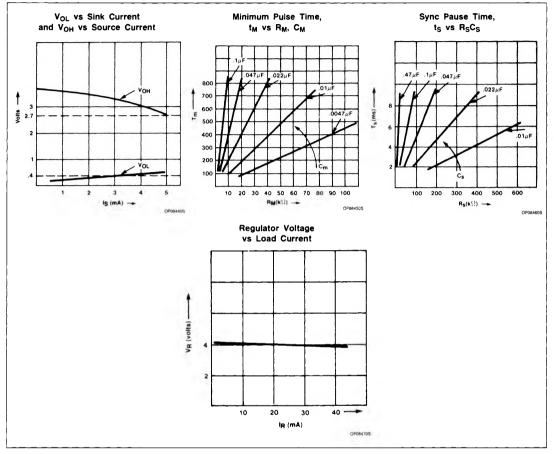

| ts                            | Sync. pause time           | $R_S C_S = 6.0 ms$           | 5.1 | 6.0  | 6.9  | ms   |

| t <sub>M</sub>                | Minimum pulse time         | $R_M C_M = 500 \mu s$        | 405 | 475  | 545  | μs   |

| Outputs -                     | - all channels             |                              |     |      |      |      |

| VOL                           | Output voltage LOW         | I <sub>SINK</sub> = 1mA      |     | 0.25 | 0.5  | V    |

| V <sub>OH</sub>               | Output voltage HIGH        | I <sub>SOURCE</sub> = 2mA    | 2.7 |      |      | V    |

### NE5045

### TYPICAL PERFORMANCE CHARACTERISTICS

8-17

## NE5045

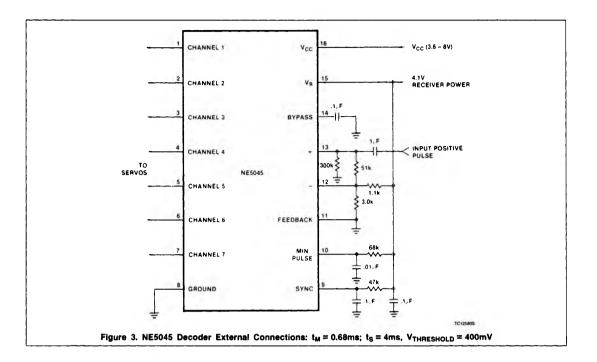

### TEST CIRCUIT

### NE5045

#### CIRCUIT OPERATION

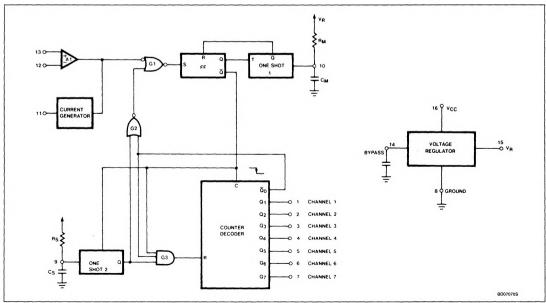

The NE5045 is a serial input, parallel output decoder containing all the active circuitry necessary to separate up to 7 channels of information in a pulse width modulated system. An internal voltage regulator provides excellent power supply rejection for the decoder as well as a regulated output for a radio receiver, if used.

The high gain input amplifier, A1 ( $A_V > 60$ dB), allows either positive or negative pulses to be used and has input bias currents less than 10nA. Signals as low as 10mV<sub>P-P</sub> can easily be demodulated. The feedback current generator can be used to provide positive feedback, thereby creating hysteresis in the input switching levels. Hysteresis prevents false triggering due to noise or IF amplifier distortion. If positive input pulses are used, the signal would be connected to the non-inverting input, Pin 13. In this case, the input threshold would be set by the voltage difference between Pin 12 and Pin 13, established externally with a resistive divider network. Design of the divider will be covered later. Negative input signals would be coupled to Pin 12, the inverting input.

The amplified signal from A1 is gated by G1 and in turn sets the flip-flop. Assume, for the time, that G2 is low. The combination of the flip-flop and One-Shot 1 produces a minimum pulse to clock the counter-decoder for each positive edge at Pin 13 which exceeds the voltage on Pin 12. The width of this pulse is:  $t_M = R_M C_M$ . With this arrangement, the system will not respond to any pulse after the first edge and before the end of  $t_{M}$ . In effect the input is turned off for a period equal to t<sub>M</sub> following the leading edge of each input pulse. The noise immunity of the decoder is thus enhanced by the ratio of t<sub>M</sub> to the period between input pulses. Obviously t<sub>M</sub> must be less than the shortest period between input pulses

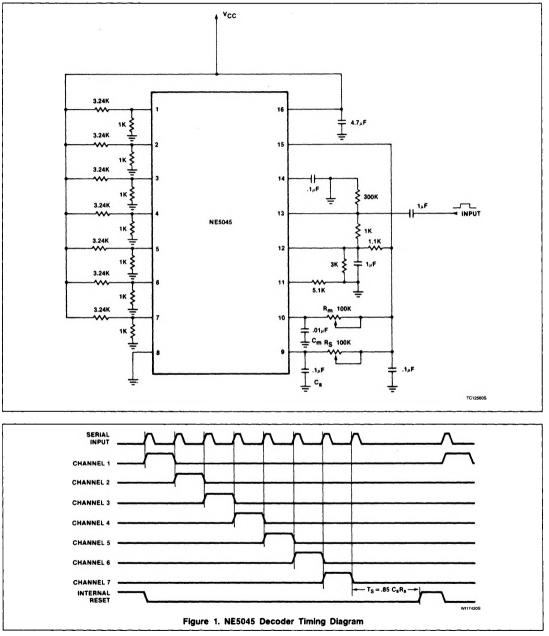

The counter is clocked and One-Shot 2 is reset (capacitor  $C_S$  is discharged) each time the flip-flop is set. When the flip-flop is reset,  $C_S$  begins to charge up through  $R_S$ . The time constant  $t_S=0.85\ R_SC_S$  is normally much larger than the time between input pulses so that the output of One-Shot 2 remains low until the last pulse of a given frame is received. Figure 1 shows the timing diagram for the decoder. After the last pulse in a frame (system synchronized)  $\overline{O}_O$  will go low and G2 will go high. The input is now disabled by G1 until One-Shot 2 times out, at which time G2 will go low.

This connection serves two purposes:

(1) establishes synchronization in no more than one frame and

(2) prevents the counter-decoder from overflowing due to extra noise pulses in a given frame. Thus, any noise pulses in a frame will only affect those channels after that pulse and only in that frame.

If fewer than 7 channels of input are used then  $\overline{O}_O$  is high after the last pulse and the counter-decoder is reset when One-Shot 2 goes high.

Each channel has a totem-pole output stage capable of sourcing 2mA and sinking 1mA.

The voltage regulator operates in two modes, depending on the power supply voltage. If Vcc is greater than 5V, the voltage regulator acts as a series pass regulator with a nominal output voltage of 4.1V. When  $V_{CC}$  is less than 5V, the regulator acts as a dynamic decoupler where the bypass capacitor on Pin 14 filters out line transients. The internal pass transistor acts like an emitter-follower whose base is decoupled by the bypass capacitor. The value of capacitance will depend upon the degree of smoothing required and the amplitude of the line transients. If the regulator provides power for the radio receiver, this capacitor may have to be as large as 33µF. However, if this is not done, 1µF should be sufficient.

#### **DECODER DESIGN EQUATIONS**

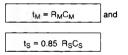

The design of the decoder's external circuitry is quite simple. The minimum pulse One-Shot (#1) and the synchronization One-Shot (#2) each have time periods given by:

respectively. The constraints on these time periods are  $t_M <$  the minimum input pulse width or time between leading edges of the input and  $t_S >$  maximum input pulse width but  $t_S <$  the sync pause (time between last pulse

in frame and first pulse of the following frame).

The design of the input amplifier biasing network depends upon a number of factors, including:

- 1. Pulse polarity

- 2. Pulse amplitude

- Variations in amplitude and noise

Detection threshold and hysteresis levels

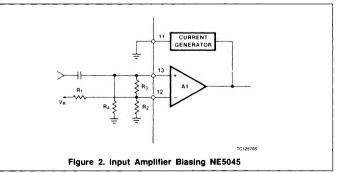

For a very simple case, assume the input is a positive pulse train and the threshold of detection is desired to be 400mV without hysteresis. Figure 2 shows the input amplifier along with the associated biasing circuits. The resistors  $R_1$  and  $R_2$  set the voltage on Pin 12, which should be between 2V to 5V.

$$V_{12} = V_R \frac{1}{1 + R_1 / R_2}$$

The threshold is set by the voltage drop across  $R_3$ , that is, the decoder will not be triggered until the voltage on Pin 13 exceeds the voltage on Pin 12.

$$V_{\text{THRESHOLD}} = V_{12} - V_{13}$$

$$V_{\text{THRESHOLD}} = V_{12} \left( \frac{1}{1 + R_4/R_3} \right)$$

If we assume  $V_R \approx 4.1V$  and let  $V_{12} = 3V$  then

$R_1 = 1.1k$

$R_2 = 3.0k$

The threshold is then set to 400mV by setting

$R_4/R_3 = 6.5$

$R_4$  should be sufficiently large so as to not load the input signal. If we let  $R_3 = 51 \rm k$  then  $R_4 = 330 \rm k$ . Figure 3 shows the external connections for a complete decoder. Note that this circuit does not have provisions for noise filtering or rejection of amplitude variations.

### NE5045