# **OKI** Semiconductor

# MSM80C154S/83C154S

**CMOS 8-bit Microcontroller**

### **GENERAL DESCRIPTION**

The MSM80C154S/MSM83C154S, designed for the high speed version of the existing MSM80C154/MSM83C154, is a higher performance 8-bit microcontroller providing low-power consumption.

The MSM80C154S/MSM83C154S covers the functions and operating range of the existing MSM80C154/83C154/80C51F/80C31F.

The MSM80C154S is identical to the MSM83C154S except it does not contain the internal program memory (ROM).

#### **FEATURES**

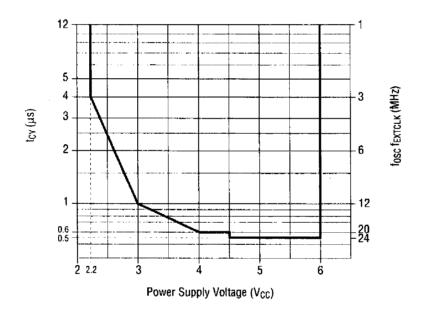

Operating range

Operating frequency :  $0 \text{ to } 3 \text{ MHz} (V_{cc}=2.2 \text{ to } 6.0 \text{ V})$

0 to 12 MHz ( $V_{cc}$ =3.0 to 6.0 V) 0 to 24 MHz ( $V_{cc}$ =4.5 to 6.0 V)

Operating voltage : 2.2 to 6.0 V

Operating temperature : -40 to +85°C (Operation at +125°C conforms to

the other specification.)

Fully static circuit

Upward compatible with the MSM80C51F/80C31F

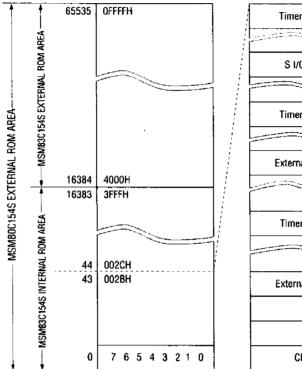

• On-chip program memory : 16K words x 8 bits ROM (MSM83C154S only)

• On-chip data memory : 256 words x 8 bits RAM External program memory address space : 64K bytes ROM (Max) : 64K bytes RAM External data memory address space • 1/O ports : 4 ports x 8 bits

(Port 1, 2, 3, impedance programmable) : 32 • 16-bit timer/counters

Multifunctional serial port : I/O Expansion mode

: UART mode (featuring error detection) • 6-source 2-priority level Interrupt and multi-level

Interrupt available by programming IP and IE registers Memory-mapped special function registers

Bit addressable data memory and SFRs • Minimum instruction cycle : 500 ns @ 24 MHz operation

Standby functions : Power-down mode (oscillator stop)

Activated by software or hardware; providing

ports with floating or active status

The software power-down stet mode is terminated by interrupt signal enabling execution from

the interrupted address.

• Package options

44-pin QFJ (QFJ44-P-S650) 44-pin TQFP (TQFP44-P-1010-K)

40-pin plastic DIP (DIP40-P-600) : (Product name: MSM80C154SRS/MSM83C154S-xxxRS) 44-pin plastic QFP (QFP44-P-910-2K) : (Product name: MSM80C154SGS-2K/MSM83C154SxxxGS-2K)

: (Product name: MSM80C154SJS/MSM83C154S-xxxJS) : (Product name: MSM80C154STS-K/MSM83C154S-xxxTS-K)

xxx: indicates the code number

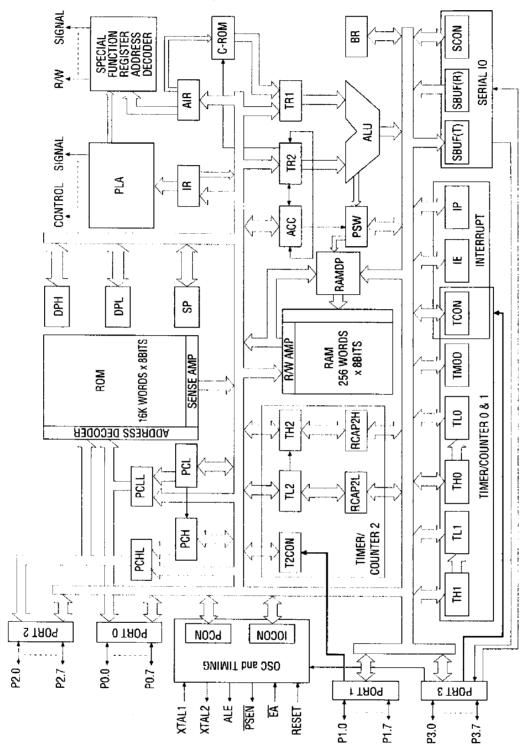

# BLOCK DIAGRAM (MSM83C154S)

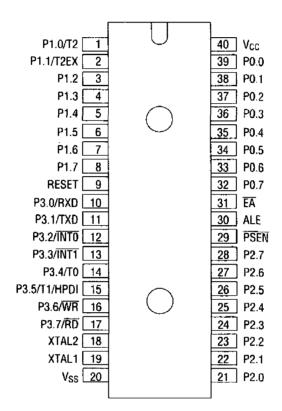

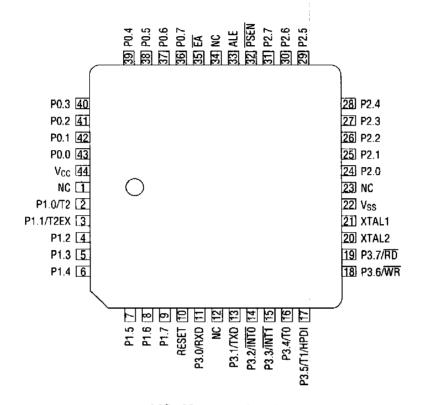

# PIN CONFIGURATION (TOP VIEW)

40-Pin Plastic DIP

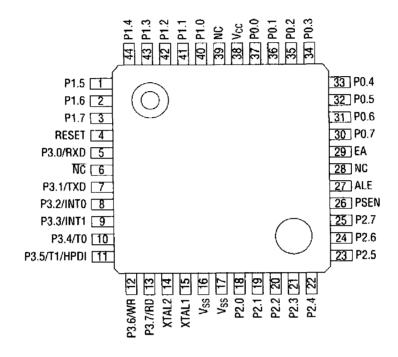

### **PIN CONFIGURATION (Continued)**

NC: No-connection pin

44-Pin Plastic QFP

NC : No-connection pin

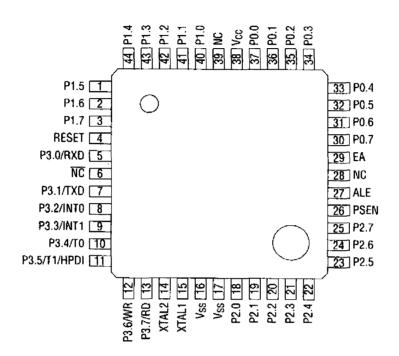

44-Pin Plastic TQFP

### **PIN CONFIGURATION (Continued)**

NC: No-connection pin

44-Pin Plastic QFJ

### PIN DESCRIPTIONS

| Symbol       | Descriptipn                                                                                                                                                                                                                                                                                                                                                           |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P0.0 to P0.7 | Bidirectional I/O ports. They are also the data/address bus (input/output of data and output of lower 8-bit address when external memory is accessed). They are open-drain outputs when used as I/O ports, but 3-state outputs when used as data/address bus.                                                                                                         |

| P1.0 to P1.7 | P1.0 to P1.7 are quasi-bidirectional I/O ports. They are pulled up internally when used as input ports. Two of them have the following secondary functions:  •P1.0 (T2) : used as external clock input pins for the timer/counter 2.  •P1.1 (T2EX) : used as trigger input for the timer/counter 2 to be reloaded or captured; causing the timer/counter 2 interrupt. |

| P2.0 to P2.7 | P2.0 to P2.7 are quasi-bidirectional I/O ports. They also output the higher 8-bit address when an external memory is accessed. They are pulled up internally when used as input ports.                                                                                                                                                                                |

| P3.0 to P3.7 | P3.0 to P3.7 are quasi-bidirectional I/O ports. They are pulled up internally when used as input ports. They also have the following secondary functions:  •P3.0 (RXD)                                                                                                                                                                                                |

|              | Serial data input/output in the I/O expansion mode and serial data input in the UART mode when the serial port is used.  •3.1 (TXD)                                                                                                                                                                                                                                   |

|              | Synchronous clock output in the I/O expansion mode and serial data output in the UART mode when the serial port is used.  -3.2 (INTO)                                                                                                                                                                                                                                 |

|              | Used as input pin for the external interrupt 0, and as count-up control pin for the timer/counter 0.  •3.3 (INT1)                                                                                                                                                                                                                                                     |

|              | Used as input pin for the external interrupt 1, and as count-up control pin for the timer/counter 1.  •3.4 (T0)                                                                                                                                                                                                                                                       |

|              | Used as external clock input pin for the timer/counter 0. •3.5 (T1)                                                                                                                                                                                                                                                                                                   |

|              | Used as external clock input pin for the timer/counter 1 and power-down-mode control input pin.  •3.6 (WR)                                                                                                                                                                                                                                                            |

|              | Output of the write-strobe signal when data is written into external data memory.  •3.7 (RD)                                                                                                                                                                                                                                                                          |

|              | Output of the read-strobe signal when data is read from external data memory.                                                                                                                                                                                                                                                                                         |

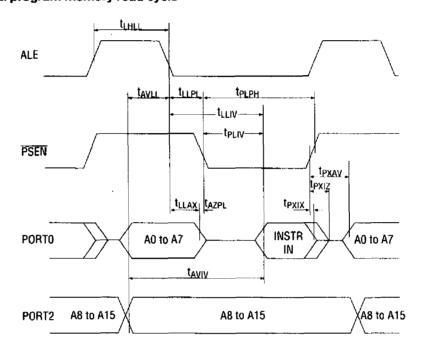

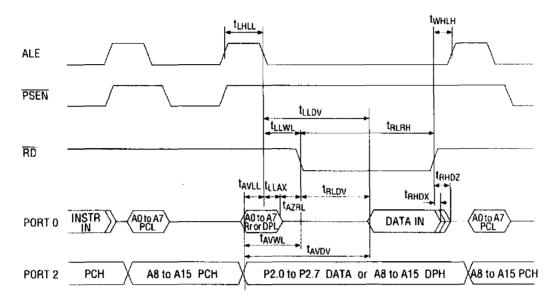

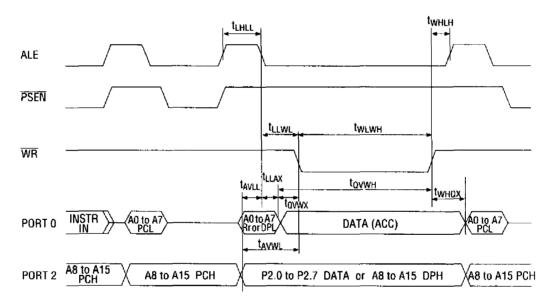

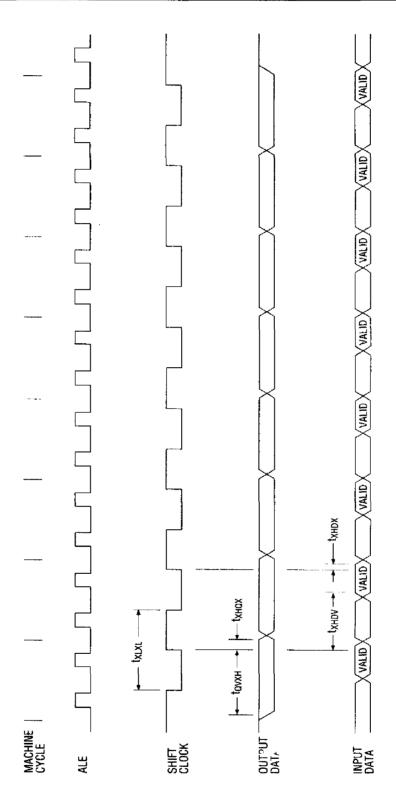

| ALE          | Address latch enable output for latching the lower 8-bit address during external memory access. Two ALE pulses are activated per machine cycle except during external data memory access at which time one ALE pulse is skipped.                                                                                                                                      |

| PSEN         | Program store enable output which enables the external memory output to the bus during external program memory access. Two PSEN pulses are activated per machine cycle except during external data memory access at which two PSEN pulses are skipped.                                                                                                                |

| EA           | When $\overline{EA}$ is held at "H" level, the MSM 83C154S executes instructions from internal program memory at address 0000H to 3FFFH, and executes instructions from external program memory above address 3FFFH.  When $\overline{EA}$ is held at "L" level, the MSM80C154S/MSM83C154S executes instructions from external program memory for all addresses.      |

# PIN Descriptions (Continued)

| Symbol          | Descriptipn                                                                                                                                                                                                                            |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET           | If this pin remains "H" for at least one machine cycle, the MSM80C154S/MSM83C154S is reset. Since this pin is pulled down internally, a power-on reset is achieved by simply connecting a capacitor between $V_{\rm CC}$ and this pin. |

| XTAL1           | Oscillator inverter input pin. External clock is input through XTAL1 pin.                                                                                                                                                              |

| XTAL2           | Oscillator inverter output pin.                                                                                                                                                                                                        |

| V <sub>CC</sub> | Power supply pin during both normal operation and standby operations.                                                                                                                                                                  |

| V <sub>SS</sub> | GND pin.                                                                                                                                                                                                                               |

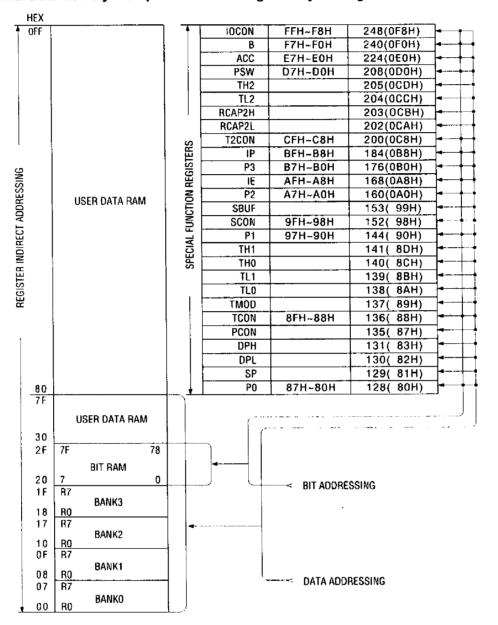

# REGISTERS

# **Diagram of Special Function Registers**

| REGISTER |    |    |            | BIT AD | DRESS |    |    |    | DIRECT     |

|----------|----|----|------------|--------|-------|----|----|----|------------|

| NAME     | b7 | b6 | b5         | b4     | b3    | b2 | b1 | bO | ADDRESS    |

| IOCON    | FF | FE | FD         | FC     | FB    | FA | F9 | F8 | 0F8H (248) |

| В        | F7 | F6 | F5         | F4     | F3    | F2 | F1 | F0 | 0F0H (240) |

| ACC      | E7 | E6 | E5         | E4     | E3    | E2 | E1 | E0 | 0E0H (224) |

| PSW      | D7 | D6 | D5         | D4     | D3    | D2 | D1 | D0 | 0D0H (208) |

| TH2      |    |    |            |        |       |    |    |    | 0CDH (205) |

| TL2      |    |    |            |        |       |    |    |    | 0CCH (204) |

| RCAP2H   |    |    |            | 1      | 1     | l  |    |    | 0CBH (203) |

| RCAP2L   |    |    |            |        |       |    |    |    | 0CAH (202) |

| T2CON    | CF | CE | CD         | CC     | СВ    | CA | C9 | CB | 0C8H (200) |

| ΙP       | BF | BE | BD         | BC     | BB    | BA | В9 | 88 | 0B8H (184) |

| P3       | B7 | 86 | B5         | B4     | В3    | B2 | B1 | 80 | 0B0H (176) |

| ΙE       | AF | AE | AD         | AC     | AB    | AA | A9 | A8 | 0A8H (168) |

| P2       | A7 | A6 | <b>A</b> 5 | A4     | А3    | A2 | A1 | A0 | 0A0H (160) |

| SBUF     |    |    | Ī          |        |       |    |    |    | 99H (153)  |

| SCON     | 9F | 9E | 9D         | 9C     | 9B    | 9A | 99 | 98 | 98H (152)  |

| P1       | 97 | 96 | 95         | 94     | 93    | 92 | 91 | 90 | 90H (144)  |

| TH1      |    |    |            |        |       |    |    |    | 8DH (141)  |

| TH0      |    |    |            |        |       |    |    |    | 8CH (140)  |

| TL1      |    |    |            |        |       |    |    |    | 8BH (139)  |

| TLO      |    |    |            |        |       |    |    |    | 8AH (138)  |

| TMOD     |    | T  | ]          |        |       |    | Ī  |    | 89H (137)  |

| TCON     | 8F | 8E | 8D         | 8C     | 88    | 8A | 89 | 88 | 88H (136)  |

| PCON     |    |    |            |        |       |    |    |    | 87H (135)  |

| DPH      |    |    |            |        |       |    |    |    | 83H (131)  |

| DPL      |    |    | <u> </u>   |        |       |    |    |    | 82H (130)  |

| SP       |    |    |            |        |       |    |    |    | 81H (129)  |

| P0       | 87 | 86 | 85         | 84     | 83    | 82 | 81 | 80 | 80H (128)  |

### **Special Function Registers**

### Timer mode register (TMOD)

| NAME         | ADDRESS | MSB                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                      |                                                              |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |                       | LSB     |  |

|--------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------|---------|--|

| NAME         | ADDRESS | 7                                                                                                                                                                                                                                                                                                     | 6                                                                                                                                                                                                                                                                                    | 5                                                            | 4                      | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2                  | 1                     | 0       |  |

| TMOD         | 89H     | GATE                                                                                                                                                                                                                                                                                                  | C/T                                                                                                                                                                                                                                                                                  | M1                                                           | MO                     | GATE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | C/T                | M1                    | MO      |  |

| BIT LOCATION | FLAG    |                                                                                                                                                                                                                                                                                                       | <u> </u>                                                                                                                                                                                                                                                                             |                                                              | FUNC                   | CTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                    |                       |         |  |

| TMOD.0       | MO      | M1                                                                                                                                                                                                                                                                                                    | МО                                                                                                                                                                                                                                                                                   | Timer/co                                                     | unter 0 m              | ode setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                    |                       |         |  |

|              |         | 0                                                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                    | 8-bit time                                                   | er/counter             | with 5-bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | prescalar.         |                       |         |  |

|              |         | 0                                                                                                                                                                                                                                                                                                     | 1                                                                                                                                                                                                                                                                                    | 16-bit tin                                                   | er/counte              | er.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                    |                       |         |  |

|              |         | 1                                                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                    | 8-bit time                                                   | ding.                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |                       |         |  |

| TMOD.1       | M1      | 1                                                                                                                                                                                                                                                                                                     | 1                                                                                                                                                                                                                                                                                    | and THO                                                      |                        | parated intended intended in parated in parategor in parated in pa |                    |                       |         |  |

| TMOD.2       | C/₹     | XTAL1•2<br>C/T = "0".                                                                                                                                                                                                                                                                                 | divided b                                                                                                                                                                                                                                                                            | ount clock d<br>by 12 clocks<br>applied to t                 | is the inp             | ut applied t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | o timer/co         |                       |         |  |

| TMOD.3       | GATE    | control th                                                                                                                                                                                                                                                                                            | ne start ar<br>is "1", tim                                                                                                                                                                                                                                                           | ", the TRO b<br>nd stop of ti<br>ner/counter<br>t signal are | mer/coun<br>O starts c | ter 0 counti<br>ounting wh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ing.<br>en both th | e TRO bit (           | of TCON |  |

| TMOD.4       | MO      | M1                                                                                                                                                                                                                                                                                                    | MO                                                                                                                                                                                                                                                                                   | Timer/co                                                     | unter 1 m              | ode setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                    |                       |         |  |

|              |         | 0                                                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                    | 8-bit time                                                   | er/counter             | with 5-bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | prescalar.         | · · · · · · · · · · · |         |  |

|              |         | 0                                                                                                                                                                                                                                                                                                     | 1                                                                                                                                                                                                                                                                                    | 16-bit tir                                                   | ner/counte             | er                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                    |                       |         |  |

| TNOD 5       |         | 1                                                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                    | 8-bit tim                                                    | er/counter             | with 8-bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | auto reloa         | ding.                 |         |  |

| TMOD.5       | M1      | 1                                                                                                                                                                                                                                                                                                     | 1                                                                                                                                                                                                                                                                                    | Timer/co                                                     | unter 1 or             | eration sto                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | pped.              |                       |         |  |

| TMOD.6       | с/ī     | XTAL1•2<br>C/T = "0".<br>The exter                                                                                                                                                                                                                                                                    | 1   Timer/counter 1 operation stopped.  Timer/counter 1 count clock designation control bit.  XTAL1*2 divided by 12 clocks is the input applied to timer/counter 1 when C/T = "0".  The external clock applied to the T1 pin is the input applied to timer/counter 1 when C/T = "1". |                                                              |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |                       |         |  |

| TMOD.7       | GATE    | when C/T = "1".  When this bit is "0", the TR1 bit of TCON is used to control the start and stop of timer/counter 1 counting.  If this bit is "1", timer/counter 1 starts counting when both the TR1 bit of TCON and INT1 pin input signal are "1", and stops counting when either is changed to "0". |                                                                                                                                                                                                                                                                                      |                                                              |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |                       |         |  |

### MSM80C154S/83C154S

# Power control register (PCON)

| NAME         | ADDRESS | MSB                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                    |                                          |                                                                       |                                                       |                                                          |                            | LSB                 |  |  |  |

|--------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------------|----------------------------|---------------------|--|--|--|

|              |         | 7                                                                                                                                                                                                                                                                                                                         | 6                                                                                                                                                                                                                                                                                  | 5                                        | 4                                                                     | 3                                                     | 2                                                        | 1                          | 0                   |  |  |  |

| PCON         | 87H     | SMOD                                                                                                                                                                                                                                                                                                                      | HPD                                                                                                                                                                                                                                                                                | RPD                                      | _                                                                     | GF1                                                   | GF0                                                      | PD                         | IDL                 |  |  |  |

| BIT LOCATION | FLAG    |                                                                                                                                                                                                                                                                                                                           | FUNCTION                                                                                                                                                                                                                                                                           |                                          |                                                                       |                                                       |                                                          |                            |                     |  |  |  |

| PCON.0       | IDL     | IDLE mod<br>and the s                                                                                                                                                                                                                                                                                                     | IDLE mode is set when this bit is set to '1". CPU operations are stopped when IDLE mode is set, but XTAL1•2, timer/counters 0, 1 and 2, the interrupt circuits, and the serial port remain active. IDLE mode is cancelled when the CPU is reset or when an interrupt is generated. |                                          |                                                                       |                                                       |                                                          |                            |                     |  |  |  |

| PCON.1       | PĐ      | stopped v                                                                                                                                                                                                                                                                                                                 | when PD n                                                                                                                                                                                                                                                                          |                                          | . PD mod                                                              |                                                       | erations an<br>led when ti                               |                            |                     |  |  |  |

| PCON.2       | GF0     | General p                                                                                                                                                                                                                                                                                                                 | urpose bit                                                                                                                                                                                                                                                                         | l.                                       |                                                                       |                                                       |                                                          |                            |                     |  |  |  |

| PCON.3       | GF1     | General p                                                                                                                                                                                                                                                                                                                 | urpose bit                                                                                                                                                                                                                                                                         | l.                                       |                                                                       |                                                       | · · · · · · · · · · · · · · · · · · ·                    |                            |                     |  |  |  |

| PCON.4       |         | Reserved                                                                                                                                                                                                                                                                                                                  | bit. The o                                                                                                                                                                                                                                                                         | output data                              | is "1", if t                                                          | ne bit is re                                          | ad.                                                      |                            |                     |  |  |  |

| PCON.5       | RPD     | interrupt Power-do enabled t If the inte "1" (even of the po                                                                                                                                                                                                                                                              | signal.<br>own mode<br>by IE (inter<br>errupt flag<br>if interrup<br>wer-down                                                                                                                                                                                                      | cannot be<br>rupt enabli<br>is set to "1 | cancelled<br>e register)<br>* by an int<br>d), the pro<br>ing instruc | by an inte<br>when this<br>errupt requ<br>ogram is ex | rrupt signa                                              | I if the inte              |                     |  |  |  |

| PCON.6       | НРО     | If the level<br>is change                                                                                                                                                                                                                                                                                                 | el of the po<br>ed from "1"<br>m is put ir                                                                                                                                                                                                                                         | ower failure<br>" to "0" whe             | e detect si<br>en this bit i                                          | gnal applie<br>is "1", XTAI                           | en this bit<br>d to the HF<br>_1•2 oscilla<br>PD mode is | Dt pin (pi<br>ition is sto | n 3.5)<br>opped and |  |  |  |

| PCON.7       | SMOD    | When the timer/counter 1 carry signal is used as a clock in mode 1, 2 or 3 of the serial port, this bit has the following functions.  The serial port operation clock is reduced by 1/2 when the bit is "0" for delayed processing. When the bit is "1", the serial port operation clock is normal for faster processing. |                                                                                                                                                                                                                                                                                    |                                          |                                                                       |                                                       |                                                          |                            | delayed             |  |  |  |

# Timer control register (TCON)

| NAME         | ADDRESS | MSB                                                                                                                                                                                 |            |                        |                                           |              |          |             | LSB                        |  |  |  |

|--------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------------------|-------------------------------------------|--------------|----------|-------------|----------------------------|--|--|--|

|              |         | 7                                                                                                                                                                                   | 6          | 5                      | 4                                         | 3            | 2        | 1           | 0                          |  |  |  |

| TCON         | 88H     | TF1                                                                                                                                                                                 | TR1        | TFO                    | TR0                                       | IE1          | IT1      | 1EO         | ITO                        |  |  |  |

| BIT LOCATION | FLAG    |                                                                                                                                                                                     | FUNCTION   |                        |                                           |              |          |             |                            |  |  |  |

| TCON.0       | IT0     | External interrupt 0 signal is used in level-detect mode when this bit is "0" and in trigger detect mode when "1".                                                                  |            |                        |                                           |              |          |             |                            |  |  |  |

| TCON.1       | IE0     | The bit is                                                                                                                                                                          | reset auto | matically              | rnal interru<br>when an in<br>y software  | terrupt is   |          |             | a cilia kaomini a mata dan |  |  |  |