# **OKI** semiconductor

# MSM6351

# CMOS 4BIT HIGH PERFORMANCE AND VERY LOW POWER SINGLE CHIP MICROCONTROLLER WITH LCD DRIVER

# **GENERAL DESCRIPTION**

OKI's MSM6351 is a low-power, high-performance single-chip microcontroller employing silicon gate CMOS technology. Integrated onto a single chip are 4-bit ALU, 61K bits of mask programmable ROM, 4096 bits of RAM, 20 bits of I/O port, serial I/O port, time-base counter, LCD driver, 3 interrupts, crystal oscillator and voltage tripler.

The MSM6351 is widely used in electronic products requiring low power consumption, a large number of LCD drivers and a large size of memory.

# **FEATURES**

- Low Power Consumption 3 μA Typical

- 4096 × 15 Internal ROM

- 1024 × 4 Internal RAM

- 20 Input/Output Ports

- 62 LCD Drivers

1/3 Duty, 1/3 Bias or 1/4 Duty 1/3 Bias

(Selectable by software)

- Serial I/O Port

8 bits or 5 bits data frame mode

Asynchronous

receiver/transmitter mode

Internal or external clock mode

- 15 stages Time Base Counter

- Watch Dog Timer

- Capture function by external trigger signal

- 3 Interrupt Sources

Real time interrupt

External interrupt

Serial I/O port interrupt

- Melody Circuit

- 65 Instructions

- Sub-routine Nesting: 7 levels

- 32.768 kHz Crystal Oscilator

- Machine Cycle: 61.0 μsec.

- Power Supply: 1.5V or 3.0V (selectable by mask option)

- 100 pad die or 100 Pin Flat Package

- Silicon gate CMOS Process

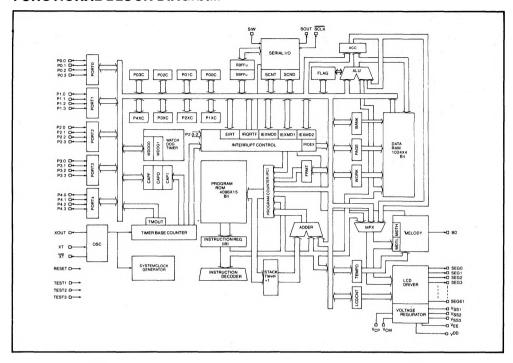

# **FUNCTIONAL BLOCK DIAGRAM**

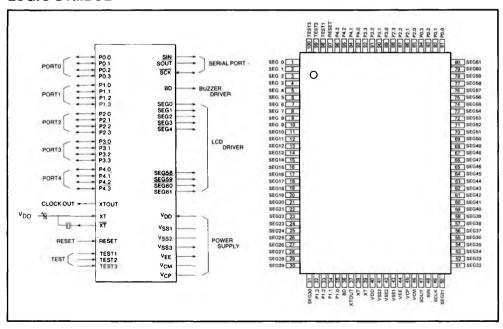

# **LOGIC SYMBOL**

# **PIN DESCRIPTION**

| Designation     |                      |                                                                           | Function                                                                                                      |                    |

|-----------------|----------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--------------------|

| P0.0            |                      | 0 4 his 1/0 nom 0                                                         |                                                                                                               | Capture            |

| P0.1            | PORTO                |                                                                           | put, the existence (*)/                                                                                       | trigger signal     |

| P0.2            | PORTU                | HALT function re                                                          | own resistance, and the elease enable/disable                                                                 |                    |

| P0.3            |                      | condition can be                                                          | selected for each bit.                                                                                        |                    |

| P1.0 ~ P1.3     | PORT 1               | • 4-bit I/O port 1                                                        |                                                                                                               |                    |

| P2.0            |                      |                                                                           | The input (*)/output, the                                                                                     |                    |

| P2.1            | PORT 2               | • 4-bit I/O port 2                                                        | existence (*)/absence of                                                                                      | External           |

| P2.2            | FUNTZ                | 4-bit 1/0 port 2                                                          | pull-down resistance, and the HALT function                                                                   | interrupt signal   |

| P2.3            |                      |                                                                           | release enable/disable condition can be selected                                                              |                    |

| P3.0 ~ P3.3     | PORT 3               | • 4-bit I/O port 3                                                        | for each bit.                                                                                                 |                    |

| P4.0 ~ P4.3     | PORT 4               | • 4-bit I/O port 4                                                        |                                                                                                               |                    |

| хтоит           |                      | or clock output<br>illator clock is output w                              | hen XTF (forth bit of port PC                                                                                 | OC) is set to "1". |

| XT              | • 0:                 |                                                                           |                                                                                                               |                    |

| XT              | Oscillato            | or connection terminal                                                    |                                                                                                               |                    |

| RESET           | Reset in Input w     |                                                                           | ce, the system is reset when "                                                                                | 1" is input.       |

| TEST 1          |                      |                                                                           |                                                                                                               |                    |

| TEST 2          | Test inp     Input w |                                                                           | ce. Generally used when the re                                                                                | esistance is open. |

| TEST 3          |                      |                                                                           |                                                                                                               |                    |

| SIN             | Circuit c            | configuration                                                             |                                                                                                               |                    |

| SOUT            | the circu            | ort data input<br>uit is set at high impeda<br>ort P4XC) or when no c     | nce level when "1" is set to Hillata is transmitted.                                                          | ZOUT (the forth    |

| SCK             | the inpu<br>register | SCNT. In the output me demultiplied signal (1,                            | out<br>hitched from each other the sel<br>ode, the serial clock frequency<br>/1, 1/2 or 1/4 of the original b | can be selected    |

| BD              | Melody               | output (buzzer drive ou                                                   | utput) (not available in the MS                                                                               | M6353.)            |

| SEG0 ~<br>SEG61 | The dut              | ve output with the 1/3<br>y can be switched by L<br>num of 177 segments c | bias, or the 1/3 or 1/4 dusty s<br>CD control register LCDCNT.<br>an be displayed with the 1/3 d              | •                  |

# • MSM6351 •-

| Designation      | Function                                                  |  |

|------------------|-----------------------------------------------------------|--|

| V <sub>DD</sub>  | OV power supply terminal                                  |  |

| V <sub>SS1</sub> | -1.5V power terminal (for the 1.5V specification)         |  |

| V <sub>SS2</sub> | • -3.0V power terminal (for the 3.0V specification)       |  |

| V <sub>SS3</sub> | -4.5V power terminal (not available in the MSM6353)       |  |

| VEE              | Internal logic power terminal                             |  |

| VCM              | • Internal pours governor conscitor connection to mission |  |

| VCP              | Internal power generator capacitor connecting terminal    |  |

Note 1: The base clock refers to an oscillator output signal demultiplied into 1/1, 1/2, 1/4, or 1/8 of the output frequency (with the masking option).

# **FUNCTIONAL DESCRIPTION**

A block diagram of MSM6351 is given on page 128. Each block of logic will be briefly discussed. For further information, please refer to MSM6351/53 user's manual.

Programmable ROM

The programmable ROM has a capacity of 4096 words, each of which is 15 bits long. It is provided with the address space of 000 to FFFH.

In the MSM6351, the programmable ROM is not only used for programming but also used to save the following items:

- 1) LCD indicator segment conversion table

- 2) Melody tone data

The program instructions are all mde up of one word, thus the ROM can save up to 4096 instructions in it.

### Data RAM

The data RAM has a capacity of 1024 words, each consisting of four bits. It is provided with the space for address between 000H and 3FFH. Data is organized in 4 bit nibble.

# Page Register (PAGE)

The page register specifies one of 16 pages in each bank of the data RAM. It is used in the addressing bank mode or in the paging mode.

### Bank Register (BANK)

The bank register specifies one of four banks in the data RAM. It is used together with the page register in the bank paging mode.

### Working Specification Register

The working specification register specifies one of 16 pages in bank 0 of the data RAM. It is used in the addressed working specification mode.

# Operational Section

The operational section consists of the ALU, accumulator (ACC), and conditional flags C, Z and G.

This operational section performs four-bit computation of the contents of the data RAM with the contents of ACC or the immediate data fetched into the instruction words.

This computation is mainly performed with the data RAM which functions as a register. The resultant data of the computation are input to the data RAM or to ACC (for operation other than comparison).

# Program Counter (PC)

The program counter (PC) generates addresses for the programmable ROM.

The addresses for programming are changed according to the instructions executed. These addresses are incremented by one each time the instruction is executed.

When an interrupt is generated, the current address is stored in the STACK. The address is set to 400H, 401H or 402H depending on the type of the interrupt (see Fig. 3.5.1).

These addresses are set to the start addresses of each interrupt routine.

In the MSM6351, the PC also gives LCD indicator "segment conversion table" or melody "tone data" addresses to the programmable ROM.

The output data of the programmable ROM whose address is specified by the PC is fetched into the instruction register (IR). If the output data is an instruction, it is decoded by the instruction decoder. Then, control signals to each section are generated.

### **Ports**

The MSM6351/6353 handle the I/O ports, flags and registers collectively as ports. Therefore, each of the I/O ports, flags and registers are selected by specifying their own addresses.

All of these ports are accessed by the INP and OUT instructions.

# PORT NAMES, ADDRESSES AND THEIR CONTENTS

| Port name | Address | Bit 3              | Bit 2           | Bit 1           | Bit 0           | Access mode (*)                    |

|-----------|---------|--------------------|-----------------|-----------------|-----------------|------------------------------------|

| PORT0     | 00      | P0.3               | P0.2            | P0.1            | P0.0            | R/W                                |

| PORT1     | 01      | P1.3               | P1.2            | P1.1            | P1.0            | R/W                                |

| PORT2     | 02      | P2.3               | P2.2            | P2.1            | P2.0            | R/W                                |

| PORT3     | 03      | P3.3               | P3.2            | P3.1            | P3.0            | R/W                                |

| PORT4     | 04      | P4.3               | P4.2            | P4.1            | P4.0            | R/W                                |

| P00C      | 05      | XTF                | HRE00           | HZ00            | DIR00           | R/W                                |

| P01C      | 06      | BUF                | HRE01           | HZ01            | DIR01           | R/W                                |

| P02C      | 07      | _                  | HRE02           | HZ02            | DIR02           | R/W                                |

| P03C      | 08      | _                  | HRE03           | HZ03            | DIR03           | R/W                                |

| P1XC      | 09      | _                  | HRE1X           | HZ1X            | DIR1X           | R/W                                |

| P2XC      | 0A      | HZSOUT             | HRE2X           | HZ2X            | DIR2X           | R/W                                |

| P3XC      | ОВ      | EISIO              | HRE3X           | HZ3X            | DIR3X           | R/W                                |

| P4XC      | ос      | 5/8                | HRE4X           | HZ4X            | DIR4X           | R/W                                |

|           | 0.0     | (L) d <sub>3</sub> | d <sub>2</sub>  | d,              | d <sub>o</sub>  | D.//4/                             |

| SBF       | OD.     | (u) d <sub>7</sub> | d <sub>6</sub>  | d <sub>s</sub>  | d <sub>4</sub>  | R/W                                |

| SCNT      | 0E      | CLKSL1             | CLKSL0          | MODE            | LSB/MSB         | R/W                                |

| SCND      | OF      | SIOEND             | STPErr          | ENRC            | ENTR            | BIT:<br>3 and 2; R<br>1 and 0; R/W |

| IRQEX     | 10      | -                  | IRQP22          | IRQP21          | IRQP20          | R                                  |

| EIRT      | 11      | EI256Hz            | EI32Hz          | E116Hz          | EI1Hz           | R/W                                |

| IRQRT     | 12      | IRQ256Hz           | IRQ32Hz         | IRQ16Hz         | IRQ1Hz          | R                                  |

| IEXM0     | 13      | _                  | EIP20           | L/E0            | P/N0            | R/W                                |

| IEXM1     | 14      | 17                 | EIP21           | L/E1            | P/N1            | R/W                                |

| IEXM2     | 15      | _                  | EIP22           | L/E2            | P/N2            | R/W                                |

| TMOUT     | 16      | 15th               | 14th            | 13th            | 12th            | R                                  |

|           |         | 128Hz<br>32Hz      | 256Hz<br>64Hz   | 512Hz<br>128Hz  | 1KHz<br>256Hz   | R                                  |

| CAPRT     | 17      | _                  | CAPMD           | CAP1F           | CAPOF           | Bity 2: R/W<br>Other bits: R       |

| FLAG      | 18      | MSTART             | G               | Z               | С               | Bity 3: R<br>Other bits: R/W       |

| WDGG      | 10      | W <sub>03</sub>    | W <sub>02</sub> | W <sub>o1</sub> | W <sub>oo</sub> | R/W                                |

| WDOG      | 19      | W <sub>13</sub>    | W <sub>12</sub> | W <sub>11</sub> | W <sub>10</sub> | ] 17/44                            |

| FRAMT     | 1A      | F <sub>3</sub>     | F,              | F,              | F <sub>o</sub>  | R/W                                |

| LCDCT     | 1B      | AIION              | Drty 3/4        | FLM1            | FLM0            | R/W                                |

# PORT NAMES, ADDRESSES AND THEIR CONTENTS (Continued)

| Port name | Address | Bit 3          | Bit 2          | Bit 1          | Bit 0          | Access mode (*) |

|-----------|---------|----------------|----------------|----------------|----------------|-----------------|

| ТЕМРО     | 1C      | P <sub>3</sub> | P <sub>2</sub> | P,             | Po             | R/W             |

| BANK      | 1D      | b <sub>3</sub> | b <sub>2</sub> | b,             | b <sub>o</sub> | R/W             |

| PAGE      | 1E      | Ρ <sub>3</sub> | P <sub>2</sub> | P <sub>1</sub> | Po             | R/W             |

| WORK      | 1F      | W <sub>2</sub> | W <sub>2</sub> | w <sub>1</sub> | w <sub>o</sub> | R/W             |

Note:

- In access mode (\*), R denotes "readable" bits and W "writable" bits.

- Bits marked with denote bits which are not present.

### I/O Ports

The MSM6351/6353 are provided with five ports; PORT0 to PORT4. Each port consists of four bits.

Ports are controlled by the I/O port control register. The register controls PORT1 to PORT4 port by port and controls PORT0 in bit units.

Each port is accessed by the OUT and INP instruction.

## **Time Base Counter**

The MSM6351/6353 have their built-in time base counters consisting of a 15-stage binary counter. System base clock  $\phi$ 0 is input to the time base counter clock.

# **Capture Circuit**

The MSM6351/6353 are provided with a capture function that fetches the 1KHz to 128Hz outputs at stages 5 to 8 of the time base counter or the 256 Hz to 32Hz outputs at stages 7 to 10 when P0.0 or P0.1 of I/O port 0 is set at the "H" level.

# Watchdog Timer

The MSM6351/6353 have their built-in watchdog timer to prevent any program runway occurrence. The time may be set with two types of setting time: 250ms and 2s.

# Serial Port (SERIAL I/O)

The MSM6351/6353 have their built-in serial port. It is used for asynchronous data communications. A data length of five or eight bits can be selected. Either internal or external clock can be selected as the driving clock. At the end of data transfer, a serial port inerrupt can be generated.

The serial port registers and their functions are described in the following sections.

# Melody Output Circuit (built in the MSM6351) (MEMODY)

The melody output circuit automatically outputs melody or buzzer sound. It is built in the MSM6351.

The melody circuit initiates its operation by the MSA instruction. Automatically fetching the musical note data defined in the program ROM, the MSA instruction outputs the melody from buzzer driving output terminal BD.

# Liquid Crystal Display Circuit (LCD DRIVER)

The MSM6351 has its built-in liquid crystal display circuit that can drive the liquid crystal (LCD).

The liquid crystal display consists of the display data register for writing the data to indicate and the display driver. After data is written in the display data register with an display instruction, the display driver automatically fetches data from the display data register to output the driving waveform.

# Interruption Controller (INTERRUPT CONTROL)

There are four types of interruptions as follows:

- Real-time interruption Interruption with the time base counter output

- 2) External interruption Interruption from PORT2

- Serial port interruption Interruption by terminating serial port data transfer

- Melody interruption Interruption by requesting melody data (not available in the MSM6353)

# **ABSOLUTE MAXIMUM RATING (Target Specification)**

$V_{DD} = 0V (V_{SS2} = Battery Voltage)$

| Parameter           | Symbol           | Conditions | Limits                       | Unit     |

|---------------------|------------------|------------|------------------------------|----------|

| Supply Voltage      | V <sub>DD</sub>  |            | <b>−6.0</b> ~ <b>+0.3</b>    | <b>v</b> |

| Input Voltage       | V <sub>IN</sub>  | T- 0500    | V <sub>SS2</sub> 0.3 ~ +0.3  | V        |

| Output Voltage*1    | V <sub>01</sub>  | Ta = 25°C  | V <sub>SS2</sub> -0.3 ~ +0.3 | V        |

| Output Voltage*2    | V <sub>02</sub>  |            | <b>−6.0</b> ~ <b>+0.3</b>    | V        |

| Storage Temperature | T <sub>STG</sub> |            | −55 ~ +125                   | °C       |

<sup>\*1</sup> Normal Output

# **OPERATING CONDITION (Target Specification)**

| Parameter             | Symbol            | Limits    | Units |

|-----------------------|-------------------|-----------|-------|

| Operating Voltage     | -V <sub>SS2</sub> | 2.6 ~ 3.3 | ٧     |

| Operating Temperature | Topr              | -20 to 60 | °C    |

<sup>\*2</sup> When LCD Driver in use

# DC CHARACTERISTICS 3V Li Battery (Target Specification)

$V_{DD}$  = 0V,  $V_{SS1}$  = -1.5V,  $V_{SS2}$  = -3.0V,  $V_{SS3}$  = -4.5V, f = 32,768Hz, Ta = 25° C\*1

| Parameter                          | Symbol            | Donditions                                                    |      | Rating | ı    | Unit       | Terminal                 |

|------------------------------------|-------------------|---------------------------------------------------------------|------|--------|------|------------|--------------------------|

| raiametei                          | Symbol            | Donations                                                     | Min. | Тур.   | Max. |            | Applied                  |

| Current Consumption                | IDD               | *3                                                            | _    | 3.0    | _    | μΑ         |                          |

| Voltage for Oscilla-<br>tion Start | -Vosc             | Within 2 sec.                                                 | _    | _      | 2.4  | ٧          |                          |

|                                    | -10H1             | V <sub>OH1</sub> = -0.2V                                      | 4    |        | _    |            |                          |

| Output Current 1                   | IIOMH1I           | V <sub>OMH1</sub> = V <sub>SS1</sub> ±0.2V                    | 4    | _      | _    | μА         | SEG0 ~ SEG61             |

| (Common Segment)                   | HOML1             | V <sub>OML1</sub> = V <sub>SS2</sub> ±0.2V                    | 4    | _      | _    | <b>"</b> " | 3200 32001               |

|                                    | IOL1              | V <sub>OL1</sub> = -4.3V                                      | 4    | _      | _    |            |                          |

| Output Current 2                   | -IOH2             | V <sub>OH2</sub> = -0.5V                                      | 500  | _      | _    | μА         | PORTO~PORT4 SOUT, SCLK   |

|                                    | IOL2              | $V_{OL2} = -2.5V$                                             | 500  | _      | _    | <i>_</i>   | XTOUT                    |

| Output Current 3                   | ~1 <sub>ON3</sub> | $V_{ON4} = -0.5V$<br>$V_{SS2} = 3.0V$                         | 7    | -      | _    | μA         | BD                       |

| output durient s                   | IOL3              | V <sub>ON4</sub> = -2.5V<br>V <sub>SS2</sub> = 3.0V           | 20   | -      | _    | <b>#</b> A | 50                       |

| Input Current 1                    | -I <sub>1N1</sub> | V <sub>IN1</sub> = 0V<br>I/O input,<br>with pull down         | 150  | 300    | 600  | μΑ         | PORT0~PORT4              |

| Input Current 2                    | 11121             | V <sub>IN2</sub> = 0V, -3V<br>I/O input,<br>without pull down | _    | _      | 1    | μΑ         | PORT0~PORT4<br>SIN, SCLK |

| Input Current 3                    | -11H3             | V <sub>IH3</sub> = 0V<br>with pull down                       | _    | 25     | _    | μΑ         | RESET                    |

| Input Voltage                      | ~VIH              |                                                               |      | _      | 0.5  | <b>V</b>   | All input                |

|                                    | ~VIH              |                                                               | 2.5  | _      | _    | <b>V</b>   | terminals                |

<sup>\*1.</sup> When 3V battery with halver is used.

<sup>\*2.</sup> PORT0 = P0.0  $\sim$  P0.3, PORT1 = P1.0  $\sim$  P1.3, PORT2 = P2.0  $\sim$  P2.3, PORT 3 = P3.0  $\sim$  P3.3, PORT4 = P4.0  $\sim$  P4.3

<sup>\*3.</sup> This value changes depending on the soft duty (HALT to HALT)

| <u>-</u> | 2 |

|----------|---|

| <b>=</b> | , |

| c        | 5 |

| F        | _ |

| C        | כ |

| Ξ        | 5 |

| ۵        | _ |

| F        | _ |

| ٧        | 3 |

| (rP), (ACC), (Z), (C) ← (rP) + (ACC)                                                                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (rP), (ACC), (Z), (C) $\leftarrow$ (rP) + i                                                                                                                             |

| (rP), (ACC), (Z), (C) $\leftarrow$ decimal adj [(rP) + (ACC) + (C)]                                                                                                     |

| (rP), (ACC), (Z), (C) $\leftarrow$ N adjust [(rP) + (C)]                                                                                                                |

| (rP), (ACC), (Z), (C) ← (rP) - (ACC)                                                                                                                                    |

| (rP), (ACC), (Z), (C) ← (rP) - i                                                                                                                                        |

| (rP), (ACC), (Z), (C) $\leftarrow$ decimal adj [(rP) $-$ (ACC) $-$ (C)]                                                                                                 |

| (rP), (ACC), (Z), (C) ← N adjust [(rP) — (C)]                                                                                                                           |

| (Z), (G) ← (rP) - (ACC)                                                                                                                                                 |

| (Z), (G) ← (rP) – i                                                                                                                                                     |

| (rP), (ACC), (Z), (C) ← (rP) + 1                                                                                                                                        |

| (rPb), (ACC), (Z), (C) ← (rPb) +                                                                                                                                        |

| (rP), (ACC), (Z), (C) $\leftarrow$ (rP) $-1$                                                                                                                            |

| (rPb), (ACC), (Z), (C) ← (rPb) - 1                                                                                                                                      |

| $(\mathbf{Z}) \leftarrow (\mathbf{rP_3}) \wedge (ACC_3) \vee (\mathbf{rP_2}) \wedge (ACC_2) \vee (\mathbf{rP_1}) \wedge (ACC_1) \\ \vee (\mathbf{rP_0}) \wedge (ACC_0)$ |

| $(2) \leftarrow (\overline{rP_3}) \wedge i_3 \vee (\overline{rP_2}) \wedge i_2 \vee (\overline{rP_1}) \wedge i_1 \vee (\overline{rP_0}) \wedge i_0$                     |

| (rP), (ACC), (Z) ← (rP) V (ACC)                                                                                                                                         |

| (rP), (ACC), (Z) ← (rP) V i                                                                                                                                             |

| (rP), (ACC), (Z) $\leftarrow$ (rP) $\land$ (ACC)                                                                                                                        |

| (rP), (ACC), (Z) ← (rP) ∧ i                                                                                                                                             |

| (rP), (ACC), (Z) ← (rP) ∨ (ACC)                                                                                                                                         |

| (rP), (ACC), (Z) ← (rP) ♥ i                                                                                                                                             |

|                |   |    |    |     |     | 드              | struc | Instruction code | ode                           |                |                |     |     |      |                                                                             |       |       |

|----------------|---|----|----|-----|-----|----------------|-------|------------------|-------------------------------|----------------|----------------|-----|-----|------|-----------------------------------------------------------------------------|-------|-------|

| Minemonic      | 4 | 13 | 12 | =   | 9   | 6              | 00    | 1                | 9 2                           | 4              | 2              | - 2 | -   | 0    | Description                                                                 | cycle | r age |

| ROR REGI       | 0 | 0  | 0  | 0   | 0   | 0              | ۵     | 0                | 0 1                           | 0              | 13             | -   |     | 20   | (Z), (ACC) $\leftarrow [ \hookrightarrow (C) \rightarrow (P) \rightarrow ]$ | -     |       |

| ROL REG1       | 0 | 0  | 0  | 0   | 0   | 1              | Ь     | 0                | 0 110                         | 0 73           | 12             | -   | 10  | -    | (Z), (ACC) $\leftarrow [ \leftarrow (C) \leftarrow (rP) \rightarrow ]$      | 1     |       |

| ASR REG1       | 0 | 0  | 0  | 0   | 0   | 0              | Ь     | 0                | 1 0                           | 1              | r3             | 7.  | 7.  | . r. | (Z), (ACC) $\leftarrow$ [ O $\rightarrow$ (rP) $\rightarrow$ (C) ]          | -     |       |

| ASL REG1       | 0 | 0  | 0  | 0   | 0   | -              | а     | 0                | 0 1                           | -              | r 3            |     | r,  | ٢.   | (2), $(ACC) \leftarrow [(C) \leftarrow (rP) \leftarrow 0]$                  | -     |       |

| CLG            | 0 | 0  | 0  | 0   | 0   | 0              | 0     | -                | 0 0                           | 0              | 0              | 0   | 0   | 0    | 0 + (9)                                                                     | -     |       |

| CLC            | 0 | 0  | 0  | 0   | 0   | 0              | 0     | -                | 0 0                           | -              | 0              | 0   | 0   | 0    | (C) ← O                                                                     | -     |       |

| CLZ            | 0 | 0  | 0  | 0   | 0   | 0              | 0     | -                | 0 1                           | 0              | 0              | 0   | 0   | 0    | O → (Z)                                                                     | -     |       |

| CLA            | 0 | 0  | 0  | 0   | 0   | 0              | 0     | -                | 0                             | -              | 0              | 0   | 0   | 0    | (Z), (C), (G) ~ O                                                           | -     |       |

| SEG            | 0 | 0  | 0  | 0   | 0   | -              | 0     | -                | 0 0                           | 0              | 0              | 0   | 0   | 0    | (G) ←1                                                                      | -     |       |

| SEC            | 0 | 0  | 0  | 0   | 0   | -              | 0     | -                | 0 0                           | -              | 0              | 0   | 0   | 0    | (C) ←1                                                                      | -     |       |

| SEZ            | 0 | 0  | 0  | 0   | 0   | -              | 0     | -                | 0                             | 0              | 0              | 0   | 0   | 0    | (Z) ←1                                                                      | -     |       |

| SEA            | 0 | 0  | 0  | 0   | 0   | -              | 0     | -                | 1 0                           | -              | 0              | 0   | 0   | 0    | (Z), (C), (G) ←1                                                            | -     |       |

| MOV ACC, REG1  | 0 | 0  | 0  | 0   | 0   | 0              | 4     | -                | 1 1                           | -              | 7.3            | F.2 | -   | ro   | (rP) + (ACC)                                                                | 1     |       |

| MOVD ACC, REG2 | - | 0  | -  | 0   | b,  | p°             | 0     | P <sub>3</sub>   | P <sub>2</sub> P <sub>1</sub> | ď              | F.             | 12  | -   | 10   | (rPb) + (ACC)                                                               | -     |       |

| MOV #i, REG1   | 0 | 0  | -  | -   | -   | 0              | ۵     |                  | i <sub>2</sub> i <sub>1</sub> | j,             | 7.             | 7.  | 1   | r.   | (rP), (ACC), (Z) ← i                                                        | -     |       |

| MOV REG1, ACC  | 0 | 0  | 0  | 0   | 0   | -              | 4     | -                | -                             | -              | r.             | 7.  | 5   | ro   | (ACC), (Z) ← (rP)                                                           | ÷     |       |

| MOVD REG2, ACC | - | 0  | -  | -   | p,  | p <sub>0</sub> | 0     | Р, Р             | P <sub>2</sub> P <sub>1</sub> | P <sub>o</sub> | r3             | 12  | 7   | ro   | (ACC), (Z) ← (rPb)                                                          | 1     |       |

| EXG REG1       | 0 | 0  | 0  | 0   | 0   | 1              | Ь     | 0                | 0 0                           | 0              | r3             | r2  | r   | ro   | (rP) ↔ (ACC)                                                                | 1     |       |

| EXGD REG2      | 0 | -  | -  | -   | o,  | p°             | 0     | Р, Р             | P, P                          | ۵°             | 7.             | 7   | £   | 70   | (rPb) + (ACC)                                                               | -     |       |

| CALL adrs      | - | -  | -  | 116 | 910 | 60             | 88    | a, a             | a <sub>s</sub> a <sub>s</sub> | 60             | a              | 9   | ø   | e e  | (STACK) o (PC), (PC) ← a <sub>11</sub> ~ a <sub>0</sub> (SP) ← (SP) + 1     | ÷     |       |

| RET            | 0 | 0  | 0  | 0   | 0   | 0              | 0     | 1                | 0                             | 0              | 0              | 0   | 0   | 0    | $(PC) \leftarrow (STACK) + 1$ $(SP) \leftarrow (SP) - 1$                    | ÷     |       |

| RT1            | 0 | 0  | 0  | 0   | 0   | 1              | 0     | 1 1              | 0 1                           | 0              | 0              | 0   | 0   | 0    | $(PC) \leftarrow (STACK) + 1$ $(SP) \leftarrow (SP) - 1$ (at INT routine)   | 1 (91 |       |

| JMP adrs       | - | -  | 0  | 911 | 910 | a <sub>9</sub> | ae    | a, a             | a <sub>6</sub> a <sub>s</sub> | 94             | a <sub>3</sub> | a   | 9,1 | a    | (PC) ← a <sub>11</sub> ~ a <sub>0</sub>                                     | •     |       |

| JMP a REG1     | 0 | 0  | 0  | 0   | 0   | 0              | ۵     | -                | 0                             | -              | 7.3            | 2   | -   | ro   | $(PC) \leftarrow (PC) + (rP) + 1$                                           | +     |       |

| JMPIO a REG1   | 0 | 0  | 0  | 0   | 0   | _              | 4     | -                | 0                             | -              | -              |     |     |      | 1 + (a-1 × C + (2a) - (2a)                                                  | ,     |       |

# INSTRUCTION LIST (Continued)

INSTRUCTION LIST (Continued)

| When P = 0 in bit 8,                                         |

|--------------------------------------------------------------|

| N = n + 1;<br>when P = 1,<br>N = _n                          |

|                                                              |

|                                                              |

|                                                              |

| Specifies the first address of note data. (E00H $\sim$ FFFH) |

|                                                              |

|                                                              |

|                                                              |

|                                                              |

|                                                              |

|                                                              |

|                                                              |

|                                                              |

|                                                              |

| •                                                            |

Note: Instructions marked with an asterisk (\*) are available for MSM6351 only.