# **OKI** semiconductor

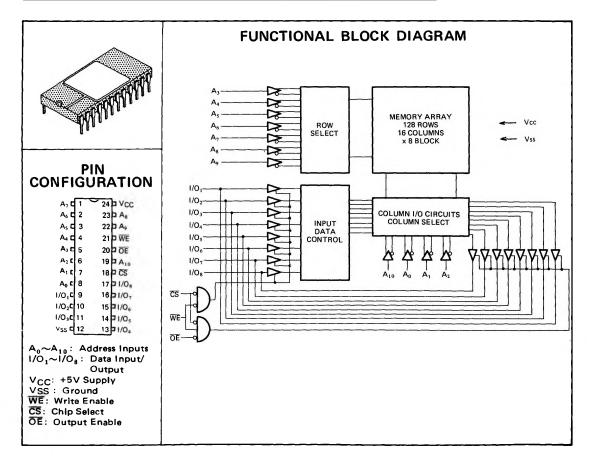

## MSM2128-1AS

16,384-BIT (2048 x 8) STATIC RAM

#### **GENERAL DESCRIPTION**

The Oki MSM2128-1 is a 16384-bit static Random Access Memory organized as 2048 words by 8 bits using Oki's Advanced N-channel Silicon Gate MOS technology. It uses fully static circuitry and therefore requires no clocks or refreshing to operate. Directly TTL compatible inputs, outputs and operation from a single +5V supply simplify system designs. Common data input/output pins using three-state outputs are provided.

The MSM2128-1 series is offered in an 24-pin dual-in-line ceramic (AS suffix) package. Operation is guaranteed from 0°C to 70°C.

#### **FEATURES**

- Low Power Dissipation

- Single +5V Supply (±10% Tolerance)

- 2048-word x 8-bit Organization

- Fully Static Operation

- Common I/O Capability using Three-State Outputs

- Directly TTL Compatible

- Advanced N-channel Silicon Gate

MOS Technology

Pin compatible with MSM2716,

16,384 Bit UV Erasable PROM

|                             | 2128-1 | 2128-13 |

|-----------------------------|--------|---------|

| Max. Access Time (NS)       | 200    | 300     |

| Max. Power Dissipation (MW) | 800    | 800     |

### **ABSOLUTE MAXIMUM RATINGS**

| Rating                 | Symbol                     | Value        | Unit | Conditions     |  |

|------------------------|----------------------------|--------------|------|----------------|--|

| Temperature Under Bias | Top                        | 0 to + 70    | °C   |                |  |

| Storage Temperature    | T <sub>stg</sub>           | -55 to + 150 | °C   |                |  |

| Supply Voltage         | ly Voltage V <sub>CC</sub> |              | V    |                |  |

| Input Voltage          | VIN                        | -0.5 to + 7  | V    | Respect to VSS |  |

| Output Voltage         | Output Voltage VOUT        |              | V    |                |  |

| Power Dissipation      | PD                         | 1.0          | w    |                |  |

Note: Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or at any other condition above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **OPERATING CONDITIONS**

| Parameter             | Symbol | Min. | Тур. | Max. | Unit        | Conditions                 |

|-----------------------|--------|------|------|------|-------------|----------------------------|

| Supply Voltage        | Vcc    | 4.5  | 5    | 5.5  | V           | 5∨ ± 10%                   |

| Input Signal Level    | VIH    | 2.0  | 5    | 6.0  | ٧           | B                          |

|                       | VIL    | -0.5 | 5    | 0.8  | <b>&gt;</b> | Respect to V <sub>SS</sub> |

| Operating Temperature | Topr   | 0    |      | +70  | °C          |                            |

#### DC CHARACTERISTICS

$(V_{CC} = 5V \pm 10\%; Ta = 0^{\circ}C \text{ to} + 70^{\circ}C \text{ unless otherwise noted})$

| Parameter            | Symbol          | Min. | Тур. | Max. | Unit | Conditions                                                                           |

|----------------------|-----------------|------|------|------|------|--------------------------------------------------------------------------------------|

| Input Load Current   | 1 <sub>L1</sub> | -10  |      | 10   | μА   | V <sub>CC</sub> = +5.5<br>V <sub>IN</sub> = 0 to V <sub>CC</sub>                     |

| I/O Leakage Current  | IFO             | -10  |      | 10   | μА   | CS = OE = 2.4V<br>V <sub>CC</sub> = +5.5V<br>V <sub>OUT</sub> = 0 to V <sub>CC</sub> |

| Output High Voltage  | Voн             | 2.4  |      |      | V    | I <sub>OH</sub> = -1.0 mA                                                            |

| Output Low Voltage   | VOL             |      |      | 0.4  | V    | I <sub>OL</sub> = 2.1 mA                                                             |

| Power Supply Current | lcc             |      |      | 145  | mA   | V <sub>CC</sub> = +5.5V<br>I <sub>I/O</sub> = 0 mA                                   |

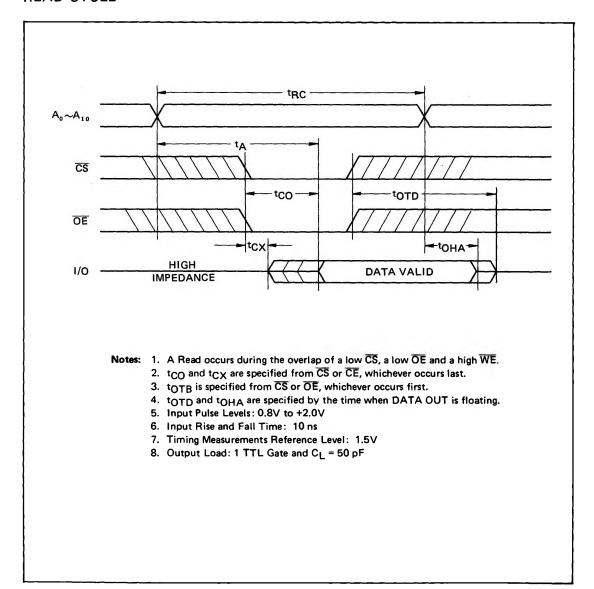

# AC CHARACTERISTICS READ CYCLE

$(V_{CC} = 5V \pm 10\%, Ta = 0^{\circ}C \text{ to } +70^{\circ}C)$

| Parameter                       | Symbol | MSM | 2128-1 | MSM2128-13 |     | l    |

|---------------------------------|--------|-----|--------|------------|-----|------|

| r al allieter                   |        | MIN | MAX    | MIN        | MAX | Unit |

| Read Cycle Time                 | tRC    | 200 |        | 300        |     | ns   |

| Access Time                     | tA     |     | 200    |            | 300 | ns   |

| Chip Selection to Output Valid  | tco    |     | 70     |            | 100 | ns   |

| Chip Selection to Output Active | tCX    | 10  |        | 10         |     | ns   |

| Output 3-State from Deselection | tOTD   |     | 60     |            | 80  | ns   |

| Output Hold from Address Change | tOHA   | 20  |        | 20         |     | ns   |

#### **READ CYCLE**

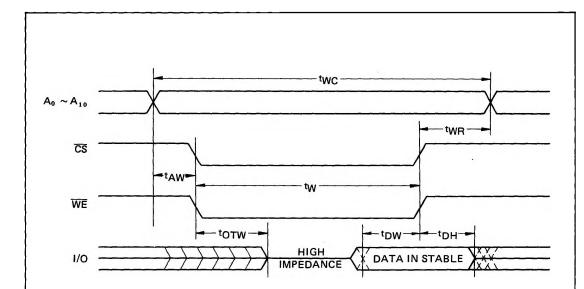

#### WRITE CYCLE

$(V_{CC} = 5V \pm 10\%, Ta = 0^{\circ}C \text{ to } +70^{\circ}C)$

|                             | Symbol | MSM21 | 128-1AS | MSM2128-13AS |      |      |

|-----------------------------|--------|-------|---------|--------------|------|------|

| Parameter                   |        | Min.  | Max.    | Min.         | Max. | Unit |

| Write Cycle Time            | twc    | 200   |         | 300          |      | ns   |

| Write Time                  | tw     | 120   |         | 150          |      | ns   |

| Write Release Time          | twn    | 20    |         | 30           |      | ns   |

| Output 3-State from Write   | tOTW   |       | 60      |              | 80   | ns   |

| Data to Write Time Overlap  | tDW    | 120   |         | 150          |      | ns   |

| Data Hold from Write Time   | tDH    | 0     |         | 0            |      | ns   |

| Address to Write Setup Time | tAW    | 0     |         | 0            |      | ns   |

#### WRITE CYCLE

Notes: 1. A Write Cycle occurs during the overlap of a low  $\overline{\text{CS}}$  and low  $\overline{\text{WE}}$ .

- 2. OE may be both high and low in a Write Cycle.

- 3.  $t_{AW}$  is specified from  $\overline{CS}$  or  $\overline{WE}$ , whichever occurs last.

- 4. tw is a overlap time of a low CS and low WE.

- 5. twR, tDW and tDH are specified from CS or WE, whichever occurs first.

- 6. toTW is specified by the time when DATA OUT is floating, not defined by output level.

- 7. When I/O pins are Data output mode, don't force inverse signal to those pins.

- 8. Input Pulse Levels: 0.8V to + 2.0V

- 9. Input Rise and Fall Time: 10 ns

- 10. Timing Measurements Reference Level: 1.5V

### **CAPACITANCE**

$(T_a = 25^{\circ}C, f = 1MHz)$

| Parameter                | Symbol           | Min. | Тур. | Max. | Unit |

|--------------------------|------------------|------|------|------|------|

| Input/Output Capacitance | C <sub>I/O</sub> |      | 4    | 6    | pF   |

| Input Capacitance        | CIN              |      | 4    | 6    | pF   |

Note: This parameter is periodically sampled and not 100% tested.