Buffered Multiplying 12-Bit Digital-to-Analog Converter

#### **FEATURES**

- Full Four Quadrant Multiplication

- 12-Bit Resolution

- Gain Error Tempco (2 ppm/°C max.)

- Latch-Up Free

- Single +5 V to +15 V Supply

- TTL/15 V CMOS Compatible

- Rugged 2000 V ESD Protection

- 3 V Version: MP75L45

- TTL/5 V VMOS Version: MP7645B

#### **APPLICATIONS**

- Industrial Automation

- Automatic Test Equipment

- · Disk Drive Servo Systems

- Digital/Synchro Conversion

- · Programmable Gain Amplifiers

- Ratiometric A/D Conversion

- Function Generation

- . Digitally Controlled Filters

#### **GENERAL DESCRIPTION**

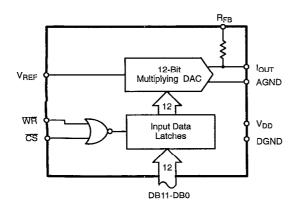

The MP7545B is a 12-bit CMOS multiplying DAC with on-board data latches. It is loaded by a single 12-bit wide word and interfaces directly to most 12- and 16-bit bus systems. Data is loaded into the input latches under the control of the CS and WR

inputs; tying these control inputs low makes the input latches transparent allowing direct unbuffered operation of the DAC.

The MP7545B is particularly suitable for single supply operation and applications with wide temperature variations.

The MP7545B can be used with any supply voltage from +5 V to +15 V. With CMOS logic levels at the inputs the device dissipates less than 0.5 mW for  $V_{DD} = +5$  V.

#### SIMPLIFIED BLOCK DIAGRAM

4

## **ORDERING INFORMATION**

| Package<br>Type | Temperature<br>Range | Part No.  | INL<br>(LSB) | DNL<br>(LSB) | Gain Error<br>(LSB) |

|-----------------|----------------------|-----------|--------------|--------------|---------------------|

| Plastic Dip     | -40 to +85°C         | MP7545BKN | 土1           | 土1           | ±3                  |

| Plastic Dip     | -40 to +85°C         | MP7545BLN | 土1/2         | 土1           | ±2                  |

| SOIC            | -40 to +85°C         | MP7545BKS | ±1           | 土1           | ±3                  |

| SOIC            | -40 to +85°C         | MP7545BLS | ±1/2         | 土1           | ±2                  |

| PLCC            | -40 to +85°C         | MP7545BKP | 土1           | 土1           | ±3                  |

| PLCC            | -40 to +85°C         | MP7545BLP | 土1/2         | 土1           | ±2                  |

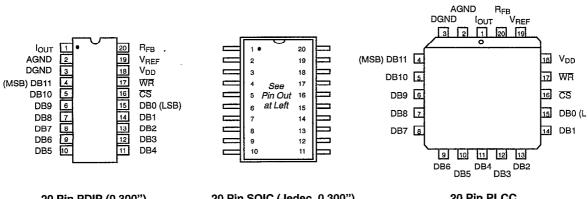

## PIN CONFIGURATIONS

See Packaging Section for Package Dimensions

20 Pin PDIP (0.300") N20 20 Pin SOIC (Jedec, 0.300") S20 20 Pin PLCC P20

## **PIN OUT DEFINITIONS**

| PIN NO. | NAME | DESCRIPTION             |

|---------|------|-------------------------|

| 1       | lout | Output Current          |

| 2       | AGND | Analog Ground           |

| 3       | DGND | Digital Ground          |

| 4       | DB11 | Data Input Bit 11 (MSB) |

| 5       | DB10 | Data Input Bit 10       |

| 6       | DB9  | Data Input Bit 9        |

| 7       | DB8  | Data Input Bit 8        |

| 8       | DB7  | Data Input Bit 7        |

| 9       | DB6  | Data Input Bit 6        |

| 10      | DB5  | Data Input Bit 5        |

|   | PIN NO. | NAME             | DESCRIPTION              |

|---|---------|------------------|--------------------------|

| ļ | 11      | DB4              | Data Input Bit 4         |

| ļ | 12      | DB3              | Data Input Bit 3         |

| Ì | 13      | DB2              | Data Input Bit 2         |

| ١ | 14      | DB1              | Data Input Bit 1         |

|   | 15      | DB0              | Data Input Bit 0 (LSB)   |

| 1 | 16      | टड               | Chip Select (Active Low) |

| 1 | 17      | WR               | Write (Active Low)       |

|   | 18      | V <sub>DD</sub>  | Digital Supply Voltage   |

|   | 19      | V <sub>REF</sub> | Reference Input          |

| ļ | 20      | R <sub>FB</sub>  | Feedback Resistor        |

4

## **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = +5 V, V_{REF} = +10 V \text{ unless otherwise noted})$

| Parameter                                                                                             | Symbol                                                  | Min | 25°C<br>Typ | Max        | Tmin to<br>Min | Tmax<br>Max | Units              | Test Conditions/Comments                                                                                                                          |

|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-----|-------------|------------|----------------|-------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| STATIC PERFORMANCE <sup>1</sup>                                                                       |                                                         |     |             |            |                |             |                    |                                                                                                                                                   |

| Resolution (All Grades)                                                                               | N                                                       | 12  |             |            | 12             |             | Bits               |                                                                                                                                                   |

| Integral Non-Linearity<br>(Relative Accuracy)                                                         | INL                                                     |     |             |            |                |             | LSB                | End Point Linearity                                                                                                                               |

| K<br>L                                                                                                |                                                         |     |             | ±1<br>±1/2 |                | ±1<br>±1/2  |                    |                                                                                                                                                   |

| Differential Non-Linearity  K L                                                                       | DNL                                                     |     |             | ±1<br>±1   |                | ±1<br>±1    | LSB                |                                                                                                                                                   |

| Gain Error<br>K<br>L                                                                                  | GE                                                      |     |             | ±3<br>±2   |                | ±4<br>±3    | LSB                | Using Internal R <sub>FB</sub>                                                                                                                    |

| Gain Temperature Coefficient <sup>2</sup>                                                             | TC <sub>GE</sub>                                        |     |             |            |                | ±2          | ррті/°С            | ΔGain/ΔTemperature                                                                                                                                |

| Power Supply Rejection Ratio                                                                          | PSRR                                                    |     |             | ±50        |                | ±100        | ppm/%              | $ \Delta Gain/\Delta V_{DD}  \Delta V_{DD} = \pm 5\%$                                                                                             |

| Output Leakage Current<br>K, L                                                                        | Іоит                                                    |     |             | ±10        |                | ±50         | nA                 |                                                                                                                                                   |

| DYNAMIC PERFORMANCE <sup>2</sup>                                                                      |                                                         |     |             |            |                |             |                    | R <sub>L</sub> =100Ω, C <sub>L</sub> =13pF                                                                                                        |

| Current Settling Time<br>AC Feedthrough at I <sub>OUT</sub><br>Propagation Delay                      | ts<br>F <sub>T</sub><br>t <sub>PD</sub>                 |     | 5<br>50     | 1          | -              | 1           | μs<br>mV p-p<br>ns | Full Scale Change to 1/2 LSB<br>V <sub>REF</sub> = 10kHz, 20 Vp-p sinewave.<br>From 50% of digital input to 90%<br>of final analog output current |

| REFERENCE INPUT                                                                                       |                                                         |     |             |            |                |             |                    |                                                                                                                                                   |

| Input Resistance                                                                                      | R <sub>IN</sub>                                         | 7   |             | 25         | 7              | 25          | kΩ                 |                                                                                                                                                   |

| DIGITAL INPUTS <sup>3</sup>                                                                           |                                                         |     |             |            |                |             |                    |                                                                                                                                                   |

| Logical "1" Voltage<br>Logical "0" Voltage<br>Input Leakage Current<br>Input Capacitance <sup>2</sup> | V <sub>IH</sub><br>V <sub>IL</sub><br>I <sub>L</sub> KG | 2.4 |             | 0.8<br>±1  | 2.4            | 0.8<br>±10  | V<br>V<br>μΑ       |                                                                                                                                                   |

| Data<br>Control                                                                                       | C <sub>IN</sub><br>C <sub>IN</sub>                      |     |             | 5<br>20    |                | 5<br>20     | pF<br>pF           |                                                                                                                                                   |

| ANALOG OUTPUTS                                                                                        |                                                         |     | <u> </u>    |            |                |             |                    |                                                                                                                                                   |

| Output Capacitance <sup>2</sup>                                                                       | C <sub>OUT</sub><br>C <sub>OUT</sub>                    |     | 100<br>50   |            |                |             | pF<br>pF           | DAC Inputs all 1's<br>DAC Inputs all 0's                                                                                                          |

# **ELECTRICAL CHARACTERISTICS (CONT'D)**

| Parameter                                                                                                                                                   | Symbol                                                  | Min                          | 25°C<br>Typ | Max     | Tmin to<br>Min | Tmax<br>Max | Units                      | Test Conditions/Comments                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|------------------------------|-------------|---------|----------------|-------------|----------------------------|---------------------------------------------|

| POWER SUPPLY <sup>5</sup>                                                                                                                                   |                                                         |                              |             |         |                |             |                            |                                             |

| Functional Voltage Range<br>Supply Current                                                                                                                  | V <sub>DD</sub><br>I <sub>DD</sub>                      | 5                            |             | 15<br>1 | 5              | 15<br>1     | V<br>mA                    | All digital inputs = 0 V or V <sub>DD</sub> |

| SWITCHING<br>CHARACTERISTICS <sup>2, 4</sup>                                                                                                                |                                                         |                              |             |         | i.             |             |                            |                                             |

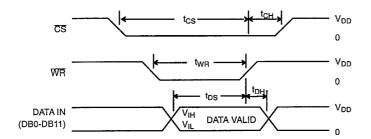

| Chip Select to Write Set-Up Time<br>Chip Select to Write Hold Time<br>Data Valid to Write Set-Up Time<br>Data Valid to Write Hold Time<br>Write Pulse Width | tcs<br>tch<br>tos<br>t <sub>DH</sub><br>t <sub>WR</sub> | 100<br>0<br>100<br>10<br>100 |             |         |                |             | ns<br>ns<br>ns<br>ns<br>ns |                                             |

#### NOTES:

- Full Scale Range (FSR) is 10V for unipolar mode. Guaranteed but not production tested.

- 2

- Digital input levels should not go below ground or exceed the positive supply voltage, otherwise damage may occur.

- See timing diagram.

- Specified values guarantee functionality. Refer to other parameters for accuracy.

Specifications are subject to change without notice

WIF / JAJL

# **ELECTRICAL CHARACTERISTICS**

( $V_{DD} = + 15 \text{ V}$ ,  $V_{REF} = +10 \text{ V}$  unless otherwise noted)

| Parameter                                                                                             | Symbol                                                 | Min  | 25°C<br>Typ | Max        | Tmin to<br>Min | Tmax<br>Max | Units              | Test Conditions/Comments                                                                                                                         |

|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------|-------------|------------|----------------|-------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| STATIC PERFORMANCE <sup>1</sup>                                                                       |                                                        |      |             |            |                |             |                    |                                                                                                                                                  |

| Resolution (All Grades)                                                                               | N                                                      | 12   |             |            | 12             |             | Bits               |                                                                                                                                                  |

| Integral Non-Linearity<br>(Relative Accuracy)                                                         | INL                                                    |      |             |            |                |             | LSB                | End Point Linearity                                                                                                                              |

| K<br>L                                                                                                |                                                        |      |             | ±1<br>±1/2 |                | ±1<br>±1/2  |                    |                                                                                                                                                  |

| Differential Non-Linearity<br>K<br>L                                                                  | DNL                                                    |      |             | ±1<br>±1   |                | ±1<br>±1    | LSB                |                                                                                                                                                  |

| Gain Error<br>K                                                                                       | GE                                                     |      |             | ±6<br>±5   |                | ±7<br>±6    | LSB                | Using Internal R <sub>FB</sub>                                                                                                                   |

| L  Gain Temperature Coefficient <sup>2</sup>                                                          | TCGE                                                   |      |             | 10         |                | ±2          | ppm/°C             | ΔGain/ΔTemperature                                                                                                                               |

| Power Supply Rejection Ratio                                                                          | PSRR                                                   |      |             | ±50        |                | ±100        | ppm/%              | ΔGain/ΔV <sub>DD</sub>   ΔV <sub>DD</sub> = ± 5%                                                                                                 |

| Output Leakage Current<br>K, L                                                                        | Іоит                                                   |      |             | ±10        |                | ±50         | nA                 |                                                                                                                                                  |

| DYNAMIC PERFORMANCE <sup>2</sup>                                                                      |                                                        |      |             |            |                |             |                    | R <sub>L</sub> =100Ω, C <sub>L</sub> =13pF                                                                                                       |

| Current Settling Time<br>AC Feedthrough at I <sub>OUT</sub><br>Propagation Delay                      | t <sub>S</sub><br>F <sub>T</sub><br>t <sub>PD</sub>    |      | 5<br>50     | 1          |                | 1           | μs<br>mV p-p<br>ns | Full Scale Change to 1/2 LSB<br>V <sub>REF</sub> =10kHz, 20 Vp-p sinewave.<br>From 50% of digital input to 90%<br>of final analog output current |

| REFERENCE INPUT                                                                                       |                                                        |      |             |            |                |             |                    |                                                                                                                                                  |

| Input Resistance                                                                                      | R <sub>IN</sub>                                        | 7    |             | 25         | 7              | 25          | kΩ                 |                                                                                                                                                  |

| DIGITAL INPUTS <sup>3</sup>                                                                           |                                                        |      |             |            |                |             |                    |                                                                                                                                                  |

| Logical "1" Voltage<br>Logical "0" Voltage<br>Input Leakage Current<br>Input Capacitance <sup>2</sup> | V <sub>IH</sub><br>V <sub>IL</sub><br>I <sub>LKG</sub> | 13.5 |             | 1.5<br>±1  | 13.5           | 1.5<br>±10  | V<br>V<br>μΑ       | V <sub>IN</sub> = 0 or V <sub>DD</sub>                                                                                                           |

| DB0-DB11<br>WR, CS                                                                                    | C <sub>IN</sub><br>C <sub>IN</sub>                     |      |             | 5<br>20    |                | 5<br>20     | pF<br>pF           | $V_{IN} = 0$ $V_{IN} = 0$                                                                                                                        |

| ANALOG OUTPUTS                                                                                        |                                                        |      |             |            |                |             |                    |                                                                                                                                                  |

| Output Capacitance <sup>2</sup>                                                                       | C <sub>OUT</sub><br>C <sub>OUT</sub>                   |      | 100<br>50   |            |                |             | pF<br>pF           | DAC Inputs all 1's<br>DAC Inputs all 0's                                                                                                         |

## **ELECTRICAL CHARACTERISTICS (CONT'D)**

| Parameter                                                                                                                                                   | Symbol                                                                                      | Min                        | 25°C<br>Typ | Max     | Tmin to<br>Min | Tmax<br>Max | Units                | Test Conditions/Comments                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|----------------------------|-------------|---------|----------------|-------------|----------------------|-------------------------------------------|

| POWER SUPPLY <sup>5</sup>                                                                                                                                   |                                                                                             |                            |             |         |                |             |                      |                                           |

| Functional Voltage Range<br>Supply Current                                                                                                                  | V <sub>DD</sub>                                                                             | 5                          |             | 15<br>1 | 5              | 15<br>1     | V<br>mA              | All digital inputs = 0 or V <sub>DD</sub> |

| SWITCHING<br>CHARACTERISTICS <sup>2, 4</sup>                                                                                                                |                                                                                             |                            |             |         |                |             |                      |                                           |

| Chip Select to Write Set-Up Time<br>Chip Select to Write Hold Time<br>Data Valid to Write Set-Up Time<br>Data Valid to Write Hold Time<br>Write Pulse Width | t <sub>CS</sub><br>t <sub>CH</sub><br>t <sub>DS</sub><br>t <sub>DH</sub><br>t <sub>WR</sub> | 75<br>0<br>100<br>10<br>75 |             |         |                |             | ns<br>ns<br>ns<br>ns |                                           |

#### NOTES:

- Full Scale Range (FSR) is 10V for unipolar mode and  $\pm 10$ V for bipolar.

- Guaranteed but not production tested.

- Digital input levels should not go below ground or exceed the positive supply voltage, otherwise damage may occur.

- See timing diagram.

- Specified values guarantee functionality. Refer to other parameters for accuracy.

Specifications are subject to change without notice

# ABSOLUTE MAXIMUM RATINGS (TA = +25°C unless otherwise noted)<sup>1, 2, 3</sup>

| V <sub>DD</sub> to GND                                                                                                                          | Storage Temperature65°C to +150°C               |

|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| Digital Input Voltage to GND GND -0.5 to V <sub>DD</sub> +0.5 V I <sub>OUT1</sub> , I <sub>OUT2</sub> to GND GND -0.5 to V <sub>DD</sub> +0.5 V | Lead Temperature (Soldering, 10 seconds) +300°C |

| V <sub>REE</sub> to GND±25 V                                                                                                                    | Package Power Dissipation Rating to 75°C        |

| V <sub>RER</sub> to GND ±25 V                                                                                                                   | PDIP, SOIC, PLCC 900mW                          |

| AGND to DGND ±0.5 V                                                                                                                             | Derates above 75°C 12mW/°C                      |

NOTES:

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation at or above this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

Any input pin which can see a value outside the absolute maximum ratings should be protected by Schottky diode clamps (HP5082-2835) from input pin to the supplies. All inputs have protection diodes which will protect the device from short transients outside the supplies of less than 100mA for less than 100μs.

GND refers to AGND and DGND.

## WRITE CYCLE TIMING DIAGRAM

# APPLICATION NOTES Refer to Section 8 for Applications Information

#### **Digital Section**

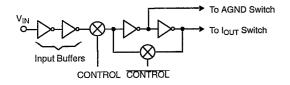

Figure 2. shows the digital structure for one bit.

Figure 1. Digital Input Structure

The digital signals CONTROL and  $\overline{\text{CONTROL}}$  are generated from  $\overline{\text{CS}}$  and  $\overline{\text{WR}}$ .

The input buffers are simple CMOS inverters designed such that when the MP7545B is operated with  $V_{DD}=5$  V, the buffers convert TTL input levels (2.4 V and 0.8 V) into CMOS logic levels. When  $V_{\rm IN}$  is in the region of 2.0 volts to 3.5 volts the input buffers operate in their linear region and draw current from the power supply. To minimize power supply currents it is recommended that the digital input voltages be as close to the supply rails (V\_DD and DGND) as is practically possible.

The MP7545B may be operated with any supply voltage in the range  $5 \le V_{DD} \le 15$  volts. With  $V_{DD} = +15$  V the input logic levels are CMOS compatible only, i.e., 1.5 V and 13.5 V.

# MICROPROCESSOR INTERFACING OF THE MP7545B

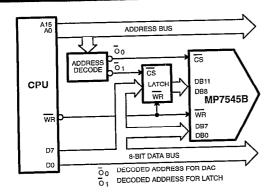

The MP7545B can interface directly to both 8- and 16-bit microprocessors via its 12-bit wide data latch using standard  $\overline{\text{CS}}$  and  $\overline{\text{WR}}$  control signals.

A typical interface circuit for an 8-bit processor is shown in *Figure 3*. This arrangement uses two memory addresses, one for the lower 8 bits of data to the DAC and one for the upper 4 bits of data into the DAC via the latch.

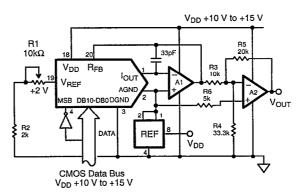

Figure 2. Single Supply "Bipolar" 2's Complement D/A Converter

Rev. 2.00

Figure 3. 8-Bit Processor to MP7545B Interface

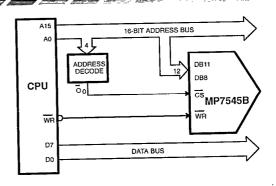

Figure 4. Connecting the MP7545B to 8-Bit Processors via the Address Bus

Figure 4. shows an alternative approach for use with 8-bit processors which have a full 16-bit wide address bush such as 6800, 8080, Z80. This technique uses the 12 lower address lines of the processor address bus to supply data to the DAC, thus each MP7545B connected in this way uses 4k bytes of ad-

dress locations. Data is written to the DAC using a single memory write instruction. The address field of the instruction is organized so that the lower 12 bits contain the data for the DAC and the upper 4 bits contain the address of the 4k block at which the DAC resides.

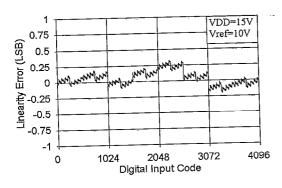

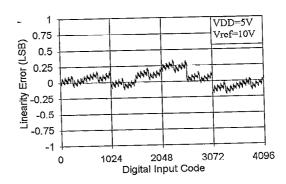

# PERFORMANCE CHARACTERISTICS

Graph 1. Linearity Error vs.

Digital Input Code

Graph 2. Linearity Error vs.

Digital Input Code

APPLICATION NOTES

Refer to Section 8 for Applications Information

Rev. 2.00