# MN35502

# D/A Converter for Digital Audio Equipment

#### Overview

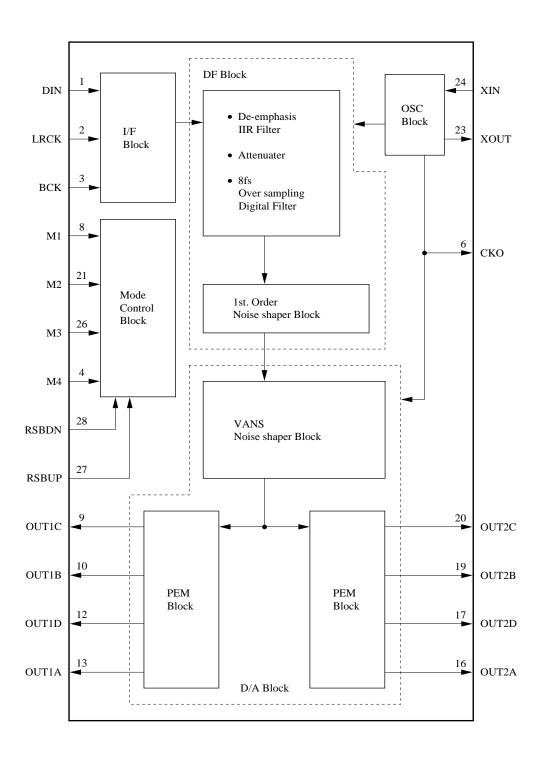

The MN35502 is a CMOS digital-to-analog converter designed especially for PCM digital audio equipment. It features a built-in digital filter with 16/20-bit input.

It uses pulse edge modulation (PEM) and JVC advanced noise shaping (VANS) to yield the high resolution and low distortion ratio equivalent to those of 20-bit systems covering the range between 0 and 20 kHz.

The chip incorporates an 8-fold oversampling digital filter that eliminates a low-pass filter after the D/A converter and thus greatly reduces the power consumption of the overall D/A conversion system.

Use of single-channel 4PEM output yields a D/A converter with a low distortion ratio and high signal-to-noise ratio.

The chip makes a major contribution to reducing the cost and size of CD players and other digital audio equipment.

#### Features

- Built-in 20-bit, 8-fold oversampling digital filter

- 2-fold oversampling digital filters with 3-stage cascade configuration

Bandwidth ripple: within  $\pm 0.0042$  dB for 0 to 0.454  $f_s$  Cutoff band attenuation

1±0.454 f<sub>s</sub>: min. 94.8dB 2±0.454 f<sub>s</sub>: min. 77.4dB 4±0.454 f<sub>s</sub>: min. 66.8dB

Transition bandwidth

$0.469 f_s$ : -0.12dB $0.531 f_s$ : -38dB

• Digital filter output: 24 bits

(Output after data compression with primary noise shaper)

• Built-in digital de-emphasis

$f_S$ =44.1 kHz 0 to 18kHz max. deviation  $\pm 0.055$ dB 18 to 20kHz max. deviation 0.115dB

• Built-in digital attenuation

Up/down over 32 steps

• Support for double-speed operation (192 f<sub>s</sub> clock)

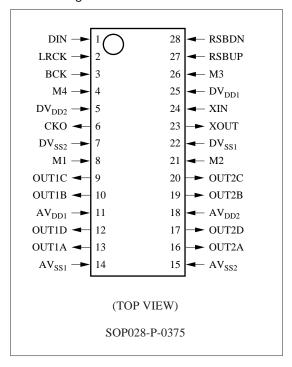

#### ■ Pin Assignment

- 8PEM output configuration (4PEM output per channel)

- Support for low-voltage (3.3-volt) operation

- Choice of system clocks:

192 f<sub>s</sub>, 256 f<sub>s</sub>, 384 f<sub>s</sub>, 512 f<sub>s</sub>, 576 f<sub>s</sub>

- Choice of input data formats: left-packed, right-packed, I<sup>2</sup>S bus (16 or 20 bits, alternating channel input, MSB first)

### Applications

• CD players and other digital audio equipment

# ■ Block Diagram

# ■ Pin Descriptions

| Pin No. | Pin Name                     | Function Description                                                           |  |  |  |  |  |  |  |  |  |  |

|---------|------------------------------|--------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

| 1       | DIN                          | Serial data pin (MSB first)                                                    |  |  |  |  |  |  |  |  |  |  |

| 2       | LRCK                         | LR synchronization signal input pin (f <sub>s</sub> rate)                      |  |  |  |  |  |  |  |  |  |  |

| 3       | BCK                          | Data shift bit clock input pin                                                 |  |  |  |  |  |  |  |  |  |  |

| 4       | M4                           | Operating mode selection pin 4 (See Table 1.)                                  |  |  |  |  |  |  |  |  |  |  |

| 5       | $\mathrm{DV}_{\mathrm{DD2}}$ | Power supply pin 2 for digital circuits                                        |  |  |  |  |  |  |  |  |  |  |

| 6       | СКО                          | Clock output pin                                                               |  |  |  |  |  |  |  |  |  |  |

| 7       | $\mathrm{DV}_{\mathrm{SS2}}$ | Ground pin for digital circuits                                                |  |  |  |  |  |  |  |  |  |  |

| 8       | M1                           | Operating mode selection pin 1, with pull-up resistor (See Table 1.)           |  |  |  |  |  |  |  |  |  |  |

| 9       | OUT1C                        | PEM output pin 1C (Left channel with reversed phase)                           |  |  |  |  |  |  |  |  |  |  |

| 10      | OUT1B                        | PEM output pin 1B (Left channel with same phase)                               |  |  |  |  |  |  |  |  |  |  |

| 11      | $AV_{DD1}$                   | Power supply pin 1 for analog circuits                                         |  |  |  |  |  |  |  |  |  |  |

| 12      | OUT1D                        | PEM output pin 1D (Left channel with reversed phase)                           |  |  |  |  |  |  |  |  |  |  |

| 13      | OUT1A                        | PEM output pin 1A (Left channel with same phase)                               |  |  |  |  |  |  |  |  |  |  |

| 14      | $AV_{SS1}$                   | Ground pin 1 for analog circuits                                               |  |  |  |  |  |  |  |  |  |  |

| 15      | $AV_{SS2}$                   | Ground pin 2 for analog circuits                                               |  |  |  |  |  |  |  |  |  |  |

| 16      | OUT2A                        | PEM output pin 2A (Right channel with same phase)                              |  |  |  |  |  |  |  |  |  |  |

| 17      | OUT2D                        | PEM output pin 2D (Right channel with reversed phase)                          |  |  |  |  |  |  |  |  |  |  |

| 18      | $AV_{DD2}$                   | Power supply pin 2 for analog circuits                                         |  |  |  |  |  |  |  |  |  |  |

| 19      | OUT2B                        | PEM output pin 2B (Right channel with same phase)                              |  |  |  |  |  |  |  |  |  |  |

| 20      | OUT2C                        | PEM output pin 2C (Right channel with reversed phase)                          |  |  |  |  |  |  |  |  |  |  |

| 21      | M2                           | Operating mode selection pin 2, with pull-up resistor (See Table 1.)           |  |  |  |  |  |  |  |  |  |  |

| 22      | $DV_{SS1}$                   | Ground pin 1 for digital circuits (Ground for oscillator circuit)              |  |  |  |  |  |  |  |  |  |  |

| 23      | XOUT                         | Crystal oscillator pin                                                         |  |  |  |  |  |  |  |  |  |  |

| 24      | XIN                          | Crystal oscillator pin (external clock input pin) (Built-in feedback resistor) |  |  |  |  |  |  |  |  |  |  |

| 25      | $\mathrm{DV}_{\mathrm{DD1}}$ | Power supply pin 1 for digital circuits                                        |  |  |  |  |  |  |  |  |  |  |

| 26      | M3                           | Operating mode selection pin 3, with pull-up resistor (See Table 1.)           |  |  |  |  |  |  |  |  |  |  |

| 27      | RSBUP                        | Reset pin/digital attenuation control pin (See Table 2.)                       |  |  |  |  |  |  |  |  |  |  |

| 28      | RSBDN                        | Reset pin/digital attenuation control pin (See Table 2.)                       |  |  |  |  |  |  |  |  |  |  |

3

# ■ Operating Mode Descriptions

Table 1. MN35502 Operating Modes

| Mode Selection Pins                    |              | Pin States and Operating Modes |       |    |                    |                           |     |           |      |                        |                  |                   |                         |                 |                  |                  |                  |                  |

|----------------------------------------|--------------|--------------------------------|-------|----|--------------------|---------------------------|-----|-----------|------|------------------------|------------------|-------------------|-------------------------|-----------------|------------------|------------------|------------------|------------------|

| M1                                     |              | L                              |       |    |                    |                           |     |           | Н    |                        |                  |                   |                         |                 |                  |                  |                  |                  |

| M2                                     |              | L                              |       |    | Н                  |                           |     |           |      |                        | Н                |                   |                         |                 | Н                |                  |                  |                  |

| M3                                     |              | L H                            |       |    | L                  |                           | Н   |           |      |                        | L                |                   | Н                       |                 | L                |                  | Н                |                  |

| M4                                     | L            | L H L H L                      |       | L  | Н                  | ]                         |     | Н         |      | L                      | Н                | L                 | Н                       | L               | Н                | L                | Н                |                  |

| RSBUP                                  |              |                                |       |    |                    |                           | L   | Н         | L    | Н                      |                  |                   |                         |                 |                  |                  |                  |                  |

| Mode                                   | 0            | 1                              | 2     | 3  | 4                  | 5                         | 60  | 61        | 70   | 71                     | 8                | 9                 | A                       | В               | С                | D                | Е                | F                |

| Input data format                      |              | Right-packe                    |       |    |                    |                           | ed  |           |      |                        | Right-<br>packed | Left-<br>packed   | Right-<br>packed        | Left-<br>packed | Right-<br>packed | I <sup>2</sup> S | Right-<br>packed | I <sup>2</sup> S |

| Input word length (bit)                |              | 1                              | 16 20 |    | 0.                 | 16                        | 20  | 16        |      | 16                     | 20               | 16                | 20                      | 16              | 20               | 16               | 20               |                  |

| Data when LRCK=H                       | Left channel |                                |       |    |                    |                           |     |           | R    | L                      | R                | L                 | L                       | R               | L                | R                |                  |                  |

| XIN clock frequency (f <sub>s</sub> )  | 38           | 34                             | 19    | 92 | 384                |                           | 512 |           | Mode | 384 576                |                  | 76                | 256                     |                 | 38               | 384              |                  |                  |

| CKO output frequency (f <sub>s</sub> ) | 38           | 34                             | 19    | 92 | 38                 | 84                        | 5   |           | 512  |                        | 32               | 32   64   32   64 |                         |                 |                  |                  |                  |                  |

| Digital attenuation                    | Available    |                                |       |    | Not available Last |                           |     | Available |      |                        |                  |                   |                         |                 |                  |                  |                  |                  |

| De-emphasis (f <sub>s</sub> =44.1kHz)  | _            | 0                              | _     | О  | 0 - 0 - 0          |                           |     |           |      |                        | _                |                   |                         |                 |                  |                  |                  |                  |

| VANS oversampling (f <sub>s</sub> )    | 64           | 4                              | 3     | 32 |                    |                           | 64  |           |      |                        | 64               |                   | 9                       | 6               | 6                | 4                | 9                | 6                |

| Theoretical signal-to-noise ratio (dB) | 13           | 134 107                        |       | 13 | 34                 | 128                       |     |           |      | 134                    |                  | 1:                | 50                      | 12              | 28               | 14               | 14               |                  |

| Output level                           |              | $0.666 \times AV_{DD}$         |       |    |                    | 0.4995 × AV <sub>DD</sub> |     |           | 0.   | $0.666 \times AV_{DD}$ |                  |                   | $0.4995 \times AV_{DD}$ |                 |                  |                  |                  |                  |

#### Notes

<sup>1:</sup> Modes 2 and 3 support  $f_s$  clock speeds up to 88.2 kHz.

<sup>2:</sup> Modes A, B, E, and F support  $f_s$  clock speeds up to 32 kHz; the others, up to 48 kHz.

#### ■ Functional Descriptions

• Digital attenuation and reset

Table 2 shows how the inputs from the two pins RSBUP and RSBDN control digital attenuation.

Table 2. Attenuation Modes

| Pin Name | Pin States and Operating Modes |                      |          |                     |          |  |  |  |  |

|----------|--------------------------------|----------------------|----------|---------------------|----------|--|--|--|--|

| RSBUP    | L                              | $\uparrow\downarrow$ | L        | <b>1</b>            | Н        |  |  |  |  |

| RSBDN    | L                              | L                    | <b>↑</b> | Н                   | <b>1</b> |  |  |  |  |

| Mode     | Reset                          | Mute                 | Normal   | Attenuation control |          |  |  |  |  |

| Volume   | 0dB                            | UP                   | DOWN     |                     |          |  |  |  |  |

#### Notes

- 1: The upward arrow indicates the rising edge change of the input signal; the paired arrows, the rising and falling edge changes.

- 2: Always reset the chip after applying the power, restarting the clock, or changing the clock speed. (Wait for the crystal oscillation to stabilize and then apply a reset signal at least eight LRCK clock cycles long.)

- 3: Digital attenuation is not available for modes with a master clock of 512  $f_s$  (modes 60 to 70).

There are a total of 32 attenuation levels.

According to the attenuation control shown in Table-2, volume goes up or down in one step every input-signal rising-edge. Still, in the 0 dB state, up-pulse does not change the volume. Similarly, in the muting state ( $-\infty$ ), down-pulse does not change the volume.

The change of the input signals is detected by inner clock of 32  $f_s$  period, so always use a frequency of 16  $f_s$  or less for changes in the RSBUP and RSBDN signals.

Do not simultaneously change the RSBUP and RSBDN signals unless setting up for a reset.

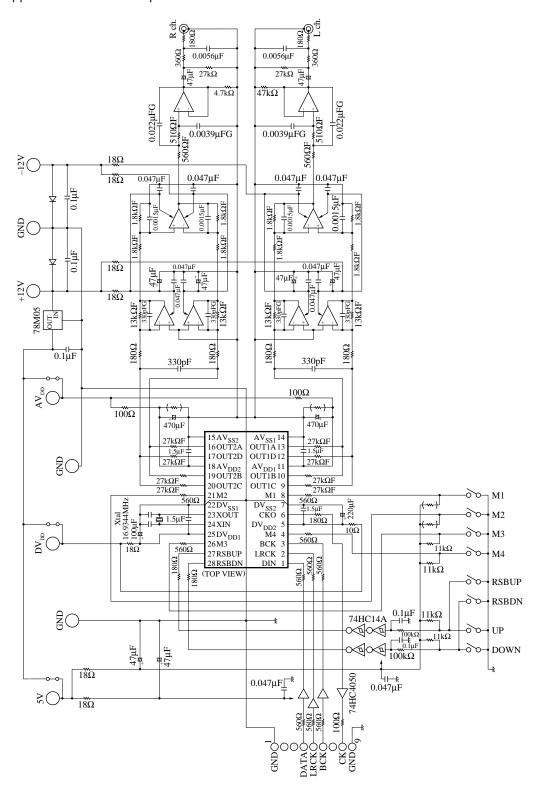

## ■ Conversion Characteristics

${\rm DV_{DD}}\!\!=\!\!5.0{\rm V},\,{\rm DV_{SS}}\!\!=\!\!0{\rm V},\,{\rm AV_{DD}}\!\!=\!\!5.0{\rm V},\,{\rm AV_{SS}},\,{\rm f}\!\!=\!\!16.9344{\rm MHz},\,{\rm Ta}\!\!=\!\!25^{\circ}{\rm C}$

Analog Characteristics for 20-bit, 1 f<sub>s</sub> input

| Parameter                 | Symbol | Test Condition | min | typ    | max    | Unit             |

|---------------------------|--------|----------------|-----|--------|--------|------------------|

| Signal-to-noise ratio     | SN     | EIAJ (kHz)     |     | 114    |        | dB               |

| Dynamic range             | D.R.   | EIAJ (kHz)     |     | 113    |        | dB               |

| Total harmonic distortion | THD+N  | EIAJ (kHz)     |     | 0.0006 | 0.0010 | %                |

| Output level              |        | 1kHz F.S.      |     | 2.1    |        | V <sub>rms</sub> |

The above analog characteristics are based on measurements with the sample application circuit using mode 4.

## ■ Application Circuit Example

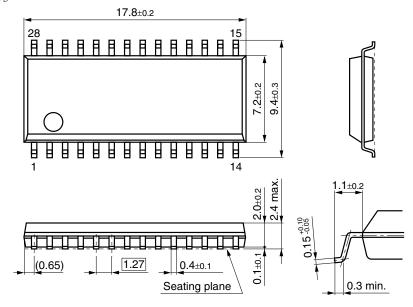

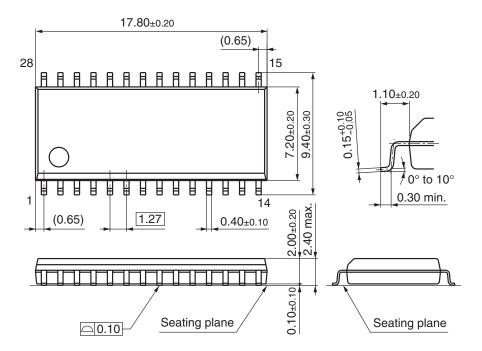

## ■ Package Dimensions (Unit: mm)

#### SOP028-P-0375

Note) The package of this product will be changed to the following lead-free type (SOP028-P-0375D).

- New Package Dimensions (Unit: mm)

- SOP028-P-0375D (Lead-free package)

8 Panasonic

# Request for your special attention and precautions in using the technical information and semiconductors described in this material

- (1) An export permit needs to be obtained from the competent authorities of the Japanese Government if any of the products or technologies described in this material and controlled under the "Foreign Exchange and Foreign Trade Law" is to be exported or taken out of Japan.

- (2) The technical information described in this material is limited to showing representative characteristics and applied circuit examples of the products. It does not constitute the warranting of industrial property, the granting of relative rights, or the granting of any license.

- (3) The products described in this material are intended to be used for standard applications or general electronic equipment (such as office equipment, communications equipment, measuring instruments and household appliances).

- Consult our sales staff in advance for information on the following applications:

- Special applications (such as for airplanes, aerospace, automobiles, traffic control equipment, combustion equipment, life support systems and safety devices) in which exceptional quality and reliability are required, or if the failure or malfunction of the products may directly jeopardize life or harm the human body.

- Any applications other than the standard applications intended.

- (4) The products and product specifications described in this material are subject to change without notice for reasons of modification and/or improvement. At the final stage of your design, purchasing, or use of the products, therefore, ask for the most up-to-date Product Standards in advance to make sure that the latest specifications satisfy your requirements.

- (5) When designing your equipment, comply with the guaranteed values, in particular those of maximum rating, the range of operating power supply voltage and heat radiation characteristics. Otherwise, we will not be liable for any defect which may arise later in your equipment. Even when the products are used within the guaranteed values, redundant design is recommended, so that such equipment may not violate relevant laws or regulations because of the function of our products.

- (6) When using products for which dry packing is required, observe the conditions (including shelf life and after-unpacking standby time) agreed upon when specification sheets are individually exchanged.

- (7) No part of this material may be reprinted or reproduced by any means without written permission from our company.

## Please read the following notes before using the datasheets

- A. These materials are intended as a reference to assist customers with the selection of Panasonic semiconductor products best suited to their applications.

- Due to modification or other reasons, any information contained in this material, such as available product types, technical data, and so on, is subject to change without notice.

- Customers are advised to contact our semiconductor sales office and obtain the latest information before starting precise technical research and/or purchasing activities.

- B. Panasonic is endeavoring to continually improve the quality and reliability of these materials but there is always the possibility that further rectifications will be required in the future. Therefore, Panasonic will not assume any liability for any damages arising from any errors etc. that may appear in this material.

- C. These materials are solely intended for a customer's individual use. Therefore, without the prior written approval of Panasonic, any other use such as reproducing, selling, or distributing this material to a third party, via the Internet or in any other way, is prohibited.