# MILITARY/HIGH-REL PRODUCTS

Extended Temperature, Extended Burn-In Industrial Processing

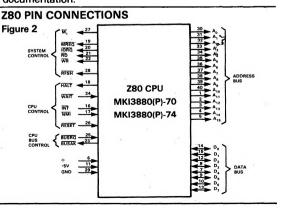

# Z80/Z80A Central Processing Unit MKI3880-70/74

### **FEATURES**

- 44 hr. min., 125°C burn-in plus industrial screening for greater reliability (see Figure 6 for processing description)

- □ -40°C to 85°C temperature range

- ☐ Two speeds

- 2.5 MHz MKI3880(P)-70 (Z80 CPU)

- 4.0 MHz MKI3880(P)-74 (Z80A CPU)

#### DESCRIPTION

The Mostek Z80 family of components is a significant advancement in the state-of-art of microcomputers. These components can be configured with any type of standard semiconductor memory to generate computer systems with an extremely wide range of capabilities. For example, as few as two LSI circuits and three standard TTL MSI packages can be combined to form a simple controller. With additional memory and I/O devices, a computer can be constructed with capabilities that only a minicomputer could deliver previously. This wide range of computational power allows standard modules to be constructed by a user that can satisfy the requirements of an extremely wide range of applications.

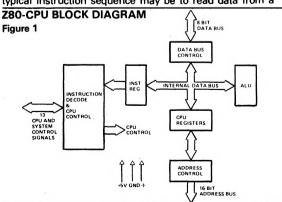

The CPU is the heart of the system. Its function is to obtain instructions from the memory and perform the desired operations. The memory is used to contain instructions and, in most cases, data that is to be processed. For example, a typical instruction sequence may be to read data from a

- ☐ Single 5-Volt supply and single-phase clock required

- ☐ Software compatible with 8080A CPU

- Complete development and OEM system product support

- ☐ Military MKB version available (-55°C/125°C)

- ☐ Typical power 625 mW

specific peripheral device, store it in a location in memory, check the parity, and write it out to another peripheral device. Note that the Mostek component set includes the CPU and various general purpose I/O device controllers, as well as a wide range of memory devices. Thus, all required components can be connected together in a very simple manner with virtually no other external logic. The user's effort then becomes primarily one of the software development. That is, the user can concentrate on describing his problem and translating it into a series of instructions that can be loaded into the microcomputer memory. Mostek is dedicated to making this step of software generation as simple as possible. A good example of this is our assembly language in which a simple mnemonic is used to represent every instruction that the CPU can perform. This language is self-documenting in such a way that from the mnemonic the user can understand exactly what the instruction is doing without constantly checking back to a complex cross listing. Please refer to the Z80 Data Book for extensive Z80 operation documentation.

# **ABSOLUTE MAXIMUM RATINGS\***

| Temperature Under Bias                    | 40°C to +85°C  |

|-------------------------------------------|----------------|

| Storage Temperature                       | 65°C to +150°C |

| Voltage on Any Pin with Respect to Ground | 0.3 V to +7 V  |

| Power Dissipation                         |                |

<sup>\*</sup>Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other condition above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### RECOMMENDED DC OPERATING CONDITIONS

(T<sub>A</sub> = -40°C to 85°C,  $V_{CC}$  = 5 V  $\pm$  5% unless otherwise specified)

| SYM                  | PARAMETER                                   | MIN               | TYP | MAX                 | UNITS | TEST CONDITIONS |

|----------------------|---------------------------------------------|-------------------|-----|---------------------|-------|-----------------|

| V <sub>ILC</sub>     | Clock Input Low Voltage                     | -0.3              |     | 0.8                 | V     |                 |

| V <sub>IHC</sub>     | Clock Input High Voltage                    | V <sub>CC</sub> 6 |     | V <sub>CC</sub> +.3 | V     | *               |

| V <sub>IL</sub>      | Input Low Voltage                           | -0.3              |     | 0.8                 | V     |                 |

| V <sub>IH</sub>      | Input High Voltage<br>All inputs except NMI | 2.4               |     | V <sub>cc</sub>     | V     |                 |

| V <sub>IH(NMI)</sub> | Input High Voltage (NMI)                    | 2.7               |     | V <sub>cc</sub>     | V     |                 |

### DC ELECTRICAL CHARACTERISTICS

(T<sub>A</sub> = -40°C to 85°C, V<sub>CC</sub> = 5 V  $\pm$  5% unless otherwise specified)

| SYM              | PARAMETER                                    | MIN | TYP | MAX | UNITS | TEST CONDITIONS                        |

|------------------|----------------------------------------------|-----|-----|-----|-------|----------------------------------------|

| V <sub>OL</sub>  | Output Low Voltage                           |     |     | 0.4 | V     | I <sub>OL</sub> = 1.8mA                |

| V <sub>OH</sub>  | Output High Voltage                          | 2.4 |     |     | V     | I <sub>OH</sub> = -250 μA              |

| Icc              | Power Supply Current                         |     |     | 200 | mA    |                                        |

| I <sub>LI</sub>  | Input Leakage Current                        |     |     | ±10 | μА    | V <sub>IN</sub> = 0 to V <sub>CC</sub> |

| I <sub>LOH</sub> | Tri-State Output Leakage<br>Current in Float |     |     | 10  | μΑ    | $V_{OUT} = 2.4 \text{ to } V_{CC}$     |

| I <sub>LOL</sub> | Tri-State Output Leakage<br>Current in Float |     |     | -10 | μΑ    | V <sub>OUT</sub> = 0.4V                |

| I <sub>LD</sub>  | Data Bus Leakage Current<br>In Input Mode    |     |     | ±10 | μΑ    | 0 < V <sub>IN</sub> < V <sub>CC</sub>  |

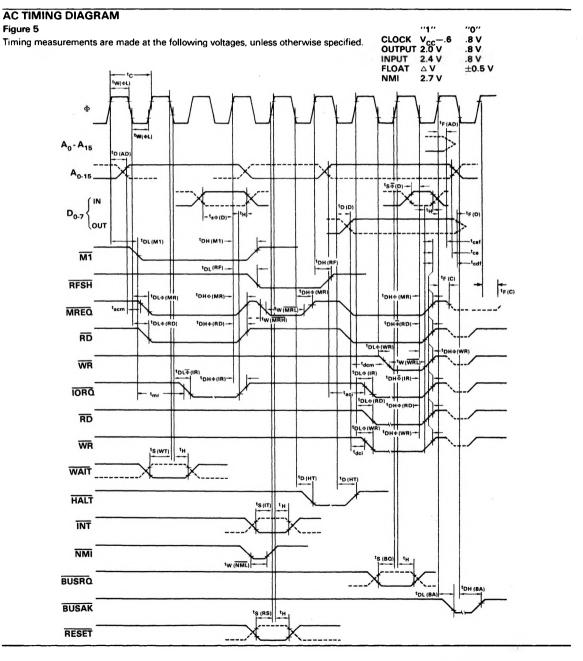

# **AC ELECTRICAL CHARACTERISTICS**

MKI3880(P)-70 Z80-CPU ( $T_A = -40^{\circ}\text{C to }85^{\circ}\text{C}$ ,  $V_{CC} = +5 \text{ V}$ ,  $\pm 5\%$ , Unless Otherwise Noted)

| SIGNAL            | SYM                                                                               | PARAMETER                                                                                                   | MIN              | MAX                       | UNIT                         | TEST CONDITIONS       |

|-------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------------------|---------------------------|------------------------------|-----------------------|

| Φ                 | t <sub>c</sub><br>t <sub>w</sub> (ΦΗ)<br>t <sub>w</sub> (ΦL)<br>t <sub>r,</sub> f | Clock Period<br>Clock Pulse Width, Clock High<br>Clock Pulse Width, Clock Low<br>Clock Rise and Fall Time   | .4<br>180<br>180 | [12]<br>(D)<br>2000<br>30 | μsec<br>nsec<br>nsec<br>nsec |                       |

| 1                 | t <sub>D(AD)</sub> t <sub>F(AD)</sub> t <sub>acm</sub>                            | Address Output Delay Delay to Float Address Stable Prior to MREQ (Memory Cycle)                             | [1]              | 145<br>110                | nsec<br>nsec<br>nsec         | C <sub>L</sub> = 50pF |

| A <sub>0-15</sub> | t <sub>aci</sub>                                                                  | Address Stable Prior to IORQ, RD or WR (I/O Cycle)                                                          | [2]              |                           | nsec                         |                       |

|                   | t <sub>ca</sub>                                                                   | Address Stable From RD, WR, IORQ or MREQ                                                                    | [3]              |                           | nsec                         | Except T3-M1          |

|                   | t <sub>caf</sub>                                                                  | Address Stable From RD or WR During Float                                                                   | [4]              |                           | nsec                         |                       |

|                   | t <sub>D(D)</sub><br>t <sub>F(D)</sub><br>t <sub>SΦ(D)</sub>                      | Data Output Delay Delay to Float During Write Cycle Data Setup Time to Rising Edge of Clock During M1 Cycle | 50               | 250<br>90                 | nsec<br>nsec<br>nsec         |                       |

| D <sub>0-7</sub>  | t <sub>S</sub> ⊕(D)                                                               | Data Setup Time to Falling Edge at<br>Clock During M2 to M5                                                 | 60               |                           | nsec                         | C <sub>L</sub> = 50pF |

|                   | t <sub>dcm</sub>                                                                  | Data Stable Prior to WR (Memory Cycle)                                                                      | [5]              |                           | nsec                         |                       |

|                   | t <sub>dci</sub>                                                                  | Data Stable Prior to WR (I/O Cycle)                                                                         | [6]              | ļ                         | nsec                         |                       |

|                   | t <sub>cdf</sub>                                                                  | Data Stable From WR                                                                                         | [7]              | {                         | nsec                         |                       |

|                   | t <sub>H</sub>                                                                    | Input Hold Time                                                                                             | 0                |                           | nsec                         |                       |

|                   | <sup>t</sup> DLΦ(MR)                                                              | MREQ Delay From Falling Edge of Clock, MREQ Low                                                             |                  | 100                       | nsec                         |                       |

| MREQ              | t <sub>DHФ(MR)</sub>                                                              | MREQ Delay From Rising Edge of Clock, MREQ High                                                             |                  | 100                       | nsec                         |                       |

|                   | t <sub>DH</sub> Φ(MR)                                                             | MREQ Delay From Falling Edge of Clock, MREQ High                                                            |                  | 100                       | nsec                         | C <sub>L</sub> = 50pF |

|                   | t <sub>w(MRL)</sub>                                                               | Pulse Width, MREQ Low                                                                                       | [8]              | ŀ                         | nsec                         |                       |

|                   | tw(MRH)                                                                           | Pulse Width, MREQ High                                                                                      | [9]              |                           | nsec                         |                       |

|                   | <sup>†</sup> DLΦ(IR)                                                              | IORQ Delay From Rising Edge of Clock, IORQ Low                                                              |                  | 90                        | nsec                         |                       |

| IORQ              | <sup>t</sup> DL⊕(IR)                                                              | IORQ Delay From Falling Edge of Clock, IORQ Low                                                             |                  | 110                       | nsec                         | C <sub>L</sub> = 50pF |

|                   | t <sub>DHΦ(IR)</sub>                                                              | IORQ Delay From Rising Edge of Clock, IORQ High                                                             |                  | 100                       | nsec                         |                       |

|                   | <sup>t</sup> DHΦ(IR)                                                              | IORQ Delay From Falling Edge of<br>Clock, IORQ High                                                         |                  | 110                       | nsec                         |                       |

|                   | t <sub>DLΦ(RD)</sub>                                                              | RD Delay From Rising Edge of Clock,                                                                         |                  | 100                       | nsec                         |                       |

| RD                | t <sub>DL⊕(RD)</sub>                                                              | RD Delay From Falling Edge of Clock,                                                                        |                  | 130                       | nsec                         | C <sub>L</sub> = 50pF |

|                   | <sup>†</sup> DHΦ(RD)                                                              | RD Delay From Rising Edge of Clock, RD High                                                                 |                  | 100                       | nsec                         |                       |

|                   | t <sub>DHΦ(RD)</sub>                                                              | RD Delay From Falling Edge of Clock, RD High                                                                |                  | 110                       | nsec                         |                       |

# AC ELECTRICAL CHARACTERISTICS (Cont.)

(T<sub>A</sub> = -40°C to 85°C,  $V_{CC}$  = +5 V,  $\pm$  5%, unless otherwise noted)

| SIGNAL | SYM                   | PARAMETER                                          | MIN  | MAX | UNIT | TEST CONDITIONS       |

|--------|-----------------------|----------------------------------------------------|------|-----|------|-----------------------|

|        | t <sub>DLΦ</sub> (WR) | WR Delay From Rising Edge of Clock,<br>WR Low      |      | 80  | nsec |                       |

| WR     | <sup>t</sup> DL⊕(WR)  | WR Delay From Falling Edge of Clock, WR Low        |      | 90  | nsec | C <sub>L</sub> = 50pF |

|        | <sup>t</sup> DHФ(WR)  | WR Delay From Falling Edge of Clock,<br>WR High    |      | 100 | nsec |                       |

|        | t <sub>W(WRL)</sub>   | Pulse Width, WR Low                                | [10] |     | nsec |                       |

| M1     | t <sub>DL(M1)</sub>   | M1 Delay From Rising Edge of Clock<br>M1 Low       |      | 130 | nsec | C <sub>L</sub> = 50pF |

|        | t <sub>DH(M1)</sub>   | M1 Delay From Rising Edge of Clock, M1 High        |      | 130 | nsec | _                     |

| RFSH   | t <sub>DL(RF)</sub>   | RFSH Delay From Rising Edge of Clock,<br>RFSH Low  |      | 180 | nsec | C <sub>1</sub> = 30pF |

|        | t <sub>DH(RF)</sub>   | RFSH Delay From Rising Edge of Clock<br>RFSH High  |      | 150 | nsec |                       |

| WAIT   | t <sub>S(WT)</sub>    | WAIT Setup Time to Falling Edge of Clock           | 70   |     | nsec |                       |

| HALT   | t <sub>D(HT)</sub>    | HALT Delay Time From Falling Edge of Clock         |      | 300 | nsec | C <sub>L</sub> = 50pF |

| ĪNT    | t <sub>s(IT)</sub>    | INT Setup Time to Rising Edge of Clock             | 80   |     | nsec |                       |

| NMI    | t <sub>w(NML)</sub>   | Pulse Width, NMI Low                               | 80   |     | nsec |                       |

| BUSRQ  | t <sub>s(BQ)</sub>    | BUSRQ Setup Time to Rising Edge of Clock           | 80   |     | nsec |                       |

| BUSAK  | t <sub>DL(BA)</sub>   | BUSAK Delay From Rising Edge of Clock, BUSAK Low   |      | 120 | nsec | C <sub>L</sub> = 50pF |

|        | t <sub>DH(BA)</sub>   | BUSAK Delay From Falling Edge of Clock, BUSAK High | 1    | 110 | nsec |                       |

| RESET  | t <sub>s(RS)</sub>    | RESET Setup Time to Rising Edge of Clock           | 90   |     | nsec |                       |

|        | t <sub>F(C)</sub>     | Delay to/from Float (MREQ, IORQ,<br>RD and WRI)    |      | 80  | nsec |                       |

|        | t <sub>mr</sub>       | M1 Stable Prior to IORQ (Interrupt Ack.)           | [11] |     | nsec |                       |

## NOTES:

- A. Data should be enabled onto the CPU data bus when RD is active. During interrupt acknowledge data should be enabled when  $\overline{\text{M1}}$  and  $\overline{\text{IORO}}$  are both

- B. The RESET signal must be active for a minimum of 3 clock cycles.

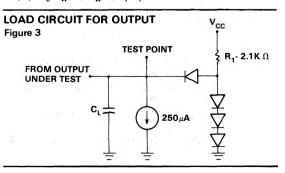

- Output Delay vs. Load Capacitance

$T_A$  = 85°C  $V_{CC}$  = 5V  $\pm$  5%

Add 10 nsec delay for each 50pF increase in load up to a maximum of 200pF for the data bus and 100pF for address and control lines.

- D. Although static by design, testing guarantees  $t_W$  ( $\Phi H$ ) of 200  $\mu sec$  maximum.

- t<sub>acm</sub> = t<sub>w</sub> (ΦH) + t<sub>f</sub> -75 [1]

- [2]

- $t_{aci} = t_c 80$   $t_{ca} = t_w (\Phi L) + t_r 40$ [3]

- [4]  $t_{caf} = t_W (\Phi L) + t_r -60$

- $t_{dcm} = t_{C} 210$   $t_{dci} = t_{W} (\Phi L) + t_{r} 210$ [5]

- [6]

- t<sub>cdf</sub> = t<sub>w</sub> (ΦL) + tr -80 t<sub>w</sub> (MRL) = t<sub>c</sub> -40

- [7] [8]

- $t_W(\overline{MRH}) = t_W(\Phi H) + t_f -70$ [9]

- $t_W(\overline{WR}) = t_C -40$

- [11]  $t_{mr} = 2t_{C} + t_{W} (\Phi H) + t_{f} -80$

- [12]  $t_C = t_W (\Phi H) + t_W (\Phi L) + t_r + t_f$

# **AC ELECTRICAL CHARACTERISTICS**

MKI3880(P)-74 Z80A-CPU ( $T_A = -40^{\circ}\text{C to }85^{\circ}\text{C}$ ,  $V_{CC} = +5\text{V}$ ,  $\pm 5\%$ , Unless Otherwise Noted)

| SIGNAL            | SYM                                                                               | PARAMETER                                                                                                   | MIN               | MAX                       | UNIT                         | TEST CONDITIONS       |

|-------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------------------|---------------------------|------------------------------|-----------------------|

| Ф                 | t <sub>c</sub><br>t <sub>w</sub> (ΦH)<br>t <sub>w</sub> (ΦL)<br>t <sub>r,</sub> f | Clock Period<br>Clock Pulse Width, Clock High<br>Clock Pulse Width, Clock Low<br>Clock Rise and Fall Time   | .25<br>110<br>110 | [12]<br>(D)<br>2000<br>30 | μsec<br>nsec<br>nsec<br>nsec |                       |

|                   | t <sub>D(AD)</sub><br>t <sub>F(AD)</sub><br>t <sub>acm</sub>                      | Address Output Delay Delay to Float Address Stable Prior to MREQ                                            | [1]               | 110<br>90                 | nsec<br>nsec<br>nsec         | C <sub>L</sub> = 50pF |

| A <sub>0-15</sub> | t <sub>aci</sub>                                                                  | (Memory Cycle) Address Stable Prior to IORQ, RD or WR (I/O Cycle)                                           | [2]               |                           | nsec                         |                       |

|                   | t <sub>ca</sub>                                                                   | Address Stable From RD, WR, IORQ or MREQ                                                                    | [3]               |                           | nsec                         | Except T3-M1          |

|                   | t <sub>caf</sub>                                                                  | Address Stable From RD or WR During Float                                                                   | [4]               |                           | nsec                         |                       |

| }                 | t <sub>D(D)</sub> t <sub>F(D)</sub> t <sub>S⊕(D)</sub>                            | Data Output Delay Delay to Float During Write Cycle Data Setup Time to Rising Edge of Clock During M1 Cycle | 35                | 170<br>90                 | nsec<br>nsec<br>nsec         |                       |

| D <sub>0-7</sub>  | t <sub>S</sub> ⊕(D)                                                               | Data Setup Time to Falling Edge at Clock During M2 to M5                                                    | 50                |                           | nsec                         | C <sub>L</sub> = 50pF |

|                   | t <sub>dcm</sub>                                                                  | Data Stable Prior to WR (Memory Cycle)                                                                      | [5]               |                           | nsec                         |                       |

|                   | t <sub>dci</sub><br>t <sub>cdf</sub><br>t <sub>H</sub>                            | Data Stable Prior to WR (I/O Cycle) Data Stable From WR Input Hold Time                                     | [6]<br>[7]<br>O   |                           | nsec<br>nsec<br>nsec         |                       |

|                   | t <sub>DL</sub> ⊕(MR)                                                             | MREQ Delay From Falling Edge of Clock, MREQ Low                                                             | 20                | 85                        | nsec                         |                       |

| MREQ              | t <sub>DHΦ(MR)</sub>                                                              | MREQ Delay From Rising Edge of Clock, MREQ High                                                             |                   | 85                        | nsec                         |                       |

| }                 | t <sub>DH</sub> ⊕(MR)                                                             | MREQ Delay From Falling Edge of Clock, MREQ High                                                            |                   | 85                        | nsec                         | C <sub>L</sub> = 50pF |

|                   | t <sub>w(MRL)</sub>                                                               | Pulse Width, MREQ Low<br>Pulse Width, MREQ High                                                             | [8]<br>[9]        |                           | nsec<br>nsec                 |                       |

|                   | t <sub>DLΦ(IR)</sub>                                                              | IORQ Delay From Rising Edge of<br>Clock, IORQ Low                                                           |                   | 75                        | nsec                         |                       |

| IORQ              | t <sub>DL</sub> ⊕(IR)                                                             | IORQ Delay From Falling Edge of<br>Clock, IORQ Low                                                          |                   | 85                        | nsec                         | C <sub>L</sub> = 50pF |

|                   | t <sub>DH</sub> ⊕(IR)                                                             | IORQ Delay From Rising Edge of<br>Clock, IORQ High                                                          |                   | 85                        | nsec                         |                       |

|                   | t <sub>DHΦ(IR)</sub>                                                              | IORQ Delay From Falling Edge of Clock, IORQ High                                                            |                   | 85                        | nsec                         |                       |

|                   | t <sub>DLΦ(RD)</sub>                                                              | RD Delay From Rising Edge of Clock,                                                                         |                   | 85                        | nsec                         |                       |

| RD                | t <sub>DL</sub> ⊕(RD)                                                             | RD Delay From Falling Edge of Clock, RD Low                                                                 |                   | 95                        | nsec                         | C <sub>L</sub> = 50pF |

|                   | <sup>†</sup> DH⊕(RD)                                                              | RD Delay From Rising Edge of Clock,<br>RD High                                                              |                   | 85                        | nsec                         |                       |

|                   | t <sub>DH</sub> ⊕(RD)                                                             | RD Delay From Falling Edge of Clock,<br>RD High                                                             |                   | 85                        | nsec                         |                       |

# **AC ELECTRICAL CHARACTERISTICS (Cont.)**

( $T_A$  = -40°C to 85°C,  $V_{CC}$  = +5 V,  $\pm$  5%, unless otherwise noted)

| SIGNAL | SYM                  | PARAMETER                                          | MIN  | MAX | UNIT | TEST CONDITIONS       |

|--------|----------------------|----------------------------------------------------|------|-----|------|-----------------------|

|        | <sup>t</sup> DLΦ(WR) | WR Delay From Rising Edge of Clock, WR Low         |      | 65  | nsec |                       |

| WR     | t <sub>DLΦ(WR)</sub> | WR Delay From Falling Edge of Clock, WR Low        |      | 80  | nsec | C <sub>L</sub> = 50pF |

|        | t <sub>DHΦ(WR)</sub> | WR Delay From Falling Edge of Clock, WR High       |      | 80  | nsec |                       |

|        | t <sub>w(WRL)</sub>  | Pulse Width, WR Low                                | [10] |     | nsec |                       |

| M1     | t <sub>DL(M1)</sub>  | M1 Delay From Rising Edge of Clock M1 Low          |      | 100 | nsec | C <sub>1</sub> = 50pF |

|        | t <sub>DH(M1)</sub>  | M1 Delay From Rising Edge of Clock, M1 High        |      | 100 | nsec |                       |

| RFSH   | t <sub>DL(RF)</sub>  | RFSH Delay From Rising Edge of Clock,              |      | 130 | nsec | C <sub>1</sub> = 50pF |

|        | t <sub>DH(RF)</sub>  | RFSH Delay From Rising Edge of Clock<br>RFSH High  |      | 120 | nsec |                       |

| WAIT   | t <sub>S(WT)</sub>   | WAIT Setup Time to Falling Edge of Clock           | 70   |     | nsec |                       |

| HALT   | t <sub>D(HT)</sub>   | HALT Delay Time From Falling Edge of Clock         |      | 300 | nsec | C <sub>L</sub> = 50pF |

| INT    | t <sub>s(IT)</sub>   | INT Setup Time to Rising Edge of Clock             | 80   |     | nsec |                       |

| NMI    | t <sub>w(NML)</sub>  | Pulse Width, NMI Low                               | 80   |     | nsec |                       |

| BUSRO  | t <sub>s(BQ)</sub>   | BUSRQ Setup Time to Rising Edge of Clock           | 50   |     | nsec |                       |

| BUSAK  | t <sub>DL(BA)</sub>  | BUSAK Delay From Rising Edge of Clock, BUSAK Low   |      | 100 | nsec | C <sub>1</sub> = 50pF |

|        | t <sub>DH(BA)</sub>  | BUSAK Delay From Falling Edge of Clock, BUSAK High |      | 100 | nsec |                       |

| RESET  | t <sub>s(RS)</sub>   | RESET Setup Time to Rising Edge of Clock           | 60   |     | nsec |                       |

|        | t <sub>F(C)</sub>    | Delay to∕From Float (MREQ, IORQ,<br>RD and WR)     |      | 80  | nsec |                       |

|        | t <sub>mr</sub>      | M1 Stable Prior to IORQ (Interrupt Ack.)           | [11] |     | nsec |                       |

NOTES:

- A Data should be enabled onto the CPU data bus when RD is active. During interrupt acknowledge data should be enabled when M1 and IORQ are both active.

- B. The RESET signal must be active for a minimum of 3 clock cycles.

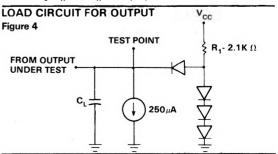

- C. Output Delay vs. Load Capacitance

$T_A = 85^{\circ}C \ V_{CC} = 5V \pm 5\%$

Add 10 nsec delay for each 50pF increase in load up to a maximum of 200pF for the data bus and 100pF for address and control lines.

- D. Although static by design, testing guarantees  $t_{\mathbf{W}}$  ( $\Phi H$ ) of 200  $\mu sec$  maximum.

- [1] tacm = tw (4H) + tf -65

- [2] taci = t<sub>c</sub> -70

- $t_{ca} = t_W (\Phi L) + t_r -50$ [3]

- [4]  $t_{caf} = t_W (\Phi L) + t_r - 45$

- [5]

- t<sub>dcm</sub> = t<sub>c</sub> -170 t<sub>dci</sub> = t<sub>w</sub> (ΦL) + t<sub>r</sub> -170 [6]

- $t_{\text{cdf}} = t_{\text{W}} (\Phi L) + t_{\text{r}} 70$   $t_{\text{W}} (\overline{\text{MRL}}) = t_{\text{c}} 30$ [7] [8]

- $t_{W}(\overline{MRH}) = t_{W}(\Phi H) + t_{f} -40$

$t_W(\overline{WR}) = t_C -30$

[11]  $t_{mr} = 2t_{c} + t_{w} (\Phi H) + t_{f} - 65$

$t_C = t_W (\Phi H) + t_W (\Phi L) + t_r + t_f$ [12]

| SYM              | PARAMETER          | MAX | UNIT | TEST CONDITIONS    |

|------------------|--------------------|-----|------|--------------------|

| СФ               | Clock Capacitance  | 35  | pF   | Unmeasured Pins    |

| C <sub>IN</sub>  | Input Capacitance  | 5   | pF   | Returned to Ground |

| C <sub>OUT</sub> | Output Capacitance | 10  | pF   |                    |

# MKI INDUSTRIAL HI-REL SCREENING Figure 6

|                             | Screen                                                     | MIL-STD 883 Method                                                                                                                                                   | Regmt.                          |

|-----------------------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Package Assembly            | Die Inspect<br>Pre-Seal Inspect                            | 75X Mostek Spec.<br>30X-60X Mostek Spec.                                                                                                                             | 100%<br>100%                    |

| Environmental               | Temperature Cycle<br>Centrifuge<br>Fine Leak<br>Gross Leak | 1010 Cond. C, 5 Cycles<br>2001 Cond. D, 20Kg Y <sub>1</sub><br>1014 Cond. B, 1 X 10 <sup>-7</sup> atm cc/sec<br>Mostek Spec.                                         | 100%<br>100%<br>100%<br>100%    |

| Electrical                  | Electrical Screens                                         | 5005 Grp. A electrical sub-groups, testing conditions and limits which guarantee ac, dc and functional performance over the full temperature range.                  | 100%                            |

| Voltage Stress (DRAMs only) | 1                                                          | 1015 Cond. D, 10 hrs. min., 125°C                                                                                                                                    | 100%                            |

| Burn-in                     |                                                            | 1015 Cond. D, 44 hrs. min., 125°C                                                                                                                                    | 100%                            |

| QA Acceptance               | Hermeticity Electrical Tests Visual/Mechanical             | Fine and gross leak samples 5005 Grp. A sample testing to guarantee performance to data sheet over full temp. range. Visual tests to guarantee marking, construction | .25% AQI<br>.4% AQL<br>.65% AQI |

|                             | Solderability Pre-shipment Inspect.                        | and mechanical integrity                                                                                                                                             | LTPD 10<br>.65% AQI             |