# MK 5009 P MK 5009 N

# **MOS Counter Time-Base Circuit**

# MOSTEK

- Ion-implanted for full TTL/DTL compatibility

- □ Internal clock operates from:

External signal External RC network External crystal

- ☐ Operates DC to above 1 MHz

- ☐ Binary-encoded for frequency selection

#### **DESCRIPTION**

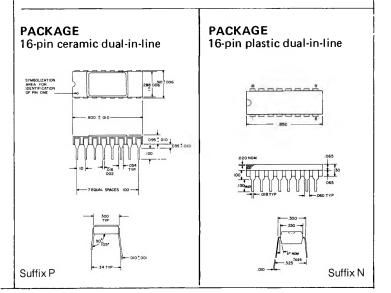

The MK 5009 P is a highly versatile MOS oscillator and di-vider chain manufactured by Mostek using its depletionload, ion-implantation process and P. - channel technology. The 16-pin DIP package provides frequency division ranges from 1 to 36×108. The circuit will operate from any of three frequency sources: the internal oscillator with an external RC combination; the internal oscillator with an external crystal; or with an externally-applied TTL signal. Control inputs provide additional versatility and allow the circuit to be used in a variety of applications including instruments, timers, and clocks,

With an input frequency of 1

MHz, the MK 5009 P provides the basic time periods necessary for most frequency measuring instruments, i.e., 1  $\mu$ s through 100 seconds. Oneminute, ten-minute, and oneclocks.

selected counter division, and by the oscillator frequency or external input. The falling edge of the output square wave should be used to control external gating circuitry.

hour periods are also available using a 1 MHz input. Using a 1/1.2 MHz input, the MK 5009 P can also provide a 50/60 Hz output for accurate generation of line frequencies in portable instruments or The time-base output (TIME OUT) is a square wave, its frequency determined by the

Special Products

#### TIME OUT

| ADD | <b>ADDRESS INPUTS</b> |     |     | WITHOUT RESET             | RES                                      | SET                                      | BYPASS MODES (see page 3)                                                                                                        |                                                                                                              |                                                                                                                                            |  |  |  |  |

|-----|-----------------------|-----|-----|---------------------------|------------------------------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 23  | 22                    | 21  | 20  | $R_{MAX} = 0$ $R_{O} = 0$ | Reset Max.<br>$R_{MAX} = 1$<br>$R_0 = 0$ | Reset Min.<br>$R_{MAX} = 0$<br>$R_0 = 1$ | $\begin{array}{c} \text{Mode 1} \\ \text{R}_{\text{MAX}} &= \text{V}_{\text{GG}} \\ \text{R}_{\text{O}} &= \text{0} \end{array}$ | $\begin{array}{ccc} & \text{Mode 2} \\ & R_{\text{MAX}} &= 0 \\ & R_{\text{O}} &= V_{\text{GG}} \end{array}$ | $\begin{array}{c} \text{Mode 3} \\ \text{R}_{\text{MAX}} = \text{V}_{\text{GG}} \\ \text{R}_{\text{O}} = \text{V}_{\text{GG}} \end{array}$ |  |  |  |  |

| 0   | 0                     | 0   | 0   | ÷ 10°                     | - <u>⊹</u> 10⁰                           | ÷ 10°                                    | ÷ 10°                                                                                                                            | ÷ 10°                                                                                                        | ÷ 10°                                                                                                                                      |  |  |  |  |

| 0   | 0                     | 0   | 1   | ÷ 10'                     |                                          |                                          | ÷ 10¹                                                                                                                            | ÷ 10¹                                                                                                        | ÷ 10¹                                                                                                                                      |  |  |  |  |

| \ o | 0                     | 1   | 0   | ÷ 10 <sup>2</sup>         | Resets                                   | Resets                                   | ÷ 10²                                                                                                                            | ÷ 10²                                                                                                        | ÷ 10 <sup>2</sup>                                                                                                                          |  |  |  |  |

| 0   | 0                     | 1   | 1   | ÷ 10³                     |                                          |                                          | ÷ 10³                                                                                                                            | ÷ 10³                                                                                                        | ÷ 10³                                                                                                                                      |  |  |  |  |

| 0   | 1                     | 0   | 0   | ÷ 10⁴                     | Counters                                 | Counters                                 | ÷ 10⁴                                                                                                                            | ÷ 10⁴                                                                                                        | ÷ 10 <sup>4</sup>                                                                                                                          |  |  |  |  |

| 0   | 1                     | 0   | 1   | ÷ 10 <sup>5</sup>         |                                          |                                          | ÷ 10²                                                                                                                            | ÷ 10 <sup>5</sup>                                                                                            | ÷ 10 <sup>2</sup>                                                                                                                          |  |  |  |  |

| 0   | 1                     | 1   | 0   | ÷ 10 <sup>6</sup>         | to their                                 | to their                                 | ÷ 10³                                                                                                                            | ÷ 10 <sup>6</sup>                                                                                            | ÷ 10³                                                                                                                                      |  |  |  |  |

| 0   | 1                     | 1   | 1   | ÷ 10 <sup>7</sup>         | ı                                        | 1                                        | ÷ 10 <sup>4</sup>                                                                                                                | ÷ 10 <sup>7</sup>                                                                                            | ÷ 10⁴                                                                                                                                      |  |  |  |  |

| 1   | 0                     | 0   | 0   | ÷ 10 <sup>8</sup>         | Highest                                  | Lowest                                   | ÷ 10 <sup>5</sup>                                                                                                                | ÷ 10 <sup>5</sup>                                                                                            | ÷ 10²                                                                                                                                      |  |  |  |  |

| 1   | 0                     | 0   | 1   | ÷ 6 × 10 <sup>7</sup>     |                                          |                                          | ÷ 6 × 104                                                                                                                        | ÷ 6 × 10⁴                                                                                                    | ÷ 6 × 10¹                                                                                                                                  |  |  |  |  |

| 1   | 0                     | 1   | 0   | ÷ 36 × 10 <sup>8</sup>    | States                                   | States                                   | ÷ 36 × 10 <sup>5</sup>                                                                                                           | ÷ 36 × 10 <sup>5</sup>                                                                                       | ÷ 36 × 10 <sup>2</sup>                                                                                                                     |  |  |  |  |

| 1   | 0                     | - 1 | 1   | ÷ 6 × 10 <sup>8</sup>     |                                          |                                          | ÷ 6 × 10 <sup>5</sup>                                                                                                            | ÷ 6 × 10 <sup>5</sup>                                                                                        | ÷ 6 × 10 <sup>2</sup>                                                                                                                      |  |  |  |  |

| Ì   |                       | *   |     | _                         |                                          |                                          | _                                                                                                                                | _                                                                                                            | _                                                                                                                                          |  |  |  |  |

| 1   | 1                     | 1   | 0   | ÷ 2 × 10⁴                 |                                          |                                          | ÷ 2 × 101                                                                                                                        | ÷ 2 × 10 <sup>1</sup>                                                                                        | ÷ 2 × 10¹                                                                                                                                  |  |  |  |  |

| 1   | _1_                   | _1_ | _ 1 | Ext. In.                  | Ext. In.                                 | Ext. In.                                 | Ext. Int.                                                                                                                        | Ext. Int.                                                                                                    | Ext. Int.                                                                                                                                  |  |  |  |  |

<sup>\*</sup>Addresses 1100 and 1101 result in Logic 0 at the output regardless of the state of the Reset Max, and Reset 0 inputs.

Logic  $1 = High = V_{SS}$

Logic  $0 = Low = V_{DD}$

#### **ABSOLUTE MAXIMUM RATINGS**

| Voltage on Any Terminal Relative to Vss. |   |   |  |  |  |  |  |   | + 0.3V to $- 20V$                     |

|------------------------------------------|---|---|--|--|--|--|--|---|---------------------------------------|

| Operating Temperature Range (Ambient)    |   |   |  |  |  |  |  |   | . $0^{\circ}$ C to $+70^{\circ}$ C    |

| Storage Temperature Range (Ambient)      | _ | _ |  |  |  |  |  | _ | $55^{\circ}$ C to $\pm 150^{\circ}$ C |

# RECOMMENDED OPERATING CONDITIONS

$\rm (0^{\circ}C \leq T_A \leq 70^{\circ}C)$

|                   | PARAMETER                                | MIN                  | TYP      | MAX                   | UNITS     | NOTES  |

|-------------------|------------------------------------------|----------------------|----------|-----------------------|-----------|--------|

| Vss               | Supply Voltage                           | + 4.5                |          | + 5.5                 | ٧         |        |

| V <sub>DD</sub>   | Supply Voltage                           | 0.0                  |          | 0.0                   | V         |        |

| ٧ <sub>ee</sub>   | Supply Voltage                           | - 9.6                |          | - 14.4                | V         |        |

| f <sub>XTAL</sub> | Crystal Frequency                        | 0.1                  |          | 2.0                   | MHz       |        |

| f <sub>RC</sub>   | RC Frequency                             | DC                   |          | 200                   | kHz       |        |

| f <sub>EXT</sub>  | External Frequency                       | DC                   |          | 2.0                   | MHz       |        |

| tpL               | Logic 0 Pulse Width, CLAMP               | _                    |          |                       |           | Note 5 |

|                   | Ext. Input                               | 200                  |          |                       | nsec      |        |

| t <sub>PH</sub>   | Logic 1 Pulse Width, Ext. Input          | 200                  |          |                       | nsec      |        |

| 1                 | Reset Max                                | 10.0                 |          |                       | μsec      |        |

|                   | Reset 0                                  | 10.0                 |          |                       | μsec      |        |

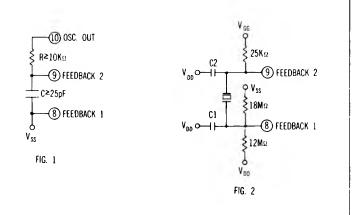

| R                 | Feedback Resistance                      | .01                  |          | 2.5                   | $M\Omega$ | Fig. 1 |

| VIL               | Input Voltage, Logic 0, Reset Inputs     | 0.0                  |          | 0.8                   | V         |        |

|                   | Reset (Bypass Mode)                      | Vee                  |          | V <sub>GG</sub> + 1.0 | V         | Note 2 |

|                   | All Other Logic Inputs                   |                      |          | 0.8                   | V         |        |

| V <sub>IH</sub>   | Input Voltage, Logic 1, All Logic Inputs | V <sub>ss</sub> -1.0 | $V_{ss}$ | $V_{ss} + 0.3$        | V         |        |

Special Products

# **ELECTRICAL CHARACTERISTICS**

'( $V_{SS} = +5V \pm 10\%$ ;  $V_{DD} = 0$  V;  $V_{GG} = -12.0$  V  $\pm 20\%$ ;  $0^{\circ}$  C  $\leq T_A \leq 70^{\circ}$  C)

|                                    | PARAMETER                                                                               | MIN | TYP†                | MAX          | UNITS       | NOTES                                                    |

|------------------------------------|-----------------------------------------------------------------------------------------|-----|---------------------|--------------|-------------|----------------------------------------------------------|

| I <sub>ss</sub><br>I <sub>GG</sub> | Supply Current, V <sub>ss</sub><br>Supply Current, V <sub>GG</sub>                      |     | 6.0<br>6.0          | 11.0<br>11.0 | mA<br>mA    | Note 1                                                   |

| l <sub>iL</sub>                    | Input Current, Logic 0                                                                  |     |                     | - 1.6        | mA          | Note 2;<br>V <sub>I</sub> = 0.4V                         |

| V <sub>OL</sub>                    | Output Voltage, Logic 0<br>Output Voltage, Logic 1                                      | 2.4 |                     | 0.4          | V           | $I_{OL} = 1.6 \text{mA}^*$ $I_{OH} = -40 \mu \text{A}^*$ |

| f <sub>STA</sub>                   | Frequency Stability w/ Volt. Change, RC Mode<br>/ Temp. Change, RC Mode<br>Crystal Mode |     | ± 3.0<br>- 0.2<br>— |              | %/V<br>%/°C | Note 3<br>Note 4                                         |

| t <sub>e e</sub>                   | Jitter, Edge-to-Edge Variation                                                          |     | <15                 |              | nsec        | Temp. & Sup-<br>ply Voltage<br>Constant                  |

$<sup>\</sup>dagger$ Typical values at Vss = +5V, VDD = 0V, VGG = -12V, and TA = 25°C

<sup>1.</sup> Logic inputs at Vss. output open circuited. Each logic input (see Note 2) contributes an additional 1.6 mA (max.) to Iss when at logic 0.

<sup>2.</sup> Logic Inputs are: Reset Max; Reset 0; Address Inputs; Ext. Input; Ext/Int Select; and Clamp.

<sup>3.</sup> Frequency variations due to power supply changes only.

<sup>4.</sup> Crystal mode stability is dependent upon crystal.

<sup>5.</sup> Minimum logic 0 time at clamp input is 50% of oscillator period.

<sup>\*</sup>Vox, VoL apply only to Time Out.

## **DESCRIPTION OF OPERATION**

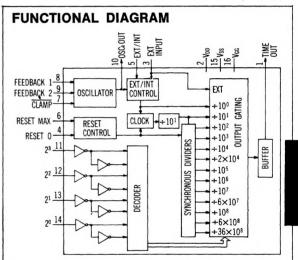

The MK 5009 P consists basically of a series of counters, selectable via an internal multiplexer. The  $\div$  10¹ counter output is used to generate an internal clock signal for the 10² through  $36\times10^8$  counter stages, which are fully synchronous with each other.

#### **OSCILLATOR CONTROLS**

Operation in the RC oscillator mode is achieved as shown in Figure 1. Frequency, f, is approximately 0.8/RC. The clamp circuit can be used in the RC mode to provide one-shot or accurate start-up operations. When Clamp goes to a logic 0, the internal circuitry is held at a reference level so that upon release of the Clamp (return to logic 1), the oscillator's first cycle will be a full cycle.

The crystal oscillator mode is shown in Figure 2. Values for the resistors are chosen to bias the internal circuitry for optimum performance. The two capacitors are chosen to provide the loading capacitance ( $C_L$ ) specified for the selected crystal. It is recommended that  $C1 = C2 = 2 C_L$ .

#### **RESET/BYPASS CONTROLS**

The MK 5009 P provides two different reset conditions. A positive-going pulse of 10 µs or longer on Reset 0 will reset counters to their lowest state, while a positive-going pulse at Reset Max will reset counters to their highest state. The Reset Max control enables the user to set up the counters to provide a falling edge at the next oscillator cycle or negative-going external input, regardless of which divider chain is selected.

In addition, taking one or both Reset Inputs to the most negative voltage,  $V_{\text{Ge}}$ , allows bypassing portions of the divider chain for testing or other purposes (see table on page 1).

#### EXTERNAL/INTERNAL FREQUENCY SOURCE

When using an external signal source to operate the MK 5009 P, that signal should be applied at the External Input (Pin 3), and the External/Internal Select (Pin 5) should be brought to logic 1.

For operation with an internal signal, the External/Internal Select should be at logic 0.

#### **OSCILLATOR OUTPUT**

The oscillator output, provided at Pin 10, is not a true logic output, but may be used to drive a high impedance device such as a junction FET or other MOS circuitry.

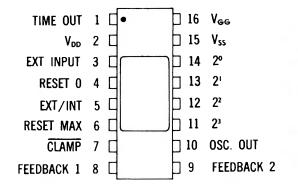

# **PIN CONNECTIONS**

Special Products

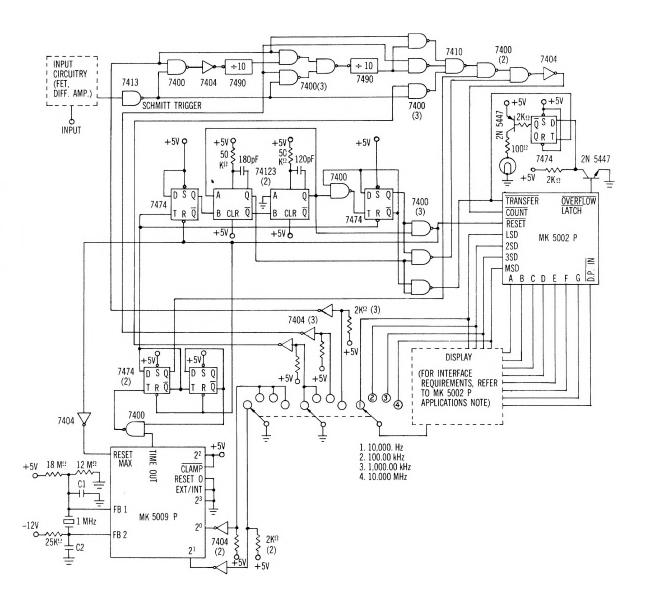

### **APPLICATION** — 10 MHz Frequency Counter

The circuit shown below is a frequency counter capable of counting input rates up to 10 MHz, selected in four ranges. The MK 5009 P provides the time base intervals while the Mostek MK 5002 P counter circuit provides counting, storage, and display functions. Two decades of prescaling using TTL are employed. TTL one-shots provide proper timing for the 5002.

To replace the functions of the MK 5009 P, an active device and Schmitt trigger for the crystal oscillator would be needed, plus six 7490's to achieve the correct time out. Replacing the functions of the MK 5002 would require four 7490's, four 7475's, and four BCD-to-seven-segment decoders.