## MK45264/45265(N) -55/70

# (64 x 5) x 2 CMOS BIDERECTIONAL BIPORT FIFO/TRANSCEIVER

- DUAL 64 x 5 FIFOS PLUS A '245-TYPE TRANSCEIVER FUNCTION

- FULLY ASYNCHRONOUS DUAL PORT OPERATION

- EMPTY, FULL. ALMOST FULL AND ALMOST EMPTY STATUS FLAGS

- SPARE BITS FOR PARITY AND BEGIN-NING/END-OF-MESSAGE FLAGS

- ± 12mA OUTPUT DRIVE CAPABILITY

- DUAL V<sub>CC</sub> AND V<sub>SS</sub> FOR IMPROVED MARGIN AND DRIVE

- 300 MIL DIP PACKAGE

- APPLICATION : ARBITRATION-FREE μP-TOμP MESSAGE PASSING

| Part No     | Access<br>Time | Cycle Time | Cycle Rate |

|-------------|----------------|------------|------------|

| MK45264N-55 | 55ns           | 75ns       | 13.3MHz    |

| MK45265N-55 | 55ns           | 75ns       | 13.3MHz    |

| MK45264N-70 | 70ns           | 95ns       | 10.5MHz    |

| MK45265N-70 | 70ns           | 95ns       | 10.5MHz    |

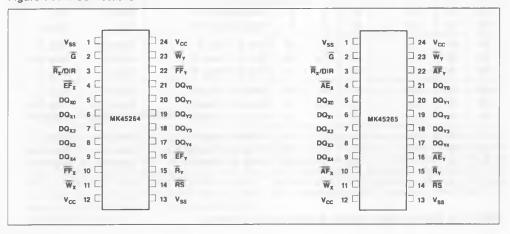

## **PIN NAMES**

| V <sub>CC</sub> , V <sub>SS</sub>  | + 5V, GND                                               |

|------------------------------------|---------------------------------------------------------|

| DQ <sub>X0</sub> -DQ <sub>X4</sub> | X Port Data I/O                                         |

| DQ <sub>Y0</sub> -DQ <sub>Y4</sub> | Y Port Data I/O                                         |

| W <sub>X</sub> , W <sub>Y</sub>    | X & Y Port Write Enables                                |

| R <sub>X</sub> /DIR                | X Port Read Enable and<br>Transceiver Direction Control |

| G                                  | Transceiver Enable                                      |

| Ry                                 | Y Port Read Enable                                      |

| RS                                 | Master Reset                                            |

| EF <sub>X</sub> , FF <sub>Y</sub>  | Y-to-X FIFO Empty/full Flag                             |

| EF <sub>Y</sub> , FF <sub>X</sub>  | X-to-Y FIFO Empty/full Flag                             |

| AE <sub>Y</sub> AF <sub>X</sub>    | X-to-Y FIFO Almost Empty/full                           |

| AE <sub>X</sub> , AF <sub>Y</sub>  | Y-to-X FIFO Almost Empty/full                           |

Figure 1: Pin Connections.

FIGURE 2. DEVICE LOGIC SYMBOL

## TRUTH TABLE

| RS             | G              | R <sub>X</sub> /DIR | $\overline{W_X}$ | R <sub>Y</sub> | $\overline{W_Y}$ | MODE                                                     | DQ <sub>X</sub>                  | DQ <sub>Y</sub>               |

|----------------|----------------|---------------------|------------------|----------------|------------------|----------------------------------------------------------|----------------------------------|-------------------------------|

| Lo             | X              | X                   | X                | Х              | Х                | Master Reset                                             | High Z                           | High Z                        |

| Hi<br>Hi       | Lo<br>Lo       | Hi<br>Lo            | X                | X              | X                | Transparent X-Y Transparent Y-X                          | Data In<br>DQ <sub>Y</sub>       | DQ <sub>X</sub><br>Data In    |

| Hi<br>Hi<br>Hi | Hi<br>Hi<br>Hi | Hi<br>Hi<br>Hi      | Hi<br>Hi<br>Hi   | Hi<br>Lo<br>X  | Hi<br>Hi<br>Lo   | Sby X / Sby Y<br>Sby X / Read Y<br>Sby X / Write Y       | High Z<br>High Z<br>High Z       | High Z<br>Data Out<br>Data In |

| Hi<br>Hi<br>Hi | Hi<br>Hi<br>Hi | Lo<br>Lo<br>Lo      | Hi<br>Hi<br>Hi   | Hi<br>Lo<br>X  | Hi<br>Hi<br>Lo   | Read X / Sby Y Read X / Read Y Read X / Write Y          | Data Out<br>Data Out<br>Data Out | High Z<br>Data Out<br>Data In |

| Hi<br>Hi<br>Hi | Hi<br>Hi<br>Hi | X<br>X<br>X         | Lo<br>Lo         | Hi<br>Lo<br>X  | Hi<br>Hi<br>Lo   | Write X / Sby Y<br>Write X / Read Y<br>Write X / Write Y | Data In<br>Data In<br>Data In    | High Z<br>Data Out<br>Data In |

X = Don't Care

NOTE: Truth Table logic states presume all status flags to be inactive.

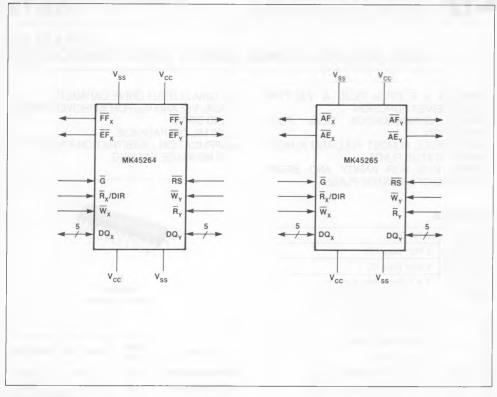

#### FIGURE 3. BLOCK DIAGRAM

#### DEVICE APPLICATION/FUNCTION

The MK45264/65 contains two independent single direction FIFOs, and a bidirectional transceiver, connected via two internal three state busses to I/O drive circuits. One FIFO is pointed X-to-Y, and the other pointed Y-to-X. Either port's FIFOs can be read or written asynchronous with FIFO read or write operations on the other port. The transceiver is activated with a low on G.

Once the transceiver is activated, direction is controlled by the  $R_X/DIR$  pin. A high on  $R_X/DIR$  points the transceiver X-to-Y; a low points it Y-to-X. A low on  $\overline{G}$  disables FIFO operations. Activating the Transceiver during FIFO operations may result in invalid or unpredictable FIFO operation.

## AC ELECTRICAL CHARACTERISTICS

(T<sub>A</sub> = 0° to 70°C, V<sub>CC</sub> = 5.0  $\pm$ 10%)

| ALT.             | STD.                 |                                  |     | 5   | 7   | 70  |       |       |

|------------------|----------------------|----------------------------------|-----|-----|-----|-----|-------|-------|

| SYMBOL           | SYMBOL               | PARAMETER                        | MIN | MAX | MIN | MAX | UNITS | NOTES |

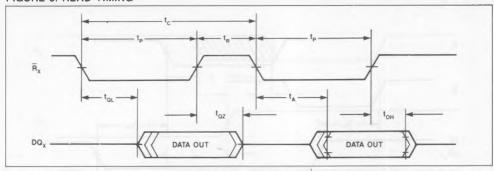

| tp               | t <sub>RL-RH</sub>   | Read Pulse Width                 | 55  |     | 70  |     | ns    |       |

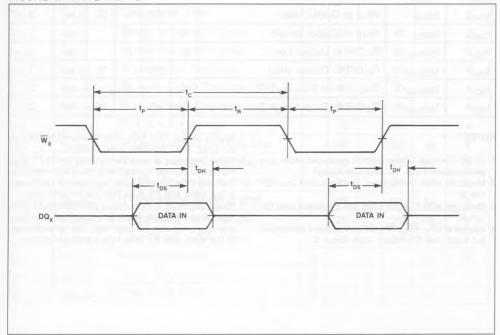

| t <sub>P</sub>   | t <sub>WL-WH</sub>   | Write Pulse Width                | 55  |     | 70  |     | ns    |       |

| tp               | t <sub>GH-RH</sub>   | X-ceiver Disable to end of Read  | 55  |     | 70  |     | ns    |       |

| tp               | t <sub>GH-WH</sub>   | X-ceiver Disable to end of Write | 55  |     | 70  |     | ns    |       |

| t <sub>R</sub>   | t <sub>RH-RL</sub>   | Read Recovery Time               | 20  |     | 25  |     | ns    |       |

| t <sub>R</sub>   | t <sub>WH-WL</sub>   | Write Recovery Time              | 20  |     | 25  |     | ns    |       |

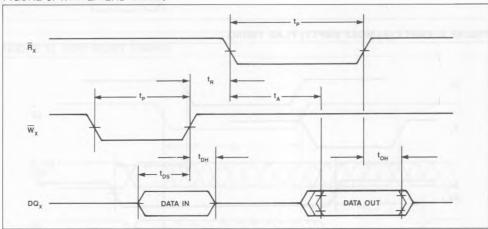

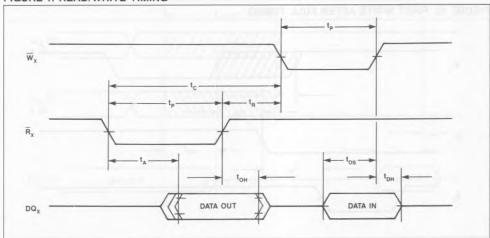

| t <sub>R</sub>   | t <sub>RH-WL</sub>   | Read Write Recovery Time         | 20  |     | 25  |     | ns    |       |

| t <sub>A</sub>   | t <sub>WH-RL</sub>   | Write Read Recovery Time         | 20  |     | 25  |     | ns    |       |

| t <sub>C</sub>   | t <sub>RL-RL</sub>   | Read Cycle Time                  | 75  |     | 95  |     | ns    |       |

| t <sub>C</sub>   | t <sub>WL-WL</sub>   | Write Cycle Time                 | 75  |     | 95  |     | ns    |       |

| t <sub>DS</sub>  | t <sub>DV-WH</sub>   | Data Set Up Time                 | 20  |     | 25  |     | ns    |       |

| t <sub>DH</sub>  | t <sub>wh-Dx</sub>   | Data Hold Time                   | 5   |     | 5   |     | ns    |       |

| t <sub>QL</sub>  | t <sub>RL-QL</sub>   | R Low to Outputs Low-Z           | 5   |     | 5   |     | ns    | 2     |

| t <sub>A</sub>   | t <sub>RL-QV</sub>   | Read Access Time                 |     | 55  |     | 70  | ns    | 3     |

| t <sub>OH</sub>  | t <sub>RH-QX</sub>   | Output Hold Time                 | 5   |     | 5   |     | ns    | 3     |

| t <sub>OH</sub>  | t <sub>WL-QX</sub>   | Output Hold Time                 | 5   |     | 5   |     | ns    | 3     |

| t <sub>QZ</sub>  | t <sub>RH-QZ</sub>   | R High to Outputs High-Z         |     | 30  |     | 40  | ns    | 2     |

| twoz             | t <sub>WL-QZ</sub>   | W Low to Outputs High-Z          |     | 45  |     | 55  | ns    | 2     |

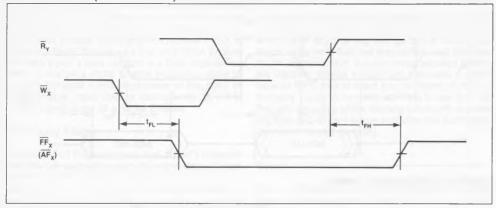

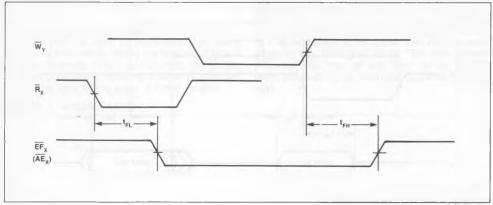

| t <sub>FL1</sub> | t <sub>WL-FFL</sub>  | W Low to Full Flag Low           |     | 60  |     | 80  | ns    | 4     |

| t <sub>FL1</sub> | t <sub>RL-EFL</sub>  | R Low to Empty Flag Low          |     | 60  |     | 80  | ns    | 4     |

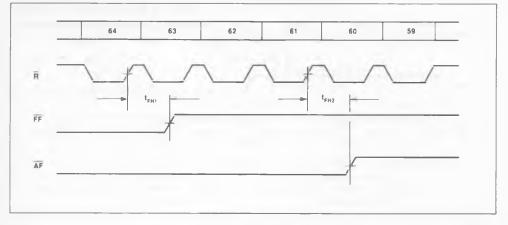

| t <sub>FH1</sub> | t <sub>WH-EFH</sub>  | W Hi to Empty Flag High          |     | 50  |     | 65  | ns    | 4     |

| t <sub>FH1</sub> | t <sub>RH-FFH</sub>  | R Hi to Full Flag High           |     | 50  |     | 65  | ns    | 4     |

| t <sub>FL2</sub> | t <sub>WL-AFL</sub>  | W Low to Almost Full Flag Low    |     | 60  |     | 80  | ns    | 5     |

| t <sub>FL2</sub> | t <sub>RL-AEL</sub>  | R Low to Almost Empty Flag Low   |     | 60  |     | 80  | ns    | 5     |

| t <sub>FH2</sub> | t <sub>WH-AEH</sub>  | W Hi to Almost Empty Flag High   |     | 75  |     | 95  | ns    | 5     |

| t <sub>FH2</sub> | t <sub>RH-AFH</sub>  | R Hi to Almost Full Flag High    |     | 75  |     | 95  | ns    | 5     |

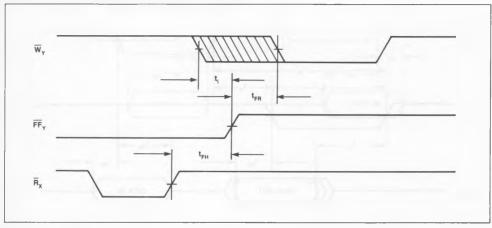

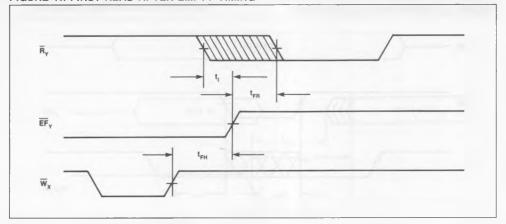

| tı               | t <sub>WL-FFH</sub>  | Write Protect Indeterminate      |     | 25  |     | 30  | ns    | 6     |

| tı               | t <sub>RL-EFH</sub>  | Read Protect Indeterminate       |     | 25  |     | 30  | ns    | 7     |

| t <sub>FR</sub>  | t <sub>FFH-WL</sub>  | Full Flag Recovery               | 0   |     | 0   |     | ns    | 6     |

| t <sub>FR</sub>  | t <sub>EFH-AL</sub>  | Empty Flag Recovery              | 0   |     | 0   |     | ns    | 7     |

| t <sub>RS</sub>  | t <sub>RSL-RSH</sub> | Reset Pulse Width                | 55  |     | 70  |     | ns    |       |

## AC ELECTRICAL CHARACTERISTICS

$(T_A = 0^{\circ} \text{ to } 70^{\circ}\text{C}, V_{CC} = 5.0 \pm 10\%)$

| ALT.              | STD.                 | PARAMETER                             |      | 55  | 70  |     |       |       |

|-------------------|----------------------|---------------------------------------|------|-----|-----|-----|-------|-------|

| SYMBOL            | SYMBOL               |                                       |      | MAX | MIN | MAX | UNITS | NOTES |

| t <sub>RSR</sub>  | t <sub>RSH-WH</sub>  | Reset Recovery Time                   | _ 75 |     | 95  |     | ns    |       |

| t <sub>RFV</sub>  | t <sub>RSL-FFH</sub> | Reset to Full Flag Valid              |      | 70  |     | 90  | ns    | 3     |

| t <sub>RFV</sub>  | tast-AFH             | Reset to AF Flag Valid                |      | 70  |     | 90  | ns    | 3     |

| t <sub>RFV</sub>  | t <sub>RSL-EFL</sub> | Reset to Empty Flag Valid             |      | 70  |     | 90  | ns    | 3     |

| t <sub>RFV</sub>  | t <sub>RSL-AEL</sub> | Reset to AE Flag Valid                |      | 70  |     | 90  | ns    | 3     |

| t <sub>RQX</sub>  | t <sub>RSL-QX</sub>  | Outout Hold from RS Low               | 0    |     | 0   |     | ns    | 3     |

| t <sub>RQZ</sub>  | t <sub>RSL-QZ</sub>  | RS Low to Output High Z               |      | 40  |     | 50  | ns    | 2     |

| t <sub>FG</sub>   | t <sub>WH-GL</sub>   | FIFO Mode to X-ceiver Mode            | 0    |     | 0   |     | ns    |       |

| t <sub>FG</sub>   | t <sub>RH-GL</sub>   | FIFO Mode to X-ceiver Mode            | 0    |     | 0   |     | ns    |       |

| t <sub>GF</sub>   | t <sub>GH-WL</sub>   | X-ceiver Mode to FIFO Mode            | 5    |     | 5   |     | ns    |       |

| t <sub>GF</sub>   | t <sub>GH-RL</sub>   | X-ceiver Mode to FIFO Mode            | 5    |     | 5   |     | ns    |       |

| t <sub>GQL</sub>  | t <sub>GL-QL</sub>   | G to Output Low Z                     | 0    |     | 0   |     | ns    | 2     |

| t <sub>GQV</sub>  | t <sub>GL-QV</sub>   | G to Output Valid                     |      | 75  |     | 95  | ns    | 3     |

| t <sub>GQX</sub>  | t <sub>GH-QX</sub>   | Output Hold from G                    | 0    |     | 0   |     | ns    | 3     |

| t <sub>GQZ</sub>  | t <sub>GH-QZ</sub>   | G to Output High Z                    |      | 40  |     | 50  | ns    | 2     |

| t <sub>DVQV</sub> | t <sub>DV-QV</sub>   | Input to Output Valid                 |      | 55  |     | 70  | ns    | 3     |

| t <sub>DXQX</sub> | t <sub>DX-QX</sub>   | Input to Output Invalid               | 10   |     | 10  |     | ns    | 3     |

| t <sub>DQL</sub>  | t <sub>DIRV-QL</sub> | R <sub>X</sub> /DIR to Output Low Z   | 0    |     | 0   |     | ns    | 2     |

| t <sub>DQV</sub>  | t <sub>DIRV-QV</sub> | R <sub>X</sub> /DIR to Output Valid   |      | 55  |     | 70  | ns    | 3     |

| t <sub>DQX</sub>  | t <sub>DIRV-QX</sub> | Output Hold from $\overline{R}_X/DIR$ | 0    |     | 0   |     | ns    | 3     |

| t <sub>DQZ</sub>  | t <sub>DIRV-QZ</sub> | R <sub>X</sub> /DIR to Output High Z  |      | 40  |     | 50  | ns    | 2     |

#### **NOTES**

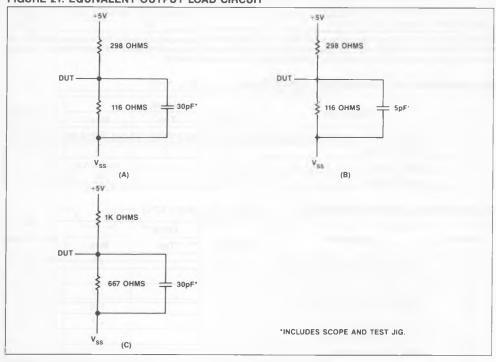

- All AC Electrical Characteristics measured under conditions specified in "AC Test Conditions".

- Measured w/5pf Output Load. See Equivalent Load Circuit B.

- Measured w/30pf Output Load. See Equivalent Load Circuit A.

- Applies to EF<sub>X</sub>, FF<sub>X</sub>, FF<sub>Y</sub>, EF<sub>Y</sub> Measured w/30pf Output Load. See Equivalent Load Circuit C.

- Applies to AE<sub>X</sub>, AF<sub>X</sub>, AE<sub>Y</sub>, AF<sub>Y</sub>. Measured w/30pf Output Load. See Equivalent Load Circuit C.

- 6. Writes beginning a) more than t<sub>1</sub> (max) before FF goes high will be blocked. b) less than t<sub>1</sub> (max) before and less than t<sub>FR</sub> (min) after FF goes high may be performed. c) t<sub>FR</sub> (min) after FF goes high will be performed.

- Reads beginning a) more than t<sub>1</sub> (max) before EF goes high will be blocked. b) less than t<sub>1</sub> (max) before and less than t<sub>FR</sub> (min) after EF goes high may be performed. c) t<sub>FR</sub> (min) after EF goes high will be performed.

### Read/Write

The FIFOs utilize separate Read and Write enable inputs to control port activity and direction. A low on a Read Enable reads a port's receive FIFO. A high on a Read Enable or a low on a Write Enable disables a port's data outputs to a high impedance state. A low on a Write Enable initiates a write to a port's transmit FIFO, regardless of the state of Read Enable. Input data is latched into the FIFO on the rising edge of a Write Enable.

## Full/Empty Flags

An active Full Flag indicates that a port's transmit FIFO is full and will accept no more data. Writes done to a FIFO while full are blocked. Once a read has occurred on a full FIFO, clearing a location in the FIFO, the Full Flag will go inactive, allowing another write to begin on the next falling edge of Write Enable.

An active Empty Flag indicates a port's receive FIFO is empty and can send no more data. Any reads done on a FIFO while empty are blocked. Once a write to an empty FIFO has occurred, the Empty Flag will go inactive, allowing another read to begin on the next falling edge of Read Enable.

#### Almost Flags

An inactive Almost Full flag indicates a port's transmit FIFO has room for at least four (4) more bytes, which is to say the flag will go active during the fourth write from full and stay active until after the fourth location from full has been vacated (read). An inactive Almost Empty flag indicates a port's receive FIFO has at least four (4) bytes of data in memory, ready to be read, which is to say that the flag will go active while reading the fourth remaining byte and remain active until after the fourth byte has been stored (written).

#### Reset

Reset is initiated by a low on the Master Reset (RS) input. A reset returns all data outputs to a high impedance state, taking precedence over the read strobes (R $_X$ /DIR and R $_Y$ ) and G. The states of the FIFO control inputs (R $_X$ /DIR, W $_X$ , R $_Y$  and W $_Y$ ) are a Don't Care throughout reset. The read strobes are a Don't Care at the end of reset because the Empty Flag becomes active (goes low) during reset, blocking any attempted reads. The write strobes (W $_X$  and W $_Y$ ) may fall any time during or after reset, but must not go high until t<sub>RSR</sub> after RS goes high.

### FIGURE 4. WRITE TIMING

## FIGURE 5. READ TIMING

## FIGURE 6. WRITE/READ TIMING

## FIGURE 7. READ/WRITE TIMING

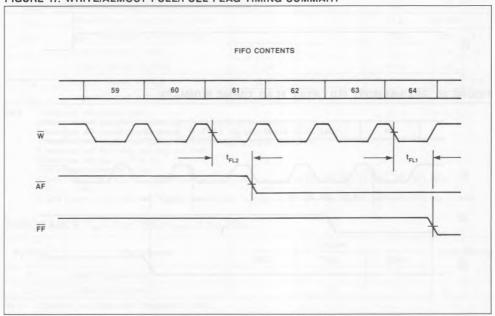

FIGURE 8. FULL (ALMOST FULL) FLAG TIMING

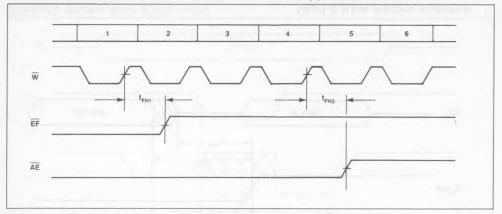

FIGURE 9. EMPTY (ALMOST EMPTY) FLAG TIMING

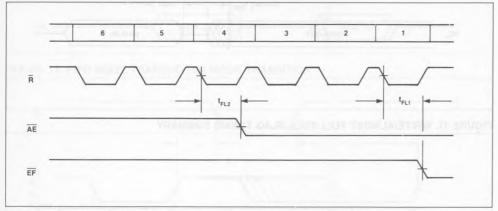

FIGURE 10. FIRST WRITE AFTER FULL TIMING

FIGURE 11. FIRST READ AFTER EMPTY TIMING

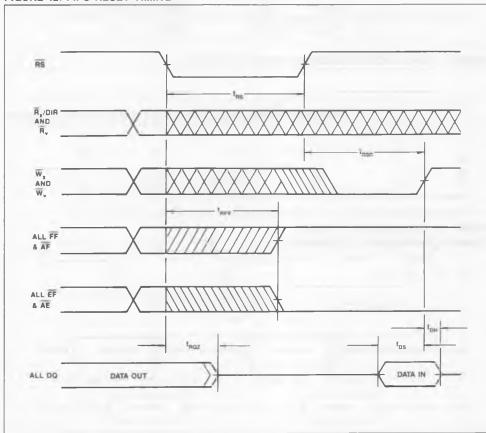

FIGURE 12. FIFO RESET TIMING

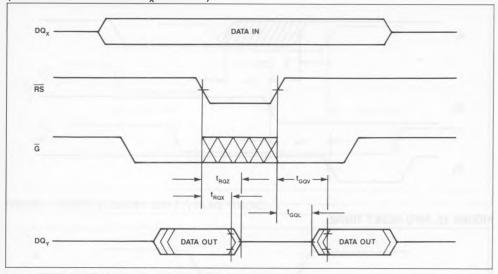

FIGURE 13. TRANSCEIVER RESET TIMING (EXAMPLE SHOWN WITH  $\overline{R_{x}}/DIR$  HIGH)

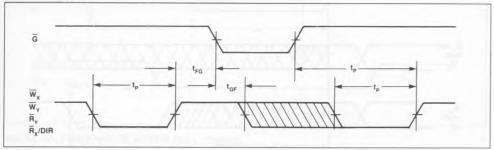

FIGURE 14. FIFO MODE/TRANSCEIVER MODE TRANSITION

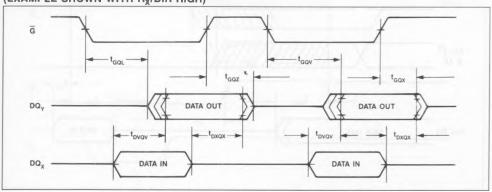

FIGURE 15. TRANSCEIVER G TIMING (EXAMPLE SHOWN WITH R<sub>x</sub>/DIR HIGH)

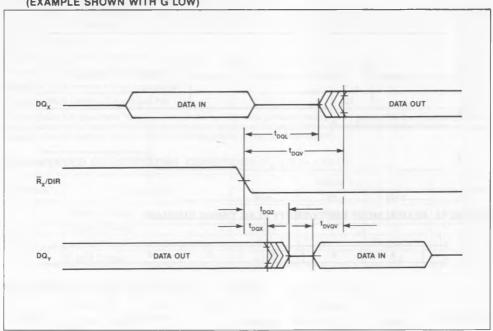

FIGURE 16. TRANSCEIVER  $\overline{R_{\chi}}/DIR$  TIMING (EXAMPLE SHOWN WITH  $\overline{G}$  LOW)

FIGURE 17. WRITE/ALMOST FULL/FULL FLAG TIMING SUMMARY

FIGURE 18. WRITE/ALMOST EMPTY/EMPTY FLAG TIMING SUMMARY

FIGURE 19. READ/ALMOST EMPTY/EMPTY FLAG TIMING SUMMARY

FIGURE 20. READ/ALMOST FULL/FULL FLAG TIMING SUMMARY

## ABSOLUTE MAXIMUM RATINGS\*

| Parameter                                       | Value          | Unit |

|-------------------------------------------------|----------------|------|

| Voltage on any Pin Relative to V <sub>SS</sub>  | - 1.5 to + 7.0 | V    |

| Ambient Operating Temperature (T <sub>A</sub> ) | 0 to + 70      | ∞    |

| Ambient Temperature under Bias                  | - 55 to + 125  | °C   |

| Ambient Storage Temperature (plastic)           | - 55 to + 125  | ∞    |

| Allowable Total Device Power Dissipation        | 1              | W    |

| Allowable RMS Output Current per Pin            | 80             | mA   |

<sup>\*</sup> Stresses greater than those listed \*Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

## RECOMMENDED DC OPERATING CONDITIONS (TA = 0° to + 70°C)

|        | Parameter      |       | 11-14 |                       |      |       |

|--------|----------------|-------|-------|-----------------------|------|-------|

| Symbol |                | Min.  | Тур.  | Max.                  | Unit | Notes |

| Vcc    | Supply Voltage | 4.5   | 5.0   | 5.5                   | V    | 1     |

| Vss    | Supply Voltage | 0     | 0     | 0                     | V    | 1     |

| VIH    | Logic 1 Input  | 2.2   |       | V <sub>CC</sub> + 0.3 | V    | 1     |

| VIL    | Logic 0 Input  | - 0.3 |       | 0.8                   | V    | 1     |

## DC ELECTRICAL CHARACTERISTICS ( $T_A = 0^{\circ}$ to $70^{\circ}$ C, $V_{CC} = 5.0 \pm 10\%$ )

| Symbol           |                                          |      | 11-14 |      |        |       |

|------------------|------------------------------------------|------|-------|------|--------|-------|

|                  | Parameter                                | Min. | Typ.  | Max. | Unit   | Notes |

| lcco             | Quiescent Power Supply Current, per Port |      |       | 25   | mA     | 1,2   |

| I <sub>CCA</sub> | Active Power Supply Current, per Port    |      |       | 40   | mA     | 1,3   |

| Icco             | Dynamic Power Supply Current, per Port   |      |       | 1.2  | mA/MHz | 1,4   |

| ССТ              | Total Power Supply Current, both Ports   |      |       | 100  | mA     | 1,5   |

| I <sub>IL</sub>  | Input Leakage Current                    | - 1  |       | + 1  | μА     | 6     |

| loL              | Output Leakage Current                   | - 10 |       | + 10 | μА     | 7     |

| V <sub>OH</sub>  | Logic 1 Output Voltage                   | 2.4  |       |      | V      | 7,8   |

| VoL              | Logic 0 Output Voltage                   |      |       | 0.4  | V      | 7,9   |

Notes: 1. Measured with outputs open.

2. Measured with opposite port quiescent ;  $\overline{R}, \ \overline{W}$  and  $\overline{G} \ge V_{\text{H}}$  (Min).

3 Measured with opposite port quiescent ;  $\overline{R}$  or  $\overline{W} \le V_{lk}$  (Max) and  $\overline{G} \ge V_{lH}$  (Min). 4 Measured with opposite port quiescent ;  $\overline{R}$  or  $\overline{W}$  toggling and  $\overline{G} \ge V_{lH}$  (Min).

5. Measured with both ports operating at to (min.).

6. Measured with V<sub>IN</sub> = 0.0V to V<sub>CC</sub>.

7. All voltages referenced to Vss.

8. Data Output Pins (DQx0-DQx4 and DQv0-DQv4) lout = 12m4 : Fig Output Pins EFx EFy FFx FFy AEx AEy AFx AFy)

9. Data Outputs (DQxo-DQx4 and DQvo-DQx4) lour = 12mA | Flag Output Pins EFx, EFy, FFx FFy, AEx AEy AFx AFy) lour = 4mA.

## CAPACITANCE ( $T_A = 0^\circ$ to $70^\circ$ C, $V_{CC} = 5.0 \pm 10\%$ )

| Symbol | Parameter          |      |      |      |      |       |

|--------|--------------------|------|------|------|------|-------|

|        |                    | Min. | Тур. | Max. | Unit | Notes |

| Cı     | Input Capacitance  |      | 4    | 5    | pF   | 1     |

| Co     | Output Capacitance |      | 8    | 10   | pF   | 1     |

Note: 1. Sampled, not 100% tested. Measured at 1 MKz.

#### **AC TEST CONDITIONS**

| Input Levels                        |            |

|-------------------------------------|------------|

| Transition Times                    | 5 ns       |

| Input and Output Reference Levels   | 1.5 Volts  |

| Ambient Temperature                 | 0° to 70°C |

| $V_{CC} = 5.0 \text{ Volts} + 10\%$ |            |

#### FIGURE 21. EQUIVALENT OUTPUT LOAD CIRCUIT

### **APPLICATION ISSUES**

#### Width Expansion

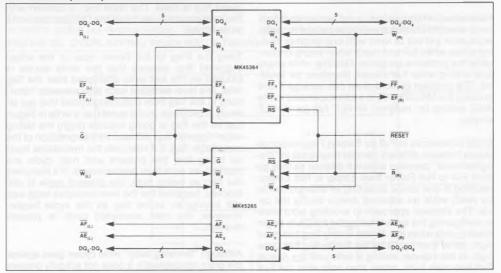

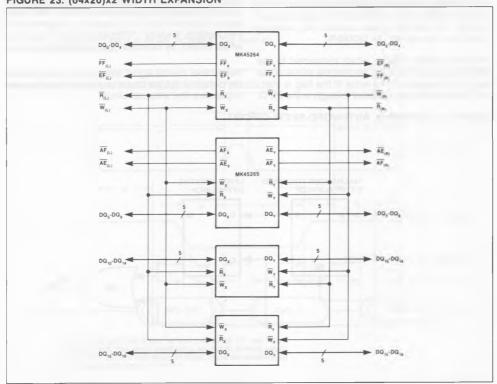

The MK45264/65 is designed to be used in sets of two or more, as shown below. The MK45264/65 is supplied in two configurations, MK45264 and MK45265; the MK45264 having Empty and Full Flags, the MK45265 having Almost Empty and Almost Full Flags. This scheme allows a pair of devices to be connected in such a way as to assure that the PAIR present a full complement of status flags in BOTH directions, that is, both to the left and to the right.

The resulting 10 bit wide configuration allows both parity AND beginning or end of message flag bits

to be carried along with an 8 bit byte of data. The 20 bit wide configuration allows carrying 2 bits of parity AND separate message start and stop bits in 16 bit applications.

The MK45264/65 was designed as a 5 bit wide device in order to allow the use of a 300 mil DIP package; allowing the MK45264/65 to: a) achieve the highest function/board space ratio possible for a fully featured bidirectional BiPORT FIFO, b) provide higher performance with improved noise margins than would be possible in higher pin count packages, and c) provide greater flexibility to users of various bus widths.

FIGURE 22. (64x10)x2 WIDTH EXPANSION

FIGURE 23. (64x20)x2 WIDTH EXPANSION

## Width Expansion and Word-Skew

Word-skew, in this context, is defined as what happens when FIFOs that are wired in parallel for width expansion get out of sync with one another. Halting writes when full and reads when empty circumvents the problems altogether. Reading while empty and writing while full should, therefore, be avoided. The problem of word-skew can emerge if one is using the MK45264/65 in width expansion mode AND writing (or reading) WHILE full (or WHILE empty).

Slight differences in Full (or Empty) Flag response delays between different devices may result in "disagreements" between adjacent devices as they go from Full to Not Full or from Empty to Not Empty; resulting in one device accepting an attempted write (or read) while an adjacent device blocks the cycle. The simplest approach to avoiding word skew is configuring the system using the FIFOs to begin reading only when the Almost Empty flag has gone high, rather than right after the Empty flag has gone high. In like manner, waiting to write until the Almost Full flag goes high, rather than right after the Full flag goes high will prevent the problem, which is why the Almost flags are provided. However, should such a scheme prove unworkable in a particular appication, the addition of an external flag latching circuit can also solve the problem.

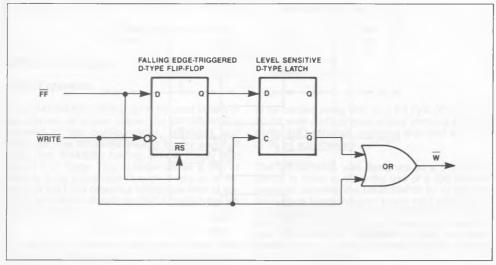

The circuit shown below, when connected to the Write strobe and Full Flag, latches the status of the flag at the beginning of a write. If the flag is inactive, the Write strobe is passed through to the FIFO.

When the flag goes active (low) the falling-edge triggered flop is reset. The reset flop, in concert with the level-sensitive latch and the OR gate block the write strobe

Tying the Flag to the Reset input of the edgetriggered flop assures that the Write strobe is blocked on the first write attempted after the flag falls. The level sensitive latch also prevents transitions in the flag from disturbing cycles that are already in progress. In the event that a write is begun just as the flag is going inactive (high) the falling edge-triggered flop will latch its interpretation of the metastable flag. If it interprets the metastable input as being low, the present and next cycle are blocked, as were their predecessors. If it interprets the flag as being high, the present cycle is still blocked, because the the level sensitive latch was still seeing an active flag as the cycle began. However, the next attempted cycle is passed through.

Although "throwing away" write cycles goes against the grain conceptually, it does not actually present a problem in this situation. It must be assumed that Writing while Full or Reading while Empty would only be allowed in applications where the write and/or read strobes are proceeding regardless of FIFO status anyway. "Throwing away" reads or writes cannot, by definition, be considered an error.

Remember, overall signal timing must comprehend the delays of the particular components chosen to implement the external circuit.

FIGURE 24. EXTERNAL ANTI-WORD-SKEW CIRCUIT

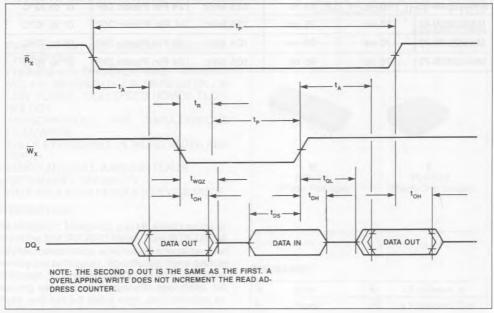

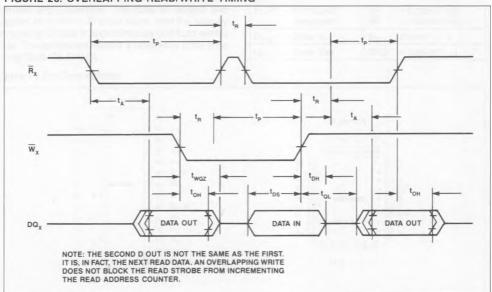

## Overlapping Read and Write Strobes

Overlapping Read and Write strobes on a given port is neither tested nor recommended. The following

timing diagrams are provided only to illustrate the relationship between the control functions.

## FIGURE 25. OVERLAPPING READ/WRITE TIMING

#### FIGURE 26. OVERLAPPING READ/WRITE TIMING

## ORDERING INFORMATION

| PART NO.    | ACCESS TIME | R/W CYCLE<br>TIME | CLOCK FREQ. | PACKAGE TYPE       | TEMPERATURE RANGE |

|-------------|-------------|-------------------|-------------|--------------------|-------------------|

| MK45264N-55 | 55 ns       | 75 ns             | 13.3 MHz    | 24 Pin Plastic DIP | 0° to 70°C        |

| MK45265N-55 | 55 ns       | 75 ns             | 13.3 MHz    | 24 Pin Plastic DIP | 0° to 70°C        |

| MK45264N-70 | 70 ns       | 95 ns             | 10.5 MHz    | 24 Pin Plastic DIP | 0° to 70℃         |

| MK45265N-70 | 70 ns       | 95 ns             | 10.5 MHz    | 24 Pin Plastic DIP | 0° to 70°C        |