### MK4202(Q)-20/22/25

### 2048 x 20 CMOS TAGRAM™

- 2048 x 20 CMOS SRAM WITH ONBOARD COMPARATOR

- MATCH ACCESS TIME = 20ns (max)

- READ ACCESS TIME = 25ns (max)

- RESET CYCLE = 25ns (max)

- Icc (outputs deselected) = 250mA (max)

- STANDBY = 50mA (max)

- FLASH CLEAR VALID BIT FUNCTION

- TARGET APPLICATION :

- 68020-25, 68030-33 AND 80386 CACHE

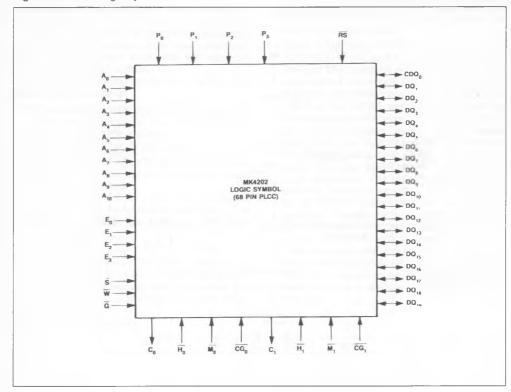

Figure 1 : Pinout for 68 Pin PLCC Package.

#### P, P, P, P, E, E, E, E, V, A, A, A, A, A, A, A, S, S, S 09 08 07 06 05 04 03 02 01 68 67 66 65 64 63 V<sub>cco</sub> 11 59 V<sub>ccs</sub> CDQ, 58 DQ, 12 00, DQ. 13 V 56 V<sub>sso</sub> DO. 15 DQ,, DO, 16 DQ, V<sub>CCB</sub> 17 A CCC TOP VIEW DQ, DQ, DQ, 19 00, 50 V<sub>SS0</sub> 20 Accu DQ,, DQ, 49 DO. DQ. 22 Vcco 47 23 V<sub>CD8</sub> DQ,, DQ. 24 DQ. 25 DO. Vssa V. 550 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 A, A, A, G VCC W S VSS M, H, CG, M, H, CG, VCC C, C

### PIN NAMES

| PIN NAM                             | E5                                                      |

|-------------------------------------|---------------------------------------------------------|

| V <sub>cc</sub> , V <sub>ss</sub>   | + 5V Supply, Ground                                     |

| V <sub>CCQ</sub> , V <sub>SSQ</sub> | + 5V Output Supply,<br>Output Ground                    |

| A <sub>0</sub> -A <sub>10</sub>     | Index Address Input                                     |

| CDOo                                | Clearable Tag Data I/O                                  |

| DQ1-DQ19                            | Tag Data I/O                                            |

| E <sub>0</sub> -E <sub>3</sub>      | Chip Enable (programmable active low or high)           |

| P <sub>0</sub> -P <sub>3</sub>      | Chip Enable Program Inputs                              |

| RS                                  | Reset Input (active low)                                |

| S                                   | Chip Select Input (active low)                          |

| W                                   | Write Enable (active low)                               |

| G                                   | Data Output Enable (active low)                         |

| Co                                  | Compare 0 Output<br>(3-state)<br>Hit = High, Miss = Low |

| C <sub>1</sub>                      | Compare 1 Output<br>(3-state)<br>Hit = High, Miss = Low |

| Ho                                  | Force hit 0 Input (active low)                          |

| H <sub>1</sub>                      | Force hit 1 Input (active low)                          |

| Mo                                  | Force Miss 0 Input (active low)                         |

| Mī                                  | Force Miss 1 Input (active low)                         |

| CG <sub>0</sub>                     | Compare 0 Output<br>Enable (active low)                 |

| CGi                                 | Compare 1 Output<br>Enable (active low)                 |

### **DEVICE DESCRIPTION AND FEATURES**

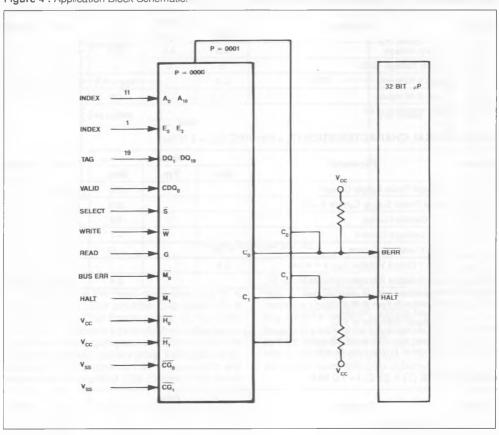

The MK4202 is designed to be connected DIRECT-LY to a high performance 32 bit microprocessor, allowing the elimination of the logic delays associated with collecting HIT or Miss outputs into a subsequent gate or the RC delays associated with wired-OR open collector match outputs.

The MK4202 TAGRAM has four major features that allow direct connection:

- Wide enough for almost any TAGRAM application without requiring multiple chip width expansion and the delays that would result.

- 2.Four (4) programmable CHIP ENABLE inputs, allowing DEPTH EXPANSION without any of the attendant chip enable decode delays that would otherwise be required.

$P_0$ - $P_3$  should be tied directly to  $V_{CC}$  or  $V_{SS}$ , or through pull-up or pull-down resistors. The MK4202 is selected when  $E_0$ - $E_3$  equals  $P_0$ - $P_3$  in a binary match.

(Example :  $E_0$ - $E_1$  = 0110,  $P_0$ - $P_3$  = 0110.)

3.3-STATE COMPARE OUTPUTS, allowing all Compare outputs to be bused together so the Address-to-Compare access time for a depth expanded application is identical to that of a single device. The Programmable Chip Enables prevent bus contention by assuring that only one TAGRAM at a time drives each Compare bus when in Compare mode.

4.DUAL COMPARE OUTPUTS (Co and C1) and FORCED HIT (Ho and H1) and FORCED MISS (Mo and M1) inputs for each. The arrangement allows direct connection of the TAGRAM to two separate processor inputs (such as BERR and HALT on the 68030), and connection of all signals that would otherwise have been connected to those processor inputs to be passed THROUGH the TAGRAM; eliminating the need for a subsequent gate to collect the COMPARE output and other BERR or HALT signal sources to the processor. The net effect is that the Address-to-Compare access time demonstrated by the MK4202 is all of the delay the user must consider. The alternative approach, using narrow TAGRAMs with open collector outputs or narrow TAGRAMs with 2-state outputs and a 10ns programmable logic device, requires that the narrow TAGRAMs demonstrate a 10ns Address-to-Compare access time to yield the same performance in a user's system that the MK4202 provides.

### TRUTH TABLE (MK4202Q)

| RS | S  | Е | W  | G  | Mx | Hx | CGx | Mode         | Cx       | DQ    | Notes |

|----|----|---|----|----|----|----|-----|--------------|----------|-------|-------|

| Hi | _  | Х | _  | _  | Lo | Х  | Х   | Force Miss   | Low      | _     | 1     |

| Hi | _  | × | _  | _  | Hi | Lo | Х   | Force Hit    | High     | _     | 1     |

| Hi | -  | X | _  | _  | Hi | Hi | Hi  | Comp Disable | Hi-Z     | _     | 1     |

| Hi | Х  | F | Х  | X  | Hi | Hi | X   | Standby      | Hi-Z     | Hi-Z  |       |

| Hi | X  | Т | Hi | Hi | Hi | Hi | Hi  | Compare      | Hi-Z     | D in  |       |

| Hi | Х  | Т | Hi | Hi | Hi | Hi | Lo  | Compare      | Hi or Lo | D in  |       |

| Hi | Hi | Т | Lo | X  | Hi | Hi | Lo  | Hit          | High     | Hi-z  |       |

| Hi | Hi | Т | Х  | Lo | Hi | Hi | Lo  | Hit          | High     | Hi-Z  |       |

| Hi | Lo | Т | Lo | X  | Hi | Hi | Lo  | Write        | High     | D in  |       |

| Hi | Lo | Т | Hi | Lo | Hi | Hi | Lo  | Read         | High     | D Out |       |

| Lo | Hi | Х | Х  | Х  | _  | -  | _   | Reset        | -        | Hi-Z  |       |

| Lo | Х  | F | Х  | Х  | _  | _  | _   | Reset        | _        | Hi-Z  |       |

| Lo | Х  | X | Hi | Hi | _  | _  | _   | Reset        | _        | Hi-Z  |       |

| Lo | Х  | × | Hi | Lo | _  | _  | -   | Reset        | _        | Lo-Z  |       |

| Lo | Lo | Т | Lo | X  | _  | -  | -   | Not Allowed  | -        | Hi-Z  | 2     |

| Lo | Х  | Т | Hi | Hi | Hi | Hi | Lo  | Reset        | Lo       | D in  | 3     |

Key:

X = Don't Care

$H_X = H_0 \text{ or } H_1$

$\frac{M_X = M_0 \text{ or } M_1}{CG_x = CG_0 \text{ or } CG_1}$

F = (False) E<sub>0</sub>-E<sub>3</sub> pattern DOES NOT match P<sub>0</sub>-P<sub>3</sub> pattern.

$T = (True) E_0-E_3$  pattern DOES match  $P_0-P_3$  pattern.

- = Not related to identified mode of operation.

Notes: 1. Force hit/miss operations independent of other RAM operations.

May disrupt Reset, will not damage device.

Reset will force C<sub>X</sub> low during a valid compare when CDQ<sub>0</sub> is D<sub>IN</sub> = HIGH.

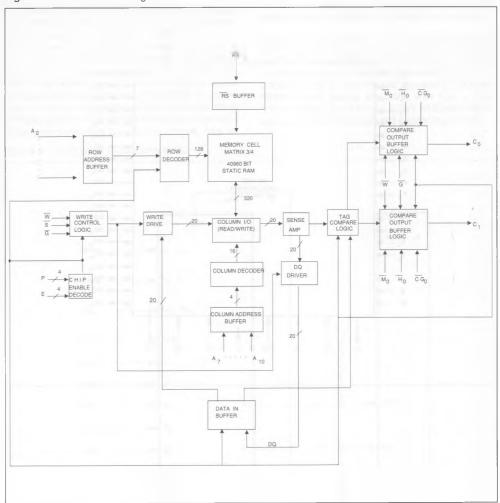

Figure 2: MK4202 Block Diagram.

Figure 3 : Device Logic Symbol.

### POWER DISTRIBUTION

The MK4202, being a 20 output device, obviously requires the use of good power bussing techniques. MK4202 has been designed in such a way as to allow the user to minimize the effects of switching transients on overall circuit operation. Of particular interest is the separate bussing of the Vcc and Vss lines to the output drivers. The advantage provided by these separate power pins, designated Vcc and Vsso, is that voltage sags and ground bumps seen on these pins are not reflected into the other portions of the chip, particularly the input structures. As a re-

sult, switching noise in the supply has much less effect on input levels, providing the user with more noise margin than would otherwise be available.

Of course V<sub>CC</sub> and V<sub>CCQ</sub> must always be at the same DC potential. VSs and V<sub>SSQ</sub> must match as well. Differences between them due to AC effects are expected, but must be minimized through the adequate use of bussing and bypassing. All specifications and testing are done with VSs = VSSQ  $\pm\,10\text{mV}$  RMS, V<sub>CC</sub> = V<sub>CCQ</sub>  $\pm\,10\text{mV}$  RMS with instantaneous peak differences not exceeding 50mV.

Figure 4: Application Block Schematic.

### **ABSOLUTE MAXIMUM RATINGS**\*

| Parameter                                       | Value       | Unit  |

|-------------------------------------------------|-------------|-------|

| Voltage on any Pin Relative to V <sub>SS</sub>  | - 0.3 to7.0 | V     |

| Ambient Operating Temperature (T <sub>A</sub> ) | 0 to 70     | °C    |

| Ambient Storage Temperature (plastic)           | - 55 to 125 | °C    |

| Total Device Power Dissipation                  | 2.5         | Watts |

| RMS Output Current per Pin                      | 25          | mA    |

<sup>\*</sup> Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other condition above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability

### **RECOMMENDED DC OPERATING CONDITIONS** $(T_A = 0 \text{ to } 70^{\circ}\text{C})$

| Symbol          | Parameter           |       | Value |                       | Unit  | Notes |

|-----------------|---------------------|-------|-------|-----------------------|-------|-------|

| Symbol          | raiametei           | Min.  | Тур.  | Max.                  | Ollit | Notes |

| V <sub>CC</sub> | Supply Voltage      | 4.5   | 5.0   | 5.5                   | V     |       |

| V <sub>SS</sub> | Supply Voltage, GND | 0     | 0     | 0                     | V     |       |

| V <sub>IH</sub> | Logic 1 All Inputs  | 2.2   |       | V <sub>CC</sub> + 0.3 | V     | 5     |

| V <sub>IL</sub> | Logic 0 All Inputs  | - 0.3 |       | 0.8                   | V     | 5     |

Note: All voltages referenced to Vss.

### DC ELECTRICAL CHARACTERISTICS ( $T_A = 0$ to $70^{\circ}$ C, $V_{CC} = \pm 10^{\circ}$ )

| Symbol           | Parameter                                         |      | Value |      | Unit | Notes |

|------------------|---------------------------------------------------|------|-------|------|------|-------|

| Symbol           | Falameter                                         | Min. | Тур.  | Max. | J    | Notes |

| lcc              | Average Power Supply Current                      |      |       | 250  | mA   | 1     |

| I <sub>CCA</sub> | Active Power Supply Current (f = 0)               |      |       | 200  | mA   | 1     |

| I <sub>SB1</sub> | TTL Standby Current                               |      |       | 50   | mA   | 1     |

| I <sub>IL</sub>  | Input Leakage Current                             | - 1  |       | + 1  | μА   | 2     |

| loL              | Output Leakage Current                            | - 10 |       | + 10 | μА   | 3     |

| V <sub>OH</sub>  | Logic 1 Output Voltage (I <sub>OUT</sub> = - 4mA) | 2.4  |       |      | V    | 4     |

| V <sub>OL</sub>  | Logic 0 Output Voltage (I <sub>OUT</sub> = 8mA)   |      |       | 0.4  | V    | 4     |

- Notes: 1. Measured with outputs open. Vcc max.

- 2. Measured with  $V_{\text{IN}} = 0.0V$  to  $V_{\text{CC}}$

- 3. Measured at CDQ<sub>0</sub>, DQ<sub>1</sub>-DQ<sub>19</sub>, C<sub>0</sub> and C<sub>1</sub>.

- 4. All voltages referenced to Vsso.

- 5. Inputs (Po-P3) require VIH min. = 4.5 volts and VIL max. = 0.5 volts.

- 6. Sampled, not 100% tested. Measured at 1 MHz.

- 7. Measured at all data I/O's, Co and C1.

### CAPACITANCE (T<sub>A</sub> = 25°C, f = 1.0 MHz)

| 0      | December           |      | Value |      | 1.1-24 | h1-4  |

|--------|--------------------|------|-------|------|--------|-------|

| Symbol | Parameter          | Min. | Тур.  | Max. | Unit   | Notes |

| Cı     | Input Capacitance  | 4    |       | 4    | pF     | 6     |

| Co     | Output Capacitance | 8    |       | 10   | pF     | 6.7   |

### AC TEST CONDITIONS

| Input Levels                            | GND to 3V  |

|-----------------------------------------|------------|

| Transition Time                         | 5ns        |

| Input and Output Timing Reference Level | 1.5V       |

| Ambient Temperature                     | 0° to 70°C |

| Vcc                                     | 5.0V ± 10% |

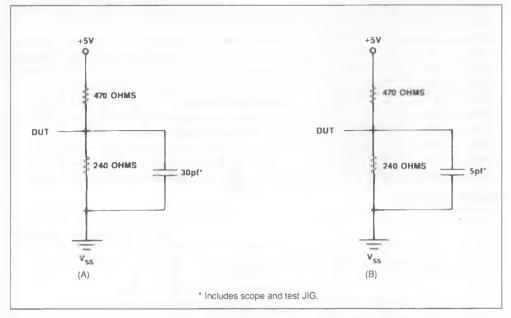

Figure 5 : Equivalent Output Load Circuit.

### **READ MODE**

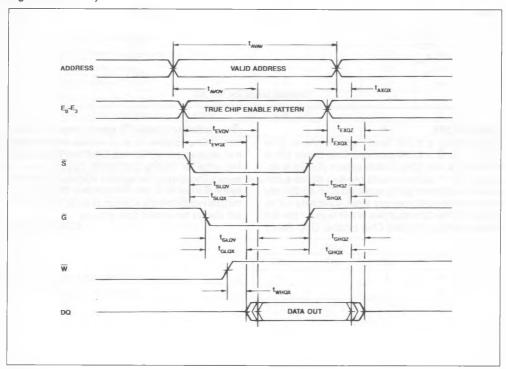

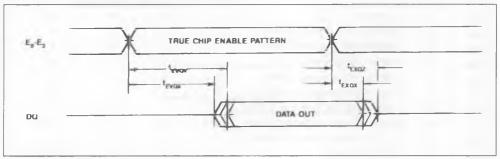

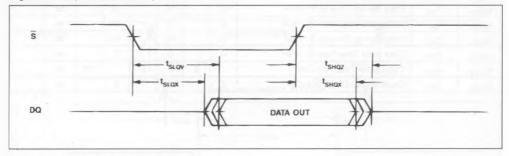

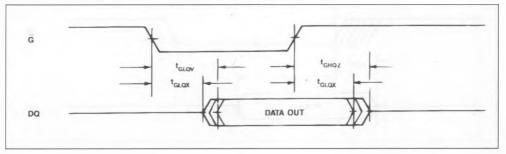

The MK4202 is in the Read mode whenever  $\overline{W}$  is HIGH, and  $\overline{G}$  is LOW provided Chip Select  $(\overline{S})$  is LOW and a true Chip Enable pattern  $(E_0-E_3)$  is applied. The 11 address inputs  $(A_0-A_{10})$  define a unique index address giving access to 20 of 40,960 bits of data in the static memory array. Valid data will be present at the 20 output pins within tavov of the last stable address provided Chip Enable, Chip Select

( $\overline{S}$ ), and Output Enable ( $\overline{G}$ ) access times have been met. If Chip Enable,  $\overline{S}$ , or  $\overline{G}$  access times are not met, data access will be measured from the latter falling edge or limiting parameter (tevov, tsLov, or tsLov). The state of the tag data I/O pins is controlled by the (E<sub>0</sub>-E<sub>3</sub>),  $\overline{S}$ ,  $\overline{G}$ , and  $\overline{W}$  input pins. The data lines may be indeterminate at tevox, or tsLox, or tgLox, but will always have valid data at tayov.

# ELECTRICAL CHARACTERISITCS AND RECOMMENDED AC OPERATING CONDITIONS (read cyle timing) (0°C $\leq$ T<sub>A</sub> $\leq$ 70°C) ( $V_{CC}$ = 5.0 $\pm$ 5%)

| STD               | ALT              | Parameter                      | -    | 20   | - :  | 22   | - :  | 25   | Units  | Notes |

|-------------------|------------------|--------------------------------|------|------|------|------|------|------|--------|-------|

| Symbol            | Symbol           | T arameter                     | Min. | Max. | Min. | Max. | Min. | Max. | Ullits | Notes |

| t <sub>AVAV</sub> | t <sub>C</sub>   | Cycle Time                     | 25   |      | 25   |      | 30   |      | ns     |       |

| tavav             | t <sub>AA</sub>  | Address Access Time            |      | 25   |      | 25   |      | 30   | ns     |       |

| t <sub>AXQX</sub> | t <sub>AOH</sub> | Address Output Hold Time       | 5    |      | 5    |      | 5    |      | ns     |       |

| tAEQV             | t <sub>EA</sub>  | Chip Enable Access Time        |      | 25   |      | 25   |      | 30   | ns     |       |

| t <sub>EXQX</sub> | t <sub>∈OH</sub> | Chip Enable Output Hold Time   | 4    |      | 4    |      | 4    |      | ns     |       |

| tevax             | t <sub>ELZ</sub> | Chip Enable TRUE to Low-Z      | 4    |      | 4    |      | 4    |      | ns     |       |

| t <sub>EXQZ</sub> | t <sub>EHZ</sub> | Chip Enable FALSE to high-Z    |      | 8    |      | 8    |      | 10   | ns     |       |

| tsLQV             | t <sub>SA</sub>  | Chip Select Access Time        |      | 15   |      | 15   |      | 18   | ns     |       |

| t <sub>SHQX</sub> | tsон             | Chip Select Output Hold Time   | 2    |      | 2    |      | 2    |      | ns     |       |

| t <sub>SLQX</sub> | t <sub>SLZ</sub> | Chip Select to Low-Z           | 3    |      | 3    |      | 3    |      | ns     |       |

| t <sub>SHQZ</sub> | t <sub>SHZ</sub> | Chip Select to High-Z          |      | 4    |      | 4    |      | 6    | ns     |       |

| †GLQV             | t <sub>GA</sub>  | Output Enable Access Time      |      | 13   |      | 13   |      | 15   | ns     |       |

| t <sub>GHQX</sub> | <sup>t</sup> GOH | Output Enable Output Hold Time | 2    |      | 2    |      | 2    |      | ns     |       |

| t <sub>GLQX</sub> | t <sub>GLZ</sub> | Output Enable to Low-Z         | 2    |      | 2    |      | 2    |      | ns     |       |

| t <sub>GHQZ</sub> | 1 <sub>GHZ</sub> | Output Enable to high-Z        |      | 5    |      | 5    |      | 8    | ns     |       |

Figure 6: Read Cycle.

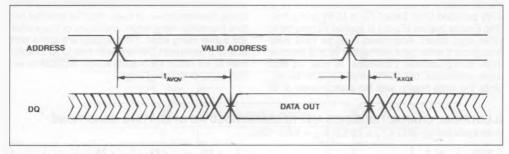

Figure 7: Address Read Cycle.

Figure 8 : Chip Enable Read Cycle.

Figure 9: Chip Select Read Cycle.

Figure 10 : Output Enable Read Cycle.

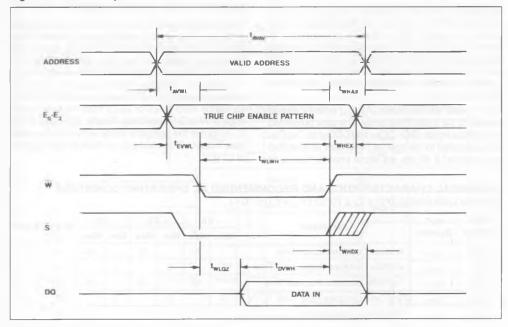

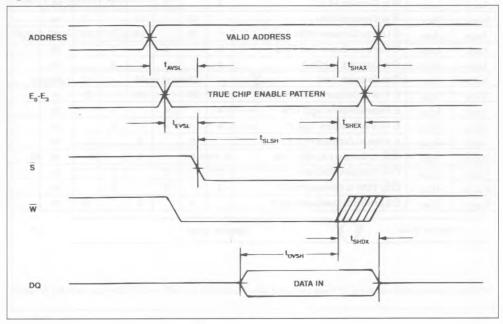

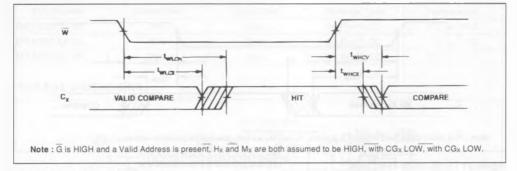

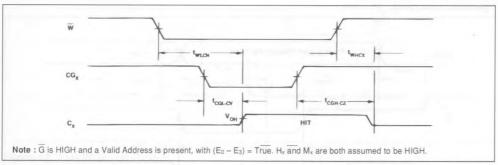

### WRITE MODE

The MK4202 is in the Write mode whenever  $\overline{W}$  is LOW provided Chip Select  $(\overline{S})$  is LOW and a true Chip Enable pattern  $(E_0\text{-}E_3)$  is applied  $(\overline{G})$  may be in either logic state). Addresses must be held valid throughout a write cycle, with either  $\overline{W}$  or  $\overline{S}$  inactive HIGH during address transitions.  $\overline{W}$  may fall with stable addresses, but must remain valid for  $t_{WLWH}$ . Since the write begins with the concurrence of  $\overline{W}$

and  $\overline{S}$ , should  $\overline{W}$  become active first, then  $t_{SLSH}$  must be satisfied. Either  $\overline{W}$  or  $\overline{S}$  can terminate the write cycle, therefore  $t_{DVWH}$  or  $t_{DVSH}$  must be satisfied before the earlier rising edge, and  $t_{WHDX}$  or  $t_{SHDX}$  after the earlier rising edge. If the outputs are active with  $\overline{G}$  and  $\overline{S}$  asserted LOW and with true Chip Enable, then  $\overline{W}$  will return the outputs to high impedance within  $t_{WLHZ}$  of its falling edge.

# ELECTRICAL CHARACTERISITICS AND RECOMMENDED AC OPERATING CONDITIONS (write cycle timing) $(0^{\circ}\text{C} \leq \text{T}_{\text{A}} \leq 70^{\circ}\text{C})$ (V<sub>CC</sub> = $5.0 \pm 10\%$ )

| STD               | ALT             | Parameter                        |      | 20   | -    | 22   | -    | 25   | Units  | Notes |

|-------------------|-----------------|----------------------------------|------|------|------|------|------|------|--------|-------|

| Symbol            | Symbol          | raidilletei                      | Min. | Max. | Min. | Max. | Min. | Max. | Offica | Hotes |

| tavav             | tc              | Cycle Time                       | 25   |      | 25   |      | 30   |      | ns     |       |

| t <sub>AVWL</sub> | tas             | Address Set-up Time to W LOW     | 0    |      | 0    |      | 0    |      | ns     |       |

| 1 <sub>WHAX</sub> | t <sub>AH</sub> | Address Hold Time from WHIGH     | 0    |      | 0    |      | 0    |      | ns     |       |

| t <sub>AVSL</sub> | tas             | Address Set-up Time to S LOW     | 0    |      | 0    |      | 0    |      | ns     |       |

| t <sub>SHAX</sub> | t <sub>AH</sub> | Address Hold Time from S HIGH    | 0    |      | 0    |      | 0    |      | ns     |       |

| t <sub>EVWL</sub> | t <sub>ES</sub> | Chip Enable Set-up Time to WLOW  | 3    |      | 3    |      | 3    |      | ns     |       |

| t <sub>WHEX</sub> | t <sub>EH</sub> | Chip Enable Hold Time from WHIGH | 0    |      | 0    |      | 0    |      | ns     |       |

| t <sub>EVSL</sub> | tes             | Chip Enable Set-up Time to S LOW | 3    |      | 3    |      | 3    |      | ns     |       |

| t <sub>SHEX</sub> | t <sub>EH</sub> | Chip Enable Hold Time to S HIGH  | 0    |      | 0    |      | 0    |      | ns     |       |

| 1 <sub>WLWH</sub> | tww             | Write Pulse Width                | 15   |      | 15   |      | 18   |      | ns     |       |

| t <sub>SLSH</sub> | tsw             | Chip Select Pulse Width          | 16   |      | 16   |      | 20   |      | ns     |       |

| t <sub>DVWH</sub> | t <sub>DS</sub> | Data Set-up Time to WHIGH        | 12   |      | 12   |      | 15   |      | ns     |       |

| t <sub>WHDX</sub> | t <sub>DH</sub> | Data Hold Time from WHIGH        | 0    |      | 0    |      | 0    |      | ns     |       |

| t <sub>DVSH</sub> | t <sub>os</sub> | Data Set-up Time to S HIGH       | 12   |      | 12   |      | 15   |      | ns     |       |

| t <sub>SHDX</sub> | tон             | Data Hold Time from S HIGH       | 0    |      | 0    |      | 0    |      | ns     |       |

| t <sub>WLQZ</sub> | t <sub>wz</sub> | Outputs Hi-Z from W-LOW          |      | 8    |      | 8    |      | 10   | ns     |       |

| t <sub>whax</sub> | t <sub>WL</sub> | Outputs Low-Z from WHIGH         | 5    |      | 5    |      | 5    |      | ns     |       |

Figure 11 : W Write Cycle.

Figure 12: S Write Cycle.

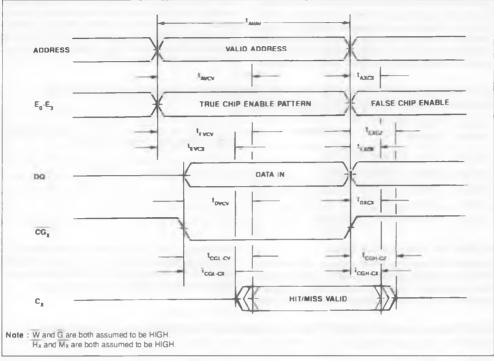

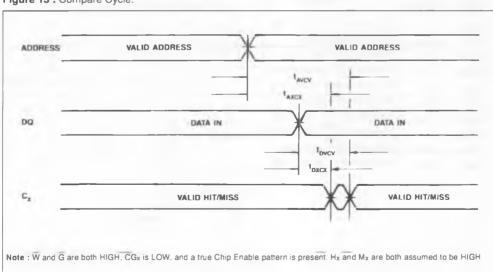

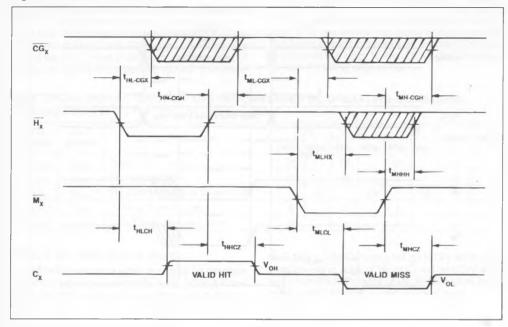

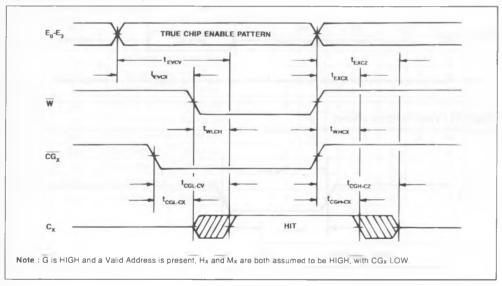

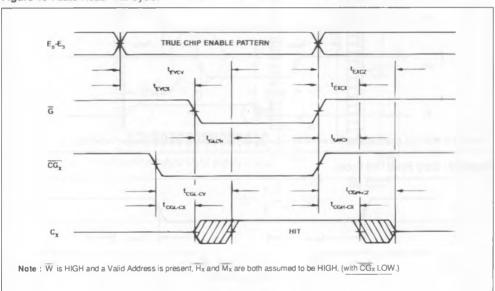

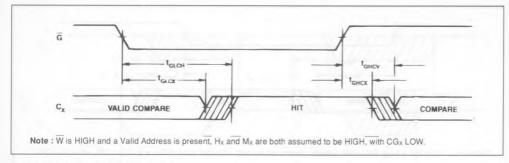

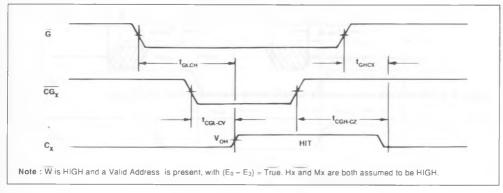

#### **COMPARE MODE**

The MK4202 is in the Compare mode whenever  $\overline{W}$  and  $\overline{G}$  are HtGH provided a true Chip Enable (E<sub>0</sub>-E<sub>3</sub>) pattern is applied. Chip Select (S) is reguarded as a don't care since the user is not concerned with the data outputs, but only with the Compare (Cx) outputs. Mx and Hx must be HIGH, and CGx active LOW to enable the Compare outputs for a valid compare hit or miss.

The 11 index address inputs  $(A_0 - A_{10})$  define a unique location in the static RAM array. The data presented on the Data Inputs  $(DQ_1 - DQ_{19} \text{ and } CDQ_0)$  as Tag Data is compared to the internal RAM data as specified by the index. If all bits are equal (match) then a hit

condition occurs ( $C_X = HIGH$ ). If at least one bit is not equal, then a miss occurs ( $C_X = LOW$ ).

The Compare output will be valid tavcv from stable address, or tovcv from valid tag data provided Chip Enable is true, and CGx is active LOW. Should the address be stable with valid tag data, and Chip Enable false, then compare access will be within tevov from true Chip Enable. When executing a write-tocompare cycle (W = LOW, and  $\overline{G}$  = LOW or HIGH), Cx will be valid twheve or tghcv from the latter rising edge of W or G respectively. Finally, when gating the Cx output in the compare mode with CGx, the compare output will be valid tcgL-cv from the falling edge of CGx.

## ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITIONS (compare cycle timing) $(0^{\circ}C \le T_A \le 70^{\circ}C)$ ( $V_{CC} = 5.0 \pm 10\%$ )

| STD                 | ALT               | Parameter                              | -    | 20   | - :  | 22   |      | 25   | Units  | Notes |

|---------------------|-------------------|----------------------------------------|------|------|------|------|------|------|--------|-------|

| Symbol              | Symbol            | raianetei                              | Min. | Max. | Min. | Max. | Min. | Max. | Ollits | Notes |

| tavcv               | t <sub>ACA</sub>  | Address Compare Access Time            |      | 20   |      | 22   |      | 25   | ns     |       |

| †AXCX               | t <sub>ACOH</sub> | Address Compare Output Hold Time       | 5    |      | 5    |      | 5    |      | ns     |       |

| tovcv               | t <sub>DCA</sub>  | Tag Data Compare Access Time           |      | 16   |      | 18   |      | 20   | ns     |       |

| toxcx               | t <sub>DCH</sub>  | Tag Data Compare Hold Time             | 2    |      | 2    |      | 2    |      | ns     |       |

| twlch               | ¹wcн              | W LOW to Compare HIGH                  |      | 10   |      | 11   |      | 12   | ns     |       |

| twhcx               | фсон              | W Compare Output hold Time             | 3    |      | 3    |      | 3    |      | ns     |       |

| twcx                | t <sub>WLCZ</sub> | W to Compare HOLD                      | 3    |      | 3    |      | 3    |      | ns     |       |

| \$whcv              | twcv              | W to Compare Valid                     |      | 10   |      | 10   |      | 12   | ns     |       |

| t <sub>GLCH</sub>   | 1 <sub>GCH</sub>  | G Low to Compare HIGH                  |      | 10   |      | 11   |      | 12   | ns     |       |

| t <sub>GHCX</sub>   | t <sub>CGOH</sub> | G Compare Output Hold Time             | 3    |      | 3    |      | 3    |      | ns     |       |

| t <sub>GLCX</sub>   | †GLCZ             | G to Compare to HOLD                   | 3    |      | 3    |      | 3    |      | ns     |       |

| t <sub>GHCV</sub>   | t <sub>GCV</sub>  | G to Compare Valid                     |      | 10   |      | 10   |      | 12   | ns     |       |

| tE∧CA               | t <sub>ECA</sub>  | E True to Compare Access Time          |      | 20   |      | 22   |      | 25   | ns     |       |

| t <sub>EXCX</sub>   | <sup>†</sup> ECOH | E False Compare Hold Time              | 4    |      | 4    |      | 4    |      | ns     |       |

| t <sub>EVCX</sub>   | t <sub>ECLZ</sub> | E True to Compare Low-Z                | 4    |      | 4    |      | 4    |      | ns     |       |

| t <sub>EXCZ</sub>   | t <sub>ECHZ</sub> | E False to Compare high-Z              |      | 8    |      | 8    |      | 10   | ns     |       |

| t <sub>CGL-CV</sub> | <sup>†</sup> CGA  | CG <sub>X</sub> to Compare Access Time |      | 8    |      | 8    |      | 10   | ns     |       |

| t <sub>CGH-CX</sub> | t <sub>CGOH</sub> | CG <sub>X</sub> Compare Hold time      | 2    |      | 2    |      | 2    |      | ns     |       |

| t <sub>CGL-CX</sub> | †cGLZ             | CG <sub>X</sub> LOW to Compare low-Z   | 2    |      | 2    |      | 2    |      | ns     |       |

| 1 <sub>CGH-CZ</sub> | t <sub>CGHZ</sub> | CG <sub>X</sub> HIGH to Compare High-Z |      | 8    |      | 8    |      | 10   | ns     |       |

Figure 12: Summary Compare Cycle.

Figure 13: Compare Cycle.

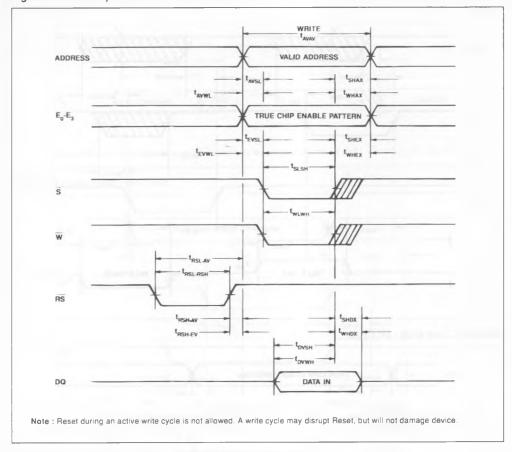

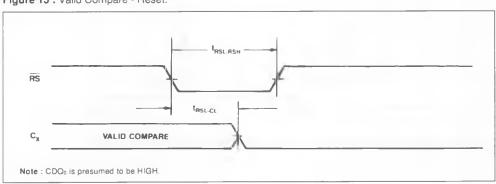

#### RESET MODE

The MK4202 allows an asynchronous reset whenever RS is LOW regardless of the logic state on the other input pins. Reset clears all internal RAM bits in CDOn (2048 bits) to a logic zero. This output can be used as a valid tag bit to insure a valid compare miss or hit. It should be noted that a valid write cycle is not allowed

during a reset cycle (W = LOW, S = LOW, RS = LOW, and Chip Enable is true). The state of the data outputs is determined by the input control logic pins: Chip Enable. S. G. and W (see truth table). Should a reset occur during a valid compare cycle, and the CDQ0 valid tag bit is set to a logic (1), then Cx will go LOW at tags. CL from the falling edge of RS.

### **ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITIONS** (reset cycle timing) $(0^{\circ}C \leq T_{A} \leq 70^{\circ}C)$ $(V_{CC} = 5.0 \pm 10\%)$

| STD                  | ALT                | Parameter                    | - 20 |      | - 22 |      | - 25 |      | Units  | Notes |

|----------------------|--------------------|------------------------------|------|------|------|------|------|------|--------|-------|

| Symbol               | Symbol             | - arameter                   | Min. | Max. | Min. | Max. | Min. | Max. | Ullits | Notes |

| talsl-AV             | tasc               | Reset Cycle Time             | 20   |      | 25   |      | 30   |      | ns     |       |

| t <sub>RSL-RSH</sub> | tasw               | Reset pulse Width            | 25   |      | 25   |      | 30   |      | ns     |       |

| t <sub>ASL-CL</sub>  | t <sub>ASCL</sub>  | RS LOW to Compare Output LOW |      | 25   |      | 25   |      | 30   | ns     |       |

| t <sub>ASH-AV</sub>  | t <sub>RSR</sub>   | Address Recovery Time        | 0    |      | 0    |      | 0    |      | ns     |       |

| t <sub>ASH-EV</sub>  | _ t <sub>RSR</sub> | Chip Enable Recovery Time    | 0    |      | 0    |      | 0    |      | ns     |       |

#### FORCE HIT AND FORCE MISS

The MK4202 can force either a miss or hit condition on the Cx output by asserting Mx or Hx LOW. A Force Miss overrides a Force Hit condition and is not dependent upon Compare Output Enable (CGx) (see truth table). The Cx output will go HIGH within thech from the falling edge of Hx or Cx will go LOW within tMLCL from the falling edge of Mx. All Mx and Hx inputs must be HIGH during a valid compare cycle.

### **ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITIONS**

(force hit or miss cycle timing)  $(0^{\circ}C \le T_A \le 70^{\circ}C)$  ( $V_{CC} = 5.0 \pm 10\%$ )

| STD                 | ALT              | Parameter                                | -    | - 20 |      | - 22 |      | - 25 |       | Notes |

|---------------------|------------------|------------------------------------------|------|------|------|------|------|------|-------|-------|

| Symbol              | Symbol           | - arameter                               | Min. | Max. | Min. | Max. | Min. | Max. | Units | Notes |

| t <sub>HLCH</sub>   | t <sub>HA</sub>  | H <sub>X</sub> to Force Hit Access Time  |      | 8    |      | 8    |      | 10   | ns    |       |

| t <sub>HHCZ</sub>   | tHHZ             | H <sub>X</sub> to Compare High-Z         |      | 5    |      | 5    |      | 8    | ns    |       |

| t <sub>HL-CGX</sub> | t <sub>HS</sub>  | Force hit to CG xdon't care              | 2    |      | 2    |      | 2    |      | ns    |       |

| t <sub>HH-CGH</sub> | t <sub>HR</sub>  | Force hit to CG xrecognized              | 2    |      | 2    |      | 2    |      | ns    |       |

| t <sub>MLCL</sub>   | t <sub>MA</sub>  | M <sub>X</sub> to Force Miss Access Time |      | 8    |      | 8    |      | 10   | ns    |       |

| t <sub>MHCZ</sub>   | t <sub>MHZ</sub> | M <sub>X</sub> to Compare to high-Z      |      | 5    |      | 5    |      | 8    | ns    |       |

| t <sub>ML-CGX</sub> | t <sub>MS</sub>  | Force Miss to CG xdon't care             | 2    |      | 2    |      | 2    |      | ns    |       |

| t <sub>MH-CGH</sub> | t <sub>MR</sub>  | Force Miss to CG xRecognized             | 2    |      | 2    |      | 2    |      | ns    |       |

| t <sub>MLHX</sub>   | t <sub>MHS</sub> | Force Miss to H xdon't care              | 2    |      | 2    |      | 2    |      | ns    |       |

| t <sub>мннн</sub>   | \$MHR            | Force Miss to H xRecognized              | 2    |      | 2    |      | 2    |      | ns    |       |

Figure 14: Reset Cycle.

Figure 15: Valid Compare - Reset.

Figure 16: Force Hit and Force Miss.

Figure 17: Late Write - Hit Cycle.

Figure 18: Compare - Write Hit - Compare Cycle.

Figure 19: Late Read - Hit Cycle.

Figure 20: Compare - Read Hit - Compare Cycle.

Figure 21 : Early Write - Hit Cycle.

Figure 22 : Early Read - Hit Cycle.

### ORDER CODE

| Part Number  | Access Time | Cycle Time | Package Type | Temperature |

|--------------|-------------|------------|--------------|-------------|

| MK4202(Q)-20 | 20ns        | 25ns       | 68 Pin PLCC  | 0°C to 70°C |

| MK4202(Q)-22 | 22ns        | 25ns       | 68 Pin PLCC  | 0°C to 70°C |

| MK4202(Q)-25 | 25ns        | 30ns       | 68 Pin PLCC  | 0°C to 70°C |

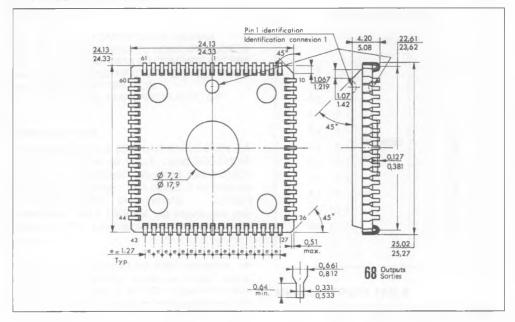

### PACKAGE DIMENSIONS