# MICROCOMPUTER COMPONENTS

# CMOS MICROCOMPUTER CLOCK/RAM

# MK3805N/MK3806N

#### **FEATURES**

- Real-time clock counts seconds, minutes, hours, date of the month, day of the week, month, and year. Every 4th year, February has 29 days.

- ☐ Serial I/O for minimum pin count (8 pins)

- □ 24 x 8 RAM for scratchpad data storage

- □ Simple Microcomputer interface

- ☐ High speed shift clock independent of crystal oscillator frequency

- Single byte or multiple byte (Burst Mode) data transfer capability for read or write of clock or RAM data.

- ☐ TTL Compatible (V<sub>CC</sub> = 5V)

- □ Low-power CMOS

- $\Box$  I<sub>CC</sub>  $\leq$  2mA (V<sub>CC</sub> = 5 V)

- $\Box$  +3V  $\leq$  V<sub>CC</sub>  $\leq$  9.5V

#### **GENERAL DESCRIPTION**

Many microprocessor applications require a real-time clock and/or memory that can be battery powered with very low power drain. The MK3805N/MK3806N are specifically designed for these applications. The device contains a real-time clock/calendar, 24 bytes of static RAM, an on-chip oscillator, and it communicates with the microprocessor via a simple serial interface. The MK3805N/MK3806N are fabricated using CMOS technology, thus insuring very low power consumption.

The real-time clock/calendar provides seconds, minutes, hours, day, date, month, and year information to the microprocessor. The end of the month date is automatically adjusted for months with less than 31 days, including correction for leap year every 4 years. The clock operates in either the 24 hour or 12 hour format with an AM/PM indicator.

The on-chip oscillator provides a real-time clock source for the clock/calendar. It incorporates a programmable divider

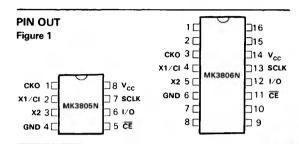

#### PIN DESCRIPTION

#### Table 1

| PIN<br>3805N | PIN<br>3806N | NAME     | DESCRIPTION                         |

|--------------|--------------|----------|-------------------------------------|

| 1            | 3            | ско      | Buffered Sytem Clock Output         |

| 2            | 4            | X1/C1    | Crystal or External Clock Input     |

| 3            | 5            | X2       | Crystal Input                       |

| 4            | 6            | GND      | Power Supply Pin                    |

| 5            | 11           | CE       | Chip Enable for Serial I/O Transfer |

| 6            | 12           | 1/0      | Data Input/Output Pin               |

| 7            | 13           | SCLK     | Shift Clock for Serial I/O Transfer |

| 8            | 14           | $v_{cc}$ | Power Supply Pin                    |

so that a wide variety of crystal frequencies can be accommodated. The oscillator also has an output available that can be connected to the microprocessor clock input. A separately programmable divider provides several different output frequencies for any given crystal frequency. This feature can eliminate having to use a separate crystal or external oscillator for the microprocessor, thereby reducing system cost.

Interfacing the CLOCK/RAM with a microprocessor is greatly simplified using synchronous serial communication. Only 3 lines are required to communicate with the CLOCK/RAM: (1)  $\overline{\text{CE}}$  (chip enable), (2) I/O (data line) and (3) SCLK (shift register clock). Data can be transferred to and from the CLOCK/RAM one byte at a time or in a burst of up to 24 bytes.

#### **TECHNICAL DESCRIPTION**

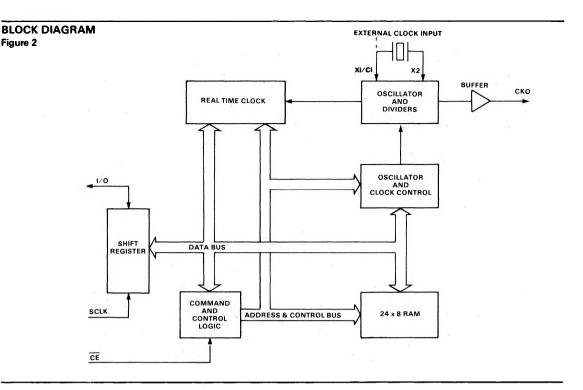

Figure 2 is a block diagram of the CLOCK/RAM chip. Its main elements are the oscillator and divider circuit, oscillator and clock control, the real-time clock/calendar, static RAM, the serial shift register, and the command and control logic.

The shift register is used to communicate with the outside world. Data on the I/O line is either input or output on each shift register clock pulse when the chip is enabled. If the chip is in the input mode, the data on the I/O line is input to the shift register on the rising edge of SCLK. If in the output mode, data is shifted out onto the I/O line on the falling edge of SCLK.

Figure 2

The command and control logic receives the first byte input by the shift register after CE goes active. This byte must be the command byte and will direct further operations within the CLOCK/RAM. The command specifies whether subsequent transfers will be data input or data output, and which register or RAM location will be involved.

A control register provides programmable control of the divider for the internal clock signal, the external clock signal, the crystal type and mode, and the write protect function.

The real-time clock/calendar is accessed via seven registers. These registers control seconds, minutes, hours, day, date, month, and year. Certain bits within these registers also control a run/stop function, 12/24 hour format, and indicate AM or PM (12 hour mode only). These registers can be accessed sequentially in Burst Mode, or randomly in a single byte transfer.

The static RAM is organized as 24 bytes of 8-bits each. They can be accessed either sequentially in burst mode, or randomly in a single byte transfer.

#### **POWER UP**

A clock signal is necessary for correct power up, and it should be noted that a delay exists between power up and the correct power up state of the clock and control registers.

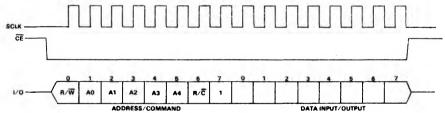

#### **PATA TRANSFER**

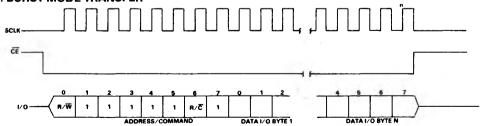

Data Transfer is accomplished under control of the CE and SCLK inputs by an external microcomputer. Each transfer consists of a single byte ADDRESS/COMMAND input followed by a single byte or multiple byte (if Burst Mode is specified) data input or output, as specified by the ADDRESS/COMMAND byte. The serial data transfer occurs with LSB first. MSB last format.

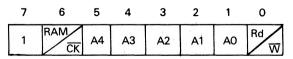

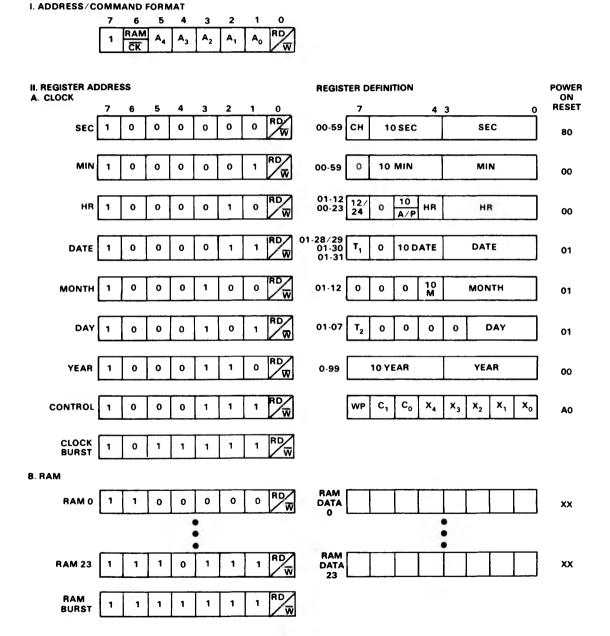

#### ADDRESS/COMMAND BYTE

The ADDRESS/COMMAND Byte is shown below:

As defined, the MSB (bit 7) must be a logical 1; bit 6 specifies a Clock/Calendar/Control register if logical 0 or a RAM register if logical 1; bits 1-5 specify the designated register(s) to be input or output; and the LSB (bit 0) specifies a WRITE operation (input) if logical 0 or READ operation (output) if logical 1.

#### **BURST MODE**

Burst Mode may be specified for either the Clock/ Calendar/Control registers or for the RAM registers by addressing location 31 Decimal (ADDRESS/COMMAND bits 1-5 = logical 1). As before, bit 6 specifies Clock or RAM and bit 0 specifies read or write.

There is no data storage capability at location 31 in either the Clock/Calendar/Control registers or the RAM registers.

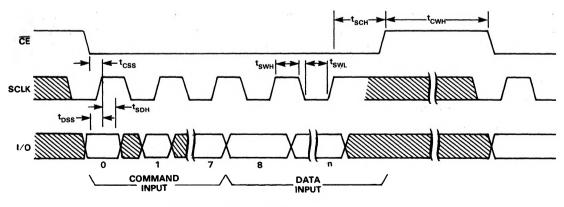

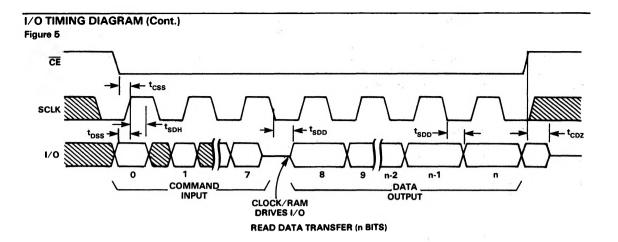

#### SCLK and CE CONTROL

All data transfers are initiated by CE going low. After CE goes low, the next 8 SCLK cycles input an ADDRESS/ COMMAND byte of the proper format. A SCLK cycle is the sequence of a positive edge followed by a negative edge. For data inputs, the data must be valid during the SCLK cycle. If bit 7 is not a logical 1, indicating a valid CLOCK/RAM ADDRESS/COMMAND, the ADDRESS/COMMAND byte is ignored as are all SCLK cycles until CE goes high and returns low to initiate a new ADDRESS/COMMAND transfer. See Figure 3.

ADDRESS/COMMAND bits and DATA bits are input on the

rising edge of SCLK, and DATA bits are output on the falling edge of SCLK.

A data transfer terminates if CE goes high, and the transfer must be reinitiated by the proper ADDRESS/ COMMAND when CE again goes low. The data I/O pin is high impedance when CE is high.

#### **DATA INPUT**

Following the 8 SCLK cycles that input the WRITE Mode ADDRESS/COMMAND byte (bit 0 = logical 0), a DATA byte is input on the rising edge of the next 8 SCLK cycles (per byte, if Burst Mode is specified), Additional SCLK cycles are ignored should they inadvertently occur.

#### **DATA OUTPUT**

Following the 8 SCLK cycles that input the READ Mode ADDRESS/COMMAND byte (bit 0 = logical 1), a DATA byte is output on the falling edge of the next 8 SCLK cycles (per byte, if Burst Mode is specified). Additional SCLK cycles retransmit the data byte(s) should they inadvertently occur, so long as CE remains low. This operation permits continuous Burst Read Mode capability.

#### **DATA TRANSFER SUMMARY**

A data transfer summary is shown in Figure 3.

#### **DATA TRANSFER SUMMARY** Figure 3

#### I. SINGLE BYTE TRANSFER

#### II. BURST MODE TRANSFER

#### NOTES

- 1) Data input sampled on rising edge of clock

- Data output changes on falling edge of clock

- 3) Rising edge of CE terminates operation and resets address/command

| FUNCTION | BYTE<br>N | SCLK |

|----------|-----------|------|

| Crock    | 8         | 72   |

| RAM      | 24        | 200  |

#### **REGISTER DEFINITION**

#### CLOCK/CALENDAR

The Clock/Calendar is contained in 7 addressable / writeable / readable registers, as defined below.

| Address | Function                 | Range (BCD) |

|---------|--------------------------|-------------|

| 0       | Connedad Clock Holt Flag | 00-59       |

|         | Seconds+Clock Halt Flag  | 1           |

| 1       | Minutes                  | 00-59       |

| 2       | Hours/AM-PM/12-24 Mode   | 00-23 or    |

|         |                          | 01-12       |

| 3       | Date                     | 01-28,29,   |

|         |                          | 30,31       |

| 4       | Month                    | 01-12       |

| 5       | Day                      | 01-07       |

| 6       | Year                     | 00-99       |

Data contained in the Clock/Calendar registers is in binary coded decimal format (BCD).

#### **CLOCK HALT FLAG**

Bit 7 of the Seconds Register is defined as the Clock Halt Flag. Bit 7 = logical 1 inhibits the 1 Hz input to the Clock/Calendar. Bit 7 is set to logical 1 on power-up to prevent counting, and it may be set high or low by writing to the seconds register under normal operation of the device.

#### AM-PM/12-24 MODE

Bit 7 of the Hours Register is defined as the 12 or 24 hour mode select bit. When high, the 12 hour mode is selected. In the 12-hour mode, bit 5 is the AM/PM bit with logic high being PM. In the 24-hour mode, bit 5 is the second 10-hour bit (20-23 hours).

#### **TEST MODE BITS**

Bit 7 of the Date Register and Bit 7 of the Day Register are Test Mode Bits utilized in testing the MK3805N/MK3806N. These bits should be logic 0 for normal operation.

#### **CONTROL REGISTER**

The Control Register specifies the crystal mode/frequency to be used, the system clock output frequency, and the WRITE PROTECT Mode for data protection. The Control Register is located at address 7 in the Clock/Calendar/Control address space.

| 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|----|----|----|----|----|----|----|----|

| WP | C1 | СО | X4 | хз | X2 | X1 | хо |

#### **CRYSTAL DIVIDER MODE**

X4 and X3 specify the Crystal frequency divider mode selected.

| X4 | хз | Xtal Mode      | Primary Frequencies                                    |

|----|----|----------------|--------------------------------------------------------|

| 0  | 0  | Binary         | 2 <sup>22</sup> , 2 <sup>21</sup> , 2 <sup>20</sup> Hz |

| 0  | 1  | Microprocessor | 8, 5, 4, 2.5, 2, 1.25, 1 MHz                           |

| 1  | 0  | Baud Rate      | 7.3728, 3.6864, 1.8432 MHz                             |

| 1  | 1  | Color Burst    | 3.5795 MHz                                             |

#### **CRYSTAL DIVIDER PRESCALER**

X2, X1, and X0 specify a particular prescaler divider selection necessary to generate a 1 Hz frequency for the Clock/Calendar. Refer to Table 2 for complete definition.

#### SYSTEM CLOCK OUTPUT

C1 and C0 designate the system clock output frequency selected. The options are X, X/2, X/4, and  $\sim$ 2 kHz. When in the Binary Mode and C1, C0 = '1', the output frequency is 2048 Hz. In any other mode, the output frequency is  $\sim$ 2048 Hz. Refer to Table 3 for complete definition.

#### WRITE PROTECT

Bit 7 of the Control Register is the WRITE PROTECT Flag. Bit 7 is set to logical 1 on power-up, and it may be set high or low by writing to the Control Register. When high, the WRITE PROTECT Flag prevents a write operation to any internal register, including the other bits of the Control Register. Further, logic is included such that the WRITE PROTECT bit may be reset to a logic 0 by a Write operation without altering the other bits of the Control Register.

#### CLOCK/CALENDAR/CONTROL BURST MODE

Address 31 Decimal of the Clock/Calendar/Control Address space specifies Burst Mode operation. In this mode, the 7 Clock/Calendar Registers and the Control Register may be consecutively read or written. Addresses above address 7 (Control Register) are non-existent; only addresses 0-7 are accessible.

#### **RAM**

The static RAM is contained in 24 addressable/writeable/ readable registers, addressed consecutively in the RAM address space beginning at location 0.

#### **RAM BURST MODE**

Address 31 Decimal of the RAM address space specifies Burst Mode operation. In this mode, the 24 RAM registers may be consecutively read or written. Addresses above the maximum RAM address location are non-existent and are not accessible.

#### **REGISTER SUMMARY**

A Register, Data Format summary is shown in Figure 4.

# MICROCOMPUTER CLOCK/RAM ADDRESS/COMMAND, REGISTER, DATA FORMAT SUMMARY

| rigure 4 | Fig | ure | 4 |

|----------|-----|-----|---|

|----------|-----|-----|---|

# CRYSTAL FREQUENCY SELECTION

Table 2

| X4 | хз | X2 | Х1 | хо | f <sub>XTAL</sub> (MHz)<br>Crystal Frequency | Comments                                |

|----|----|----|----|----|----------------------------------------------|-----------------------------------------|

| 0  | 0  | 0  | 0  | 0  | 8.388608                                     | Power on condition                      |

| 0  | 0  | 0  | 0  | 1  | 8.388608                                     |                                         |

| 0  | Ō  | Ō  | 1  | 0  | 4.194304                                     |                                         |

| 0  | Ō  | 0  | 1  | 1  | 4.194304                                     |                                         |

| 0  | 0  | 1  | 0  | 0  | 2.097152                                     |                                         |

| 0  | 0  | 1  | 0  | 1  | 2.097152                                     | •                                       |

| 0  | 0  | 1  | 1  | 0  | 1.048576                                     |                                         |

| 0  | 0  | 1  | 1  | 1  | 0.032768                                     |                                         |

|    |    |    |    |    |                                              | 7 (7)                                   |

| 0  | 1  | 0  | 0  | 0  | 8.000000                                     |                                         |

| 0  | 1  | 0  | 0  | 1  | 5.000000                                     |                                         |

| 0  | 1  | 0  | 1  | O  | 4.000000                                     |                                         |

| 0  | 1  | 0  | 1  | 1  | 2.500000                                     |                                         |

| 0  | 1  | 1  | 0  | 0  | 2.000000                                     |                                         |

| 0  | 1  | 1  | 0  | 1  | 1.250000                                     |                                         |

| 0  | 1  | 1  | 1  | 0  | 1.000000                                     | 0                                       |

| 0  | 1  | 1  | 1  | 1  | 0.031250                                     |                                         |

|    |    |    |    |    |                                              |                                         |

| 1  | 0  | 0  | 0  | 0  | 7.372800                                     | "                                       |

| 1  | 0  | 0  | 0  | 1  | 7.372800                                     |                                         |

| 1  | 0  | 0  | 1  | 0  | 3.686400                                     | y.                                      |

| 1  | 0  | 0  | 1  | 1  | 3.686400                                     |                                         |

| 1  | 0  | 1  | 0  | 0  | 1.843200                                     |                                         |

| 1  | 0  | 1  | 0  | 1  | 1.843200                                     |                                         |

| 1  | 0  | 1  | 1  | 0  | 0.921600                                     |                                         |

| 1  | 0  | 1  | 1  | 1  | 0.028800                                     |                                         |

|    |    |    |    |    |                                              |                                         |

| 1  | 1  | 0  | 0  | 0  | 7.159040                                     | * · · · · · · · · · · · · · · · · · · · |

| 1  | 1  | 0  | 0  | 1  | 7.159040                                     |                                         |

| 1  | 1  | 0  | 1  | 0  | 3.579520                                     |                                         |

| 1  | 1  | 0  | 1  | 1  | 3.579520                                     |                                         |

| 1  | 1  | 1  | 0  | 0  | 1.789760                                     |                                         |

| 1  | 1  | 1  | 0  | 1  | 1.789760                                     |                                         |

| 1  | 1  | 1  | 1  | 0  | 0.894880                                     |                                         |

| 1  | 1  | 1  | 1  | 1  | 0.027965                                     |                                         |

| L  |    |    |    |    | L                                            | <u> </u>                                |

# **CLOCK OUTPUT SELECTION**

Table 3

| C1 | CO | CKO<br>Output Frequency | Comments                        |

|----|----|-------------------------|---------------------------------|

| 0  | 0  | f <sub>XTAL</sub>       | Power on condition  Binary mode |

| 0  | 1  | f <sub>XTAL</sub> ÷ 2   |                                 |

| 1  | 0  | f <sub>XTAL</sub> ÷ 4   |                                 |

| 1  | 1  | 2048 Hz                 |                                 |

#### **ELECTRICAL SPECIFICATIONS**

#### **ABSOLUTE MAXIMUM RATINGS\***

| Voltage on V <sub>CC</sub> relative to GND | 0.5 V to + 12.0 V                        |

|--------------------------------------------|------------------------------------------|

| Voltage on any pin                         | $-0.5 \text{ V to} + \text{V}_{CC} + .5$ |

| Temperature under bias                     | 50°C + 95°C                              |

| Storage Temperature                        | 55°C to +125°C                           |

<sup>\*</sup>Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other condition above those indicated in the operational sections of this specification is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.

### **DC OPERATING CONDITIONS**

-40°C  $\leq T_A \leq$  + 85°C

| SYMBOL          | PARAMETER      | MIN | TYP | MAX | UNIT | NOTES |

|-----------------|----------------|-----|-----|-----|------|-------|

| V <sub>cc</sub> | Supply Voltage | 3.0 | 5.0 | 9.5 | ٧    | 1     |

#### DC ELECTRICAL CHARACTERISTICS

-40°C  $\leq$  T<sub>A</sub>  $\leq$  + 85°C, V<sub>CC</sub> = 5V  $\pm$  10%

| SYMBOL                                           | PARAMETER                                                                                                                                                                                                                                                                                                                                              | MIN                                | TYP | MAX                              | UNIT                          | NOTES                                                                                                                     |

|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----|----------------------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| Icc1 Icc2 ILI ILO VIH VIL VIHX2 VI/OH VI/OL VCKH | Power Supply Current Power Supply Current Input Leakage Current, SCLK and CE Output Leakage Current, I/O Pin Logic "1" Voltage, All Inputs except X1 Logic "0" Voltage, All Inputs Logic "1" Voltage, X2 Input Output Logic "1" Voltage, I/O pin Output Logic "0" Voltage, I/O pin Output Logic "1" Voltage, I/O pin Output Logic "1" Voltage, CKO pin | -1.0<br>-10.0<br>2.0<br>2.4<br>2.4 | 3.5 | 2.0<br>0.1<br>1.0<br>10.0<br>0.8 | mA<br>mA<br>µA<br>V<br>V<br>V | 2<br>3<br>4<br>4<br>1, 5<br>1<br>1(I <sub>OH</sub> =-100μA)<br>1(I <sub>OH</sub> = 1.8 mA)<br>1(I <sub>OH</sub> = -400μA) |

| V <sub>CKL</sub>                                 | Output Logic "O" Voltage, CKO pin                                                                                                                                                                                                                                                                                                                      |                                    |     | 0.4                              | v                             | 1(I <sub>OL</sub> = 4.0 mA)                                                                                               |

#### NOTES:

- 1. All voltages referenced to GND.

- 2. Crystal/Clock Input frequency = 8.4 MHz, outputs open.

- 3. Crystal/Clock Input frequency = 32,768 Hz, outputs open

- 4. Measured with  $V_{CC}$  = 5.0 V,  $0 \le V_I \le 5.0$  V, outputs in high impedance state.

- 5. When X<sub>1</sub> is driven by an external signal, a pull-up resistor is required.

| SYMBOL                             | PARAMETER                                | MIN  | TYP | MAX  | UNIT | NOTES   |

|------------------------------------|------------------------------------------|------|-----|------|------|---------|

| Cı                                 | Capacitance on Input pin                 |      | 6   | 10   | pF   | 6       |

| CIZO                               | Capacitance on I/O pin                   |      | 7   | 12   | pF   | 6       |

| C <sub>I∕O</sub><br>C <sub>X</sub> | Capacitance on XI/CI and X2              |      | 7   | 12   | pF   | 6       |

| fX                                 | Crystal frequency                        | 27   |     | 8400 | kHz  |         |

| tcss                               | CE to SCLK1 set up time                  | 1.0  |     | 1    | μs   | 1,7     |

| tsch                               | SCLKt to CEt hold time                   | 1.0  |     | 1    | μs   | 1,7,12  |

| t <sub>DSS</sub>                   | Input Data to SCLK1 set up time          | 1.0  |     |      | μs   | 1,7     |

| t <sub>SDH</sub>                   | Input Data from SCLK1 hold time          | 100  |     | }    | ns   | 1,7     |

| t <sub>SDD</sub>                   | Output Data from SCLKI delay time        | 300  |     | 1000 | ns   | 1,7,8,9 |

| t <sub>CDZ</sub>                   | CEt to I/O high impedance                |      |     | 500  | ns   | 1,7,8,9 |

| t <sub>SWL</sub>                   | SCLK low time                            | 1.95 |     | ∞    | μs   | İ       |

| tswH                               | SCLK high time                           | 1.95 | 1   | ∞    | μs   | l       |

| fSCLK                              | SCLK frequency                           | DC   | ł   | 250  | kHz  | 1       |

| t <sub>SR</sub> , t <sub>SF</sub>  | SCLK Rise and Fall Time                  |      |     | 1    | μs   | 10      |

| t <sub>CR</sub> , t <sub>CF</sub>  | CKO Rise and Fall Time                   |      | 1   | 50   | ns   | 9,10    |

| tcwH                               | CE high time                             | 2.0  |     | 1    | μs   |         |

| t <sub>INIT</sub>                  | Delay from power XTAL=27 kHz             |      | }   | 500  | ms   | 11      |

|                                    | up till power up XTAL=1 MHz states valid |      |     | 150  | ms   | 11      |

#### NOTES:

- 6. Measured as  $C = 1 \triangle t$ , with  $\triangle V = 3V$ , and unmeasured pins grounded.

- 7. Measured at  $V_{IH} = 2.0 \text{V or } V_{IL} = 0.8 \text{V}$  and 50 ns rise and fall times on inputs.

- Measured at V<sub>OH</sub> = 2.4V and V<sub>OL</sub> = 0.4V.

Load Capacitance = 100 pF

- 10. t<sub>r</sub> and t<sub>f</sub> measured from 0.8V to 2.0V

- 11. t<sub>NTT</sub> is measured from the time V<sub>CC</sub> = 4.5 V and XTAL input is valid until the power up states of the CLOCK/RAM registers are valid.

- 12. tSCH must follow the last rising edge of SCLK during a write cycle in order to allow time to complete a write to the internal register.

#### I/O TIMING DIAGRAM

Figure 5

WRITE DATA TRANSFER (n BITS)

#### ORDERING INFORMATION

There are two types of part numbers for the 3870 family of devices. The generic part number describes the basic device type, the amount of ROM and executable RAM, the desired package type, temperature range and power supply

tolerence. For each customer specific code, additional information defining I/O options and oscillator options will be combined with the information describes in the generic part number to define a customer/code specific device order number.

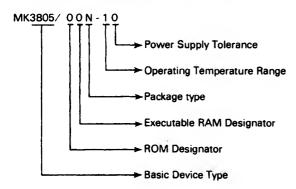

#### **GENERIC PART NUMBER**

An example of the generic part number is shown below.

$$0 = 5 V \pm 10\%$$

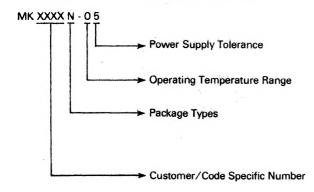

#### **DEVICE ORDER NUMBER**

An example of the device order number is shown below.

The customer/code specific number defines the ROM bit pattern, I/O configuration, oscillator type, and generic part type to be used to satisfy the requirement of a particular customer purchase order. For further information on the ordering of mask ROM devices, the customer should refer to the 3870 Family Technical Manual.

$$0 = +5 V \pm 10\%$$

$5 = +5 V \pm 5\%$