## 64K-BIT MOS READ-ONLY MEMORY

# MK37000(P/J/N) Series

#### **FEATURES**

- ☐ Organization: 8K x 8 Bit ROM JEDEC Pinout

- ☐ Pin compatible with Mostek's BYTEWYDE™ Memory Family

- □ Access Time/Cycle Time

| P/N       | ACCESS | CYCLE  |

|-----------|--------|--------|

| MK37000-5 | 300 ns | 450 ns |

| MK37000-4 | 250 ns | 375 ns |

#### DESCRIPTION

The MK37000 is a N-channel silicon gate MOS Read Only Memory, organized as 8192 words by 8 bits. As a state-of-the-art device, the MK37000 incorporates advanced circuit techniques designed to provide maximum circuit density and reliability with the highest possible performance, while maintaining low power dissipation and wide operating margins. The MK37000 is to be used as a pin/function compatible mask programmable alternative to the 2764 8K x 8 bit EPROM. As a member of the Mostek BYTEWYDE

- ☐ Mask ROM replacement for 2764 EPROM

- □ No Connections allow easy upgrade to future generation higher density ROMs

- ☐ Low power dissipation: 220mW max active, 45mW max standby

- □ CE and OE functions facilitate Bus control

- □ MKB version screened to MIL-STD-883

PIN CONNECTIONS

Memory Family, the MK37000 brings to the memory market a new era of ROM, PROM and EPROM compatibility previously unavailable.

Use of clocked control periphery and a standard static ROM cell makes the MK37000 the lowest power 64K ROM available. Active power is a mere 220mW while standby (CE high) is only 45mW. To provide greater system flexibility an output enable (OE) function has been added using one of the extra pins available on the

## **FUNCTIONAL DIAGRAM (MK37000)** Q<sub>0</sub> Q<sub>1</sub> Q<sub>2</sub> Q<sub>3</sub> Q<sub>4</sub> Q<sub>5</sub> Q<sub>6</sub> Q<sub>7</sub> **OUTPUT BUFFERS** A12 A10. v<sub>cc</sub> Y DECODER A<sub>9</sub> Aρ A7 A<sub>6</sub> A<sub>5</sub> ADDRESS INPUT 65536 BIT **CELL MATRIX** Α3 \_ CE A<sub>1</sub> A<sub>0</sub> **TRUTH TABLE**

OUTPUTS

High-Z

High-Z

DOUT

**POWER**

Standby

Active

Active

|                      | -    |                           |

|----------------------|------|---------------------------|

| NC 1                 | •    | □28 <b>v<sub>cc</sub></b> |

| A <sub>12</sub> 2    |      | □27 NC                    |

| A7 3                 | J    | □26 NC                    |

| A <sub>6</sub> 4     |      | □25 <b>A<sub>8</sub></b>  |

| A <sub>5</sub> 5     |      | □24 <b>A</b> 9            |

| A4 6                 |      | □23 A <sub>11</sub>       |

| A3 7                 |      | □22 <b>OE</b>             |

| A <sub>2</sub> 8     |      | □21 A <sub>10</sub>       |

| A <sub>1</sub> 9     |      | □20 <b>CE</b>             |

| A <sub>0</sub> 10    |      | ⊒19 <b>0</b> 7            |

| a <sub>0</sub> 11 □  |      | □18 <b>Δ</b> 6            |

| <b>a</b> ₁ 12□       |      | □17 Ω <sub>5</sub>        |

| a <sub>2</sub> 13 □  |      | □16 <b>0</b> 4            |

| v <sub>ss</sub> 14 [ |      | ∏15 <b>0</b> ₃            |

| PIN NAMES            |      | ı                         |

| A0 - A12-Address     | NC - | No Connection             |

OE -

v<sub>cc</sub> -

VSS -

**Output Enable**

+5V supply

Ground

X = Don't Care

OE |

Х

VIH

$V_{IL}$

MODE

Deselect

Inhibit

Read

CE

VIН

$V_{1L}$

٧ıı

CE

Chip Enable

Q0 - Q7 - Outputs

## **ABSOLUTE MAXIMUM RATINGS\***

| Voltage on Any Terminal Relative to VSS        | –1.0V to +7V   |

|------------------------------------------------|----------------|

| Operating Temperature T <sub>A</sub> (Ambient) |                |

| Storage Temperature—Ceramic (Ambient)          | 65°C to +150°C |

| Storage Temperature—Plastic (Ambient)          |                |

| Power Dissipation                              | 1 Watt         |

<sup>\*</sup>Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operating sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## RECOMMENDED DC OPERATING CONDITIONS<sup>6</sup>

$(0^{\circ}C \leq T_{A} \leq +70^{\circ}C)$

| SYM | PARAMETER             | MIN  | TYP | MAX             | UNITS | NOTES |

|-----|-----------------------|------|-----|-----------------|-------|-------|

| Vcc | Power Supply Voltage  | 4.5  | 5.0 | 5.5             | V     |       |

| VIL | Input Logic O Voltage | -1.0 |     | 0.8             | V     |       |

| VIH | Input Logic 1 Voltage | 2.0  |     | v <sub>cc</sub> | V     |       |

## DC ELECTRICAL CHARACTERISTICS 6

$(V_{CC} = 5V \pm 10\%) (0^{\circ}C \le T_{A} \le +70^{\circ}C)$

| SYM              | PARAMETER                                                          | MIN | TYP | MAX | UNITS | NOTES |

|------------------|--------------------------------------------------------------------|-----|-----|-----|-------|-------|

| l <sub>CC1</sub> | V <sub>CC</sub> Power Supply Current (Active)                      |     |     | 40  | mA    | 1     |

| I <sub>CC2</sub> | V <sub>CC</sub> Power Supply Current (Standby)                     |     |     | 8   | mA    | 7     |

| l(L)             | Input Leakage Current                                              | -10 |     | 10  | μΑ    | 2     |

| IO(L)            | Output Leakage Current                                             | -10 |     | 10  | μА    | 3     |

| V <sub>OL</sub>  | Output Logic "0" Voltage<br>@ I <sub>OUT</sub> = 3.3mA             |     |     | 0.4 | V     |       |

| VOH              | Output Logic ''1'' Voltage<br>@ I <sub>OUT</sub> = -220 <i>μ</i> A | 2.4 |     |     | V     |       |

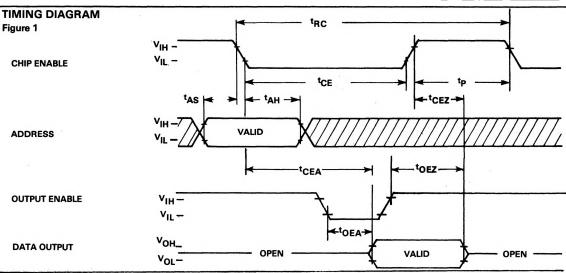

## **AC ELECTRICAL CHARACTERISTICS<sup>6</sup>**

$(V_{CC} = 5V \pm 10\%) (0^{\circ}C \le T_{A} \le +70^{\circ}C)$

|                  |                                     | -   | -4     |     | -5     |       |       |

|------------------|-------------------------------------|-----|--------|-----|--------|-------|-------|

| SYM              | PARAMETER                           | MIN | MAX    | MIN | MAX    | UNITS | NOTES |

| <sup>t</sup> RC  | Read Cycle Time                     | 375 |        | 450 |        | ns    | 4     |

| <sup>t</sup> CE  | CE Pulse Width                      | 250 | 10,000 | 300 | 10,000 | ns    | 4     |

| <sup>t</sup> CEA | CE Access Time                      |     | 250    |     | 300    | ns    | 4     |

| tCEZ             | Chip Enable Data Off Time           |     | 60     |     | 75     | ns    |       |

| <sup>t</sup> AH  | Address Hold Time Referenced to CE  | 60  |        | 75  |        | ns    |       |

| <sup>t</sup> AS  | Address Setup Time Referenced to CE | 0   |        | 0   |        | ns    |       |

| tp               | CE Precharge Time                   | 125 |        | 150 |        | ns    |       |

| <sup>t</sup> OEA | Output Enable Access Time           |     | 80     |     | 100    | ns    |       |

| tOEZ             | Output Enable Data Off Time         |     | 60     |     | 75     | ns    |       |

#### CAPACITANCE

$(0^{\circ}C \leq T_{A} \leq 70^{\circ}C)$

| SYM | PARAMETER          | TYP | MAX | UNITS | NOTES |

|-----|--------------------|-----|-----|-------|-------|

| Cl  | Input Capacitance  | 5   | 8   | pF    | 5     |

| co  | Output Capacitance | 7   | 15  | pF    | 5     |

#### NOTES:

- Current is proportional to cycle rate. I<sub>CC1</sub> is measured at the specified minimum cycle time. Data Outputs open.

- V<sub>IN</sub> = 0V to 5.5V

- Device unselected; V<sub>OUT</sub> = 0V to 5.5V

- Measured with 2 TTL loads and 100pF, transition times = 20ns

- Capacitance measured with Boonton Meter or effective capacitance calculated from the equation:

- $C = \Delta Q$  with  $\Delta V = 3$  volts

- A minimum 2ms time delay is required after the application of V<sub>CC</sub> (+5) before proper device operation is achieved. CE must be at V<sub>IH</sub> for this time period.

- 7. CE high

#### **DESCRIPTION** (Continued)

28 pin DIP. This function matches that found on all of the new BYTEWYDE family of memories available from Mostek.

The use of clocked  $\overline{\text{CE}}$  mode of operation provides an automatic power down mode of operation. The MK37000 features on chip address latches controlled by the  $\overline{\text{CE}}$  input. Once address hold time is met, new address data can be provided to the device in anticipation of a subsequent cycle. It is not necessary to maintain the address up to access time to access valid data. The output enable function controls only the outputs and is not latched by  $\overline{\text{CE}}$ . The  $\overline{\text{CE}}$  input can be used for device selection and the  $\overline{\text{OE}}$  input used to avoid bus conflicts so that outputs can be 'OR'ed together when using multiple devices.

Other system oriented features include fully TTL compatible inputs and outputs. The three state outputs, controlled by the  $\overline{OE}$  input, will drive a minimum of 2 standard TTL loads. The MK37000 operates from a single +5 volt power supply with a wide  $\pm$  10%

tolerance, providing the widest operating margins available. The MK37000 is packaged in the industry standard 28 pin DIP. Pin 1 and 26 are not connected to allow easy upward compatibility with next generation higher density ROM which will use these pins for addresses. Pin 27 is not connected in order to maintain compatibility with RAMs which use this pin as a write enable (WE) control function.

Any application requiring a high performance, high bit density ROM can be satisfied by the MK37000. This device is ideally suited for 8 bit microprocessor systems such as those which utilize the MK3880. It can offer significant cost advantages over PROM.

## **OPERATION**

The MK37000 is controlled by the chip enable  $(\overline{CE})$  and output enable  $(\overline{OE})$  inputs. A negative going edge at the  $\overline{CE}$  input will activate the device and latch the addresses into the on chip address registers. The output buffers, under the control of  $\overline{OE}$ , will become active in  $\overline{CE}$  access

time ( $t_{CEA}$ ) if the output enable access time ( $t_{OEA}$ ) requirement is met. The on chip address register allows addresses to be changed after the specified hold time ( $t_{AH}$ ) in preparation for the next cycle. The outputs will remain valid and active until either  $\overline{CE}$  or  $\overline{OE}$  is returned to the inactive state. After chip deselect time ( $t_{CEZ}$ ) the output buffers will go to a high impedance state. The  $\overline{CE}$  input must remain inactive (high) between subsequent cycles for time  $t_P$  to allow for precharging the nodes of the internal circuitry.

#### MK37000 ROM CODE DATA INPUT PROCEDURE

The preferred method of supplying code data to Mostek is in the form of programmed EPROMs (see table). In addition to the programmed set, Mostek requires an additional set of blank EPROMs for supplying customer code verification. When multiple EPROMs are required to describe the ROM they shall be designated in ascending address space with the numbers 1, 2, 3, etc. As an example, EPROM #1 would start with address space 0000 and go to 07FF for a 2K x 8 device. EPROM #2 would then start at address space 0800 and so on. A

total of (4) 2K x 8 devices would be required to totally describe the address space of the 8K x 8 MK37000.

A paper printout and verification approval letter will accompany each verification EPROM set returned to the customer. Approval is considered to be excepted when the signed verification letter is returned to Mostek. The original set of EPROMs will be retained by Mostek for the duration of the prototyping process.

## Acceptable EPROMs for Code Data

Table 1

| EPROM     | # REQUIRED |

|-----------|------------|

| 2716/2516 | 4          |

| 2732      | 2          |

| 2764      | 1          |