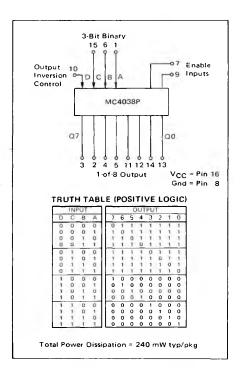

INVERTING/NON-INVERTING ONE-OF-EIGHT DECODER

## MC4300/MC4000 series

# MC4038P\*

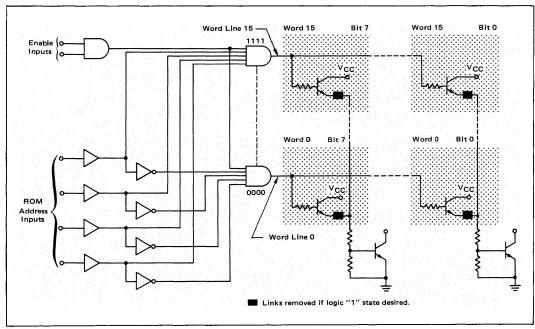

The MC4038P is derived from the XC170 128-Bit Read Only Memory. A 3-bit binary address selects the desired word for the 8-bit output. The inversion control, D, selects half of the memory chip with the bit pattern that defines a 1-of-8 decoder function. When D is a logic "0". A logic "1" on D produces a logic "1" on the selected output.

### Features:

Address times < 45 ns Outputs sink 20 mA Output capacitance < 7.0 pF @ 1.5 V Wired OR capability to 64 memories

### **ENABLE INPUT TRUTH TABLE (POSITIVE LOGIC)**

| Е | E | <b>Q</b> 7       | <b>Q</b> 6 | Q5  | Q4  | Q3 | Q2 | Q1 | QO |

|---|---|------------------|------------|-----|-----|----|----|----|----|

| 0 | 0 | 1                | 1          | 1   | _ 1 | 1  | 1  | 1  | 1  |

| 0 | 1 | 1                | 1          | 1   | 1   | 1  | 1  | 1  | 1  |

| 1 | 0 | 1                | 1          | . 1 | 1   | 1  | 1  | 1  | 1  |

| 1 | 1 | FUNCTION ENABLED |            |     |     |    |    |    |    |

\*P suffix = 16-pin dual in-line plastic package (Case 612).

# INPUT and OUTPUT LOADING FACTORS with respect to MTTL and MDTL families

| FAMILY | MC4000<br>INPUT<br>LOADING<br>FACTOR | MC4000<br>OUTPUT<br>LOADING<br>FACTOR |

|--------|--------------------------------------|---------------------------------------|

| MC4000 | 1.0                                  |                                       |

| MC400  | 1.0                                  |                                       |

| MC2000 | 0.67                                 | Open                                  |

| мсзооо | 0.7                                  | Collector                             |

| MC7400 | 1.0                                  | IOL = 20 mA                           |

| MC830  | 1.15**                               |                                       |

Note: Differences in MC4000 series loading factors result from differences in specifications for each family.

\*\* Applies only when input is being driven by MDTL gate with 2 k ohm pullup resistor. Logic "1" state drive limitations of gates with 6 k ohm pullup resistors reduce drive capability to fan-out of 3.

### MAXIMUM RATINGS

| Rating                         | Symbol           | Value        | Unit |  |

|--------------------------------|------------------|--------------|------|--|

| Supply Voltage                 | V <sub>CC</sub>  | -0.5 to +7.0 | Vdc  |  |

| Supply Operating Voltage Range | v <sub>CC</sub>  | 4.5 to 5.5   | Vdc  |  |

| Input Voltage                  | V <sub>in</sub>  | -1.5 to +5.5 | Vdc  |  |

| Operating Temperature Range    | TA               | 0 to +75     | °C   |  |

| Storage Temperature Range      | T <sub>stg</sub> | -55 to +125  | °C   |  |

### ELECTRICAL CHARACTERISTICS ( $T_A = 0 \text{ to } +75^{\circ}\text{C}$ )

| Characteristic                                                                                                                              | Symbol  | Min  | Max  | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------|---------|------|------|------|

| Address Input Forward Current (V <sub>A</sub> = 0, V <sub>CC</sub> = 5.0 Vdc)                                                               | IF      | 3628 | 1.6  | mAdc |

| Enable Input Forward Current $(V_E = 0, V_{CC} = 5.0 \text{ Vdc})$                                                                          | lF      | -    | 1.6  | mAdc |

| Address Input Leakage Current (VA = 5.5 Vdc, VCC = 5.0 Vdc)                                                                                 | IR      | D -  | 100  | μAdc |

| Enable Input Leakage Current (V <sub>E</sub> = 5.5 Vdc, V <sub>CC</sub> = 5.0 Vdc)                                                          | IR      |      | 100  | μAdc |

| Logical "0" Output Voltage<br>(I <sub>OL</sub> = 20 mAdc, V <sub>IL</sub> = 0.9 Vdc, V <sub>IH</sub> = 2.0 Vdc, V <sub>CC</sub> = 4.75 Vdc) | VOL     | -    | 0.45 | Vdc  |

| Logical "1" Output Leakage Current (VIL = 0.9 Vdc, V <sub>IH</sub> = 2.0 Vdc, V <sub>CEX</sub> = 7.0 Vdc, V <sub>CC</sub> = 5.25 Vdc)       | ICEX    | -    | 100  | μAdc |

| Power Supply Drain Current                                                                                                                  |         |      |      | mAdc |

| (Memory Enabled, V <sub>CC</sub> = 5.25 Vdc)                                                                                                | IPD max |      | 73   | ĺ    |

| (Memory Disabled, V <sub>CC</sub> = 5.25 Vdc)                                                                                               | IPD min | 1 41 | 55   |      |

### SWITCHING TIMES (V<sub>CC</sub> = 5.0 Vdc)

| Positive Input Address to Positive Output           |                                             | t++ | - | 45 | ns |

|-----------------------------------------------------|---------------------------------------------|-----|---|----|----|

| Negative Input Address to Negative Output           | 1                                           | t   | - | 45 | ns |

| Positive Input Address or Enable to Negative Output | I <sub>OL</sub> = 10 mA<br>driving<br>30 pF | t+- | - | 45 | ns |

| Negative Input Address or Enable to Positive Output |                                             | t-+ |   | 45 | ns |