## LINEAR/DIGITAL INTERFACE CIRCUITS

# MC1582L

## MONOLITHIC DUAL MDTL/MTTL LINE DRIVER

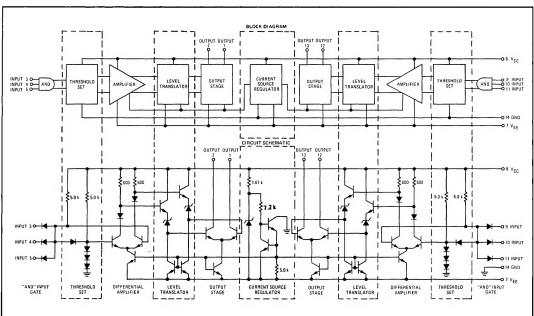

. . . designed with a three-input AND gate input circuit. The differential output current switches in response to an MDTL or MTTL compatible input voltage level. Typical applications include driving twisted-pair transmission lines, line sharing, and logic level translation.

- Low Propagation Delay Time − 20 ns max

- Wide Common-Mode Output Voltage Range +9.0/-3.0 Volts

- High Output Impedance 7.0 k Ohms @ 10 MHz

- 3-Input AND Gate

- Device Compatibility with Other Members of the Line Driver/Receiver Series

## DUAL MDTL/MTTL LINE DRIVER INTEGRATED CIRCUIT

MONOLITHIC SILICON EPITAXIAL PASSIVATED

See Packaging Information Section for outline dimensions.

# MAXIMUM RATINGS ( $T_A = +25^{\circ}C$ unless otherwise noted)

| Rating                                                                                                               | Symbol                             | Value        | Unit                     |

|----------------------------------------------------------------------------------------------------------------------|------------------------------------|--------------|--------------------------|

| Power Supply Voltage                                                                                                 | V <sub>CC</sub><br>V <sub>EE</sub> | +7.0<br>-7.0 | Vdc                      |

| Input Signal Voltage                                                                                                 | Vin                                | +30          | Volts                    |

| Power Dissipation (Package Limitation) Ceramic Dual In-Line Package Derate above T <sub>A</sub> = +25 <sup>o</sup> C | P <sub>D</sub>                     | 575<br>3.85  | mW<br>mW/ <sup>O</sup> C |

| Operating Temperature Range                                                                                          | TA                                 | -55 to +125  | °c                       |

| Storage Temperature Range                                                                                            | T <sub>stg</sub>                   | -65 to +175  | °c                       |

# ELECTRICAL CHARACTERISTICS (Each Line Driver, V<sub>CC</sub> = +5.0 Vdc, V<sub>EE</sub> = -5.0 Vdc, T<sub>A</sub> = +25°C unless otherwise noted)

| Characteristic                                                                                                  | Figure | Symbol                                                            | Min                    | Тур                    | Max                 | Unit         |

|-----------------------------------------------------------------------------------------------------------------|--------|-------------------------------------------------------------------|------------------------|------------------------|---------------------|--------------|

| Operating Supply Currents                                                                                       | 1      | ICC<br>IEE                                                        | -                      | 8.0<br>25              | 10<br>30            | mA           |

| Input Leakage Current                                                                                           | 1      | I <sub>R</sub>                                                    | _                      | 0.04                   | 0.1                 | μА           |

| Input Current T <sub>A</sub> = -55°C T <sub>A</sub> = +25°C T <sub>A</sub> = +125°C T <sub>A</sub> = +125°C     | 1      | lin                                                               | -<br>-<br>-            | 0.72<br>0.70<br>0.63   | 1.0<br>1.0<br>1.0   | mA           |

| Output Leakage Current                                                                                          | 1      | ICEX                                                              | _                      | 0.1                    | 0.2                 | μΑ           |

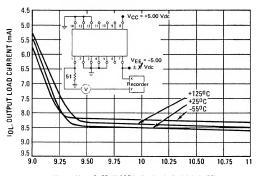

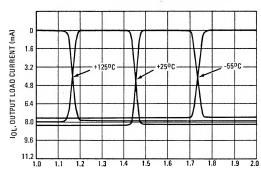

| Output Load Current $T_A = -55^{\circ}C$ $T_A = +25^{\circ}C$ $T_A = +125^{\circ}C$ $T_A = +125^{\circ}C$       | 1      | lOL                                                               | 6.5<br>6.9<br>6.8      | 8.1<br>8.6<br>8.5      | 9.8<br>10.4<br>10.2 | mA           |

| Output Load Current Match $T_A = -55^{\circ}C$ $T_A = +25^{\circ}C$ $T_A = +125^{\circ}C$ $T_A = +125^{\circ}C$ | 2      | △IOL                                                              | <del>-</del><br>-<br>- | 0.7<br>0.8<br>0.8      | _<br>_<br>_         | mA           |

| Input Voltage Transition Width*  TA = -55°C  TA = +25°C  TA = +125°C                                            |        | VTR                                                               | -<br>-<br>-            | 50<br>40<br>50         | <u>-</u><br>-<br>-  | mV           |

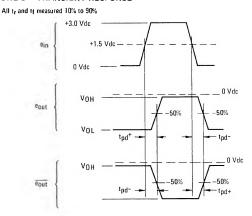

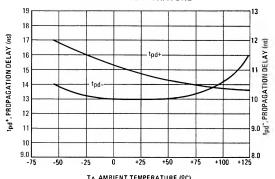

| Switching Times Propagation Delay Time  Rise Time Fall Time                                                     | 3      | t <sub>pd</sub> + t <sub>pd</sub> - t <sub>r</sub> t <sub>f</sub> | -<br>-<br>-            | 15<br>13<br>8.0<br>7.0 | 20<br>18<br>-<br>-  | ns           |

| Threshold Voltage $T_A = -55^{\circ}C$ $T_A = +25^{\circ}C$ $T_A = +125^{\circ}C$ $T_A = +125^{\circ}C$         | 3      | V <sub>TH</sub>                                                   | 0.9<br>1.1<br>0.9      | 1.74<br>1.45<br>1.16   | 2.0<br>1.8<br>1.5   | Volts        |

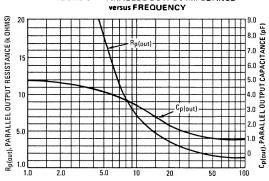

| Parallel Output Impedance (f = 5.0 MHz)<br>Capacitance<br>Resistance                                            |        | C <sub>p(out)</sub><br>R <sub>p(out)</sub>                        | -                      | 10<br>18               | -<br>-              | pF<br>k ohms |

| Common-Mode Output Voltage Range<br>T <sub>A</sub> = -55 to +125 <sup>0</sup> C                                 | 4      | CMVR <sub>out</sub>                                               | +9.0<br>-3.0           | +10<br>-3.3            | -                   | Volts        |

| Power Supply Operating Range                                                                                    |        | V <sub>CC</sub>                                                   | +4.75<br>-6.0          | +5.0<br>-5.0           | +6.0<br>-4.75       | Vdc          |

| Input Breakdown Voltage                                                                                         |        | VIHH                                                              | 15                     | 30                     | -                   | Volts        |

| Power Dissipation                                                                                               |        | PD                                                                | _                      | 140                    | 170                 | mW           |

<sup>\*</sup>Measured from points of unity gain with a 50 ohm load. Ground all unused input pins to assure correct device biasing.

### **CHARACTERISTIC DEFINITIONS**

+5.0 Vdc

-5.0 Vdc

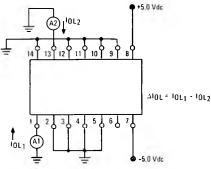

FIGURE 1 - TERMINAL CURRENTS

6

+5 Vdc

FIGURE 2 - OUTPUT CURRENT MATCH

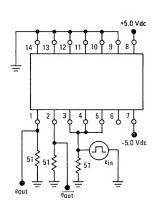

### FIGURE 3 - TRANSIENT RESPONSE

# FIGURE 4 ~ COMMON-MODE OUTPUT VOLTAGE RANGE • +5.0 Vdc — +1.5 Vdc - 0 Vdc Common-Mode Output Voltage Range = The Value of V which causes a 10% shift in the dc level eout or eout whichever occurs first. -5.0 Vdc 51 ± POWER SUPPLY \* eout ein eout

#### TYPICAL CHARACTERISTICS

FIGURE 5 - OUTPUT LOAD CURRENT versus SUPPLY OPERATING VOLTAGE AND TEMPERATURE

VCC + VEE, SUPPLY OPERATING VOLTAGE (VOLTS)

FIGURE 6 - OUTPUT LOAD CURRENT versus INPUT VOLTAGE AND TEMPERATURE

ein, INPUT VOLTAGE (VOLTS)

FIGURE 7 - PROPAGATION DELAY TIME versus AMBIENT TEMPERATURE

TA, AMBIENT TEMPERATURE (°C)

## FIGURE 8 - PARALLEL OUTPUT IMPEDANCE

f, FREQUENCY (MHz)

#### APPLICATIONS INFORMATION

#### Line Driver/Receiver Family Characteristics

The Motorola line driver/receiver series provides interface circuits for driving digital data transmission lines e.g., coaxial cable or twisted pair. The digital data transmission is via a balanced differential mode. The line drivers and receivers are designed to provide high common-mode noise rejection, present high impedances to the transmission line and have low propagation times. A feature of the drivers is the capability to operate in a party-line mode whereby a number of drivers can be connected to a single line. This series provides drivers and receivers compatible with MRTL, MDTL, MTTL and MECL. The five circuits of the family are:

MC1580L Dual Line Driver/Receiver

MC1581L Dual MECL Receiver

MC1582L Dual MDTL/MTTL Driver

MC1583L Dual Receiver (Open Collector)

MC1584L Dual Receiver (Active Pullup)

Figure 9 indicates line drivers and receivers recommended for interfacing with each of the various digital logic families.

FIGURE 9

| Digital Logic Family | Driver             | Receiver           |  |  |  |

|----------------------|--------------------|--------------------|--|--|--|

| MECL                 | MC1580L            | MC1581L            |  |  |  |

| MDTL                 | MC1582L            | MC1583L<br>MC1584L |  |  |  |

| MTTL                 | MC1582L            | MC1583L<br>MC1584L |  |  |  |

| MRTL                 | MC1580L<br>MC1582L | MC1583L            |  |  |  |

These five circuits are extremely useful in numerous applications other than line drivers and receivers. The differential amplifier input of the receiver makes it useful in applications such as voltage comparators, waveform generators and high-input-impedance buffers. The drivers and receivers are useful as logic level translators.

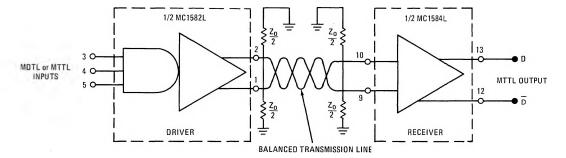

The MC1582L in Figure 10 serves as the line driver for a balanced differential transmission line. The driver input and receiver outputs of the MC1584L receiver are compatible with MTTL circuits.

The output stage of the driver switches a current source between the two driver outputs in response to the input logic signals. Hence, a voltage differential that is a function of the line termination impedances is created on the twisted pair and at the input of the receiver. The receiver is designed to reject +3.5/-3.5 Volts of commonmode voltage signals which may be present due to ground loop currents and noise coupled from nearby transmission lines.

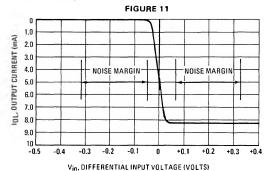

While common-mode noise is the major concern in a twisted part transmission line; a good data transmission system must offer some immunity from differential-mode voltages that may be present due to mismatches in termination impedances. The drivers and receivers of the MC1580 Series are designed with this requirement in mind. The exact amount of noise immunity depends on line impedances but the following example shows how differential-mode noise immunity is calculated for a given system. For a line with a characteristic impedance of Z<sub>O</sub>, calculate the minimum differential input voltage from the equation.

$$\pm V_{in} = \frac{I_0(min) \times Z_0}{4}$$

For a 170-ohm line,  $V_{in} = \frac{(6.9) (170)}{4} = 0.29$  Volts.

Since the receivers recommended for use with the MC1582L driver require 50 mV maximum input differential to maintain the output state, the worst case differential-mode noise immunity is 0.26 V. (See Figure 11).

FIGURE 10 - MDTL, MTTL COMPATIBLE TRANSMISSION SYSTEM

#### **APPLICATIONS INFORMATION** (continued)

Hence the direct coupling of the driver and receiver to the line provides a built-in differential-mode noise immunity. The direct coupling also matches the line at all frequencies (often a problem with ac coupling lines). The recovery problem in ac coupling devices at high-signal repetition rates is also eliminated.

The high output impedance of the MC1582L and the high input impedances of the MC1584L drivers minimize impedance discontinuities on the transmission line and allow many drivers and receivers to be connected to the line.

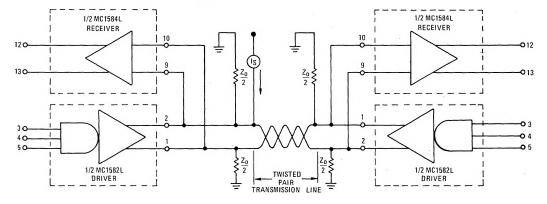

Use of the MC1584L in a bi-directional MDTL or MTTL compatible transmission system is shown in Figure 12. The MC1582L drivers of Figure 12 are connected so that the current sources from both drivers pull current from the same wire of the twisted pair when both drivers are transmitting logic "0" signals. The external current source, Ig, supplies the current required by one driver. The current for the other driver is drawn from the termination impedances, creating a voltage differential across the line. When either

driver transmits a logic "1", a voltage difference of the opposite polarity is created across the line. For a system with two drivers the current source  $\{I_S\}$  can be supplied by a 600-ohm resistor connected to  $\pm 5.0$  volts.

If additional drivers are connected to the line, a matching current source is connected for each added driver. The current sources are connected to the line so that when all drivers are transmitting logic "0"s, the difference in current drawn from the terminating resistors of the two wires in the twisted pair is equal to one current source (8.6 mA). The current sources should also be connected so that when any driver transmits a logic "1" then a current difference of the opposite polarity exists. The matching current source should be the companion circuit on the MC1580L driver chip. The difference in amplitude of the current sources on a single chip is specified to allow the system designer to calculate the maximum current source mismatch,  $\Delta l_{\rm OL}$ , and hence the maximum number of drivers that can be connected to a given transmission line.

FIGURE 12 - BI-DIRECTIONAL TRANSMISSION