# LR38617

#### **DESCRIPTION**

The LR38617 is a CMOS timing generator IC which generates timing pulses for driving 3 300 k/3 370 k-pixel CCD area sensors and processing pulses.

#### **FEATURES**

- Designed for 1/1.8-type 3 300 k/3 370 k-pixel CCD area sensors

- Frequency of driving horizontal CCD: 18.00 MHz

- In monitoring mode, it can be obtained 30 fields/s.

- External shutter control function with serial data input is possible

- +3.3 V and +4.5 V power supplies

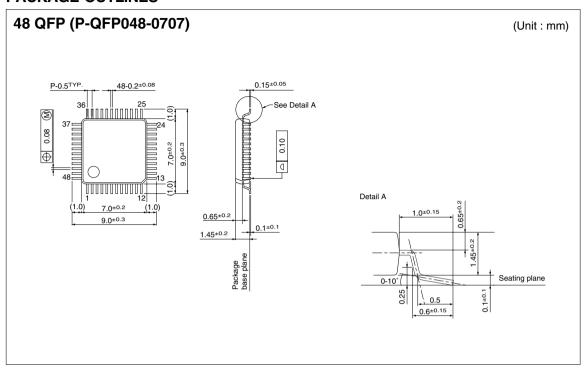

- Package:

48-pin QFP (P-QFP048-0707) 0.5 mm pin-pitch

# Timing Generator IC for 3 300 k/3 370 k-pixel CCDs

#### PIN CONNECTIONS

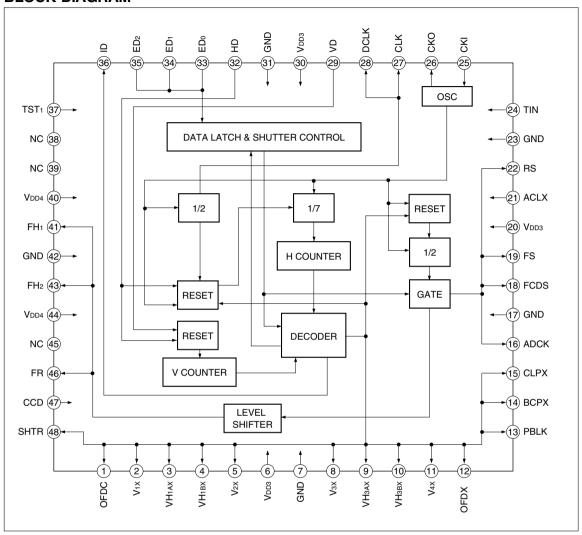

#### **BLOCK DIAGRAM**

# **PIN DESCRIPTION**

| PIN NO. | SYMBOL             |             | POI ARITV | PIN NAME                  | AME DESCRIPTION                                                                                                 |  |  |  |

|---------|--------------------|-------------|-----------|---------------------------|-----------------------------------------------------------------------------------------------------------------|--|--|--|

| FIN NO. | STWIDOL            | IO STINIDOL | FOLANITI  | Control pulse output      | DESCRIFTION                                                                                                     |  |  |  |

| 1       | OFDC               | О3          | П         | for OFD voltage           | A pulse to control OFD voltage.                                                                                 |  |  |  |

|         |                    |             |           | Vertical transfer         | A vertical transfer pulse for the CCD.                                                                          |  |  |  |

| 2       | 2 V1X              |             |           |                           | ·                                                                                                               |  |  |  |

|         |                    |             |           | pulse output 1            | Connect to V <sub>1</sub> x pin of vertical driver IC.  A pulse that transfers the charge of the photo-diode to |  |  |  |

|         | Milan              | 00          |           | Readout pulse output 1A   |                                                                                                                 |  |  |  |

| 3       | VH <sub>1</sub> AX | O3          | Ш         |                           | the vertical shift register.                                                                                    |  |  |  |

|         |                    |             |           |                           | Connect to VH1AX pin of vertical driver IC.                                                                     |  |  |  |

| 4       | VH1BX              | 00          |           | Readout pulse             | A pulse that transfers the charge of the photo-diode to                                                         |  |  |  |

| 4       | VH1BX              | O3          | Ш         | output 1B                 | the vertical shift register.                                                                                    |  |  |  |

|         |                    |             |           | Mautiaal tuanafan         | Connect to VH1BX pin of vertical driver IC.                                                                     |  |  |  |

| 5       | V <sub>2</sub> X   | О3          |           | Vertical transfer         | A vertical transfer pulse for the CCD.                                                                          |  |  |  |

|         | .,                 |             |           | pulse output 2            | Connect to V2x pin of vertical driver IC.                                                                       |  |  |  |

| 6       | VDD3               |             | _         | Power supply              | Supply of +3.3 V power.                                                                                         |  |  |  |

| 7       | GND                | _           | _         | Ground                    | A grounding pin.                                                                                                |  |  |  |

| 8       | 8 V3X              |             |           | Vertical transfer         | A vertical transfer pulse for the CCD.                                                                          |  |  |  |

|         |                    |             |           | pulse output 3            | Connect to V <sub>3</sub> x pin of vertical driver IC.                                                          |  |  |  |

|         | VНзах              | О3          | I         | Readout pulse output 3A   | A pulse that transfers the charge of the photo-diode to                                                         |  |  |  |

| 9       |                    |             |           |                           | the vertical shift register.                                                                                    |  |  |  |

|         |                    |             |           |                           | Connect to VH3AX pin of vertical driver IC.                                                                     |  |  |  |

|         |                    | О3          | 7.5       | Readout pulse output 3B   | A pulse that transfers the charge of the photo-diode to                                                         |  |  |  |

| 10      | VНзвх              |             | I         |                           | the vertical shift register.                                                                                    |  |  |  |

|         |                    |             |           |                           | Connect to VH3BX pin of vertical driver IC.                                                                     |  |  |  |

| 11      | V <sub>4</sub> X   | О3          | O3 ]      | Vertical transfer         | A vertical transfer pulse for the CCD.                                                                          |  |  |  |

| L.,     | • 170              |             |           | pulse output 4            | Connect to V <sub>4</sub> x pin of vertical driver IC.                                                          |  |  |  |

|         |                    |             |           |                           | A pulse that sweeps the charge of the photo-diode for                                                           |  |  |  |

| 12      | OFDX               | О3          |           | OFD pulse output          | the electronic shutter. Connect to OFD pin of the CCD                                                           |  |  |  |

| '-      | OIDX               | 00          |           | Of D pulse output         | through the vertical driver IC and DC offset circuit.                                                           |  |  |  |

|         |                    |             |           |                           | Held at H level in normal mode.                                                                                 |  |  |  |

|         |                    |             |           |                           | A pulse for pre-blanking. This pulse is controlled by                                                           |  |  |  |

|         |                    |             |           |                           | serial data BLKCNT.                                                                                             |  |  |  |

| 13      | PBLK               |             |           |                           | BLKCNT = H; This pulse stays low during the                                                                     |  |  |  |

|         |                    | 02          | 75        | Pre-blanking pulse output | absence of effective pixels within the                                                                          |  |  |  |

|         |                    | O3          |           |                           | vertical blanking or during the                                                                                 |  |  |  |

|         |                    |             |           |                           | sweepout signal.                                                                                                |  |  |  |

|         |                    |             |           |                           | BLKCNT = L; Continuous pulse                                                                                    |  |  |  |

|         |                    |             |           |                           | The output phase of PBLK is selected by serial data.                                                            |  |  |  |

| PIN NO. | SYMBOL           | IO SYMBOL | POLARITY   | PIN NAME DESCRIPTION |                                                               |       |       |  |  |       |       |       |  |  |  |                             |

|---------|------------------|-----------|------------|----------------------|---------------------------------------------------------------|-------|-------|--|--|-------|-------|-------|--|--|--|-----------------------------|

|         |                  |           |            |                      | A pulse to clamp the optical black signal.                    |       |       |  |  |       |       |       |  |  |  |                             |

|         |                  |           |            |                      | This pulse is controlled by serial data BCPCNT.               |       |       |  |  |       |       |       |  |  |  |                             |

|         |                  |           |            |                      | BCPCNT = H; This pulse stays high during the                  |       |       |  |  |       |       |       |  |  |  |                             |

| , ,     | DODY             | 00        | 7.5        | Optical black clamp  | absence of effective pixels within the                        |       |       |  |  |       |       |       |  |  |  |                             |

| 14      | BCPX             | O3        | T          | pulse output         | vertical blanking or during the                               |       |       |  |  |       |       |       |  |  |  |                             |

|         |                  |           |            |                      | sweepout signal.                                              |       |       |  |  |       |       |       |  |  |  |                             |

|         |                  |           |            |                      | BCPCNT = L; This pulse stays high during sweepout             |       |       |  |  |       |       |       |  |  |  |                             |

|         |                  |           |            |                      | signal.                                                       |       |       |  |  |       |       |       |  |  |  |                             |

| 15      | CLDY             | 0         | 7.5        | Claman mulas autout  | A pulse to clamp the dummy outputs of the CCD signal.         |       |       |  |  |       |       |       |  |  |  |                             |

| 15      | CLPX             | O3        | T          | Clamp pulse output   | This pulse stays high during the sweepout period.             |       |       |  |  |       |       |       |  |  |  |                             |

| 10      | ADCK             | O6MA3     | П          | AD alask sutaut      | An output pin for AD converter. The output phase of           |       |       |  |  |       |       |       |  |  |  |                             |

| 16      | ADCK             | ObiviA3   | 1          | AD clock output      | ADCK is selected by serial data in 90° steps.                 |       |       |  |  |       |       |       |  |  |  |                             |

| 17      | GND              | ı         | ı          | Ground               | A grounding pin.                                              |       |       |  |  |       |       |       |  |  |  |                             |

|         |                  |           |            |                      | A pulse to clamp the feed-through level for the CCD.          |       |       |  |  |       |       |       |  |  |  |                             |

| 18      | FCDS             | O6MA3     |            | CDS pulse output 1   | The output phase and output polarity of FCDS are              |       |       |  |  |       |       |       |  |  |  |                             |

|         |                  |           | T          |                      | selected by serial data.                                      |       |       |  |  |       |       |       |  |  |  |                             |

|         |                  | O6MA3     |            |                      | A pulse to sample-hold the signal for the CCD.                |       |       |  |  |       |       |       |  |  |  |                             |

| 19      | FS               |           |            | CDS pulse output 2   | The output phase and output polarity of FS are selected       |       |       |  |  |       |       |       |  |  |  |                             |

|         |                  |           | T          |                      | by serial data.                                               |       |       |  |  |       |       |       |  |  |  |                             |

| 20      | V <sub>DD3</sub> | -         | -          | Power supply         | Supply of +3.3 V power.                                       |       |       |  |  |       |       |       |  |  |  |                             |

|         |                  | ICU3      |            | All clear input      | An input pin for resetting all internal circuits at power-on. |       |       |  |  |       |       |       |  |  |  |                             |

| 21      | ACLX             |           | -          |                      | Connect to VDD3 through the diode and GND through             |       |       |  |  |       |       |       |  |  |  |                             |

|         |                  |           |            |                      | the capacitor.                                                |       |       |  |  |       |       |       |  |  |  |                             |

|         |                  | O6MA3     | floor      | S/H pulse output     | A pulse to sample-hold the signal for the CDS circuit.        |       |       |  |  |       |       |       |  |  |  |                             |

| 22      | RS               |           |            |                      | The output phase and output polarity of RS are selected       |       |       |  |  |       |       |       |  |  |  |                             |

|         |                  |           | T          |                      | by serial data.                                               |       |       |  |  |       |       |       |  |  |  |                             |

| 23      | GND              | _         | -          | Ground               | A grounding pin.                                              |       |       |  |  |       |       |       |  |  |  |                             |

| 24      | TIN              | IC3       | -          | Test input           | A test pin. Set to L level in normal mode.                    |       |       |  |  |       |       |       |  |  |  |                             |

| 25      | CKI              | OSCI3     | _          | Clock input          | An input pin for reference clock oscillation.                 |       |       |  |  |       |       |       |  |  |  |                             |

|         |                  |           | 55510      |                      | 55515                                                         | 55010 | 300.0 |  |  | 30010 | 30010 | 30010 |  |  |  | The frequency is 36.00 MHz. |

| 26      | СКО              | OSCO3     | _          | Clock output         | An output pin for reference clock oscillation.                |       |       |  |  |       |       |       |  |  |  |                             |

|         |                  | 20000     |            |                      | The output is the inverse of CKI (pin 25).                    |       |       |  |  |       |       |       |  |  |  |                             |

| 27      | CLK              | K O6MA3   | $\prod$    | Clock output         | An output pin to generate HD and VD pulses.                   |       |       |  |  |       |       |       |  |  |  |                             |

|         | OLI (            | 001111110 | 1 []       |                      | The frequency is 18.00 MHz.                                   |       |       |  |  |       |       |       |  |  |  |                             |

|         | DCLK             |           |            |                      | An output pin for DSP IC. The frequency is 18.00 MHz.         |       |       |  |  |       |       |       |  |  |  |                             |

| 28      |                  | O6MA3     | <b>/</b> 3 | Clock output         | The output phase of DCLK is selected by serial data in        |       |       |  |  |       |       |       |  |  |  |                             |

|         |                  |           |            |                      | 90° steps.                                                    |       |       |  |  |       |       |       |  |  |  |                             |

| 29      | VD               | IC3       |            | Vertical reference   | An input pin for reference of vertical pulse.                 |       |       |  |  |       |       |       |  |  |  |                             |

|         |                  |           |            | pulse input          | Connect to VD pin of DSP IC.                                  |       |       |  |  |       |       |       |  |  |  |                             |

| 30      | V <sub>DD3</sub> | _         | _          | Power supply         | Supply of +3.3 V power.                                       |       |       |  |  |       |       |       |  |  |  |                             |

| 31      | GND              | -         | _          | Ground               | A grounding pin.                                              |       |       |  |  |       |       |       |  |  |  |                             |

| PIN NO. | SYMBOL           | IO SYMBOL | POLARITY | PIN NAME                  | DESCRIPTION                                                  |                  |                                                 |  |  |  |

|---------|------------------|-----------|----------|---------------------------|--------------------------------------------------------------|------------------|-------------------------------------------------|--|--|--|

| 32      | HD               | IC3       |          | 100                       | ır                                                           | Horizontal drive | An input pin for reference of horizontal pulse. |  |  |  |

| 32      |                  |           |          | pulse input               | Connect to HD pin of DSP IC.                                 |                  |                                                 |  |  |  |

| 33      | 3 EDo ICSU3 -    |           |          | Ctualia a mula a immust   | An input pin for the strobe pulse, to control the functions  |                  |                                                 |  |  |  |

| 33      | ED <sub>0</sub>  | 10303     | _        | Strobe pulse input        | of LR38617. For details, see "Serial Data Control".          |                  |                                                 |  |  |  |

|         |                  |           |          | Chift register alcole     | An input pin for the clock of the shift register, to control |                  |                                                 |  |  |  |

| 34      | ED <sub>1</sub>  | ICSU3     | _        | Shift register clock      | the functions of LR38617. For details, see "Serial Data      |                  |                                                 |  |  |  |

|         |                  |           |          | input                     | Control".                                                    |                  |                                                 |  |  |  |

|         |                  |           |          | Shift register data       | An input pin for the data of the shift register, to control  |                  |                                                 |  |  |  |

| 35      | ED <sub>2</sub>  | ICSU3     | _        | Shift register data input | the functions of LR38617. For details, see "Serial Data      |                  |                                                 |  |  |  |

|         |                  |           |          | input                     | Control".                                                    |                  |                                                 |  |  |  |

| 36      | ID               | O3        |          | Line index pulse          | The pulse is used in the color separator.                    |                  |                                                 |  |  |  |

| 30      | טו               | 3         | ] []     | output                    | The signal switches between high and low at every line.      |                  |                                                 |  |  |  |

| 37      | TST <sub>1</sub> | ICD4      | _        | Test pin 1                | A test pin. Set open or to L level in normal mode.           |                  |                                                 |  |  |  |

| 38      | NC               | ı         | _        | No connection             | No connection.                                               |                  |                                                 |  |  |  |

| 39      | NC               | ı         | _        | No connection             | No connection.                                               |                  |                                                 |  |  |  |

| 40      | VDD4             | -         | _        | Power supply              | Supply of +4.5 V power.                                      |                  |                                                 |  |  |  |

| 41      | 41 FH1 O6MA43    |           | Ш        | Horizontal transfer       | A horizontal transfer pulse for the CCD.                     |                  |                                                 |  |  |  |

| 41      | ГПІ              | OdiviA43  | ] []     | pulse output 1            | Connect to <i>∲</i> H1 pin of the CCD.                       |                  |                                                 |  |  |  |

| 42      | GND              | ı         | _        | Ground                    | A grounding pin.                                             |                  |                                                 |  |  |  |

| 43      | FH2              | O6MA43    | Ш        | Horizontal transfer       | A horizontal transfer pulse for the CCD.                     |                  |                                                 |  |  |  |

| 43      | ГП2              | OdiviA43  | ШΙ       | pulse output 2            | Connect to ∮H₂ pin of the CCD.                               |                  |                                                 |  |  |  |

| 44      | V <sub>DD4</sub> | ı         | _        | Power supply              | Supply of +4.5 V power.                                      |                  |                                                 |  |  |  |

| 45      | NC               | ı         | _        | No connection             | No connection.                                               |                  |                                                 |  |  |  |

| 46      | FR               | O6MA43    | L        | Reset pulse output        | A pulse to reset the charge of output circuit.               |                  |                                                 |  |  |  |

| 40      | ГN               | OdiviA43  | 43       | neset puise output        | The output phase of FR is selected by serial data.           |                  |                                                 |  |  |  |

|         |                  |           |          | CCD selection input       | An input pin to select CCD.                                  |                  |                                                 |  |  |  |

| 47      | CCD              | ICU4      | _        |                           | L level : Aspect ratio 4:3 CCD                               |                  |                                                 |  |  |  |

|         |                  |           |          |                           | H level or open : Aspect ratio 3:2 CCD                       |                  |                                                 |  |  |  |

| 48      | SHTR             | О3        | $\prod$  | Trigger output            | A trigger pulse for effective signal period.                 |                  |                                                 |  |  |  |

IC3 : Input pin (CMOS level)

ICU3 : Input pin (CMOS level with pull-up resistor)

ICSU3 : Input pin (CMOS schmitt-trigger level with pull-up

resistor)

ICU4 : Input pin (CMOS level with pull-up resistor) ICD4 : Input pin (CMOS level with pull-down resistor)

OSCO3 : Output pin for oscillation

5

О3

OSCI3

: Output pin (output high level is VDD3.)

O6MA3 : Output pin (output high level is VDD3.)

O6MA43: Output pin (output high level is VDD4.)

: Input pin for oscillation

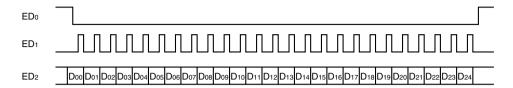

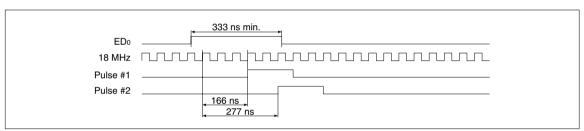

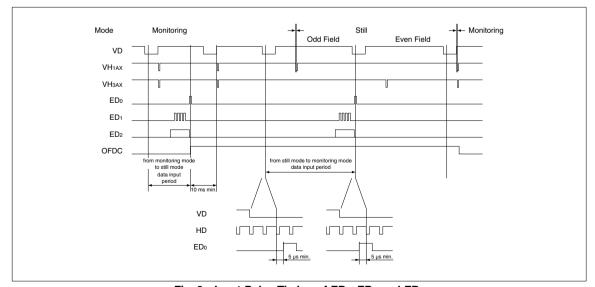

# Serial Data Control SERIAL DATA INPUT TIMING

ED2 is shifted by the rising edge of ED1, and is latched by the pulse #1 which is generated after 167 to 222 ns delay from the rising edge of ED0. (See **Fig. 2**.)

The latched serial data are divided into two types by the data of Doo, and are relatched by the pulse #2 which is generated after 277 to 332 ns delay from the rising edge of EDo. (See **Fig. 1**.)

INMD is effective at the start of #3 horizontal line, and shutter control data are effective at the start of #6 or #234 horizontal line at CCD = L, or #12 HD horizontal line at CCD = H, and other data are effective at pulse #2.

ED<sub>0</sub> should be at low level during data inputs of ED<sub>1</sub> and ED<sub>2</sub>, or while ACLX is at low level.

Fig. 1 Data Latch Timing

Fig. 2 Input Pulse Timing of ED<sub>0</sub>, ED<sub>1</sub> and ED<sub>2</sub>

# **SERIAL DATA INPUTS**

$D_{00} = L$

| DATA    | NAME                               | FUNCTION DATA = L DATA = H         |                          | AT ACLX = L |       |  |

|---------|------------------------------------|------------------------------------|--------------------------|-------------|-------|--|

| D01-D09 | SDV0-SDV8                          | Integration time control in field  |                          |             |       |  |

| D01-D09 | 3000-3000                          | period step by horizontal period.  |                          | All L       |       |  |

|         |                                    | Integration time control in        |                          |             |       |  |

| D10-D15 | SDH <sub>0</sub> -SDH <sub>5</sub> | horizontal period step by 112      | -                        | All L       |       |  |

|         |                                    | CLK clock period.                  |                          |             |       |  |

| D16     | SDF <sub>0</sub>                   | Internation times control by field |                          |             |       |  |

| D17     | SDF1                               | Integration time control by field  | _                        |             | All L |  |

| D18     | SDF <sub>2</sub>                   | period.                            |                          |             |       |  |

| D19     | SMD                                | Electronic shutter mode control    | _                        |             | L     |  |

| D20     | PWSA                               | Power save control                 | Normal                   | Power save  | L     |  |

| D21     | INMD                               | Integration mode control           | Monitoring               | Still       | L     |  |

| D22     | Dummy                              | Dummy                              | Fix to L level           |             | L     |  |

| D23     | BCPCNT                             | BCPX control                       | Discontinuous Continuous |             | L     |  |

| D24     | VHCNT                              | VH1AX to VH3BX control             | Output Held at H level   |             | L     |  |

## D00 = H

| DATA | NAME   | FUNCTION                                   | DATA = L                 | DATA = H | AT ACLX = L |

|------|--------|--------------------------------------------|--------------------------|----------|-------------|

| D01  | ML1    |                                            |                          | •        | All L       |

| D02  | ML2    |                                            | -                        | All L    |             |

| D03  | MR1    |                                            |                          |          |             |

| D04  | MR2    |                                            | -                        | _        | All L       |

| D05  | MR3    |                                            |                          |          |             |

| D06  | MC1    |                                            |                          |          |             |

| D07  | MC2    |                                            | -                        | _        | All L       |

| D08  | MC3    |                                            |                          |          |             |

| D09  | MS1    |                                            |                          |          |             |

| D10  | MS2    |                                            | -                        | All L    |             |

| D11  | MS3    | Phase control                              |                          |          |             |

| D12  | MF1    |                                            |                          |          |             |

| D13  | MF2    |                                            | -                        | All L    |             |

| D14  | MF3    |                                            |                          |          |             |

| D15  | MA1    |                                            |                          |          | All L       |

| D16  | MA2    |                                            | _                        | All L    |             |

| D17  | MD1    |                                            |                          |          |             |

| D18  | MD2    |                                            | -                        | All L    |             |

| D19  | MD3    |                                            |                          |          |             |

| D20  | MP1    |                                            |                          | All L    |             |

| D21  | MP2    |                                            | -                        | _        | All L       |

| D22  | PLCH   | Polarity control of FCDS, FS and RS pulses | Negative                 | Positive | L           |

| D23  | BLKCNT | PBLK control                               | Continuous Discontinuous |          | L           |

| D24  | Dummy  | Dummy                                      | Fix to                   | L        |             |

#### **ABSOLUTE MAXIMUM RATINGS**

| PARAMETER             | SYMBOL          | RATING             | UNIT |

|-----------------------|-----------------|--------------------|------|

| Supply voltage        | VDD3, VDD4      | -0.3 to +6.0       | V    |

| Input voltage         | Vıз             | -0.3 to VDD3 + 0.3 | V    |

| Input voltage         | VI4             | -0.3 to VDD4 + 0.3 | V    |

| Output voltage        | Vo <sub>3</sub> | -0.3 to VDD3 + 0.3 | V    |

| Output voltage        | V04             | -0.3 to VDD4 + 0.3 | V    |

| Operating temperature | Topr            | -20 to +70         | °C   |

| Storage temperature   | Tstg            | -55 to +150        | °C   |

## **ELECTRICAL CHARACTERISTICS**

### **DC Characteristics**

$(VDD3 = 3.0 \text{ V to } VDD4, VDD4 = 4.2 \text{ to } 5.5 \text{ V}, TOPR = -20 \text{ to } +70^{\circ}\text{C})$

|                       | `                 | (************************************** |            |      | ,        |      | 1700) |

|-----------------------|-------------------|-----------------------------------------|------------|------|----------|------|-------|

| PARAMETER             | SYMBOL            | CONDITIONS                              | MIN.       | TYP. | MAX.     | UNIT | NOTE  |

| Input "Low" voltage   | VIL3-1            |                                         |            |      | 0.2VDD3  | V    | 1.0   |

| Input "High" voltage  | VIH3-1            |                                         | 0.8VDD3    |      |          | V    | 1, 2  |

| Input "Low" voltage   | VIL3-2            |                                         | 0.2VDD3    |      |          | V    |       |

| Input "High" voltage  | VIH3-2            | Schmitt-buffer                          |            |      | 0.75VDD3 | V    | 3     |

| Hysteresis voltage    | $V_{T+} - V_{T-}$ |                                         | 0.08VDD3   |      |          | V    |       |

| Input "Low" voltage   | VIL4              |                                         |            |      | 0.2VDD4  | V    | 4     |

| Input "High" voltage  | VIH4              |                                         | 0.8VDD4    |      |          | V    | 4     |

| Input "Low" current   | IIL3-1            | $V_I = 0 V$                             |            |      | 1.0      | μΑ   | 1     |

| Input "High" current  | IIH3-1            | $V_I = V_{DD3}$                         |            |      | 1.0      | μΑ   | Į.    |

| Input "Low" current   | IIL3-2            | $V_I = 0 V$                             | 2.0        |      | 60       | μΑ   | 2, 3  |

| Input "High" current  | IIH3-2            | $V_I = V_{DD3}$                         |            |      | 2.0      | μΑ   | 2, 3  |

| Input "Low" current   |                   | $V_I = 0 V$                             |            |      | 2.0      | μΑ   | 4     |

| Input "High" current  | IIH4-1            | $V_I = V_{DD4}$                         | 4.0        |      | 60       | μΑ   | 4     |

| Input "Low" current   | IIL4-2            | $V_I = 0 V$                             | 4.0        |      | 60       | μΑ   | 5     |

| Input "High" current  | IIH4-2            | $V_I = V_{DD4}$                         |            |      | 2.0      | μΑ   | 3     |

| Output "Low" voltage  | VOL3-1            | IOL = 2  mA                             |            |      | 0.4      | V    | 6     |

| Output "High" voltage | VOH3-1            | IoH = −1 mA                             | VDD3 - 0.5 |      |          | V    | 8     |

| Output "Low" voltage  | VOL3-2            | IoL = 3 mA                              |            |      | 0.4      | V    | 7     |

| Output "High" voltage | VOH3-2            | Ioн = −3 mA                             | VDD3 - 0.5 |      |          | V    | _ ′   |

| Output "Low" voltage  | VOL4              | IoL = 10 mA                             |            |      | 0.4      | ٧    | 8     |

| Output "High" voltage | Voн4              | lон = −10 mA                            | VDD4 - 0.5 |      |          | V    | 8     |

#### NOTES:

- 1. Applied to inputs (IC3, OSCI3).

- 2. Applied to input (ICU3).

- 3. Applied to input (ICSU3).

- 4. Applied to input (ICD4).

- 5. Applied to input (ICU4).

- 6. Applied to output (O3).

- Applied to outputs (OSCO3, O6MA3). (Output (OSCO3) measures on condition that input (OSCI3) level is 0 V or VDD3.)

- 8. Applied to output (O6MA43).

# **PACKAGE OUTLINES**