# LMV1099 Uplink Far Field Noise Suppression & Downlink SNR Enhancing Microphone Amplifier with Earpiece Driver

Check for Samples: LMV1099

#### **FEATURES**

- Noise reduction without DSP-type artifacts.

- Adapting AGC (Automatic Gain Control) on ambient noise level & downlink signal strength

- Downlink adjustable noise-reducing high pass filter

- Separate Uplink & Downlink Enable Functions

- No added process delays

- Low power consumption

- Shutdown function

- Maximum AGC Limiter

- Differential inputs & outputs for noise immunity

- Earpiece amplifier

- Available in a 25-bump micro SMD

#### **APPLICATIONS**

- Mobile Handsets

- Mobile and handheld two-way radios

- · Bluetooth and other power headsets

#### DESCRIPTION

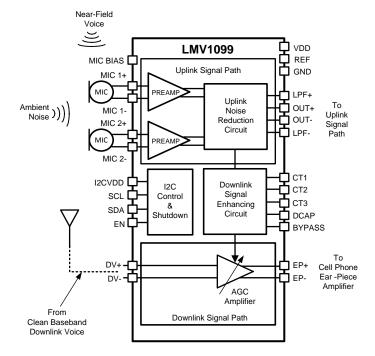

The LMV1099 is an uplink and downlink voice intelligibility enhancing analog IC, ideally suited for mobile handsets. Uplink voice intelligibility is improved by rejecting far-field noise through a unique two-microphone solution. Downlink voice intelligibility is improved by enhancing the SNR (Signal-to-Noise Ratio) between the downlink voice and the ambient noise environment at the user's earpiece.

The LMV1099 preserves uplink near-field voice signals within close range of the microphones while rejecting far-field acoustic noise greater than 0.5m from the microphones.

The LMV1099 also enhances downlink voice intelligibility by improving near-field SNR based on the user's environment. The analog circuitry adapts dynamically to both the user's ambient noise environment as well as the downlink signal amplitude to ensure optimum SNRI (signal-to-noise ratio improvement). The downlink path also provides uplink noise attenuation through an adjustable high pass filter before the SNR enhanced downlink voice reaches the user's earpiece.

Unlike digital-based noise reduction solutions, the all-analog low power consuming LMV1099 increases both uplink and downlink voice intelligibility without DSP-type artifacts, distortions or processing delays.

Table 1. Key Specifications

|                                                                                 | VALUE        | UNIT     |

|---------------------------------------------------------------------------------|--------------|----------|

| ■ Uplink Far Field Noise Suppression (Electrical FFNS <sub>E</sub> at f = 1kHz) | 33           | dB (typ) |

| ■ Near-Field SNR Enhancement                                                    | 6 to 18      | dB (typ) |

| ■ Downlink SNRI <sub>E</sub>                                                    | 16           | dB (typ) |

| ■ Supply voltage range                                                          | 2.7V to 5.5  | V        |

| ■ Supply current (V <sub>DD</sub> = 3.6V)                                       | 3.8mA (typ)  |          |

| ■ Shutdown current                                                              | 0.06μA (typ) |          |

| ■ Uplink PSRR (f = 217Hz)                                                       | 106          | dB (typ) |

| ■ Downlink SNR (A-weighted)                                                     | 102          | dB (typ) |

| ■ Downlink THD+N                                                                | 0.03% (typ)  |          |

| ■ Earpiece output power (R <sub>L</sub> = 32Ω)                                  | 83           | mW (typ) |

M

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

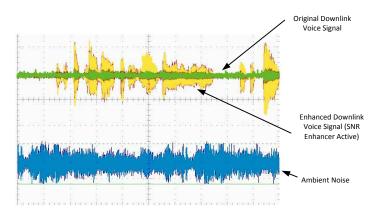

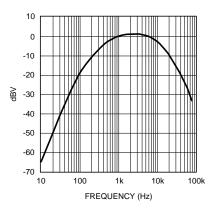

Figure 1. Voice Enhanced Signal

# **Block Diagram**

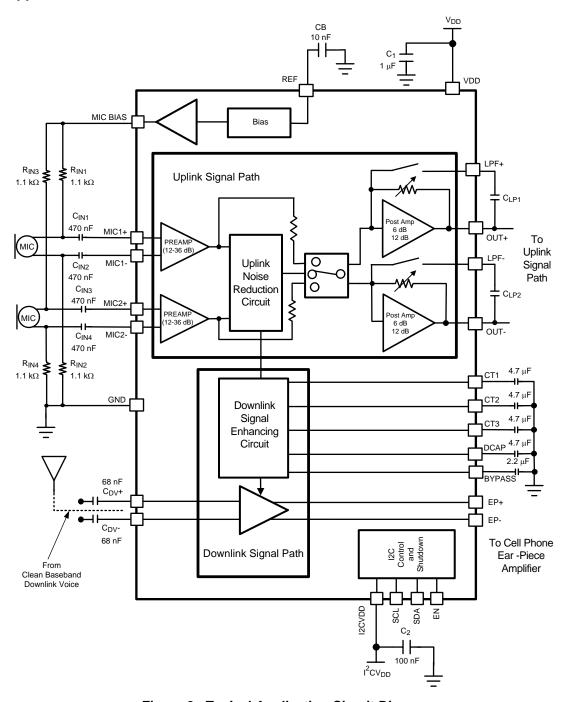

# **Typical Application**

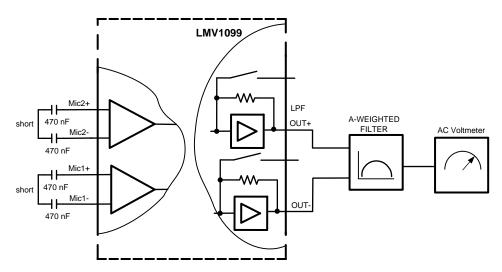

Figure 2. Typical Application Circuit Diagram

Copyright © 2010–2011, Texas Instruments Incorporated

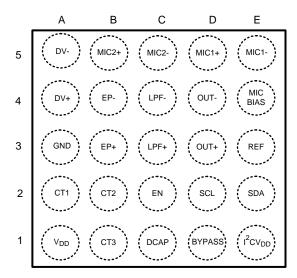

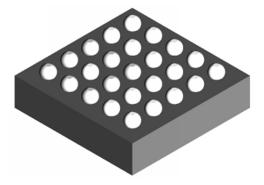

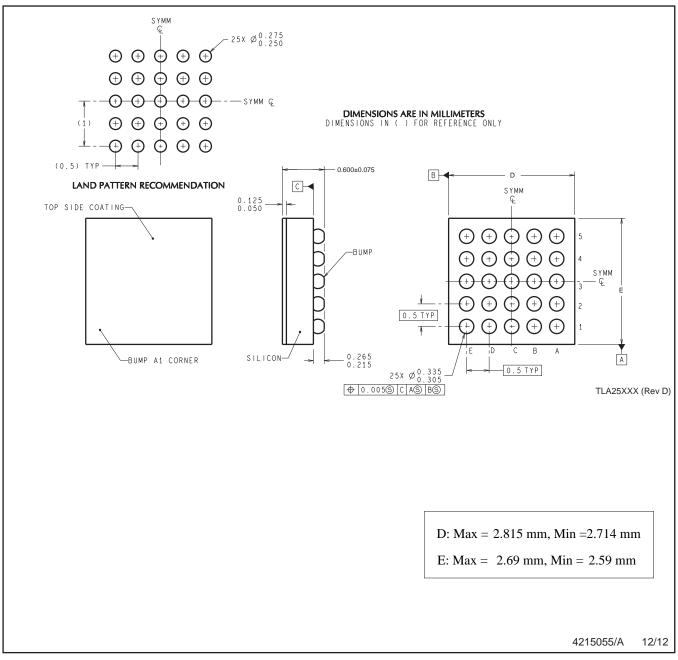

# **Connection Diagram**

Figure 3. Top View 25 – Bump micro SMD Package

Figure 4. Top View

25 – Bump micro SMD Marking

X = Plant Code

Y = Date Code

TT = Die Traceability

ZA5 = LMV1099TL

Figure 5. Bottom View 25 – Bump micro SMD Package View

# **Pin Descriptions**

Table 2. Pin Name and Function<sup>(1)</sup>

| PIN | NAME                            | TYPE           | UPLINK PIN DESCRIPTIONS                                       |

|-----|---------------------------------|----------------|---------------------------------------------------------------|

| D5  | MIC1+                           | Analog Input   | Uplink Voice Positive Microphone #1 Input                     |

| E5  | MIC1-                           | Analog Input   | Uplink Voice Negative Microphone #1 Input                     |

| B5  | MIC2+                           | Analog Input   | Uplink Voice Positive Microphone #2 Input                     |

| C5  | MIC2-                           | Analog Input   | Uplink Voice Negative Microphone #2 Input                     |

| E4  | MIC BIAS                        | Analog Output  | Microphone DC Bias Voltage Output                             |

| E3  | REF                             | Analog Ref     | Microphone Reference Bypass Pin                               |

| D3  | OUT+                            | Analog Output  | Uplink Positive Output (To Baseband Chipset)                  |

| C3  | LPF+                            | Analog Input   | Uplink-Output Low Pass Filter Positive Feedback Input         |

| D4  | OUT-                            | Analog Output  | Uplink Negative Output (To Baseband Chipset)                  |

| C4  | LPF-                            | Analog Input   | Uplink-Output Low Pass Filter Negative Feedback Input         |

| PIN | NAME                            | TYPE           | DOWNLINK PIN DESCRIPTIONS                                     |

| A4  | DV+                             | Analog Input   | Downlink Voice Positive Input                                 |

| A5  | DV-                             | Analog Input   | Downlink Voice Negative Input                                 |

| A2  | CT1                             | Analog Ref     | Control Signal Timing Capacitor                               |

| B2  | CT2                             | Analog Ref     | Control Signal Timing Capacitor                               |

| B1  | CT3                             | Analog Ref     | Control Signal Timing Capacitor                               |

| A3  | GND                             | Ground         | Power Supply Ground Pin                                       |

| D1  | Bypass                          | Analog Ref     | Earpiece Reference Bypass Pin                                 |

| В3  | EP+                             | Analog Output  | Ear Speaker Positive Output (To Ear Piece Speaker)            |

| B4  | EP-                             | Analog Output  | Ear Speaker Negative Output (To Ear Piece Speaker)            |

| PIN | NAME                            | TYPE           | DIGITAL INTERFACE & SUPPLY PIN DESCRIPTIONS                   |

| D2  | SCL                             | Digital Input  | I <sup>2</sup> C Serial Clock Digital Input                   |

| C2  | EN                              | Digital Input  | I <sup>2</sup> C Chip Enable Digital Input                    |

| E2  | SDA                             | Digital I/O    | I <sup>2</sup> C Serial Data Address Digital Input/Output Pin |

| E1  | I <sup>2</sup> CV <sub>DD</sub> | Digital Supply | I <sup>2</sup> C Digital Supply Voltage Pin                   |

| A1  | $V_{DD}$                        | Supply         | Power Supply Voltage Pin                                      |

| C1  | DCAP                            | Analog Ref     | Voice Signal Detection Capacitor                              |

|     |                                 |                |                                                               |

<sup>(1)</sup> Note: Pin assignment subject to change.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# Absolute Maximum Ratings (1)

| Supply Voltage                                            | 6.0V            |

|-----------------------------------------------------------|-----------------|

| Storage Temperature                                       | -85°C to +150°C |

| ESD Rating (HBM) (2)                                      | 2000V           |

| ESD Rating (MM) (3)                                       | 200V            |

| ESD Rating (CDM) <sup>(4)</sup>                           | 750V            |

| Junction Temperature (T <sub>JMAX</sub> )                 | 150°C           |

| Mounting Temperature<br>Infrared or Convection (20 sec.)  | 235°C           |

| Thermal Resistance                                        |                 |

| θ <sub>JA</sub> (microSMD) <sup>(5)</sup>                 | 70°C/W          |

| Soldering Information                                     |                 |

| See AN-112 "microSMD Wafers Level<br>Chip Scale Package." |                 |

- (1) "Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the Recommended Operating Conditions is not implied. The Recommended Operating Conditions indicate conditions at which the device is functional and the device should not be operated beyond such conditions. All voltages are measured with respect to the ground pin, unless otherwise specified.

- (2) Human body model, applicable std. JESD22-A114C.

- (3) Machine model, applicable std. JESD22-A115-A.

- (4) Charge device model, applicable std. JESD22-C101D.

- (5) The maximum power dissipation must be de-rated at elevated temperatures and is dictated by T<sub>JMAX</sub>, θ<sub>JC</sub>, and the ambient temperature T<sub>A</sub>. The maximum allowable power dissipation is P<sub>DMAX</sub> = (T<sub>JMAX</sub> T<sub>A</sub>) / θ<sub>JA</sub> or the number given in the *Absolute Maximum Ratings*, whichever is lower.

# Operating Ratings (1)

| Supply Voltage                  | $2.7 \text{V} \leq \text{V}_{\text{DD}} \leq 5.5 \text{V}$            |

|---------------------------------|-----------------------------------------------------------------------|

| I <sup>2</sup> CV <sub>DD</sub> | $1.7V \le I^2 CV_{DD} \le 5.5V$                                       |

|                                 | $I^2CV_{DD} \le V_{DD}$                                               |

| $T_{MIN} \le T_A \le T_{MAX}$   | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +85^{\circ}\text{C}$ |

(1) "Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the Recommended Operating Conditions is not implied. The Recommended Operating Conditions indicate conditions at which the device is functional and the device should not be operated beyond such conditions. All voltages are measured with respect to the ground pin, unless otherwise specified.

# Electrical Characteristics $V_{DD} = 3.6V^{(1)}$

Unless otherwise specified, all limits guaranteed for  $T_A = 25^{\circ}C$ ,  $V_{DD} = 3.6V$ ,  $EN = V_{DD}$ . For Uplink tests, unless otherwise specified, preamplifier gain = 20dB, post amplifier gain = 6dB,  $V_{IN} = 18 \text{mV}_{P-P}$ , f = 1 kHz,  $R_L = 100 \text{k}\Omega$ ,  $C_L = 4.7 \text{pF}$  and in pass-through mode. For Downlink tests, unless otherwise specified, f = 1 kHz,  $R_L = 32\Omega$ ,  $AGC_{AV} = 0 \text{dB}$ .

|                   |                                                                     |                                                                | LM          | <b>/1099</b>                        | Units                  |  |

|-------------------|---------------------------------------------------------------------|----------------------------------------------------------------|-------------|-------------------------------------|------------------------|--|

| Symbol            | Parameter                                                           | Conditions                                                     | Typical (2) | Limit<br>(3)                        | (Limits)               |  |

| GENERAL S         | SPECIFICATIONS                                                      |                                                                |             |                                     |                        |  |

| I <sub>DDQ</sub>  | Supply Quiescent Current                                            | V <sub>IN</sub> = 0V                                           | 3.8         | 4.5                                 | mA (max)               |  |

| I <sub>SD</sub>   | Shutdown Current                                                    | EN pin is Low                                                  | 0.06        | 1                                   | μA (max)               |  |

| T <sub>ON</sub>   | IC Wake-up Time                                                     |                                                                | 27          | 40                                  | ms (max)               |  |

| V <sub>IH</sub>   | Logic High Input Threshold                                          | EN, SCL, SDA                                                   |             | 0.7xl <sup>2</sup> CV <sub>DD</sub> | V (min)                |  |

| $V_{IL}$          | Logic Low Input Threshold                                           | EN, SCL, SDA                                                   |             | $0.3xI^2CV_{DD}$                    | V (max)                |  |

| UPLINK SP         | ECIFICATIONS                                                        |                                                                |             |                                     |                        |  |

| FFNS <sub>E</sub> | Far Field Noise Suppression (Electrical)                            | f = 1kHz (See Test Method)<br>f = 300Hz (See Test Method)      | 33<br>42    | 27.5                                | dB (min)<br>dB (min)   |  |

| SNRI <sub>E</sub> | Signal-to-Noise Ratio Improvement (Electrical)                      | f = 1khz (See Test Method)<br>f = 300Hz (See Test Method)      | 25<br>33    | 19.5                                | dB (min)<br>dB (min)   |  |

| V <sub>IN</sub>   | Maximum Input Signal                                                | THD+N < 1%, Pre Amp Gain = 12dB                                | 435         | 395                                 | mV <sub>PP</sub> (min) |  |

| V <sub>OUT</sub>  | Maximum AC Output Voltage  Differential Output, f = 1kHz THD+N < 1% |                                                                | 1.25        | 1.10                                | V <sub>RMS</sub> (min) |  |

| 001               | DC Level at Outputs                                                 | V <sub>IN</sub> = GND                                          | 825         |                                     | mV                     |  |

| Vos               | Output Offset Voltage                                               | V <sub>IN(Mic1/Mic2)</sub> = 0V, Input Referred                | 0.7         | 5.0                                 | mV (max)               |  |

| THD+N             | Total Harmonic Distortion + Noise                                   | Differential Output                                            |             | 0.3                                 | % (max)                |  |

| FR                | Frequency Response                                                  | 30Hz – 12kHz (without Filter)                                  | ±0.5        |                                     | dB                     |  |

| SNR               | Signal-to-Noise Ratio                                               | V <sub>IN</sub> = 18mV <sub>P-P</sub> , A-Weighted, audio band | 65          |                                     | dB                     |  |

| e <sub>N</sub>    | Input Referred Noise level                                          | A-Weighted                                                     | 7           |                                     | $\mu V_{RMS}$          |  |

| Z <sub>IN</sub>   | Input Impedance                                                     |                                                                | 150         | 127<br>173                          | kΩ (min)<br>kΩ max)    |  |

| Z <sub>OUT</sub>  | Output Impedance                                                    |                                                                | 235         |                                     | Ω                      |  |

| Z <sub>LOAD</sub> | Allowable Load Impedance                                            | R <sub>LOAD</sub>                                              |             | 10<br>100                           | kΩ (min)<br>pF (max)   |  |

| A <sub>M</sub>    | Microphone Pre Amplifier Gain Range                                 | Minimum setting<br>Maximum setting                             | 12<br>36    |                                     | dB                     |  |

| A <sub>MR</sub>   | Microphone Pre Amplifier Gain<br>Resolution                         |                                                                | 2           | 1.7<br>2.3                          | dB (min)<br>dB (max)   |  |

| $A_P$             | Post Amplifier Gain Range                                           | Minimum setting<br>Maximum setting                             | 6<br>12     |                                     | dB                     |  |

| $A_{PR}$          | Post Amplifier Gain Resolution                                      |                                                                | 6.0         | 5.8<br>6.2                          | dB (min)<br>dB (max)   |  |

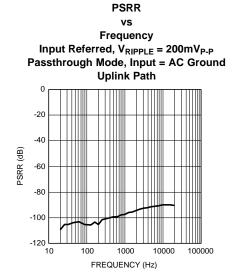

|                   |                                                                     | Input Referred, Input AC Grounded (470nl                       | F)          |                                     |                        |  |

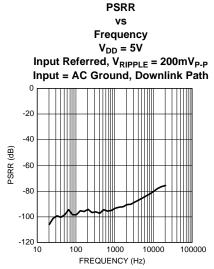

| PSRR              | Power Supply Rejection Ratio                                        | $f = 217Hz$ , $V_{RIPPLE} = 200mV_{PP}$                        | 106         | 92                                  | dB (min)               |  |

|                   |                                                                     | $f = 1kHz, V_{RIPPLE} = 200mV_{PP}$                            | 102         | 91                                  | dB (min)               |  |

| CMRR              | Common Mode Rejection Ratio                                         | Input referred                                                 | 60          |                                     | dB                     |  |

| $V_{BM}$          | Microphone Bias Supply Voltage                                      | I <sub>BM</sub> = 1mA                                          | 2.0         | 1.85<br>2.15                        | V (max)<br>V (min)     |  |

| e <sub>VBM</sub>  | Microphone Bias Supply Noise                                        | A-Weighted, C <sub>B</sub> = 10nF                              | 5.5         |                                     | $\mu V_{RMS}$          |  |

| I <sub>BMAX</sub> | Maximum Microphone Reference Output Current                         |                                                                |             | 1.2                                 | mA (max)               |  |

<sup>(1)</sup> The Electrical Characteristics tables list guaranteed specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not guaranteed.

<sup>(2)</sup> Typical values represent most likely parametric norms at T<sub>A</sub> = +25°C, and at the *Recommended Operation Conditions* at the time of product characterization and are not guaranteed.

<sup>3)</sup> Datasheet min/max specification limits are guaranteed by test or statistical analysis.

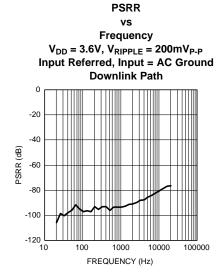

# Electrical Characteristics $V_{DD} = 3.6V^{(1)}$ (continued)

Unless otherwise specified, all limits guaranteed for  $T_A$  = 25°C,  $V_{DD}$  = 3.6V, EN =  $V_{DD}$ . For Uplink tests, unless otherwise specified, preamplifier gain = 20dB, post amplifier gain = 6dB,  $V_{IN}$  = 18m $V_{P-P}$ , f = 1kHz,  $R_L$  = 100k $\Omega$ ,  $C_L$  = 4.7pF and in pass-through mode. For Downlink tests, unless otherwise specified, f = 1kHz,  $R_L$  = 32 $\Omega$ , AGC<sub>AV</sub> = 0dB.

|                     |                                     |                                                                    | LMV'             | 1099         | Units                       |

|---------------------|-------------------------------------|--------------------------------------------------------------------|------------------|--------------|-----------------------------|

| Symbol              | Parameter                           | Conditions                                                         | Typical          | Limit<br>(3) | (Limits)                    |

| DOWNLINK            | SPECIFICATIONS                      |                                                                    |                  |              |                             |

| V <sub>IN(DV)</sub> | Maximum Input Signal (Differential) | THD+N < 1%, AGC <sub>AV</sub> = 0dB                                | 4.7              | 4.1          | V <sub>PP(DIFF)</sub> (min) |

| Vos                 | Output Offset Voltage               | $V_{IN(DV)} = 0V$ , $R_L = 32\Omega$ , Input Referred              | 0.7              | 5.0          | mV (max)                    |

| e <sub>N</sub>      | Output Noise level                  | A-Weighted, $V_{IN(DV)} = 0V$ , $AGC_{AV} = 0dB$                   | 8.9              |              | $\mu V_{RMS}$               |

| SNR                 | Downlink Signal-to-Noise Ratio      | P <sub>O</sub> = 35mW, A-Weighted                                  | 102              |              | dB                          |

| P <sub>OUT</sub>    | Output Power                        | THD+N<1%, f = 1kHz, $R_L = 32\Omega$                               | 83               | 65           | mW (min)                    |

|                     | Outrot Valta and Limit              | PLEV = 0                                                           | 3.6              |              | V <sub>P-P</sub>            |

| $V_{LIMIT}$         | Output Voltage Limit                | PLEV = 1                                                           | 4.1              |              | V <sub>P-P</sub>            |

| THD+N               | Total Harmonic Distortion + Noise   | $f = 1kHz$ , $P_O = 35mW$ , $R_L = 32\Omega$                       | 0.03             | 0.05         | % (max)                     |

| FR                  | Frequency Response                  | 30Hz – 17kHz (without Filter)                                      | ±0.5             |              | dB                          |

|                     |                                     | Input AC Grounded (68nF)                                           |                  |              | <u>'</u>                    |

| PSRR Power Su       | Power Supply Rejection Ratio        | $f = 217Hz$ , $V_{RIPPLE} = 200mV_{P-P}$ , $R_L = 32\Omega$        | 93               | 82           | dB (min)                    |

|                     |                                     | $f = 1kHz$ , $V_{RIPPLE} = 200mV_{P-P}$ , $R_L = 32\Omega$         | 92               | 81           | dB (min)                    |

| OMPD                | Occurred Made Bailedine Batis       | $V_{IN} = 200 \text{mV}_{P-P}, f = 217 \text{Hz}, R_L = 32 \Omega$ | 50               |              | dB                          |

| CMRR                | Common Mode Rejection Ratio         | $V_{IN} = 200 \text{mV}_{P-P}, f = 1 \text{kHz}, R_L = 32 \Omega$  | 60               |              | dB                          |

| ZIN(DL)             | Downlink Input Impedance            | (See Register Map, Table 8)                                        | 6.5<br>9.5<br>57 |              | kΩ<br>kΩ<br>kΩ              |

| SNR ENHAI           | NCEMENT SPECIFICATIONS              |                                                                    | ·                |              | ·                           |

| $AGC_AV$            | Automatic Gain Control Range        | Minimum setting Maximum setting                                    | 0<br>18          |              | dB                          |

| ΔAGC <sub>AV</sub>  | 0dB Gain Accuracy                   | $AGC_{AV} = 0dB$ , $f = 1kHz$ , $V_{DV} = 1V$ , $V_{AN} = 0V$      | ±0.05            |              | dB                          |

|                     |                                     | $f_{DV} = f_{AN} = 300Hz$                                          |                  |              |                             |

|                     |                                     | $V_{DV} = 100 \text{mV}_{P-P}, V_{AN} = 0.8 \text{mV}_{P-P}$       | 6                |              | dB                          |

| CNIDI               | Signal-To-Noise Ratio Improvement   | $V_{DV} = 100 \text{mV}_{P-P}, V_{AN} = 2 \text{mV}_{P-P}$         | 16               |              | dB                          |

| SNRI <sub>E</sub>   | (Electrical) <sup>(4)</sup>         | $f_{DV} = f_{AN} = 1kHz$                                           | <del>'</del>     |              | •                           |

|                     |                                     | $V_{DV} = 100 \text{mV}_{P-P}, V_{AN} = 1.4 \text{mV}_{P-P}$       | 12               |              | dB (min)                    |

|                     |                                     | $V_{DV} = 100 \text{mV}_{P-P}, V_{AN} = 2 \text{mV}_{P-P}$         | 16               |              | dB (min)                    |

$<sup>\</sup>begin{array}{ll} \text{(4)} & f_{\text{DV}} = \text{Frequency of Downlink signal} \\ & f_{\text{AN}} = \text{Frequency of Ambient Noise signal} \\ & V_{\text{DV}} = \text{Voltage swing of Downlink signal} \\ & V_{\text{AN}} = \text{Voltage swing of Ambient signal} \\ \end{array}$

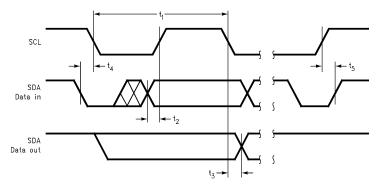

# $I^2C$ Interface Characteristics $V_{DD}$ = 3.3V, 1.8V $\leq I^2CV_{DD} \leq 5.5V$ (1) (2)

The following specifications apply for LS and HP VOLUMEGAIN = 0dB LSGAIN = 12B, HPGAIN = 0dB, EPGAIN = 0dB, R<sub>L</sub> =  $8\Omega + 30\mu H$  (Loudspeaker),  $R_1 = 32\Omega$  (Headphone),  $R_1 = 32\Omega$  (Earpiece), CSET = 0.1 $\mu$ F, ALC disabled, f = 1kHz, unless otherwise specified. Limits apply for  $T_A = 25$ °C. (Note 7).

|                 |                      |            | I       | _MV1099                             | Units (Limits) |

|-----------------|----------------------|------------|---------|-------------------------------------|----------------|

| Symbol          | Parameter            | Conditions | Typical | Limits (3)                          |                |

| t <sub>1</sub>  | SCL Period           |            |         | 2.5                                 | μs (min)       |

| t <sub>2</sub>  | SDA Setup Time       |            |         | 250                                 | ns (min)       |

| t <sub>3</sub>  | SDA Stable Time      |            |         | 0                                   | ns (min)       |

| t <sub>4</sub>  | Start Condition Time |            |         | 250                                 | ns (min)       |

| t <sub>5</sub>  | Stop Condition Time  |            |         | 250                                 | ns (min)       |

| t <sub>6</sub>  | SDA Data Hold Time   |            |         | 250                                 | ns (min)       |

| $V_{IH}$        | Input High Voltage   |            |         | 0.7xl <sup>2</sup> CV <sub>DD</sub> | V (min)        |

| V <sub>IL</sub> | Input Low Voltage    |            |         | 0.3xl <sup>2</sup> CV <sub>DD</sub> | V (max)        |

- "Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the Recommended Operating Conditions is not implied. The Recommended Operating Conditions indicate conditions at which the device is functional and the device should not be operated beyond such conditions. All voltages are measured with respect to the ground pin, unless otherwise specified.

- The Electrical Characteristics tables list guaranteed specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not quaranteed.

- Typical values represent most likely parametric norms at T<sub>A</sub> = +25°C, and at the Recommended Operation Conditions at the time of product characterization and are not guaranteed.

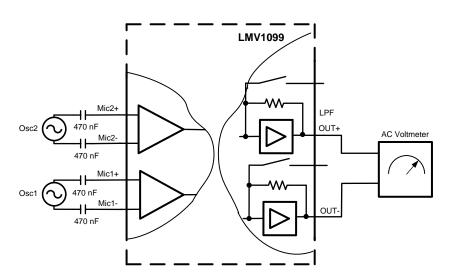

#### **Test Methods**

Figure 6. FFNS<sub>E</sub>, NFSL<sub>E</sub>, SNRI<sub>E</sub> Test Circuit

# FAR FIELD NOISE SUPPRESSION (FFNS<sub>F</sub>)

For optimum noise suppression the far field noise should be in a broadside array configuration from the two microphones, see Figure 13. Which means the far field sound source is equidistance from the two microphones. This configuration allows the amplitude of the far field signal to be equal at the two microphone inputs, however a slight phase difference may still exist. To simulate a real world application a slight phase delay was added to the FFNS<sub>F</sub> test. The block diagram from Figure 3 is used with the following procedure to measure the FFNS<sub>F</sub>.

- 1. A sine wave with equal frequency and amplitude (25mV<sub>P.P</sub>) is applied to Mic1 and Mic2. Using a signal generator, the phase of Mic 2 is delayed by 1.1° for 1kHz, or 0.33° for 300Hz, when compared with Mic1.

- 2. Measure the output level in dBV (X)

Submit Documentation Feedback

- 3. Mute the signal from Mic2

- 4. Measure the output level in dBV (Y)

- 5.  $FFNS_E = Y X dB$

#### NEAR FIELD SPEECH LOSS (NFSL<sub>E</sub>)

For optimum near field speech preservation, the sound source should be in an endfire array configuration from the two microphones (see Figure 14). In this configuration the speech signal at the microphone closest to the sound source will have greater amplitude than the microphone further away. Additionally the signal at microphone further away will experience a phase lag when compared with the closer microphone. To simulate this, phase delay as well as amplitude shift was added to the NFSL<sub>E</sub> test. The schematic from Figure 3 is used with the following procedure to measure the NFSL<sub>E</sub>.

- A 25mV<sub>P-P</sub> and 17.25mV<sub>P-P</sub> (0.69\*25mV<sub>P-P</sub>) sine wave is applied to Mic1 and Mic2 respectively. Once again, a signal generator is used to delay the phase of Mic2 by 15.9° for 1Khz, or 4.8° for 300Hz, when compared with Mic1.

- 2. Measure the output level in dBV (X)

- 3. Mute the signal from Mic2

- 4. Measure the output level in dBV (Y)

- 5.  $NFSL_E = Y X dB$

# SINGLE TO NOISE RATIO IMPROVEMENT ELECTRICAL (SNRI<sub>E</sub>)

The SNRI<sub>E</sub> is the ratio of FFNS<sub>E</sub> to NFSL<sub>E</sub> and is defined as:

$SNRI_E = FFNS_E - NFSL_E$

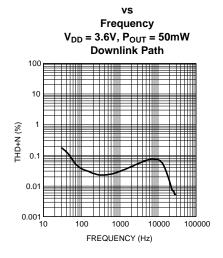

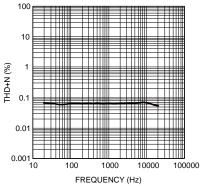

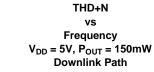

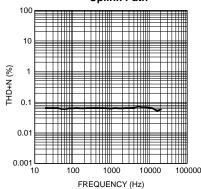

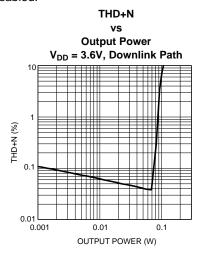

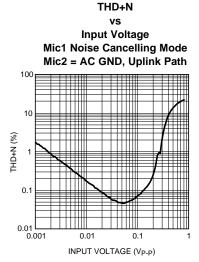

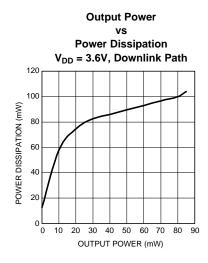

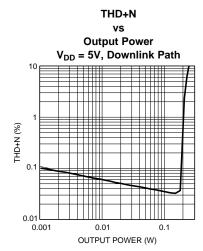

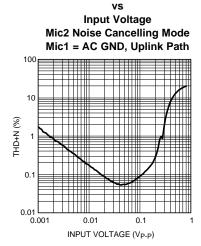

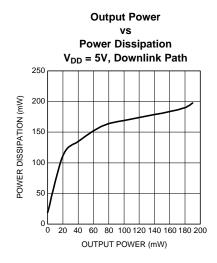

# Typical Performance Characteristics

Unless otherwise specified,  $T_J = 25^{\circ}\text{C}$ ,  $V_{DD} = 3.6\text{V}$ . Uplink Path: Input Voltage =  $18\text{mV}_{P-P}$ , f = 1 kHz, pass through mode (Note 8), Pre Amp gain = 20dB, Post Amp gain = 6dB,  $R_L = 100\text{k}\Omega$ , and  $C_L = 4.7\text{pf}$ . Downlink Path:  $R_L = 32\Omega$ , f = 1kHz, SNR Enhancer disabled.

THD+N

THD+N

vs

Frequency

Mic1 = 36mV, Pass Through Mode Mic1

Uplink Path

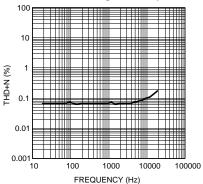

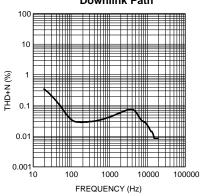

THD+N

vs

Frequency

Mic1 = 36mV<sub>P-P</sub>, Mic2 = AC GND

Noise Cancelling Mode, Uplink Path

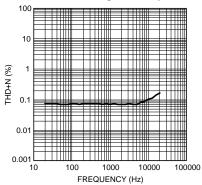

THD+N

vs

Frequency

Mic2 = 36mV, Pass Through Mode Mic2

Uplink Path

Copyright © 2010–2011, Texas Instruments Incorporated

# **Typical Performance Characteristics (continued)**

Unless otherwise specified,  $T_J$  = 25°C,  $V_{DD}$  = 3.6V. Uplink Path: Input Voltage = 18m $V_{P-P}$ , f =1 kHz, pass through mode (Note 8), Pre Amp gain = 20dB, Post Amp gain = 6dB,  $R_L$  = 100k $\Omega$ , and  $C_L$  = 4.7pf. Downlink Path:  $R_L$  = 32 $\Omega$ , f = 1kHz, SNR Enhancer disabled.

THD+N

#### **Typical Performance Characteristics (continued)**

Unless otherwise specified,  $T_J$  = 25°C,  $V_{DD}$  = 3.6V. Uplink Path: Input Voltage = 18m $V_{P-P}$ , f =1 kHz, pass through mode (Note 8), Pre Amp gain = 20dB, Post Amp gain = 6dB,  $R_L$  = 100k $\Omega$ , and  $C_L$  = 4.7pf. Downlink Path:  $R_L$  = 32 $\Omega$ , f = 1kHz, SNR Enhancer disabled.

# **Application Data**

#### UPLINK FAR-FIELD NOISE REDUCTION OVERVIEW

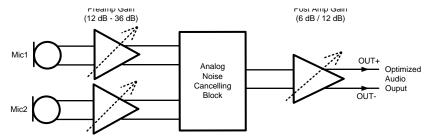

The uplink portion of the LMV1099 is a fully analog solution to reduce the far field noise picked up by microphones in a communication system. A simplified block diagram is provided in Figure 7.

Figure 7. Simplified Block Diagram of the LMV1099 Uplink path

The output signal of the microphones is amplified by a pre-amplifier with adjustable gain between 12dB and 36dB. The matched signals are then routed through the Analog Noise Cancelling block which suppresses the far-field signal. The output of the analog noise cancelling processor is amplified in the post amplifier with selectable gain, 6dB or 12dB. For optimum noise and EMI immunity, the microphones have a differential connection to the LMV1099 and the uplink output is also differential. The adjustable gain functions can be controlled via I<sup>2</sup>C.

#### **POWER SUPPLY CIRCUITS**

A low drop-out (LDO) voltage regulator in the LMV1099 allows the device to be independent of supply voltage variations.

The Power On Reset (POR) circuitry in the LMV1099 requires the supply voltage to rise from 0V to  $V_{DD}$  in less than 100ms.

The Mic Bias output is provided as a low noise supply source for the electret microphones. The noise voltage on the Mic Bias microphone supply output pin depends on the noise voltage on the internal the reference node. The de-coupling capacitor on the  $V_{REF}$  pin determines the noise voltage on this internal reference. This capacitor should be larger than 1nF; having a larger capacitor value will result in a lower noise voltage on the Mic Bias output.

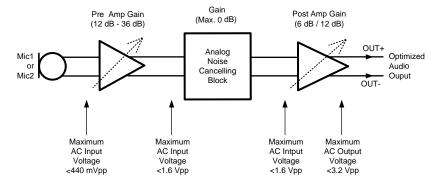

#### GAIN BALANCE AND GAIN BUDGET

In systems where input signals have a high dynamic range, critical noise levels or where the dynamic range of the output voltage is also limited, careful gain balancing is essential for the best performance. Too low of a gain setting in the preamplifier can result in higher noise levels, while too high of a gain setting in the preamplifier will result in saturation of the noise cancelling processor and output stages.

The gain ranges and maximum signal levels for the different functional blocks are shown in Figure 8. Two examples are given as a guideline on how to select proper gain settings.

Figure 8. Maximum Signal Levels

#### Example 1:

An application using microphones with  $50mV_{P-P}$  maximum output voltage, and a baseband chip after the LMV1099 with  $1.5V_{P-P}$  maximum input voltage.

For optimum noise performance, the gain of the input stage should be set to the maximum.

- 1.  $50\text{mV}_{P-P} + 36\text{dB} = 3.1\text{V}_{P-P}$ .

- 2. 3.1V<sub>P-P</sub> is higher than the maximum 1.5V<sub>P-P</sub> allowed for the Noise Cancelling Block (NCB). This means a gain lower than 29.5dB should be selected.

- 3. Select the nearest lower gain from the gain settings shown in Table 7, 28dB is selected. This will prevent the NCB from being overloaded by the microphone. With this setting, the resulting output level of the Pre Amplifier will be 1.26V<sub>P-P</sub>.

- 4. The NCB has a gain of 0dB which will result in 1.26V<sub>P-P</sub> at the output of the LMV1099. This level is less than the maximum level that is allowed at the input of the post amp of the LMV1099.

- 5. The baseband chip limits the maximum output voltage to 1.5V<sub>P-P</sub> with the minimum of 6dB post amp gain, this results in requiring a lower level at the input of the post amp of 0.75V<sub>P-P</sub>. Now calculating this for a maximum preamp gain, the output of the preamp must be no more than 0.75mV<sub>P-P</sub>.

www.ti.com

- 6. Calculating the new gain for the preamp will result in <23.5dB gain.

- 7. The nearest lower gain will be 22dB.

So using preamp gain = 22dB and postamp gain = 6dB is the optimum for this application.

#### Example 2:

An application using microphones with  $10\text{mV}_{P-P}$  maximum output voltage, and a baseband chip after the LMV1099 with  $3.3\text{V}_{P-P}$  maximum input voltage.

For optimum noise performance we would like to have the maximum gain at the input stage.

- 1.  $10\text{mV}_{P-P} + 36\text{dB} = 631\text{mV}_{P-P}$ .

- 2. This is lower than the maximum  $1.5V_{P-P}$ , so this is OK.

- The NCB has a gain of 0dB which will result in 1.5V<sub>P-P</sub> at the output of the LMV1099. This level is lower than the maximum level that is allowed at the input of the Post Amp of the LMV1099.

- 4. With a Post Amp gain setting of 6dB the output of the Post Amp will be  $3V_{P,P}$  which is OK for the baseband.

- 5. The nearest lower Post Amp gain will be 6dB.

So using preamp gain = 36dB and postamp gain = 6dB is optimum for this application.

#### I<sup>2</sup>C Compatible Interface

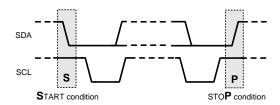

The LMV1099 is controlled through an I<sup>2</sup>C compatible serial interface that consists of a serial data line (SDA) and a serial clock (SCL). The clock line is uni-directional. The data line is bi-directional (open-collector) although the LMV1099 does not write to the I<sup>2</sup>C bus. The LMV1099 and the master can communicate at clock rates up to 400kHz. Figure 5 shows the I<sup>2</sup>C Interface timing diagram. Data on the SDA line must be stable during the HIGH period of SCL. The LMV1099 is a transmit/receive slave-only device, reliant upon the master to generate the SCL signal. Each transmission sequence is framed by a START condition and a STOP condition (Figure 6). The data line is 8 bits long and is always followed by an acknowledge pulse (Figure 7).

#### I<sup>2</sup>C Compatible Interface Power Supply Pin (I<sup>2</sup>CV<sub>DD</sub>)

The LMV1099  $I^2C$  interface is powered up through the  $I^2CV_{DD}$  pin. The LMV1099  $I^2C$  interface operates at a voltage level set by the  $I^2CV_{DD}$  pin which can be set independent to that of the main power supply pin  $V_{DD}$ . This is ideal whenever logic levels for the  $I^2C$  Interface are dictated by a microcontroller or microprocessor that is operating at a lower supply voltage than the main battery of a portable system.

#### I2C Bus Format

The I<sup>2</sup>C bus format is shown in Figure 7. The START signal, the transition of SDA from HIGH to LOW while SCL is HIGH is generated, alerting all devices on the bus that a device address is being written to the bus. The 7-bit device address is written to the bus, most significant bit (MSB) first followed by the R/W bit, R/W = 0 indicates the master is writing to the slave device, R/W = 1 indicates the master wants to read data from the slave device. Set R/W = 0; the LMV1099 is a WRITE-ONLY device and will not respond to the R/W = 1. The data is latched in on the rising edge of the clock. Each address bit must be stable while SCL is HIGH. After the last address bit is transmitted, the mater device release SDA, during which time, an acknowledge clock pulse is generated by the slave device. If the LMV1099 receives the correct address, the device pulls the SDA line low, generating an acknowledge bit (ACK)

Once the master device registers the ACK bit, the 8-bit register data word is sent. Each data bit should be stable while SCL is HIGH. After the 8-bit register data word is sent, the LMV1099 sends another ACK bit. Following the acknowledgement of the last register data word, the master issues a STOP bit, allowing SDA to go high while SCL is high.

Figure 9. I<sup>2</sup>C Timing Diagram

Figure 10. I<sup>2</sup>C Start Stop Conditions

Figure 11. Start and Stop Diagram

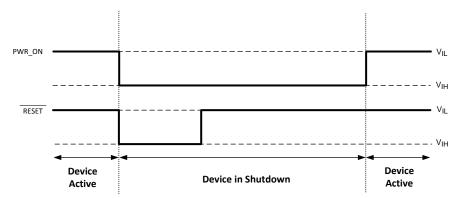

#### I<sup>2</sup>C RESET PIN

When the I<sup>2</sup>C RESET pin is pulled low, the device will go into shutdown and the Power\_on bit (see) in the shutdown control register will reset. The device will remain in shutdown until an I<sup>2</sup>C command brings the device out of shutdown (see timing diagram in Figure 12). This pin can be connected to the I<sup>2</sup>CV<sub>DD</sub> pin to prevent undefined and unwanted state changes that may occur when the I<sup>2</sup>C supply voltage is cycled.

Figure 12.

# Table 3. Chip Address

|              | B7 <sup>(1)</sup> | В6 | B5 | B4 | В3 | B2 | B1 | B0/W |

|--------------|-------------------|----|----|----|----|----|----|------|

| Chip Address | 1                 | 1  | 0  | 0  | 1  | 1  | 1  | 0    |

(1) The 7th Bit (B7) of the Register Data determines whether it will activate Register A or Register B.

# **Table 4. Control Registers**

| Register Name    | Register<br>Address<br>B<6:5> | B<4>          | B<3>          | B<2>          | B<1>                                | B<0>          |

|------------------|-------------------------------|---------------|---------------|---------------|-------------------------------------|---------------|

| Shutdown control | 00                            | x             | х             | enable_ep     | I <sup>2</sup> CV <sub>DD</sub> _sd | power_on      |

| Mic mode control | 01                            | mic_sel1      | mic_sel0      | agc_mic_mute  | mute_mic2                           | mute_mic1     |

| Mic Gain control | 10                            | mic_post_gain | mic_pre_gain3 | mic_pre_gain2 | mic_pre_gain1                       | mic_pre_gain0 |

| EP               | 11                            | ep_mute       | plev          | ep_bypass_agc | ep_ri1                              | ep_ri0        |

# **Table 5. Shutdown Control Register**

| BIT          | NAME                                  | DESCRIPTION |                                                                                                                                                                                                            |  |  |  |

|--------------|---------------------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| D2           | DO sachle an                          |             | Disable earpiece                                                                                                                                                                                           |  |  |  |

| B2 enable_ep |                                       | 1           | Enable earpiece                                                                                                                                                                                            |  |  |  |

| B1           | B1 I <sup>2</sup> CV <sub>DD</sub> SD |             | I <sup>2</sup> CV <sub>DD</sub> is an active low RESET input. If I <sup>2</sup> CV <sub>DD</sub> drops below 1.1V the device resets and the I <sup>2</sup> C registers are restored to their default state |  |  |  |

|              |                                       |             | Normal operation. I <sup>2</sup> CV <sub>DD</sub> voltage does not reset the device                                                                                                                        |  |  |  |

| D0           |                                       | 0           | Device disable                                                                                                                                                                                             |  |  |  |

| В0           | power_on                              | 1           | Device enable                                                                                                                                                                                              |  |  |  |

# Table 6. LMV1099 Microphone Mode Control Register

| BIT   | NAME                     |    |    | DESCRIPTION                      |

|-------|--------------------------|----|----|----------------------------------|

|       |                          | B4 | B3 |                                  |

|       |                          | 0  | 0  | Noise canceling mode             |

| B4:B3 | mic_sel<4><br>mic_sel<3> | 0  | 1  | Only mic1 enabled (pass through) |

|       | 11110_001302             | 1  | 0  | Only mic2 enabled (pass through) |

|       |                          | 1  | 1  | (mic1+mic2)/2                    |

| DO    |                          |    | 0  | mic1 & mic2 mute not allowed     |

| B2    | agc_mic_mute             |    | 1  | mic1 & mic2 mute allowed         |

| B1    | mute_mic2 <sup>(1)</sup> |    | 0  | mic2 on                          |

| DΊ    | mute_mic2(*)             | 1  |    | mic2 mute                        |

| DΩ    | muta mia1 (1)            |    | 0  | mic1 on                          |

| ВО    | B0 mute_mic1 (1)         |    | 1  | mic1 mute                        |

<sup>(1)</sup> agc\_mic\_mute overrides mute\_mic1 and mute\_mic2

# Table 7. LMV1099 Microphone Gain Control Register

| BIT | NAME          | DESCRIPTION |      |  |  |

|-----|---------------|-------------|------|--|--|

| D4  | mic_post_gain | 0           | 6dB  |  |  |

| B4  |               | 1           | 12dB |  |  |

# Table 7. LMV1099 Microphone Gain Control Register (continued)

| BIT   | NAME                                                            | DESCRIPTION |    |    |    |      |  |  |

|-------|-----------------------------------------------------------------|-------------|----|----|----|------|--|--|

|       | mic_pre_gain<3> mic_pre_gain<2> mic_pre_gain<1> mic_pre_gain<0> | В3          | B2 | B1 | В0 |      |  |  |

|       |                                                                 | 0           | 0  | 0  | 0  | 12dB |  |  |

|       |                                                                 | 0           | 0  | 0  | 1  | 12dB |  |  |

|       |                                                                 | 0           | 0  | 1  | 0  | 12dB |  |  |

|       |                                                                 | 0           | 0  | 1  | 1  | 12dB |  |  |

|       |                                                                 | 0           | 1  | 0  | 0  | 14dB |  |  |

|       |                                                                 | 0           | 1  | 0  | 1  | 16dB |  |  |

|       |                                                                 | 0           | 1  | 1  | 0  | 18dB |  |  |

| B3:B0 |                                                                 | 0           | 1  | 1  | 1  | 20dB |  |  |

|       |                                                                 | 1           | 0  | 0  | 0  | 22dB |  |  |

|       |                                                                 | 1           | 0  | 0  | 1  | 24dB |  |  |

|       |                                                                 | 1           | 0  | 1  | 0  | 26dB |  |  |

|       |                                                                 | 1           | 0  | 1  | 1  | 28dB |  |  |

|       |                                                                 | 1           | 1  | 0  | 0  | 30dB |  |  |

|       |                                                                 | 1           | 1  | 0  | 1  | 32dB |  |  |

|       |                                                                 | 1           | 1  | 1  | 0  | 34dB |  |  |

|       |                                                                 | 1           | 1  | 1  | 1  | 36dB |  |  |

#### Table 8. LMV1099 Earpiece Control Register

| BIT   | NAME                 | DESCRIPTION |                                                                   |                                                                |  |  |  |

|-------|----------------------|-------------|-------------------------------------------------------------------|----------------------------------------------------------------|--|--|--|

| D4    |                      |             | 0                                                                 | EP on                                                          |  |  |  |

| B4    | ep_mute              |             | 1                                                                 | EP mute                                                        |  |  |  |

| В3    | nlov                 |             | 0                                                                 | 3.6V <sub>P-P</sub> Earpiece Output Level (50mW with 32Ω load) |  |  |  |

| ВЗ    | plev                 |             | 1                                                                 | 4.1V <sub>P-P</sub> Earpiece Output Level (70mW with 32Ω load) |  |  |  |

|       | B2 ep_bypass_agc 0 1 |             | 0                                                                 | Normal operation                                               |  |  |  |

| B2    |                      |             | Downlink SNR Enhancer Circuit bypassed (earpiece is still active) |                                                                |  |  |  |

|       |                      | B1          | В0                                                                |                                                                |  |  |  |

|       |                      | 0           | 0                                                                 | 60kΩ input impedance                                           |  |  |  |

| B1:B0 | ep_ri<1><br>ep_ri<0> | 0           | 1                                                                 | 9kΩ input impedance                                            |  |  |  |

|       | ορ_1/0>              | 1           | 0                                                                 | 6kΩ input impedance                                            |  |  |  |

|       |                      | 1 1         |                                                                   | 6kΩ input impedance                                            |  |  |  |

# **Shutdown Function**

As part of the Powerwise<sup>TM</sup> family, the LMV1099 consumes only 0.50mA of current. In many applications the part does not need to be continuously operational. To further reduce the power consumption in the inactive period, the LMV1099 provides two individual microphone power down functions (controlled through the mode control registers B3:B4). When either one of the shutdown functions is activated the part will go into shutdown mode consuming only a few μA of supply current. Shutdown functions can be controlled via the I<sup>2</sup>C interface or a hardware pin.

#### SHUTDOWN VIA HARDWARE PIN

The hardware shutdown function is operated via the EN pin. In normal operation the EN pin must be at a 'high' level  $(V_{DD})$ . Whenever a 'low' level (GND) is applied to the EN pin the part will go into shutdown mode disabling all internal circuits.

# **Microphone Mode Control**

The LMV1099 features four Microphone modes, Noise Cancellation Mode, Mic 1 pass through, Mic 2 pass through, and (Mic1+Mic2)/2. When in Noise Cancellation mode, it is imperative that Mic 1 and Mic 2 are NOT muted. If the mute function for either microphone path is enabled, the noise cancellation circuitry will be disabled. In mic1/mic2 pass through mode the noise canceling block is bypassed, and the LMV1099 is simply used as a microphone amplifier where the microphone signal passes through the pre and post amplifier gain stages. The last mode provides an average of the two microphone pass through signals (noise cancelling block is bypassed).

The microphone input paths can be muted individually via I<sup>2</sup>C (Mic mode control register B1:B0). To enable the mute function, set bit B2 of the microphone mode control register to 1. If B2 is set to 0, the mute function will not activate.

# Signal-to-Noise Ratio Enhancer (SNR Enhancer)

The SNR Enhancer in the LMV1099 is designed to provide excellent voice intelligibility in noisy environments. The control signal for the output gain adjustment is dependent on both the level and the type of ambient noise, compared with the signal energy of the downlink voice. The system was designed to operate transparently to the user, such that the gain changes are not evident but provide excellent voice intelligibility.

National has invested considerable amount of time evaluating the acoustic effects of different ambient noise source types along with their practical SPL levels to determine optimum timing capacitor values for the proprietary downlink solution. These timing capacitor values should not be changed. We recommend using standard ceramic chip type capacitors with a low leakage rating. Electrolytic capacitors should not be used.

The SNR enhancing circuit will analyze the various energy levels for different frequency ranges and weight the AGC's gain change accordingly such that the downlink voice will remain intelligent. The overall intent of the circuit is for the gain changes to be transparent. Great care has gone into ensuring that gain changes won't be too perceptible or obnoxious. The system with have more dynamic gain change capability at low ambient noise levels in order to respond to fast changing noise sources. At the other extreme the system will have less dynamic gain change at high ambient noise levels since the environment will constantly be affecting intelligibility.

#### **Earpiece Control Registers**

#### **OUTPUT POWER LIMIT (PLEV)**

While National has done extensive ambient SPL analysis, there will always be unusual circumstances that may cause the amplifier to be at its maximum 18dB setting. LMV1099 features an Output Voltage Limit function to limit the output power delivered to a speaker. When the SNR enhancer is active, the Output Voltage Limit works to protect the loudspeaker in conditions where a large downlink input signal is present. The Output Voltage Limit can be set to a selectable (3.6V<sub>P-P</sub> or 4.1V<sub>P-P</sub>) output level to avoid violating the maximum power limitation of the transducer.

#### SNR ENHANCER BYPASS (EP BYPASS AGC)

The SNR enhancer can be bypassed by setting B4 of the Earpiece Control Register to 1. When the SNR enhancer is bypassed, the earpiece amplifier has a fixed 0dB gain.

# **EP\_RI (INPUT IMPEDANCE)**

The earpiece input of the LMV1099 features three input impedance options, this impedance in conjunction with the input capacitor creates a high-pass filter. The three options provide various cutoff frequencies for the high-pass filter. Table 9 shows the respective cutoff frequencies for each of the input impedance options when using a 68nF input capacitor.

Table 9. Input Impedance options

| Input Impedance | f <sub>C</sub> |

|-----------------|----------------|

| 60kΩ            | 40Hz           |

| 9kΩ             | 260Hz          |

| 6kΩ             | 390Hz          |

Changing the input coupling capacitor will affect the filters -3dB point through the simple RC equation shown below:

$$f = 1 / 2\pi RC \tag{1}$$

# **Microphone Placement**

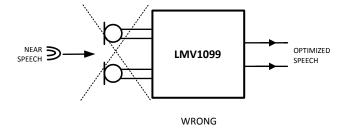

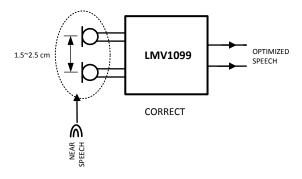

Because the LMV1099 is a microphone array Far Field Noise Reduction solution, proper microphone placement is critical for optimum performance. Two things need to be considered: The spacing between the two microphones and the position of the two microphones relative to near field source.

If the spacing between the two microphones is too small near field speech will be canceled along with the far field noise. Conversely, if the spacing between the two microphones is large, the far field noise reduction performance will be degraded. The optimum spacing between mic1 and mic2 is 1.5-2.5cm. This range provides a balance of minimal near field speech loss and maximum far field noise reduction. The microphones should be in line with the desired sound source 'near speech' and configured in an endfire array (see Figure 14) orientation from the sound source. If the 'near speech' (desired sound source) is equidistant to the source like a broadside array (see Figure 13) the result will be a great deal of near field speech loss.

Figure 13. Broadside Array (WRONG)

Figure 14. Endfire Array (CORRECT)

# **Low-Pass Filter At The Output**

At the output of the LMV1099 there is a provision to create a 1st order low-pass filter (only enabled in 'Noise Cancelling' mode). This low-pass filter can be used to compensate for the change in frequency response that results from the noise cancellation process. The change in frequency response resembles a first-order high-pass filter, and for many of the applications it can be compensated by a first-order low-pass filter with cutoff frequency between 1.5kHz and 2.5kHz.

The transfer function of the low-pass filter is derived as:

$$H(s) = \frac{\text{Post Amplifier gain}}{sR_fC_f + 1}$$

(2)

Product Folder Links: LMV1099

Copyright © 2010-2011, Texas Instruments Incorporated

This low-pass filter is created by connecting a capacitor between the LPF pin and the OUT pin of the LMV1099. The value of this capacitor also depends on the selected output gain. For different gains the feedback resistance in the low-pass filter network changes as shown in Table 10.

This will result in the following values for a cutoff frequency of 2000 Hz:

Table 10. Low-Pass Filter Capacitor For 2kHz

| Post Amplifier Gain Setting (dB) | R <sub>f</sub> (kΩ) | C <sub>f</sub> (nF) |  |

|----------------------------------|---------------------|---------------------|--|

| 6                                | 20                  | 3.9                 |  |

| 12                               | 40                  | 2.0                 |  |

# **A-Weighted Filter**

The human ear is sensitive for acoustic signals within a frequency range from about 20Hz to 20kHz. Within this range the sensitivity of the human ear is not equal for each frequency. To approach the hearing response, weighting filters are introduced. One of those filters is the A-weighted filter.

The A-weighted filter is used in signal to noise measurements, where the wanted audio signal is compared to device noise and distortion.

The use of this filter improves the correlation of the measured values to the way these ratios are perceived by the human ear.

Figure 15. A-Weighted Filter

# Measuring Uplink Noise and SNR

The overall noise of the LMV1099 is measured within the frequency band from 10Hz to 22kHz using an A-weighted filter. The Mic+ and Mic- inputs of the LMV1099 are AC shorted between the input capacitors, see Figure 16.

Figure 16. Noise Measurement Setup

For the signal to noise ratio (SNR) the signal level at the output is measured with a 1kHz input signal of  $18mV_{P-P}$  using an A-weighted filter. This voltage represents the output voltage of a typical electret condenser microphone at a sound pressure level of 94dB SPL, which is the standard level for these measurements. The LMV1099 is programmed for 26dB of total gain (20dB preamplifier and 6dB postamplifier) with only mic1 or mic2 used. (See also  $^{\rho}C$  Compatible Interface).

The input signal is applied differentially between the Mic+ and Mic-. Because the part is in Pass Through mode the low-pass filter at the output of the LMV1099 is disabled.

**Table 11. Revision History**

| Rev  | Date     | Description                                          |  |  |  |  |

|------|----------|------------------------------------------------------|--|--|--|--|

| 1.0  | 08/12/10 | Initial release.                                     |  |  |  |  |

| 1.01 | 12/10/10 | Added the X1, X2, and X3 values of the mktg outline. |  |  |  |  |

| 1.02 | 03/30/11 | Edited Table 3 (Control Registers).                  |  |  |  |  |

18-Jan-2013

#### **PACKAGING INFORMATION**

| Orderable Device | Status | Package Type | _       |    | Package Qty | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp      | Samples          |

|------------------|--------|--------------|---------|----|-------------|----------------------------|------------------|--------------------|------------------|

|                  | (1)    |              | Drawing |    |             | (2)                        |                  | (3)                | (Requires Login) |

| LMV1099TL/NOPB   | NRND   | DSBGA        | YZR     | 25 | 250         | Green (RoHS<br>& no Sb/Br) | SNAGCU           | Level-1-260C-UNLIM |                  |

| LMV1099TLX/NOPB  | NRND   | DSBGA        | YZR     | 25 | 3000        | Green (RoHS<br>& no Sb/Br) | SNAGCU           | Level-1-260C-UNLIM |                  |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

NOTES: A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M-1994. B. This drawing is subject to change without notice.

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive Communications and Telecom **Amplifiers** amplifier.ti.com www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP **Energy and Lighting** dsp.ti.com www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical logic.ti.com Logic Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers <u>microcontroller.ti.com</u> Video and Imaging <u>www.ti.com/video</u>

RFID www.ti-rfid.com

OMAP Applications Processors <a href="www.ti.com/omap">www.ti.com/omap</a> TI E2E Community <a href="e2e.ti.com">e2e.ti.com</a>

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>