# LM3146 High Voltage Transistor Array

#### **General Description**

The LM3146 consists of five high voltage general purpose silicon NPN transistors on a common monolithic substrate. Two of the transistors are internally connected to form a differentially-connected pair. The transistors are well suited to a wide variety of applications in low power system in the dc through VHF range. They may be used as discrete transistors in conventional circuits however, in addition, they provide the very significant inherent integrated circuit advantages of close electrical and thermal matching. The LM3146 is supplied in a 14-lead molded dual-in-line package for applications requiring only a limited temperature range.

#### **Features**

- High voltage matched pairs of transistors, V<sub>BE</sub> matched ±5 mV, input offset current 2 µA max at I<sub>C</sub> = 1 mA

- Five general purpose monolithic transistors

- Operation from dc to 120 MHz

- Wide operating current range

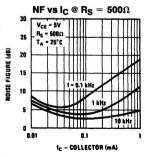

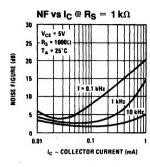

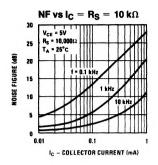

- Low noise figure

3.2 dB tvp at 1 kHz

### **Applications**

- General use in all types of signal processing systems operating anywhere in the frequency range from dc to VHF

- Custom designed differential amplifiers

- Temperature compensated amplifiers

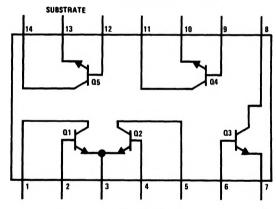

### **Connection Diagram**

#### **Dual-In-Line and Small Outline Packages**

TL/H/7959-1

Top View

Order Number LM3146M or LM3146N

See NS Package Number M14A or N14A

### **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

| Office/Distributors for availability and specifications. |                |       |  |  |  |  |

|----------------------------------------------------------|----------------|-------|--|--|--|--|

|                                                          | LM3146         | Units |  |  |  |  |

| Power Dissipation: Each transistor                       |                |       |  |  |  |  |

| $T_A = 25^{\circ}C$ to 55°C                              | 300            | mW    |  |  |  |  |

| T <sub>A</sub> > 55°C                                    | Derate at 6.67 | mW/°C |  |  |  |  |

| Power Dissipation: Total Package                         |                |       |  |  |  |  |

| T <sub>A</sub> = 25°C                                    | 500            | mW    |  |  |  |  |

| T <sub>A</sub> > 25°C                                    | Derate at 6.67 | mW/°C |  |  |  |  |

| Collector to Emitter Voltage, V <sub>CEO</sub>           | 30             | ٧     |  |  |  |  |

| Collector to Base Voltage, V <sub>CBO</sub>              | 40             | ٧     |  |  |  |  |

| Collector to Substrate Voltage,                          |                |       |  |  |  |  |

| V <sub>CIO</sub> (Note 1)                                | 40             | ٧     |  |  |  |  |

| Emitter to Base Voltage, VEBO                            |                |       |  |  |  |  |

| (Note 2)                                                 | 5              | ٧     |  |  |  |  |

| Collector to Current, I <sub>C</sub>                     | 50             | mΑ    |  |  |  |  |

| Operating Temperature Range                              | -40 to +85     | •C    |  |  |  |  |

| Storage Temperature Range                                | -65  to  + 150 | ٠c    |  |  |  |  |

Soldering Information

Dual-In-Line Package

Soldering (10 seconds)

Small Outline Package

Vapor Phase (60 seconds)

Infrared (15 seconds)

220°C

See AN-450 "Surface Mounting Methods and Their Effect on Product Reliability" for other methods of soldering surface mount devices:

## DC Electrical Characteristics TA = 25°C

| Symbol                             | Parameter                                               | Conditions                                                                                                     | Limits |                 |      | Units |

|------------------------------------|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--------|-----------------|------|-------|

|                                    |                                                         | Conditions                                                                                                     | Min    | Тур             | Max  | Units |

| V <sub>(BR)CBO</sub>               | Collector to Base Breakdown Voltage                     | $I_{C} = 10  \mu A, I_{E} = 0$                                                                                 | 40     | 72              |      | ٧     |

| V <sub>(BR)CEO</sub>               | Collector to Emitter Breakdown Voltage                  | I <sub>C</sub> = 1 mA, I <sub>B</sub> = 0                                                                      | 30     | 56              |      | ٧     |

| V <sub>(BR)CIO</sub>               | Collector to Substrate Breakdown<br>Voltage             | $I_{CI} = 10 \mu A, I_{B} = 0,$ $I_{E} = 0$                                                                    | 40     | 72              |      | ٧     |

| V <sub>(BR)EBO</sub>               | Emitter to Base Breakdown Voltage (Note 2)              | I <sub>C</sub> = 0, I <sub>E</sub> = 10 μA                                                                     | 5      | 7               |      | V     |

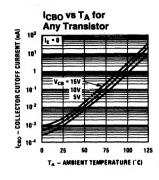

| Ісво                               | Collector Cutoff Current                                | $V_{CB} = 10V, I_{E} = 0$                                                                                      |        | 0.002           | 100  | nA    |

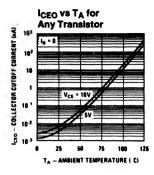

| CEO                                | Collector Cutoff Current                                | V <sub>CE</sub> = 10V, I <sub>B</sub> = 0                                                                      |        | (Note 3)        | 5    | μА    |

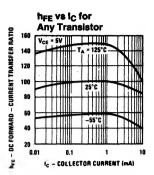

| h <sub>FE</sub>                    | Static Forward Current Transfer<br>Ratio (Static Beta)  | $I_C = 10 \text{ mA}, V_{CE} = 5V$<br>$I_C = 1 \text{ mA}, V_{CE} = 5V$<br>$I_C = 10 \mu\text{A}, V_{CE} = 5V$ | 30     | 85<br>100<br>90 |      |       |

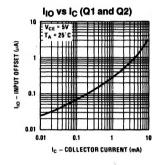

| l <sub>B1</sub> -l <sub>B2</sub>   | Input Offset Current for Matched Pair Q1 and Q2         | $I_{C1} = 1_{C2} = 1 \text{ mA},$<br>$V_{CE} = 5V$                                                             |        | 0.3             | 2    | μΑ    |

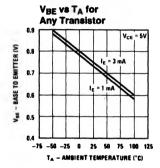

| V <sub>BE</sub>                    | Base to Emitter Voltage                                 | I <sub>C</sub> = 1 mA, V <sub>CE</sub> = 3V                                                                    | 0.63   | 0.73            | 0.83 | ٧     |

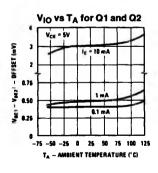

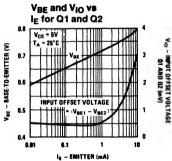

| V <sub>BE1</sub> -V <sub>BE2</sub> | Magnitude of Input Offset Voltage for Differential Pair | V <sub>CE</sub> = 5V, I <sub>E</sub> = 1 mA                                                                    |        | 0.48            | 5    | mV    |

| ΔV <sub>BE</sub> /ΔT               | Temperature Coefficient of Base to Emitter Voltage      | V <sub>CE</sub> = 5V, I <sub>E</sub> = 1 mA                                                                    |        | -1.9            |      | mV/°0 |

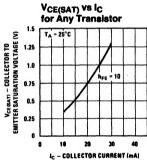

| V <sub>CE(SAT)</sub>               | Collector to Emitter Saturation Voltage                 | $I_C = 10 \text{ mA}, I_B = 1 \text{ mA}$                                                                      |        | 0.33            |      | V     |

| ΔV <sub>10</sub> /ΔΤ               | Temperature Coefficient of Input Offset Voltage         | I <sub>C</sub> = 1 mA, V <sub>CE</sub> = 5V                                                                    |        | 1.1             |      | μV/°( |

Note 1: The collector of each transistor is isolated from the substrate by an integral diode. The substrate must be connected to a voltage which is more negative than any collector voltage in order to maintain isolation between transistors and provide normal transistor action. To avoid undesired coupling between transistors, the substrate terminal should be maintained at either dc or signal (ac) ground. A suitable bypass capacitor can be used to establish a signal ground.

Note 2: If the transistors are forced into zener breakdown (V(BR)EBO), degradation of forward transfer current ratio (hFE) can occur.

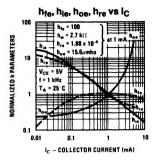

Note 3: See curve.

### **AC Electrical Characteristics**

| Symbol Parameter | Parameter                                      | Conditions                                                                            | Limits |                        |       | Units |

|------------------|------------------------------------------------|---------------------------------------------------------------------------------------|--------|------------------------|-------|-------|

|                  | Conditions                                     | Min                                                                                   | Тур    | Max                    | Uilla |       |

| NF               | Low Frequency Noise Figure                     | $ f = 1 \text{ kHz, } V_{CE} = 5V, $ $I_{C} = 100  \mu\text{A, } R_{S} = 1  k\Omega $ |        | 3.25                   |       | dB    |

| fT               | Gain Bandwidth Product                         | V <sub>CE</sub> = 5V, I <sub>C</sub> = 3 mA                                           | 300    | 500                    |       | MHz   |

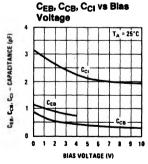

| C <sub>EB</sub>  | Emitter to Base Capacitance                    | $V_{EB} = 5V, I_{E} = 0$                                                              |        | 0.70                   |       | pF    |

| C <sub>CB</sub>  | Collector to Base Capacitance                  | $V_{CB} = 5V, I_{C} = 0$                                                              |        | 0.37                   |       | рF    |

| C <sub>CI</sub>  | Collector to Substrate Capacitance             | V <sub>CI</sub> = 5V, I <sub>C</sub> = 0                                              |        | 2.2                    |       | pF    |

| _ow Frequ        | ency, Small Signal Equivalent Circuit          | Characteristics                                                                       |        |                        |       |       |

| h <sub>fe</sub>  | Forward Current Transfer Ratio                 | f = 1 kHz, V <sub>CE</sub> = 3V, I <sub>C</sub> = 1 mA                                |        | 100                    |       |       |

| h <sub>ie</sub>  | Short Circuit Input Impedance                  | f = 1 kHz, V <sub>CE</sub> = 3V, I <sub>C</sub> = 1 mA                                |        | 3.5                    |       | kΩ    |

| h <sub>oe</sub>  | Open Circuit Output Impedance                  | $f = 1 \text{ kHz}, V_{CE} = 3V, I_{C} = 1 \text{ mA}$                                |        | 15.6                   |       | μmho  |

| h <sub>re</sub>  | Open Circuit Reverse Voltage<br>Transfer Ratio | f = 1 kHz, V <sub>CE</sub> = 3V,<br>I <sub>C</sub> = 1 mA                             |        | 1.8 x 10 <sup>-4</sup> |       |       |

| Admittance       | e Characteristics                              |                                                                                       |        |                        |       |       |

|                  | Farmed Transfer Admittages                     | 4 44415 1/ 01/1 4 554                                                                 |        | 04 14.5                | 1     |       |

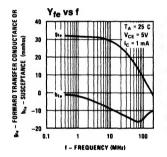

| Y <sub>fe</sub> | Forward Transfer Admittance | f = 1 MHz, V <sub>CE</sub> = 3V, I <sub>C</sub> = 1 mA | 31 — j 1.5     | mmho |

|-----------------|-----------------------------|--------------------------------------------------------|----------------|------|

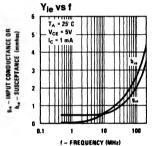

| Yie             | Input Admittance            | f = 1 MHz, V <sub>CE</sub> = 3V, I <sub>C</sub> = 1 mA | 0.3 + j 0.04   | mmho |

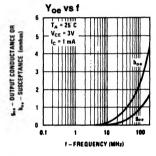

| Yoe             | Output Admittance           | f = 1 MHz, V <sub>CE</sub> = 3V, I <sub>C</sub> = 1 mA | 0.001 + j 0.03 | mmho |

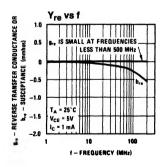

| Yre             | Reverse Transfer Admittance | f = 1 MHz, V <sub>CE</sub> = 3V, I <sub>C</sub> = 1 mA | (Note 3)       | mmho |

Note 1: The collector of each transistor is isolated from the substrate by an integral diode. The substrate must be connected to a voltage which is more negative than any collector voltage in order to maintain isolation between transistors and provide normal transistor action. To avoid undesired coupling between transistors, the substrate terminal should be maintained at either dc or signal (ac) ground. A suitable bypass capacitor can be used to establish a signal ground.

Note 2: If the transistors are forced into zener breakdown (V<sub>(BR)EBO</sub>), degradation of forward transfer current ratio (h<sub>FE</sub>) can occur. Note 3: See curve.

## **Typical Performance Characteristics**

TL/H/7959-2

## **Typical Performance Characteristics** (Continued)

TL/H/7959-3