## PHASE LOCKED FREQUENCY CONTROLLER

ADVANCE DATA

- PRECISION PHASE LOCKED FREQUENCY CONTROL SYSTEM

- XTAL OSCILLATOR

- PROGRAMMABLE REFERENCE FRE-QUENCY DIVIDERS

- PHASE DETECTOR WITH ABSOLUTE FRE-QUENCY STEERING

- DIGITAL LOCK INDICATOR

- DOUBLE EDGE OPTION ON THE FRE-QUENCY FEEDBACK SENSE AMPLIFIER

- TWO HIGH CURRENT OP-AMPS

- 5V REFERENCE OUTPUT

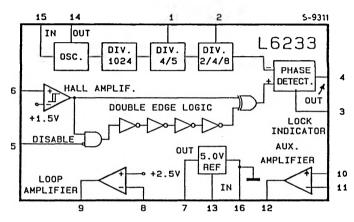

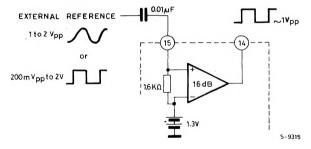

The L6233 is designed for use in phase locked frequency control loops. While optimized for precision speed control of DC motors, these device is universal enough for most applications that require phase locked control. A precise reference frequency can be generated using the device's high frequency oscillator and programmable frequency dividers. The oscillator operates using a broad range of crystals, or, can function as a buffer stage to an external frequency source.

The phase detector on these integrated circuit compares the reference frequency with a frequency/phase feedback signal. In the case of a motor, feedback is obtained at a hall output or other speed detection device. This signal is buffered by a sense amplifier that squares up the

signal as it goes into the digital phase detector. The phase detector responds proportionally to the phase error between the reference and the sense amplifier output. This phase detector includes absolute frequency steering to provide maximum drive signals when any frequency error exists. This feature allows optimum startup and lock times to be realized.

Two op-amps are included that can be configured to provide necessary loop filtering. The outputs of these op-amps will source or sink in excess of 16mA, so they can provide a low impedance control signal to driving circuits. Additional features include a double edge option on the sense amplifier that can be used to double the loop reference frequency for increased loop bandwidths. A digital lock signal is provided that indicates when there is zero frequency error and a 5V reference output allows DC operating levels to be accurately set.

**DIP-16 Plastic** (0.25)

20 PLCC

ORDERING NUMBERS: L6233 (DIP-16)

L6233 (DIP-16) L6233P (20 PLCC)

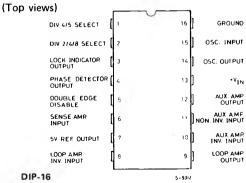

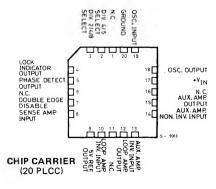

## CONNECTION DIAGRAMS

## ABSOLUTE MAXIMUM RATINGS

| Т                | Supply voltage Power dissipation (T <sub>amb</sub> ≤ 70°C) Operating temperature range | 14<br>1<br>0 to 70 | °C<br>W<br>V |

|------------------|----------------------------------------------------------------------------------------|--------------------|--------------|

| T <sub>stg</sub> | Storage temperature                                                                    | -65 to 150         | °C           |

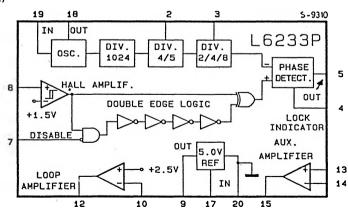

# BLOCK DIAGRAMS (DIP-16)

## (PLCC PACKAGE)

**ELECTRICAL CHARACTERISTICS** (Unless otherwise stated, specifications hold for  $T_{amb} = 0^{\circ}C$  to  $+70^{\circ}C$ ;  $+V_{IN} = 12V$ )

|                               | Parameter                       | Test Conditions                                   | Min. | Тур.  | Max. | Unit |

|-------------------------------|---------------------------------|---------------------------------------------------|------|-------|------|------|

| I <sub>S</sub> Supply current |                                 |                                                   |      | 20    |      | mA   |

| REFER                         | ENCE                            |                                                   | •    |       |      |      |

| V <sub>REF</sub>              | Output voltage                  |                                                   | 4.75 | 5.0   | 5.25 | V    |

| ΔV <sub>REF</sub>             | Load Regulation                 | I <sub>OUT</sub> = 0 to 7mA                       |      | 5.0   | 20   | mV   |

| ۵V <sub>REF</sub>             | Line regulation                 | +V <sub>IN</sub> = 8 to 12V                       |      | 2.0   | 20   | mV   |

| Isc                           | Short circuit current           | V <sub>OUT</sub> = 0V                             |      | 35    |      | mA   |

| OSCILL                        | ATOR                            |                                                   |      |       |      |      |

| G <sub>v</sub>                | DC voltage gain                 | Oscillator input to oscillator output             |      | 16    |      | dB   |

| V <sub>IB</sub>               | Input DC level                  | Oscillator input pin open, $T_j = 25^{\circ}C$    |      | 1.3   |      | V    |

| Z <sub>IN</sub> *             | Input impedance                 | $V_{1N} = V_{1B} \pm 0.5V,$ $T_{j} = 25^{\circ}C$ |      | 1.6   |      | ΚΩ   |

| V <sub>o</sub>                | Output DC level                 | Oscillator input pin open T <sub>j</sub> = 25°C   |      | 1.4   |      | V    |

| f <sub>o</sub> MAX            | Maximum operating frequency     |                                                   | 10   |       |      | MHz  |

| DIVIDE                        | RS                              |                                                   |      |       |      |      |

| f <sub>o</sub> MAX            | Maximum input frequency         | Input = 1V <sub>pp</sub> at oscillator input      | 10   |       |      | MHz  |

|                               | Div. 4/5 input current          | Input = 5V (Div. by 4)                            |      | 150   | 500  | μΑ   |

|                               | Div. 4/5 input current          | Input = 0V (Div. by 5)                            | -5.0 | 0.0   | 5.0  | μΑ   |

| V <sub>TH</sub>               | Div. 4/5 threshold              |                                                   | 0.5  | 1.6   | 2.2  | ٧    |

|                               | Div. 2/4/8 input current        | Input = 5V (Div. by 8)                            |      | 150   | 500  | μА   |

|                               |                                 | Input = 0V (Div. by 2)                            | -500 | - 150 |      | μА   |

|                               | Div. 2/4/8 open circuit voltage | Input current = 0µA (Div. by 4)                   | 1.5  | 2.5   | 3.5  | ٧    |

|                               | Div. by 2 threshold             |                                                   | 0.35 | 0.8   |      | ٧    |

|                               | Div. by 4 threshold             |                                                   | 1.5  |       | 3.5  | ٧    |

|                               | Div. by 8 threshold             | Volts below V <sub>REF</sub>                      | 0.35 | 0.8   |      | ٧    |

| SENSE                         | AMPLIFIER                       |                                                   |      |       |      |      |

| VT                            | Threshold voltage               | Percent of V REF                                  |      | 30    |      | %    |

| нт                            | Threshold hysteresis            |                                                   |      | 10    |      | mV   |

| l <sub>b</sub>                | Input bias current              | Input = 1.5V                                      |      | -0.2  |      | μΑ   |

| OOUBL                         | E EDGE DISABLE INPUT            |                                                   |      |       |      |      |

|                               | Input current                   | Input = 5V (Disabled)                             |      | 150   | 500  | μΑ   |

| V <sub>I</sub>                |                                 | Input = 0V (Enabled)                              | -5.0 | 0.0   | 5.0  | μА   |

| VT                            | Threshold voltage               |                                                   | 0.5  | 1.6   | 2.2  | ٧    |

## ELECTRICAL CHARACTERISTICS (continued)

| Parameter       |                                        | Test Conditions                   |                             | Min. | Тур. | Max. | Unit |

|-----------------|----------------------------------------|-----------------------------------|-----------------------------|------|------|------|------|

| PHASE           | DETECTOR                               |                                   |                             |      |      | •    |      |

| V <sub>ОН</sub> | High output level                      | Positive Phase/Freq. Error, Ve    | oits Below V <sub>REF</sub> |      | 0.2  | 0.5  | V    |

| VoL             | Low output level                       | Negative Phase/Freq. Error        |                             |      | 0.2  | 0.5  | V    |

| V <sub>OM</sub> | Mid output level                       | Zero Phase/Freq. Error, Perce     | ent of V <sub>REF</sub>     | 47   | 50   | 53   | %    |

|                 | High level maximum source current      | V <sub>OUT</sub> = 4.3V           |                             | 2.0  | 8.0  |      | mA   |

|                 | Low level maximum sink curr.           | V <sub>OUT</sub> = 0.7V           |                             | 2.0  | 5.0  |      | mA   |

|                 | Mid level output impedance<br>(Note 2) | I <sub>OUT</sub> = -200 to +200μA | T <sub>j</sub> = 25°C       |      | 6.0  |      | ΚΩ   |

| LOCK            | INDICATOR OUTPUT                       |                                   |                             |      |      |      |      |

| $V_{sat}$       | Saturation voltage                     | Freq. Error,                      | I <sub>OUT</sub> = 5mA      |      | 0.3  | 0.45 | V    |

|                 | Leakage current                        | Zero Freq. Error                  | V <sub>OUT</sub> = 12V      |      | 0.1  | 1.0  | μΑ   |

| LOOP            | AMPLIFIER                              |                                   |                             |      |      |      |      |

|                 | NON INV. reference voltage             | Percent of V <sub>REF</sub>       |                             | 47   | 50   | 53   | %    |

| I <sub>b</sub>  | Input bias current                     | Input = 2.5V                      | ****                        | -0.8 | -0.2 | ļ    | μΑ   |

| G <sub>v</sub>  | Open loop gain                         |                                   |                             | 60   | 75   |      | dB   |

| SVR             | Supply voltage rejection               | +V <sub>IN</sub> = 8 to 12V       |                             | 70   | 100  |      | dB   |

|                 | Short circuit current                  | Source,                           | V <sub>OUT</sub> = 0V       | 16   | 35   |      | mA   |

| <sup>I</sup> sH | Short circuit current                  | Sink,                             | V <sub>OUT</sub> = 5V       | 16   | 30   |      | mA   |

| AUXIL           | IARY OP-AMP                            |                                   |                             |      |      |      |      |

| ٧ <sub>os</sub> | Input offset voltage                   | V <sub>CM</sub> = 2.5V            |                             | - ×  |      | 8    | mV   |

| l <sub>b</sub>  | Input bias current                     | V <sub>CM</sub> = 2.5V            |                             |      | 200  |      | mA   |

| los             | Input offset current                   | V <sub>CM</sub> = 2.5V            |                             | 1    | 10   |      | mA   |

| G <sub>v</sub>  | Open loop gain                         |                                   |                             | 70   | 120  |      | dB   |

| SVR             | Supply voltage rejection               | +V <sub>IN</sub> = 8 to 12V       |                             | 70   | -100 |      | dB   |

| CMR             | Common mode rejection                  | V <sub>CM</sub> = 0 to 10V        |                             | 70   | 100  |      | dB   |

|                 |                                        | Source,                           | V <sub>OUT</sub> = 0V       |      | 35   |      | mA   |

| I <sub>SH</sub> | Short circuit current                  | Sink,                             | V <sub>OUT</sub> = 5V       |      | 30   |      | mA   |

<sup>\*</sup> These impedance levels will vary with  $T_j$  at about 1700ppm/°C

## THERMAL DATA

| R <sub>th j-amb</sub> | Thermal resistance junction-ambient | max | 100 | °C/W |

|-----------------------|-------------------------------------|-----|-----|------|

|-----------------------|-------------------------------------|-----|-----|------|

## APPLICATION INFORMATION

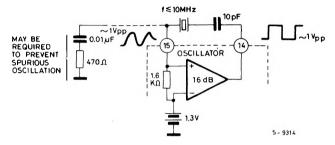

## **Determining the Oscillator Frequency**

The frequency at the oscillator is determined by: the desired RPM of the motor, the divide ratio selected, the number of poles in the motor, and the state of the double edge select pin.

f<sub>osc</sub> (Hz) = (Divide Ratio) • (Motor RPM) • (1/60 SEC/MIN) • (No. of Rotor Poles/2) • (× 2 if Pin 5 Low)

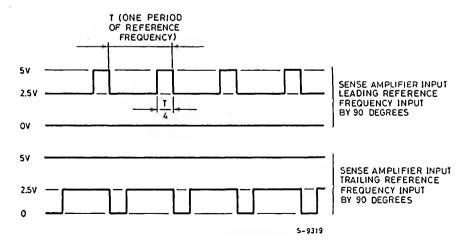

The resulting reference frequency appearing at the phase detector inputs is equal to the oscillator frequency divided by the selected divide ratio. If the double edge option is used, (Pin 5 low), the frequency of the sense amplifier input signal is doubled by responding to both the rising and falling edges of the input signal. Using this option the loop reference frequency can be doubled for a given motor RPM.

Fig. 1 - Recommended Oscillator Configuration Using AT Cut Quartz XTAL

Fig. 2 - External Reference Frequency Input

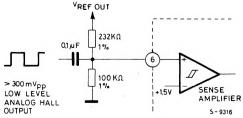

Fig. 3 - Method for Deriving Rotation Feedback Signal From Analog Hall Effect Device

<sup>\*</sup> This signal may require filtering if chopped mode drive scheme is used.

## APPLICATION INFORMATION (continued)

## Phase detector operation

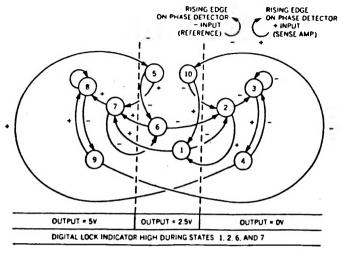

The phase detector on these devices is a digital circuit that responds to the rising edges of the detector's two inputs. The phase detector output has three states: a high, 5V state, a low, 0V state, and a middle, 2.5V state. In the high and low states the output impedance of the detector is low, the middle state output impedance is high, tipically  $6.0 \, \mathrm{K} \Omega$ . When there is any static frequency difference between the inputs the detector output is fixed at its high level if the +input (the sense amplifier signal) is greater in frequency, and fixed at its low level if the -input (the reference frequency signal) is greater in frequency.

When the frequencies of the two inputs to the detector are equal the phase detector switches between its middle state and either the high or low states, depending on the relative phase of the two signals. If the +input is leading in phase then, during each period of the input frequency, the detector output will be high for a time equal to the time difference between the rising edges of the inputs, and will be at its middle level the remainder of the period. If the phase relationship is reversed then the detector will go low for a time proportional to the phase difference of the inputs. The resulting gain of the

phase detector,  $K\phi$ , is  $5V/4\pi$ , radians, or about 0.4V/radian. The dynamic range of the detector is  $\pm 2\pi$  radians.

The operation of the phase detector is illustrated in the figures below. The upper figure shows typical voltage waveforms seen at the detector output for leading and lagging phase conditions. The lower figure is a state diagram of the phase detector logic. In this figure, the circles represent the 10 possible states of the logic and the connecting arrows the transition events/paths to and from these states. Transition arrows that have a clockwise rotation are the result of a rising edge on the +input, and conversely, those with counter-clockwise rotation are tied to the rising edge on the-input signal.

The normal operational states of the logic are 6 and 7 for positive phase error, 1 and 2 for a negative phase error. States 8 and 9 occur during positive frequency error, 3 and 4 during negative frequency error. States 5 and 10 occur only as the inputs cross over from a frequency error to a normal phase error only condition. The level of the phase detector output is determined by the logic state as defined in the state diagram figure. The lock indicator output is high, off, when the detector is in states 1, 2, 6 or 7.

Fig. 4 - Typical Phase Detector Output Waveforms

Fig. 5 - Phase Detector State Diagram

5-9421

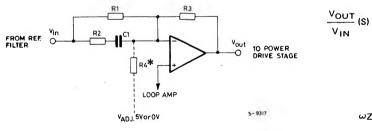

Fig. 6 - Suggested Loop Filter Configuration

$$\frac{V_{OUT}}{V_{IN}}(S) = \frac{R3}{R1} \cdot \frac{1 + S/\omega Z}{1 + S/\omega P}$$

$$\omega P = \frac{1}{R2C1}$$

$$\omega Z = \frac{1}{(R1 + R2) C1}$$

\* The statistic phase error of the loop is easily adjusted by adding resistor, R4, as shown. To lock at zero phase error R4 is determined by:

$$R4 = \frac{2.5V \cdot R3}{|\Delta V_{OUT}|}$$

Where:  $|\Delta V_{OUT}| = |V_{OUT} - 2.5V|$ and  $V_{OUT} = DC$  Operating Voltage At Loop Amplifier Output During Phase Lock

$(V_{OUT} - 2.5) > 0$  R4 Goes to 0V  $(V_{OUT} - 2.5) < 0$  R4 Goes to 5.0V

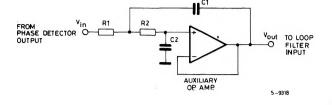

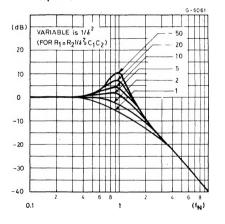

Fig. 7 - Reference Filter Configuration

$$\frac{V_{OUT}}{V_{IN}}(S) = \frac{1}{1 + \frac{S2}{\omega_N} + \frac{S^2}{\omega_N^2}}$$

$$\omega_N = \frac{1}{\sqrt{R1R2C1C2}}$$

$$\delta = \frac{1}{2Q} = \frac{1}{2} \sqrt{\frac{C2}{C1}} \frac{R1 + R2}{\sqrt{R1R2}}$$

Note: with R1 = R2

$$\delta = \sqrt{\frac{C2}{C1}}$$

Fig. 8 - Reference Filter Design Aid - Gain Response

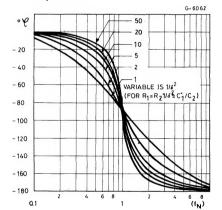

Fig. 9 - Reference Filter Design Aid - Phase Response