# 1.5A POWER SWITHING REGULATOR

PRELIMINARY DATA

- 1.5A OUTPUT CURRENT

- 5.1V TO 40V OUTPUT VOLTAGE RANGE

- PRECISE (± 2 %) ON-CHIP REFERENCE

- HIGH SWITCHING FREQUENCY

- VERY HIGH EFFICIENCY (UP TO 90%)

- VERY FEW EXTERNAL COMPONENTS

- SOFT-START

- INTERNAL LIMITING CURRENT

- THERMAL SHUTDOWN

The L4962 is a monolithic power switching regulator delivering 1.5A at a voltage veriable from 5V to 40V in step down configuration.

Features of device include current limiting, soft start, thermal protection and 0 to 100% duty cycle for continuous operating mode.

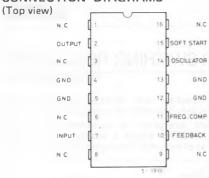

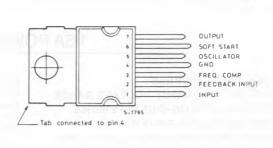

The L4962 is mounted in a 16-lead Powerdip

plastic package and Heptawatt package and requires very few external components.

Efficient operation at switching frequencies up to 150KHz allows a reduction in the size and cost of external filter components.

#### ABSOLUTE MAXIMUM RATINGS

| V <sub>2</sub>      | Input voltage                                               |        | 50  | V  |

|---------------------|-------------------------------------------------------------|--------|-----|----|

| V7 - V2             | Input to output voltage difference                          |        | 50  | V  |

| V <sub>2</sub>      | Negative output DC voltage                                  |        | - 1 | V  |

| 2                   | Output peak voltage at $t = 0.1\mu s$ , $f = 100KHz$        |        | -5  | V  |

| $V_{11}, V_{15}$    | Voltage at pin 11, 15                                       |        | 5.5 | V  |

| V <sub>10</sub>     | Voltage at pin 10                                           |        | 7   | V  |

| 111                 | Pin 11 sink current                                         |        | 1   | mA |

| 114                 | Pin 14 source current                                       |        | 20  | mA |

| P <sub>tot</sub>    | Power dissipation at $T_{pins} \leq 90^{\circ}C$ (Powerdip) |        | 4.3 | W  |

| tot                 | $T_{case} \leq 90^{\circ} C$ (Heptawatt)                    |        | 15  | W  |

| $T_{j}$ , $T_{stg}$ | Junction and storage temperature                            | -40 to | 150 | °C |

#### **CONNECTION DIAGRAMS**

| THERMAL DATA                                                              |                                                                                                                   |  | Heptawatt       | Powerdip          |  |  |

|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--|-----------------|-------------------|--|--|

| R <sub>th J-case</sub><br>R <sub>th J-pins</sub><br>R <sub>th J-amb</sub> | Thermal resistance junction-case max Thermal resistance junction-pins max Thermal resistance junction-ambient max |  | 4°C/W<br>50°C/W | 14°C/W<br>80°C/W* |  |  |

Obtained with the GND pins soldered to printed circuit with minimized copper area.

# PIN FUNCTIONS

| HEPTAWATT | POWERDIP             | NAME                      | FUNCTION                                                                                                                                                                                            |  |  |

|-----------|----------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1         | 7                    | SUPPLY VOLTAGE            | Unregulated voltage input. An internal regulator powers the internal logic.                                                                                                                         |  |  |

| 2         | 10                   | FEEDBACK INPUT            | The feedback terminal of the regulation to the output is connected directly to this minal for 5.1V operation; it is connected vidivider for higher voltages.                                        |  |  |

| 3         | 11                   | FREQUENCY<br>COMPENSATION | A series RC network connected between this terminal and ground determines the regulation loop gain characteristics.                                                                                 |  |  |

| 4         | 4, 5, 12, 13         | GROUND                    | Common ground terminal.                                                                                                                                                                             |  |  |

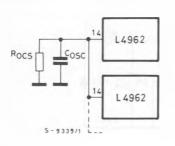

| 5         | 14                   | OSCILLATOR                | A parallel RC network connected to this terminal determines the switching frequency. This pin must be connected to pin 7 input when the internal oscillator is used.                                |  |  |

| 6         | 15                   | SOFT START                | Soft start time constant. A capacitor is connected between this terminal and ground to define the soft start time constant. The capacitor also determines the average short circuit output current. |  |  |

| 7         | 2                    | OUTPUT                    | Regulator output.                                                                                                                                                                                   |  |  |

|           | 1, 3, 6,<br>8, 9, 16 |                           | N.C.                                                                                                                                                                                                |  |  |

# **ELECTRICA\_ CHARACTERISTICS** (Refer to the test circuit, $T_j = 25^{\circ}C$ , $V_1 = 35V$ , unless otherwise specified)

|                                   | Parameter                                         | rameter Test Conditions                                                |                               | Min.             | Тур. | Max. | Unit  |

|-----------------------------------|---------------------------------------------------|------------------------------------------------------------------------|-------------------------------|------------------|------|------|-------|

| YNAN                              | IIC CHARACTERISTICS                               |                                                                        |                               |                  |      |      |       |

| Vo                                | Output voltage range                              | V <sub>1</sub> = 46V                                                   | I <sub>0</sub> = 1A           | V <sub>ref</sub> |      | 40   | V     |

| V <sub>I</sub>                    | Input voltage range                               | V <sub>o</sub> = V <sub>ref</sub> to 36V                               | I <sub>o</sub> = 1.5A         | 9                |      | 46   | V     |

| ΔV <sub>o</sub>                   | Line regulation                                   | V <sub>I</sub> = 10V to 40V                                            | o = Vref Io = 1A              |                  | 15   | 50   | mV    |

| ΔV <sub>o</sub>                   | Load regulation                                   | Vo = Vref                                                              | I <sub>o</sub> = 0.5A to 1.5A |                  | 8    | 20   | mV    |

| V <sub>ref</sub>                  | Internal reference voltage (pin 10)               | V <sub>1</sub> = 9V to 46V                                             | I <sub>0</sub> = 1A           | 5                | 5.1  | 5.2  | V     |

| $\frac{\Delta V_{ref}}{\Delta T}$ | Average temperature coefficient of refer, voltage | $T_j = 0^{\circ} C \text{ to } 125^{\circ} C$ $I_0 = 1 A$              |                               |                  | 0.4  |      | mV/°C |

| V <sub>d</sub>                    | Dropout voltage                                   | I <sub>o</sub> = 1.5A                                                  |                               |                  | 1.5  | 2    | V     |

| om                                | Maximum operating load current                    | V <sub>1</sub> = 9V to 46V<br>V <sub>0</sub> = V <sub>ref</sub> to 36V |                               | 1.5              |      |      | А     |

| I <sub>2L</sub>                   | Current limiting threshold (pin 2)                | $V_1 = 9V \text{ to } 46V$<br>$V_0 = V_{\text{ref}} \text{ to } 36V$   |                               | 2                |      | 3.3  | А     |

| I <sub>SH</sub>                   | Input average current                             | V <sub>I</sub> = 46V; output s                                         | hort-circuit                  |                  | 15   | 30   | mA    |

| η                                 | Efficiency                                        | f = 100KHz                                                             | Vo = Vref                     |                  | 70   |      | %     |

|                                   |                                                   | i <sub>o</sub> = 1A                                                    | V <sub>o</sub> = 12V          |                  | 80   |      | %     |

| SVR                               | Supply voltage ripple rejection                   | $\Delta V_{I} = 2V_{rms}$ $f_{r pple} = 100Hz$ $V_{o} = V_{ref}$       | I <sub>O</sub> = 1A           | 50               | 56   |      | dB    |

| f                                 | Switching frequency                               |                                                                        |                               | 85               | 100  | 115  | KHz   |

| Δf                                | Voltage stability of switching frequency          | V <sub>i</sub> = 9V to 46V                                             |                               |                  | 0.5  |      | %     |

| Δf<br>ΔT <sub>j</sub>             | Temperature stability of switching frequency      | T <sub>j</sub> = 0°C to 125°C                                          |                               |                  | 1    |      | %     |

| <sup>f</sup> max                  | Maximum operating switching frequency             | Vo = Vret                                                              | 1 <sub>0</sub> = 1A           | 120              | 150  |      | KHz   |

| T <sub>sd</sub>                   | Thermal shutdown junction temperature             |                                                                        |                               |                  | 150  |      | °c    |

# ELECTRICAL CHARACTERISTICS (continued)

|                    | Parameter                 | Test Conditions                       |                         | Min. | Тур. | Max. | Unit |

|--------------------|---------------------------|---------------------------------------|-------------------------|------|------|------|------|

| C CHA              | RACTERISTICS              |                                       |                         |      |      |      |      |

| I <sub>7Q</sub>    | Quiescent drain current   | 100% duty cycle<br>pins 2 and 14 open |                         |      | 30   | 40   | mA   |

|                    |                           | 0% duty cycle                         | V; = 46V                |      | 15   | 20   | mA   |

| -1 <sub>2</sub> L  | Output leakage current    | 0% duty cycle                         |                         |      |      | 1    | mA   |

| OFT ST             | ART                       |                                       |                         |      |      |      |      |

| 1 <sub>15</sub> SO | Source current            |                                       |                         | 100  | 130  | 160  | μА   |

| <sup> </sup> 15SI  | Sink current              |                                       |                         | 50   | 70   | 120  | μА   |

| RROR               | AMPLIFIER                 |                                       |                         |      |      |      |      |

| V <sub>11 H</sub>  | High level output voltage | V <sub>10</sub> = 4.7V                | I <sub>11</sub> = 100μA | 3.5  |      |      | V    |

| V <sub>11</sub> L  | Low level output voltage  | V <sub>10</sub> = 5.3V                | Ι <sub>11</sub> = 100μΑ |      |      | 0.5  | V    |

| l<br>11SI          | Sink output current       | V <sub>10</sub> = 5.3V                |                         | 100  | 150  |      | μА   |

| -l <sub>1150</sub> | Source output current     | V <sub>10</sub> = 4.7V                |                         | 100  | 150  |      | μΑ   |

| 110                | Input bias current        | V <sub>10</sub> = 5.2V                |                         |      | 2    | 10   | μА   |

| G <sub>v</sub>     | DC open loop gain         | V <sub>11</sub> = 1V to 3V            |                         | 46   | 55   |      | dB   |

mΑ

-114

Oscillator source current

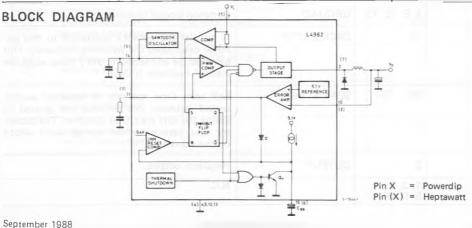

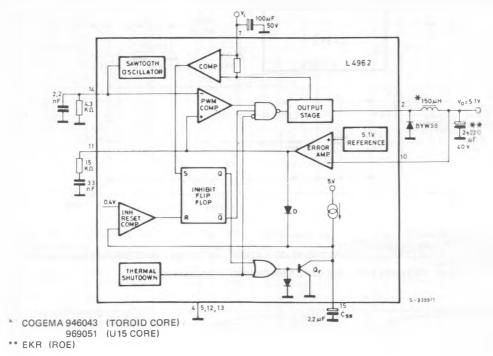

#### CIRCUIT OPERATION (refer to the block diagram)

The L4962 is a monolithic stepdown switching regulator providing output voltages from 5.1V to 40V and delivering 1.5A.

The regulation loop consists of a sawtooth oscillator, error amplifier, comparator and the output stage. An error signal is produced by comparing the output voltage with a precise 5.1V on-chip reference (zener zap trimmed to  $\pm~2\%$ ).

This error signal is then compared with the sawtooth signal to generate the fixed frequency pulse width modulated pulses which drive the output stage.

The gain and frequency stability of the loop can be adjusted by an external RC network connected to pin 11. Closing the loop directly gives an output voltage of 5.1V. Higher voltages are obtained by inserting a voltage divider.

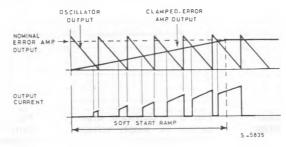

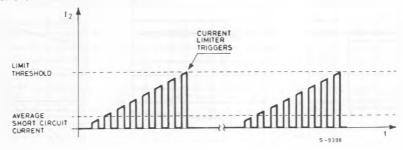

Output overcurrents at switch on are prevented by the soft start function. The error amplifier output is initially clamped by the external capacitor  $C_{ss}$  and allowed to rise, linearly, as this capacitor is charged by a constant current source. Output overload protection is provided in the form of a current limiter. The load current is sensed by a internal metal resistor connected to a comparator. When the load current exceeds a preset threshold this comparator sets a flip flop which disables the output stage and discharges the soft start capacitor. A second comparator resets the flip flop when the voltage across the soft start capacitor has fallen to 0.4V.

The output stage is thus re-enabled and the output voltage rises under control of the soft start network. If the overload condition is still present the limiter will trigger again when the threshold current is reached. The average short circuit current is limited to a safe value by the dead time introduced by the soft start network. The thermal overload circuit disables circuit operation when the junction temperature reaches about 150°C and has hysteresis to prevent unstable conditions.

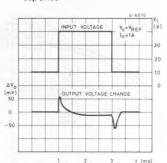

Fig. 1 - Soft start waveforms

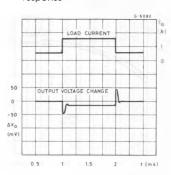

Fig. 2 - Current limiter waveforms

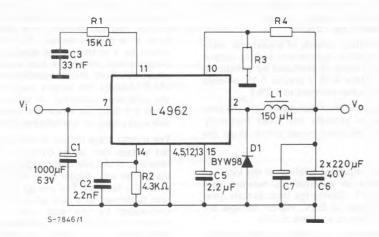

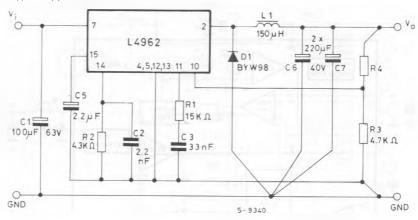

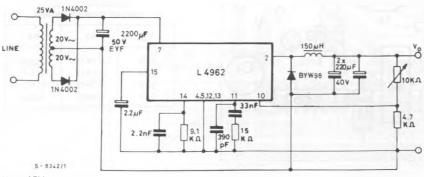

Fig. 3 - Test and application circuit (Powerdip)

- D<sub>1</sub>: BYW98 or 3A Schottky diode, 45V of VRRM;

L<sub>1</sub>: CORE TYPE MAGNETICS 58120 A2 MPP N° TURNS 45, WIRE GAUGE: 0.8mm (20 AWG)

- 3) C<sub>6</sub>, C<sub>7</sub>: ROE, EKR 220µF 40V

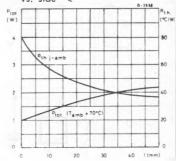

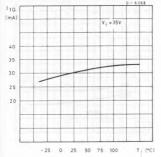

Fig. 4 ~ Quiescent drain current vs. supply voltage (0% duty cycle)

Fig. 5 - Quiescent drain current vs. supply voltage (100% duty cycle)

Fig. 6 - Quiescent drain current vs. junction temperature (0% duty cycle)

Fig. 7 - Quiescent drain current vs. junction temperature (100% duty cycle)

Fig. 8 - Reference voltage (pin 10) vs.  $V_1$  rdip) vs.  $V_1$

Fig. 9 - Reference voltage (pin 10) vs. junction temperature

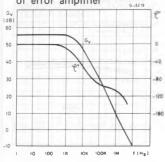

Fig. 10 - Open loop frequency and phase response of error amplifier

Fig. 11 - Switching frequency vs. input voltage

Fig. 12 - Switching frequency vs. junction tem-

Fig. 13 - Switching frequency vs. R2 (see test

Fig. 14 – Line transient response

Fig. 15 - Load transient response

Fig. 16 - Supply voltage ripple rejection vs. frequency

Fig. 17 - Dropout voltage between pin 7 and pin 2 vs. current at pin 2

Fig. 18 - Dropout voltage between pin 7 and 2 vs. junction temperature

Fig. 19 - Efficiency vs. output current

Fig. 20 - Efficiency vs. output current

Fig. 21 - Efficiency vs. output current

Fig. 22 - Efficiency vs. output voltage

Fig. 23 - Efficiency vs. output voltage

Fig. 24 - Maximum allowable power dissipation vs. ambient temperature (Powerdip)

#### APPLICATION INFORMATION

Fig. 25 - Typical application circuit

$C_1,\,C_6,\,C_7\colon$  EKR (ROE)  $D_1\colon$  BYW98 OR VISK340 (SCHOTTKY) SUGGESTED INDUCTORS  $(L_1)\colon$  MAGNETICS 58120 - A2MPP - 45 TURNS - WIRE GAUGE 0.8mm (20AWG) - COGEMA 946043 OR U15. GUP15, 60 TURNS 1mm, AIR GAP 0.8mm (20AWG) - COGEMA 969051

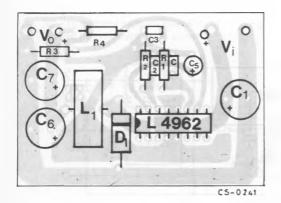

Fig. 26 - P.C. board and component layout of the circuit of Fig. 25 (1:1 scale)

|     | lesistor values<br>lard output 7 v |       |

|-----|------------------------------------|-------|

| Vo  | R3                                 | R4    |

| 12V | 4.7ΚΩ                              | 6.2ΚΩ |

| 15V | 4.7ΚΩ                              | 9.1KΩ |

| 18V | 4.7ΚΩ                              | 12ΚΩ  |

| 24V | 4.7ΚΩ                              | 18KΩ  |

### APPLICATION INFORMATION (continued)

Fig. 27 - A minimal 5.1V fixed regulator; very few components are required

Fig. 28 - Programmable power supply

$V_0 = 5.1V \text{ to } 15V$  $I_0 = 1.5A \text{ max}$

Load regulation (0.5A to 1.5A) = 10mV ( $V_0 = 5.1\text{V}$ )

Line regulation (220V  $\pm$  15% and to I<sub>O</sub> = 1A) = 15mV (V<sub>o</sub> = 5.1V)

## APPLICATION INFORMATION (continued)

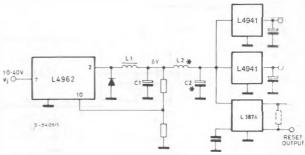

Fig. 29 - DC-DC converter 5.1V/4A, ± 12V/1A. A suggestion how to synchronize a negative output

L2 = COGEMA 946044 (946045)

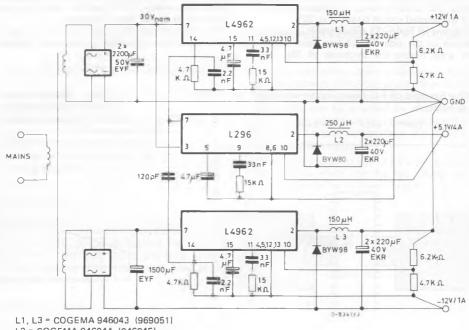

Fig. 30 - In multiple supplies several L4962s can be synchronized as shown

Fig. 31 - Preregulator for distributed supplies

L2 and C2 are necessary to reduce the switching frequency spikes when linear regulators are remote from L4962

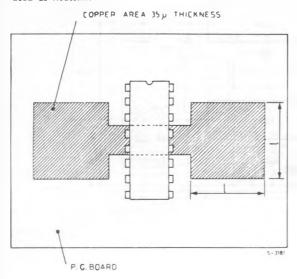

#### MOUNTING INSTRUCTION

The  $R_{th\,J-amb}$  of the L4962 can be reduced by soldering the GND pins to a suitable copper area of the printed circuit board (Fig. 32).

The diagram of figure 33 shows the  $R_{\text{th H-amb}}$  as a function of the side "2" of two equal square copper areas having the thickness of  $35\mu$  (1.4

mils). During soldering the pins temperature must not exceed 260°C and the soldering time must not be longer than 12 seconds.

The external heatsink or printed circuit copper area must be connected to electrical ground.

Fig. 32 - Example of P.C. board copper area which is used as heatsink

Fig. 33 - Maximum dissipable power and junction to ambient thermal resistance vs. side "?"