# Description

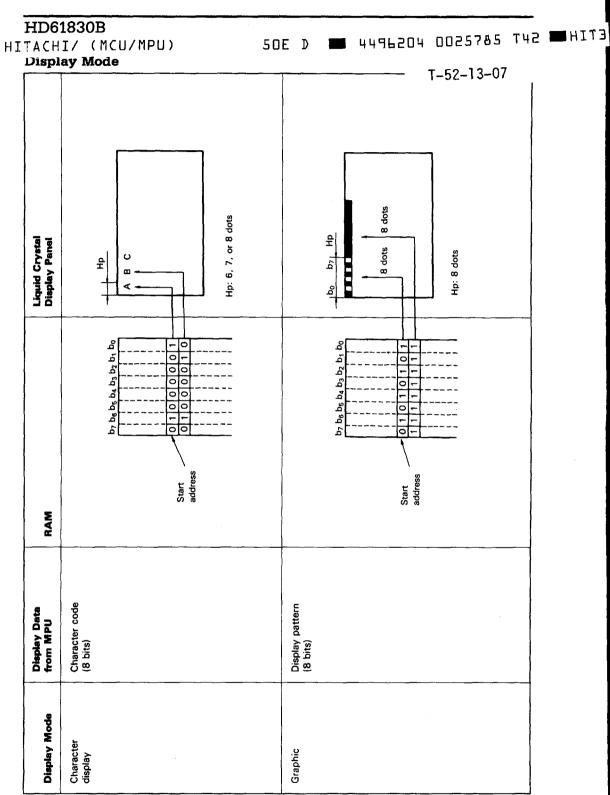

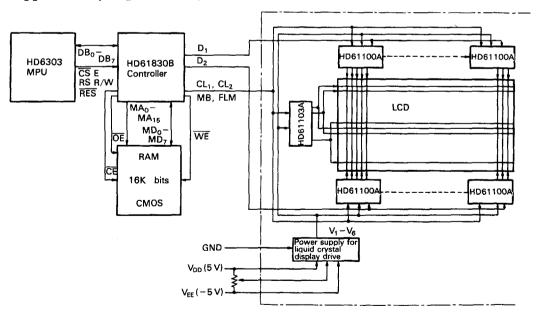

The HD61830B is a dot matrix liquid crystal graphic display controller LSI that stores the display data sent from an 8-bit microcontroller in the external RAM to generate dot matrix liquid crystal driving signals.

It has a graphic mode in which 1-bit data in the external RAM corresponds to the on/off state of 1 dot on liquid crystal display and a character mode in which characters are displayed by storing character codes in the external RAM and developing them into the dot patterns with the internal character generator ROM. Both modes can be provided for various applications.

The HD61830B is produced by the CMOS process. Thus, combined with a CMOS microcontroller it can complete a liquid crystal display device with lower power dissipation.

#### **Features**

- Dot matrix liquid crystal graphic display controller

- Display control capacity

- -Graphic mode: 512k dots (216 bytes)

- -Character mode: 4096 characters (212 characters)

- Internal character generator ROM: 7360 bits

- -160 types of 5 imes 7 dot characters

- -32 types of 5 imes 11 dot characters

- Total 192 characters

- Can be extended to 256 characters (4k bytes max.) by external ROM

- Interfaces to 8-bit MPU

- Display duty cycle (Can be selected by a program)

- Static to 1/128 duty cycle

- Various instruction functions

- Scroll, Cursor on/off/blink, Character blink, Bit manipulation

- Display method: Selectable A or B types

- Operating frequency: 2.4 MHz

- Low power dissipation

- Power supply: Single +5 V ± 10%

- CMOS process

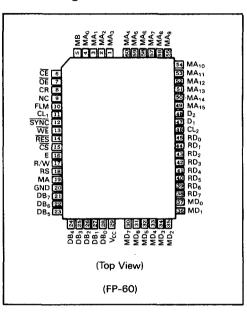

- Package: 60-pin plastic QFP (FP-60)

### Pin Arrangement

T-52-13-07

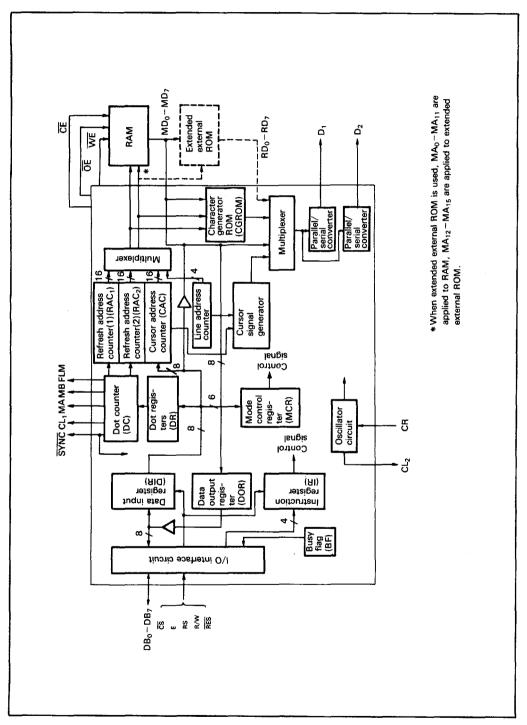

# **Block Diagram**

### **Block Functions**

### Registers

The HD61830B has the five types of registers: instruction register (IR), data input register (DIR), data output register (DOR), dot registers (DR), and mode control register (MCR).

The IR is a 4-bit register that stores the instruction codes for specifying MCR, DR, a start address register, a cursor address register, and so on. The lower order 4 bits DB0 to DB3 of data buses are written in it.

The DIR is an 8-bit register used to temporarily store the data written into the external RAM, DR, MCR, and so on.

The DOR is an 8-bit register used to temporarily store the data read from the external RAM. Cursor address information is written into the cursor address counter (CAC) through the DIR. When the memory read instruction is set in the IR (latched at the falling edge of E segnal), the data of external RAM is read to DOR by an internal operation. The data is transferred to the MPU by reading the DOR with the next instruction (the contents of DOR are output to the data bus when E is at the High level).

The DR are registers used to store dot information such as character pitches and the number of vertical dots and so on. The information sent from the MPU is written into the DR via the DIR.

The MCR is a 6-bit register used to store the data which specifies states of display such as display on/off and cursor on/off/blink. The information sent from the MPU is written in it via the DIR.

# Busy Flag (BF)

The busy flag = 1 indicates the HD61830B is performing an internal operation. Instructions cannot be accepted. As shown in Control Instruction, read busy flag, the busy flag is output on DB7 under the conditions of RS = 1, R/W = 1, and E = 1. Make sure the busy flag is 0 before writing the next instruction.

### Dot Counters (DC)

The dot counters are counters that generate liquid crystal display timing according to the contents of DR.

### T-52-13-07

### Refresh Address Counters (RAC1/RAC2)

The refresh address counters RAC1 and RAC2 control the addresses of external RAM, character generator ROM (CGROM), extended external ROM. The RAC1 is used for upper half of the screen and the RAC2 for the lower half. In the graphic mode, 16-bit data is output and used as the address signal of external RAM. In the character mode, the high order 4 bits (MA12-MA15) are ignored. The 4 bits of line address counter are output instead and used as the address of extended ROM.

### Character Generator ROM

The character generator ROM has 7360 bits in total and stores 192 types of character data. A character code (8 bits) from the external RAM and a line code (4 bits) from the line address counter are applied to its address signals, and it outputs 5-bit dot data.

The character font is  $5 \times 7$  (160 characters) or  $5 \times 11$  (32 characters). The use of extended ROM allows 8 × 16 (256 characters max.) to be used.

### **Cursor Address Counter**

The cursor address counter is a 16-bit counter that can be preset by instruction. It holds an address when the data of external RAM is read or written (when display dot data or a character code is read or written). The value of the cursor address counter is automatically increased by 1 after the display data is read or written and after the set/clear bit instruction is executed.

# **Cursor Signal Generator**

The cursor can be displayed by instruction in character mode. The cursor is automatically generated on the display specified by the cursor address and cursor position.

### Parallel/Serial Conversion

The parallel data sent from the external RAM, character generator ROM, or extended ROM is converted into serial data by two parallel/ serial conversion circuits and transferred to the liquid crystal driver circuits for upper screen and lower screen simultaneously.

T-52-13-07

# **Terminal Functions**

| Name     | Function                                                                                                                                                             |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DBO-DB7  | Data bus: Three-state I/O common terminal Data is transferred to MPU through DBO to DB7.                                                                             |

| CS       | Chip select: Selected state with $\overline{CS} = 0$                                                                                                                 |

| R/W      | Read/Write: R/W = 1: MPU ← HD61830B<br>R/W = 0: MPU → HD61830B                                                                                                       |

| RS       | Register select: RS = 1: Instruction register RS = 0: Data register                                                                                                  |

| E        | Enable: Data is written at the fall of E Data can be read while E is 1                                                                                               |

| CR       | External clock input                                                                                                                                                 |

| RES      | Reset: RES = 0 results in display off, slave mode and Hp = 6                                                                                                         |

| MAO-MA15 | External RAM address output In character mode, the lane code for external CG is output through MA12 to MA15 (O: Character 1st line, F: Character 16th line)          |

| MDO-MD7  | Display data bus: Three-state I/O common terminal                                                                                                                    |

| RDO-RD7  | ROM data input: Dot data from external character generator is input                                                                                                  |

| WE       | Write enable: Write signal for external RAM                                                                                                                          |

| CL2      | Display data shift clock for LCD drivers                                                                                                                             |

| CL1      | Display data latch signal for LCD drivers                                                                                                                            |

| FLM      | Frame signal for display synchronization                                                                                                                             |

| MA       | Signal for converting liquid crystal driving signal into AC, A type                                                                                                  |

| МВ       | Signal for converting liquid crystal driving signal into AC, B type                                                                                                  |

| D1, D2   | Display data serial output D1: For upper half of screen D2: For lower half of screen                                                                                 |

| SYNC     | Synchronous signal for parallel operation Three-state I/O common terminal (with pull-up MOS) Master: Synchronous signal is output Slave: Synchronous signal is input |

| CE       | Chip enable $\overline{\text{CE}} = 0$ : Chip enables make external RAM in active                                                                                    |

| ŌĒ       | Output enable  OE = 1: Output enable informs external RAM that HD61830B requires data bus                                                                            |

| NC       | Unused terminal. Don't connect any wires to this terminal                                                                                                            |

### T-52-13-07

### **Absolute Maximum Ratings**

| Item                  | Symbol             | Value                          | Unit | Note |

|-----------------------|--------------------|--------------------------------|------|------|

| Supply voltage        | Vcc                | - 0.3 to + 0.7                 | V    | 1, 2 |

| Terminal voltage      | V <sub>T</sub>     | - 0.3 to V <sub>CC</sub> + 0.3 | V    | 1, 2 |

| Operating temperature | T <sub>opr</sub> - | - 20 to + 75                   | *C   |      |

| Storage temperature   | T <sub>stg</sub>   | - 55 to + 125                  | °C   |      |

- Notes: 1. All voltage is referred to GND = 0 V.

- 2. If LSIs are used beyond absolute maximum ratings, they may be permanently destroyed. We strongly recommend that you use the LSIs within electrical characteristic limits for normal operation, because use beyond these conditions will cause malfunction and poor reliability.

### **Electrical Characteristics**

| Item                        | Symbol           | Min                   | Тур | Max                 | Unit | <b>Test Condition</b>                       | Note |

|-----------------------------|------------------|-----------------------|-----|---------------------|------|---------------------------------------------|------|

| Input high voltage (TTL)    | ViH              | 2.2                   | _   | Vcc                 | ٧    |                                             | 1    |

| Input low voltage (TTL)     | VIL              | 0                     | _   | 0.8                 | V    |                                             | 2    |

| Input high voltage          | VIHR             | 3.0                   | _   | Vcc                 | V    |                                             | 3    |

| Input high voltage (CMOS)   | VIHC             | 0.7 V <sub>CC</sub>   | _   | Vcc                 | V    |                                             | 4    |

| Input low voltage (CMOS)    | VILC             | 0                     | _   | 0.3 V <sub>CC</sub> | ٧    |                                             | 4    |

| Output high voltage (TTL)   | VoH              | 2.4                   | _   | Vcc                 | V    | $-i_{OH} = 0.6 \text{ mA}$                  | 5    |

| Output low voltage (TTL)    | V <sub>OL</sub>  | 0                     | _   | 0.4                 | ٧    | I <sub>OL</sub> = 1.6 mA                    | 5    |

| Output high voltage (CMOS)  | Vonc             | V <sub>CC</sub> - 0.4 | _   | Vcc                 | ٧    | - I <sub>OH</sub> = 0.6 mA                  | 6    |

| Output low voltage (CMOS)   | Volc             | 0                     | _   | 0.4                 | ٧    | I <sub>OI</sub> = 0.6 mA                    | 6    |

| Input leakage current       | l <sub>IN</sub>  | - 5                   | _   | 5                   | μΑ   | VIN = 0-VCC                                 | 7    |

| Three-state leakage current | I <sub>TSL</sub> | - 10                  | _   | 10                  | μΑ   | V <sub>OUT</sub> = 0-V <sub>CC</sub>        | 8    |

| Pull-up current             | l <sub>PL</sub>  | 2                     | 10  | 20                  | μΑ   | V <sub>in</sub> = GND                       | 9    |

| Power dissipation           | Pw               | _                     |     | 50                  | mW   | External clock<br>f <sub>cp</sub> = 2.4 MHz | 10   |

- Notes: 1. Applied to input terminals and I/O common terminals, except terminals SYNC, CR, and RES.

- 2. Applied to input terminals and I/O common terminals, except terminals SYNC and CR.

- 3. Applied to terminal RES

- 4. Applied to terminals SYNC and CR

- 5. Applied to terminals DBO-DB7, WE, MAO-MA15, OE, CE, and MDO-MD7.

6. Applied to terminals SYNC, FLM, CL1, CL2, D1, D2, MA, and MB.

- 7. Applied to input terminals.

- 8. Applied to I/O common terminals. However, the current which flows into the output drive MOS is excluded.

- 9. Applied to SYNC, DBO-DB7, and RDO-RD7.

- 10. The current which flows into the input and output circuits is excluded. When the input of CMOS is in the intermediate level, current flows through the input circuit, resulting in the increase of power supply current. To avoid this, input must be fixed at high or low.

T-52-13-07

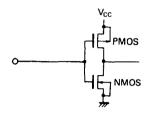

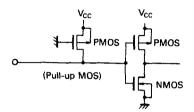

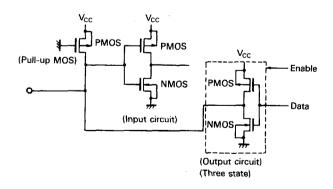

### Input Terminal

Applicable terminal:  $\overline{CS}$ , E, RS, R/W,  $\overline{RES}$ , CR (Without pull-up MOS)

Applicable terminal: RD0 – RD7 (With pull-up MOS)

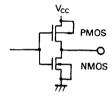

### **Output Terminal**

Applicable terminal: CL1, CL2, MA, MB, FLM, D1, D2, WE, OE, CE, MA0-MA15

### I/O Common Terminal

Applicable terminal: DB0-DB7, \$\overline{SYNC}\$, MD0-MD7 (MD0-MD7 have no pull-up MOS)

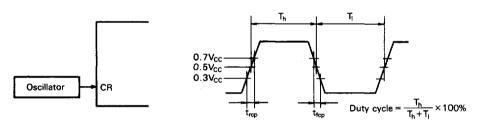

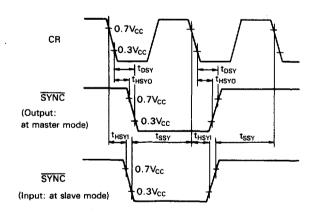

| Clock Operation T-52-13-07         |                   |             |     |      |      |      |  |  |  |

|------------------------------------|-------------------|-------------|-----|------|------|------|--|--|--|

| İtem                               | Symbol            | Min         | Тур | Max  | Unit | Note |  |  |  |

| External clock operating frequency | f <sub>cp</sub>   | 100         |     | 2400 | kHz  | 1    |  |  |  |

| External clock duty                | Duty              | 47.5        | 50  | 52.5 | %    | 1    |  |  |  |

| External clock rise time           | t <sub>rcp</sub>  |             | _   | 25.0 | ns   | 1    |  |  |  |

| External clock fall time           | t <sub>fcp</sub>  |             | _   | 25.0 | ns   | 1    |  |  |  |

| SYNC output hold time              | thsyo             | 30          | _   |      | ns   | 2, 3 |  |  |  |

| SYNC output delay time             | t <sub>DSY</sub>  | <del></del> | _   | 210  | ns   | 2, 3 |  |  |  |

| SYNC input hold time               | t <sub>HSYI</sub> | 10          |     | _    | ns   | 2    |  |  |  |

| SYNC input set-up time             | tssy              | _           | _   | 180  | ns   | 2    |  |  |  |

Notes: 1. Applied to external clock input terminal.

# 2. Applied to SYNC terminal.

### 3. Testing load circuit.

T-52-13-07

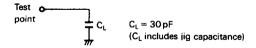

### **MPU** Interface

450

| Item               |            | Symbol           | Min  | Тур | Max | Unit      |

|--------------------|------------|------------------|------|-----|-----|-----------|

| Enable cycle time  |            | tcyc             | 1.0  | _   | _   | μS        |

| Enable pulse width | High level | <sup>1</sup> WEH | 0.45 | _   | _   | μS        |

|                    | Low level  | t <sub>WEL</sub> | 0.45 |     | _   | μS        |

| Enable rise time   |            | t <sub>Er</sub>  | _    |     | 25  | ns        |

| Enable fall time   |            | t <sub>Ef</sub>  | -    | _   | 25  | ns        |

| Setup time         |            | tas              | 140  |     | _   | ns        |

| Data setup time    |            | t <sub>DSW</sub> | 225  | _   | _   | ns        |

| Data delay time    |            | t <sub>DDR</sub> | _    |     | 225 | ns (Note) |

| Data hold time     |            | t <sub>DHW</sub> | 10   | _   | _   | ns        |

| Address hold time  |            | t <sub>AH</sub>  | 10   | _   | _   | ns        |

| Data hold time     |            | t <sub>DH</sub>  | 20   |     | _   | ns        |

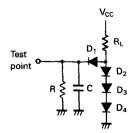

Note: The following load circuit is connected for specification:

2

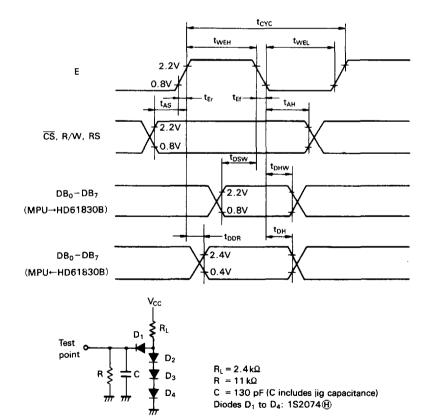

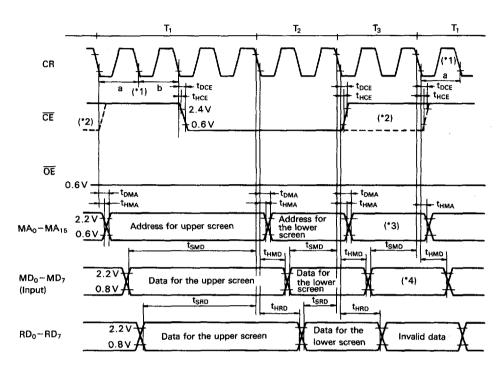

| External RAM and ROM              | xternal RAM and ROM Interface |     |     |              |      |         |  |  |  |  |

|-----------------------------------|-------------------------------|-----|-----|--------------|------|---------|--|--|--|--|

| Item                              | Symbol                        | Min | Тур | Max          | Unit | Note    |  |  |  |  |

| MA0-MA15 delay time               | t <sub>DMA</sub>              |     | _   | 300          | ns   | 1, 2, 3 |  |  |  |  |

| MA0-MA15 hold time                | t <sub>HMA</sub>              | 40  | _   |              | ns   | 1, 2, 3 |  |  |  |  |

| CE delay time                     | t <sub>DCE</sub>              | _   | _   | 300          | ns   | 1, 2, 3 |  |  |  |  |

| CE hold time                      | tHCE                          | 40  | _   | _            | ns   | 1, 2, 3 |  |  |  |  |

| OE delay time                     | t <sub>DOE</sub>              | _   | _   | 300          | ńs   | 1, 3    |  |  |  |  |

| OE hold time                      | tHOE                          | 40  |     | _            | ns   | 1, 3    |  |  |  |  |

| MD output delay time              | tomo                          | _   | _   | 150          | ns   | 1, 3    |  |  |  |  |

| MD output hold time               | thmow                         | 10  |     | _            | ns   | 1, 3    |  |  |  |  |

| WE delay time                     | towe                          | _   | _   | 150          | ns   | 1, 3    |  |  |  |  |

| WE clock pules width              | t <sub>WWE</sub>              | 150 | _   | _            | ns   | 1, 3    |  |  |  |  |

| MD output high impedance time (1) | tzmdf                         | 10  |     |              | ns   | 1, 3    |  |  |  |  |

| MD output high impedance time (2) | t <sub>ZMDR</sub>             | 50  | _   | _            | ns   | 1, 3    |  |  |  |  |

| RD data set-up time               | t <sub>SRD</sub>              | 50  | _   | _            | ns   | 2       |  |  |  |  |

| RD data hold time                 | t <sub>HRO</sub>              | 40  | _   | <del>-</del> | ns   | 2       |  |  |  |  |

| MD data set-up time               | t <sub>SMD</sub>              | 50  | _   | _            | ns   | 2       |  |  |  |  |

MD data hold time

40

$t_{\text{HMD}}$

- T1: Memory data refresh timing for upper screen

- T2: Memory data refresh timing for lower screen

- T3: Memory read/write timing

Notes: 2. ROM/RAM read timing

- \*1 This figure shows the timing for Hp = 8.

For Hp = 7, time shown by "b" becomes zero. For Hp = 6, time shown by "a" and "b" become zero.

Therefore, the number of clock pulses during T1 become 4, 3, or 2 in the case of Hp = 8, Hp = 7, or Hp = 6 respectively.

- \*2 The waveform for instructions with memory read is shown with a dash line. In other cases, the waveform shown with a solid line is generated.

- \*3 When an instruction with RAM read/write is excuted, the value of cursor address is output. In other cases, invalid data is output.

- \*4 When an instruction with RAM read is excuted, HD61830B latches the data at this timing. In other cases, this data is invalid.

### 3. Test load circuit

452

$R_L = 2.4 \,k\Omega$  $R = 11 \,k\Omega$

C = 50 pF (C includes jig capacitance) Diodes  $D_1$  to  $D_4$ : 1S2074 $\bigcirc$

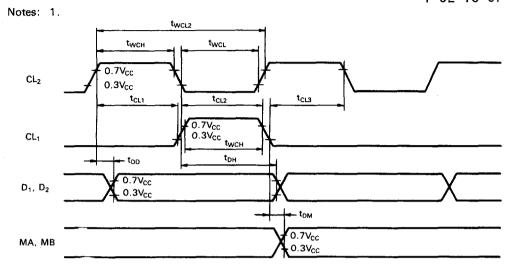

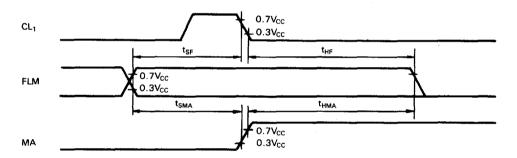

| LCD Driver Interface              |                  |      |     |     | T-52- | 13-07 |

|-----------------------------------|------------------|------|-----|-----|-------|-------|

| Item                              | Symbol           | Min  | Тур | Max | Unit  | Note  |

| Clock cycle time                  | twc12            | 416  |     |     | ns    | 1, 3  |

| Clock pulse width<br>(High level) | twcн             | 150  | -   | _   | ns    | 1, 3  |

| Clock pulse width<br>(Low level)  | twcL             | 150  |     | _   | ns    | 1, 3  |

| Data delay time                   | too              | _    | _   | 50  | กร    | 1, 3  |

| Data hold time                    | t <sub>DH</sub>  | 100  |     | _   | ns    | 1, 3  |

| Clock phase difference (1)        | t <sub>CL1</sub> | 100  | _   | _   | ns    | 1, 3  |

| Clock phase difference (2)        | t <sub>CL2</sub> | 100  | _   | _   | ns    | 1, 3  |

| Clock phase difference (3)        | t <sub>CL3</sub> | 100  |     | _   | ns    | 1, 3  |

| MA, MB delay time                 | t <sub>DM</sub>  | -200 | _   | 200 | ns    | 1, 3  |

| FLM set-up time                   | t <sub>SF</sub>  | 400  | _   | _   | ns    | 2, 3  |

| FLM hold time                     | tHF              | 1000 | _   |     | ns    | 2, 3  |

| MA set-up time                    | t <sub>SMA</sub> | 400  | _   | _   | ns    | 2, 3  |

| MA hold time                      | t <sub>HMA</sub> | 1000 | -   | _   | ns    | 2, 3  |

T-52-13-07

2.

### 3. Test load circuit

454

### **Display Control Instructions**

Display is controlled by writing data into the instruction register and 13 data registers. The RS signal distinguishes the instruction register from the data registers. 8-bit data is written into the instruction register with RS = 1, and the data register code is specified. After that, the 8-bit data is written in the data register and the specified instruction is executed with RS = 0.

During the execution of the instruction, no new instruction can be accepted. Since the busy flag is set during this, read the busy flag and make sure it is 0 before writing the next instruction.

### 1. Mode control

Code \$"00" (hexadecimal) written into the instruction register specifies the mode control register.

| Register          | R/W | RS | DB7 | DB6 | DB5       | DB4 | DB3 | DB2 | DB1 | DBO |

|-------------------|-----|----|-----|-----|-----------|-----|-----|-----|-----|-----|

| Instruction reg.  | 0   | 1  | 0   | 0   | 0         | 0   | 0   | 0   | 0   | 0   |

| Mode control reg. | 0   | 0  | 0   | 0   | Mode data |     |     |     |     |     |

| DB5            | DB4          | DB3   | DB2    | DB1                       | DB0         | Cursor/blink                | CG          | Graphic/character display             |

|----------------|--------------|-------|--------|---------------------------|-------------|-----------------------------|-------------|---------------------------------------|

| 1/0            | 1/0          | 0     | 0      | 0                         | 0           | Cursor off                  |             | Character display<br>(Character mode) |

|                |              | 0     | 1      |                           |             | Cursor on                   | 50 Je       | (Character mode)                      |

|                |              | 1     | 0      |                           |             | Cursor off, Character blink | Internal CG | }                                     |

|                |              | 1     | 1      |                           |             | Cursor blink                | =           |                                       |

|                |              | 0     | 0      |                           | 1           | Cursor off                  | <b>(</b> D  |                                       |

|                |              | 0     | 1      |                           |             | Cursor on                   | a CC        |                                       |

|                |              | 1     | 0      |                           |             | Cursor off, character blink | External CG |                                       |

|                |              | 1     | 1      |                           |             | Cursor blink                |             |                                       |

|                |              | 0     | 0      | 1                         | 0           |                             |             | Graphic mode                          |

| Display ON/OFF | Master/slave | Blink | Cursor | Graphic/character<br>mode | Ext./Int.CG |                             |             |                                       |

1: Master mode

0: Slave mode

1: Display ON

0: Display OFF

T-52-13-07

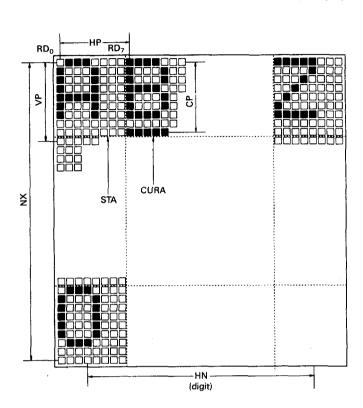

### 2. Set character pitch

Vp indicates the number of vertical dots per character. The spece between the verticallydisplayed characters is considered for determination. This value is meaningful only during character display (in the character mode) and becomes invalid in the graphic mode.

Hp indicates the number of horizontal dots per character in display, including the space between horizontally-displayed characters. In the graphic mode, the Hp indicates the number of bits of 1-byte display data to be displayed.

There are three Hp values (Table 1).

| Register             | R/W | RS | DB7                                                | DB6 | DB5 | DB4 | DB3     | DB2  | DB1 | DBO |

|----------------------|-----|----|----------------------------------------------------|-----|-----|-----|---------|------|-----|-----|

| Instruction reg.     | 0   | 1  | 0                                                  | 0   | 0   | 0   | 0       | 0    | 0   | 1   |

| Character pitch reg. | 0   | 0  | (V <sub>p</sub> - 1) binary 0 (H <sub>p</sub> - 1) |     |     |     | - 1) bi | nary |     |     |

### 3. Set number of characters

$H_{N}$  indicates the number of horizontal characters in the character mode or the number of horizontal bytes in the graphic mode. If the total sum of horizontal dots on the screen is taken as n,

$$n = Hp \times H_N$$

H<sub>N</sub> can be set to an even number from 2 to 128 (decimal).

| Register                  | R/W | RS | DB7 | DB6                        | DB5 | DB4 | DB3 | DB2 | DB1 | DBO |

|---------------------------|-----|----|-----|----------------------------|-----|-----|-----|-----|-----|-----|

| Instruction reg.          | 0   | 1  | 0   | 0                          | 0   | 0   | 0   | 0   | 1   | 0   |

| Number-of-characters reg. | 0   | 0  | 0   | (H <sub>N</sub> ~1) binary |     |     |     |     |     |     |

### Table 1 Hp Values

| Нр | DB2 | DB1 | DB0 | Horizontal character pitch |

|----|-----|-----|-----|----------------------------|

| 6  | 1   | 0 , | 1   | 6                          |

| 7  | 1   | 1   | 0   | 7                          |

| 8  | 1   | 1   | 1   | 8                          |

### 4. Set number of time divisions (inverse of display duty ratio)

Nx indicates the number of time divisions in multiplex display. 1/Nx is the display duty

ratio.

A value of 1 to 128 (decimal) can be set to Nx.

| Register                   | R/W | RS | DB7 | DB6 | DB5 | DB4             | DB3     | DB2  | DB1 | DB0 |

|----------------------------|-----|----|-----|-----|-----|-----------------|---------|------|-----|-----|

| Instruction reg.           | 0   | 1  | 0   | 0   | 0   | 0               | 0       | 0    | 1   | 1   |

| Number-of-time shares reg. | 0   | 0  | 0   |     |     | (N <sub>X</sub> | - 1) bi | nary |     |     |

### 5. Set cursor position

Cp indicates the position in a character where the cursor is displayed in the character mode. For example, in  $5 \times 7$  dot font, the cursor is displayed under a character by specifying Cp = 8 (decimal). The cursor horizontal length is equal to the horizontal character pitch Hp. A value of 1 to 16 (decimal) can be set to Cp. If a smaller value than the vertical character pitch Vp is set (Cp ≤ Vp), and a character overlaps with the cursor, the cursor has higher priority of display (at cursor display on). If Cp is greater than Vp, no cursor is displayed. The cursor horizontal length is equal to Hp.

| Register             | R/W | RS | DB7 | DB6 | DB5 | DB4 | DB3                         | DB2 | DB1 | DB0 |

|----------------------|-----|----|-----|-----|-----|-----|-----------------------------|-----|-----|-----|

| Instruction reg.     | 0   | 1  | 0   | 0   | 0   | 0   | 0                           | 1   | 0   | 0   |

| Cursor position reg. | 0   | 0  | 0   | 0   | 0   | 0   | (C <sub>p</sub> - 1) binary |     |     |     |

# 6. Set display start low order addres

Cause display start addresses to be written in the display start address registers. The display start address indicates a RAM address at which the data displayed at the top left end on the screen is stored. In the graphic mode, the start address is composed of high/low order 16 bits. In the character display, it is composed of the lower 4 bits of high order address (DB<sub>3</sub>-DB<sub>0</sub>) and 8 bits of low order address. The upper 4 bits of high order address are ignored.

| Register                                    | R/W | RS | DB7 | DB6 | DB5       | DB4      | DB3     | DB2      | DB1 | DBO |

|---------------------------------------------|-----|----|-----|-----|-----------|----------|---------|----------|-----|-----|

| Instruction reg.                            | 0.  | 1  | 0   | 0   | 0         | 0        | 1       | 0        | 0   | 0   |

| Display start address reg. (low order byte) | 0   | 0  |     |     | (Start Id | ow order | address | ) binary |     |     |

### Set display start high order address

| Register                                     | R/W | RS | DB7 | DB6 | DB5       | DB4      | DB3      | DB2       | DB1 | DBO |

|----------------------------------------------|-----|----|-----|-----|-----------|----------|----------|-----------|-----|-----|

| Instruction reg.                             | 0   | 1  | 0   | 0   | 0         | 0        | 1        | 0         | 0   | 1   |

| Display start address reg. (high order byte) | 0   | 0  |     |     | (Start hi | igh orde | r addres | s) binary | ,   |     |

# 7. Set cursor address (low order) (RAM write low order address)

Cause cursor addresses to be written in the cursor address counters. The cursor address indicates an address for sending or receiving display data and character codes to or from the RAM.

That is, data at the address specified by the cursor address are read/written. In the character mode, the cursor is displayed at the character specified by the cursor address.

A cursor address consists of the low-order

address (8 bits) and the high-order address (8 bits). Satisfy the following requirements when setting the cursor address (Table 2).

The cursor address counter is a 16-bit upcounter with set and reset functions. When bit N changes from 1 to 0, bit N + 1 is incremented by 1. When setting the low order address, the LSB (bit 1) of the high order address is added by 1 if the MSB (bit 8) of the low order address changes from 1 to 0. Therefore, set both the low order address and the high order address as shown in table 2.

| Register                                | R/W | RS | DB7                               | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|-----------------------------------------|-----|----|-----------------------------------|-----|-----|-----|-----|-----|-----|-----|

| Instruction reg.                        | 0   | 1  | .0                                | 0   | 0   | 0   | 1   | 0   | 1   | 0   |

| Cursor address counter (low order byte) | 0   | 0  | (Cursor low order address) binary |     |     |     |     |     |     |     |

### Set cursor address (high order) (RAM write high order address)

| Register                                 | R/W | RS | DB7 | DB6 | DB5      | DB4       | DB3       | DB2       | DB1 | DBO |

|------------------------------------------|-----|----|-----|-----|----------|-----------|-----------|-----------|-----|-----|

| Instruction reg.                         | 0   | 1  | 0   | 0   | 0        | 0         | 1         | 0 .       | 1   | 1   |

| Cursor address counter (high order byte) | 0   | 0  |     | (   | Cursor t | nigh orde | er addres | ss) binar | У   |     |

### Table 2 Cursor Address Setting

| Condition                                                                             | Requirement                                                                         |

|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| When you want to rewrite (set) both the low order address and the high order address. | Set the low order address and then set the high order address.                      |

| When you want to rewrite only the low order address.                                  | Don't fail to set the high order address again after setting the low order address. |

| When you want to rewrite only the high order address.                                 | Set the high order address. You don't have to set the low order address again.      |

8. Write display data

After the code \$"0C" is written into the instruction register with RS = 1, 8 bit data with RS = 0 should be written into the data register. This data is transferred to the RAM specified by the cursor address as display data or character code. The cursor address is increased by 1 after this operation.

| Register         | R/W | RS | DB7                                    | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DBO |

|------------------|-----|----|----------------------------------------|-----|-----|-----|-----|-----|-----|-----|

| Instruction reg. | 0   | 1  | 0                                      | 0   | 0   | 0   | 1   | 1   | 0   | 0   |

| RAM              | 0   | 0  | MSB (pattern data, character code) LSB |     |     |     |     |     |     |     |

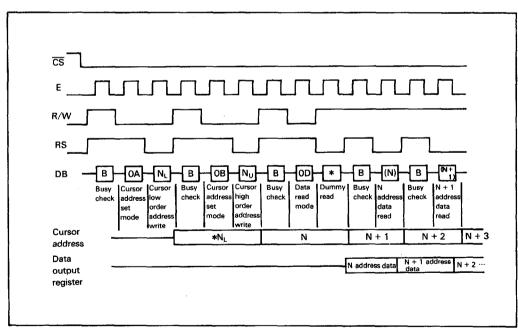

# 9. Read display data

Data can be read from the RAM with RS = 0

after writing code \$"0C" into the instruction register. Figure 1 shows the read procedure.

| Register         | R/W | RS | DB7                                    | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DBO |

|------------------|-----|----|----------------------------------------|-----|-----|-----|-----|-----|-----|-----|

| Instruction reg. | 0   | 1  | 0                                      | 0   | 0   | 0   | 1   | 1   | 0   | 1   |

| RAM              | 1   | 0  | MBS (pattern data, character code) LSB |     |     |     |     |     |     |     |

This instruction outputs the contents of data output register on the data bus (DB0 to DB7) and then transfers RAM data specified by the cursor address to the data output register, also increasing the cursor address by 1. After

setting the cursor address, correct data is not output at the first read but at the second one. Thus, make one dummy read when reading data after setting the cursor address.

Figure 1 Read Procedure

### HITACHI

Hitachi America, Ltd. • Hitachi Plaza • 2000 Sierra Point Pkwy. • Brisbane, CA 94005-1819 • (415) 589-8300

T-52-13-07

#### 10. Clear bit

The clear/set bit instruction sets 1 bit in a byte of display data RAM to 0 or 1, respectively. The position of the bit in a byte is specified by  $N_B$  and RAM address is specified

by cursor address. After the execution of the instruction, the cursor address is automatically increased by 1.  $N_B$  is a value from 1 to 8.  $N_B\,=\,1$  and  $N_B\,=\,8$  indicates LSB and MSB, respectively.

| Register         | R/W | RS | DB7 | DB6 | DB5 | DB4 | DB3 | DB2                         | DB1 | DBO |

|------------------|-----|----|-----|-----|-----|-----|-----|-----------------------------|-----|-----|

| Instruction reg. | 0   | 1  | 0   | 0   | 0   | 0   | 1   | 1                           | 1   | 0   |

| Bit clear reg.   | 0   | 0  | 0   | 0   | 0   | 0   | 0   | (N <sub>B</sub> - 1) binary |     |     |

### Set bit

| Register         | R/W | RS | DB7 | DB6 | DB5 | DB4 | DB3 | DB2                         | DB1 | DBO |

|------------------|-----|----|-----|-----|-----|-----|-----|-----------------------------|-----|-----|

| Instruction reg. | 0   | 1  | 0   | 0   | 0   | 0   | 1   | 1                           | 1   | 1   |

| Bit set reg.     | 0   | 0  | 0   | 0   | 0   | 0   | 0   | (N <sub>B</sub> - 1) binary |     |     |

### 11. Read busy flag

When the read mode is set with RS = 1, the busy flag is output to DB7. The busy flag is set to 1 during the execution of any of the other instructions. After the execution, it is set to 0. The next instruction can be accepted. No instruction can be accepted when busy flag = 1. Before executing an instruction or writing data, perform a busy flag check to make

sure the busy flag is 0. When data is written in the register (RS = 1), busy flag doesn't change. Thus, no busy flag check is required just after the write operation into the instruction register with RS = 1.

The busy flag can be read without specifying any instruction register.

| Register  | R/W | RS | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DBO |

|-----------|-----|----|-----|-----|-----|-----|-----|-----|-----|-----|

| Busy flag | 1   | 1  | 1/0 |     |     |     | *   |     |     |     |

| Name                            | Meaning                                                                                                                           | Value                                                                                                                                                                                                                                                                                            |  |  |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Horizontal character fitch      | Horizontal character pitch                                                                                                        | 6 to 8 dots                                                                                                                                                                                                                                                                                      |  |  |

| Number of horizontal characters | Number of horizontal characters per line (number of digits) in the character mode or number of bytes per line in the graphic mode | 2 to 128 digits<br>(an even num-<br>ber)                                                                                                                                                                                                                                                         |  |  |

| Vertical character pitch        | Vertical character pitch                                                                                                          | 1 to 16 dots                                                                                                                                                                                                                                                                                     |  |  |

| Cursor position                 | Line number on which the cursor can be displayed                                                                                  | 1 to 16 lines                                                                                                                                                                                                                                                                                    |  |  |

| Number of time divisions        | Inverse of dispgay duty ratio                                                                                                     | 1 to 128 lines                                                                                                                                                                                                                                                                                   |  |  |

|                                 | Number of horizontal characters  Vertical character pitch  Cursor position                                                        | Horizontal character fitch  Number of horizontal character pitch  Number of horizontal characters per line (number of digits) in the character mode or number of bytes per line in the graphic mode  Vertical character pitch  Cursor position  Line number on which the cursor can be displayed |  |  |

Note: if the number of vertical dots on the screen is m, and the number of horizontal dots is n,

$$1/m=1/N_X=$$

display duty ratio  $\pi=H_p\times H_N,\ m/V_p=Number$  of display lines  $C_p\le V_p$

Figure 2 Display Variables

462

# **Internal Character Generator Patterns and Character Codes**

T-52-13-07

| Higher                 | T          |            |             |      |              |          |             |          | Γ        |                 |           |                                                              |

|------------------------|------------|------------|-------------|------|--------------|----------|-------------|----------|----------|-----------------|-----------|--------------------------------------------------------------|

| Lower 4 bits<br>4 bits | 0010       | 0011       | 0100        | 0101 | 0110         | 0111     | 1010        | 1011     | 1100     | 1101            | 1110      | 1111                                                         |

| ××××0000               |            |            |             | ļ:   | ••           | :        |             | *****    |          |                 |           |                                                              |

| ××××0001               |            | ***        |             |      |              | -:::     | II          |          |          | ·               | -:::      |                                                              |

| ××××0010               |            | ****       |             |      |              | ļ.".     |             |          | ij       | <u>;</u> ∷'     | <b></b> : |                                                              |

| ××××0011               |            |            | 141         | :;   | : <u>"</u> . | •        |             | ŗŢ       |          |                 | ::        | :::                                                          |

| ××××0100               |            |            |             | 1    |              | <b>.</b> | ••          | *****    |          | #:              | 1         |                                                              |

| ××××0101               |            | ;          | 1111        |      | ;i           | i!       | #           |          | <b>;</b> | ***             | :::       | 1.4                                                          |

| ××××0110               |            | <u>:</u>   |             | Ļ    |              | i.,:     | ****        | <u> </u> |          |                 |           |                                                              |

| ××××0111               | ::         | .,         |             | ļį   |              | Ų        | ***         |          |          |                 |           | :::                                                          |

| ××××1000               | i.         | ; <u>;</u> |             | ×    | ļ <u>,</u>   | ::       | .:          |          |          | Ļ               | .i"       | *****                                                        |

| ××××1001               | <u>;</u> ; |            |             | ij   |              |          | ::::        | •        | .!       | 11.             | -:        |                                                              |

| ××××1010               | <b>:</b>   | #          |             |      |              |          |             |          | 1 1      | į·              |           |                                                              |

| ××××1011               |            | #<br>;;    | <b>!</b> :. |      |              | :        |             | ***      |          |                 | ×         | :::                                                          |

| ××××1100               | :          |            |             |      |              |          | <b>;</b> ;; | :: ,!    | ;i       | <b>!</b>        | #.        | ::::                                                         |

| ××××1101               |            | *****      |             |      | l'i          | }        | ***         |          | •••      | <sub>.</sub> .: |           |                                                              |

| ××××1110               | ::         |            |             | .**. | ř"į          |          | :::         | •        |          | •••             | :":       |                                                              |

| ××××1111               | .••        | •          |             |      | [            | •••••    | :::         | ·        |          | <b>!!!</b>      |           | 1004<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000<br>0000 |

5

T-52-13-07

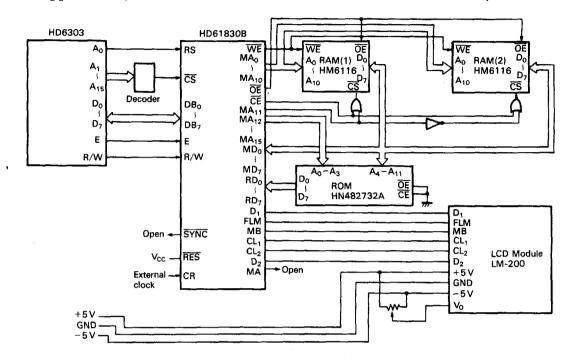

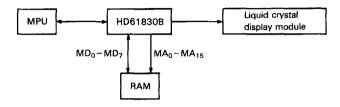

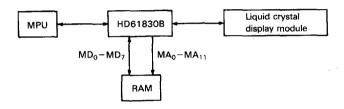

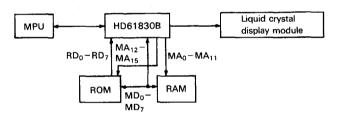

# Application (Character Mode, External CG, Character Font 8 × 8)

### Application (Graphic Mode)

### **Graphic Mode**

### Character Mode (1) (Internal Character Generator)

# Character Mode (2) (External Character Generator)

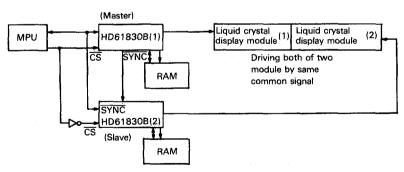

### **Parallel Operation**