# FMS6406 Precision S-Video Filter with Summed Composite Output, Sound Trap, and Group Delay Compensation

#### Features

- 7.6MHz 5th-order Y,C filters with composite summer

- 14dB notch at 4.425MHz to 4.6MHz for sound trap capable of handling stereo

- 50dB stopband attenuation at 27MHz on Y, C, and CV outputs

- Better than 0.5dB flatness to 4.2MHz on Y, C, and CV outputs

- Equalizer and notch filter for driving RF modulator with group delay of -180ns

- No external frequency selection components or clocks

- < 5ns group delay on Y, C, and CV outputs</p>

- AC coupled inputs

- AC or DC coupled outputs

- Capable of PAL frequency for Y, C, CV

- Continuous Time Low Pass Filters

- <1.4% differential gain with 0.7° differential phase on Y, C, and CV channels

- Integrated DC restore circuitry with low tilt

#### Applications

- Cable set-top boxes

- Satellite set-top boxes

- DVD players

## Description

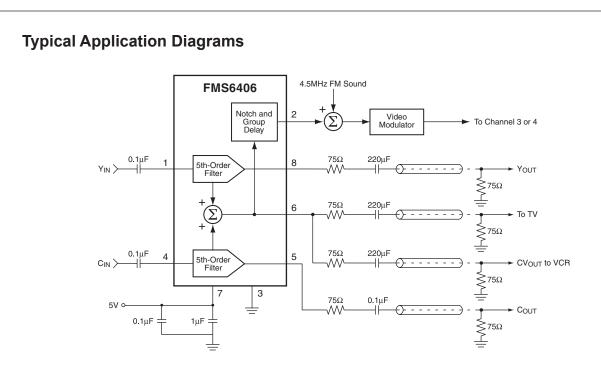

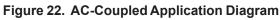

The FMS6406 is a dual Y/C 5th-order Butterworth lowpass video filter optimized for minimum overshoot and flat group delay. The device also contains a summing circuit to generate filtered composite video, an audio trap and group delay compensation circuit. The audio trap removes video information in the spectral location of the subsequent RF audio carrier. The group delay circuit predistorts the signal to compensate for the inherent receiver IF filter's group delay distortion.

In a typical application, the Y and C input signals from DACs are AC-coupled into the filters. Both channels have DC-restore circuitry to clamp the DC-input levels during video sync. The Y and C channels use separate feedback clamps. The clamp pulse is derived from the Y channel.

All outputs are capable of driving  $2V_{pp}$ , AC or DC-coupled, into either a single or dual video load. A single video load consists of a series  $75\Omega$  impedance matching resistor connected to a terminated  $75\Omega$  line, this presents a total of  $150\Omega$  of loading to the part. A dual load would be two of these in parallel which would present a total of  $75\Omega$  to the part. The gain of the Y, C and CV signals is 6dB with  $1V_{pp}$  input levels. All video channels are clamped during sync to establish the appropriate output voltage reference levels.

### **Block Diagram**

### **Ordering Information**

| Part Number | Package | Pb-Free | Operating Temp<br>Range | Packaging<br>Method |

|-------------|---------|---------|-------------------------|---------------------|

| FMS6406CS   | SOIC-8  | Yes     | 0°C to +70°C            | Tube                |

| FMS6406CSX  | SOIC-8  | Yes     | 0°C to +70°C            | Tape and Reel       |

August 2006

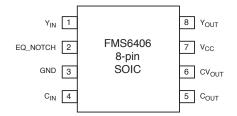

## **Pin Assignments**

| Pin# | Pin               | Туре   | Description                                                                                                                                            |

|------|-------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Y <sub>IN</sub>   | Input  | Luminance (Luma) Input: In a typical<br>system, this pin is connected to the<br>Luma or composite video output pin<br>from the external video encoder. |

| 2    | EQ_NOTCH          | Output | Composite video output to RF modulator/driver.                                                                                                         |

| 3    | GND               | Input  | Ground                                                                                                                                                 |

| 4    | C <sub>IN</sub>   | Input  | Chrominance (Chroma) Input: In a typical system, this pin is connected to the Chroma output pin from the external video encoder.                       |

| 5    | C <sub>OUT</sub>  | Output | Filtered Chrominance Video Output from the C <sub>IN</sub> channel.                                                                                    |

| 6    | CV <sub>OUT</sub> | Output | Composite Video Output: This pin is the sum of $\rm Y_{OUT}$ and $\rm C_{OUT}.$                                                                        |

| 7    | V <sub>CC</sub>   | Input  | +5V supply.                                                                                                                                            |

| 8    | Y <sub>OUT</sub>  | Output | Filtered Luminance Video Output from the Y <sub>IN</sub> channel.                                                                                      |

## **Absolute Maximum Ratings**

The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum ratings. The "Recommended Operating Conditions" table defines the conditions for actual device operation.

| Parameter                                        | Min. | Max.                  | Unit |

|--------------------------------------------------|------|-----------------------|------|

| V <sub>CC</sub>                                  | -0.3 | 6                     | V    |

| Analog and Digital I/O                           | -0.3 | V <sub>CC</sub> + 0.3 | V    |

| Output Channel - Any One Channel (Do Not Exceed) |      | 100                   | mA   |

Notes:

Functional operation under any of these conditions is NOT implied. Performance and reliability are guaranteed only if operating conditions are not exceeded.

## **Reliability Information**

| Parameter                                                                               | Min. | Тур. | Max. | Unit |

|-----------------------------------------------------------------------------------------|------|------|------|------|

| Junction Temperature                                                                    |      |      | 150  | °C   |

| Storage Temperature Range                                                               | -65  |      | +150 | °C   |

| Lead Temperature (Soldering, 10s)                                                       |      |      | 300  | °C   |

| Thermal Resistance ( $\theta_{JA}$ ), JEDEC Standard Multi-layer Test Boards, Still Air |      | 115  |      | °C/W |

## **Recommended Operating Conditions**

| Parameter                   | Min   | Тур  | Мах   | Unit |

|-----------------------------|-------|------|-------|------|

| Operating Temperature Range | 0     |      | 70    | °C   |

| V <sub>CC</sub> Range       | +4.75 | +5.0 | +5.25 | V    |

| GND                         |       | 0    |       | V    |

## **Electrical Characteristics**

$T_c = 25^{\circ}C$ ,  $V_i = 1V_{pp}$ ,  $V_{CC} = 5V$ , all inputs AC-coupled with 0.1µF, all outputs are AC-coupled with 220µF into 150 $\Omega$ , referenced to 400kHz; unless otherwise noted.

| Symbol             | Parameter                                                                                          | Conditions                                       | Min  | Тур  | Max  | Units           |

|--------------------|----------------------------------------------------------------------------------------------------|--------------------------------------------------|------|------|------|-----------------|

| I <sub>cc</sub>    | Supply Current <sup>1</sup>                                                                        | V <sub>cc</sub> no load                          | 50   | 80   | 110  | mA              |

| AV                 | Low Frequency Gain (Y <sub>OUT</sub> , C <sub>OUT</sub> , CV <sub>OUT</sub> ) <sup>1</sup>         | at 400kHz                                        | 5.8  | 6.0  | 6.2  | dB              |

| AV <sub>EQ</sub>   | Low Frequency Gain (EQ_NOTCH) <sup>1</sup>                                                         | at 400kHz                                        | 5.7  | 6.0  | 6.4  | dB              |

| C <sub>sync</sub>  | C <sub>OUT</sub> Output Level (during Sync) <sup>1</sup>                                           | Sync present on Y <sub>IN</sub> (after 6dB gain) | 1.0  | 1.1  | 1.3  | V               |

| Y <sub>sync</sub>  | Y <sub>OUT</sub> Output Level (during Sync) <sup>1</sup>                                           | Sync present on Y <sub>IN</sub> (after 6dB gain) |      | 0.35 | 0.5  | V               |

| CV <sub>sync</sub> | CV <sub>OUT</sub> Output Level (during Sync) <sup>1</sup>                                          | Sync present on Y <sub>IN</sub> (after 6dB gain) |      | 0.35 | 0.5  | V               |

| EQ <sub>sync</sub> | EQ_NOTCH Output Level (during Sync) <sup>1</sup>                                                   | Sync present on Y <sub>IN</sub> (after 6dB gain) |      | 0.35 | 0.5  | V               |

| T <sub>CLAMP</sub> | Clamp Response Time (Y Channel)                                                                    | Settled to within 10mV                           |      | 5    |      | ms              |

| f <sub>FLAT</sub>  | Gain Flatness to 4.2MHz <sup>2</sup><br>(Y <sub>out</sub> , C <sub>out</sub> , CV <sub>out</sub> ) |                                                  | -0.5 | 0    | 0.5  | dB              |

| f <sub>c</sub>     | -3dB Bandwidth <sup>1</sup>                                                                        | Y, C, CV Channels                                | 6.7  | 7.6  |      | MHz             |

| f <sub>sb</sub>    | Stopband Attenuation <sup>1</sup><br>(Y <sub>out</sub> , C <sub>out</sub> , CV <sub>out</sub> )    | at 27MHz                                         | 40   | 50   |      | dB              |

| V <sub>i</sub>     | Input Signal Dynamic Range                                                                         | All Channels/AC coupled                          |      | 1.4  |      | V <sub>pp</sub> |

| I <sub>sc</sub>    | Output Short Circuit Current <sup>4</sup><br>(Any One Channel)                                     | Y, C, CV, EQ_NOTCH to GND                        |      | 85   |      | mA              |

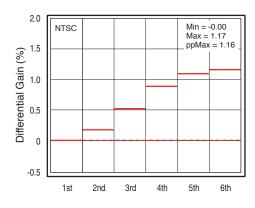

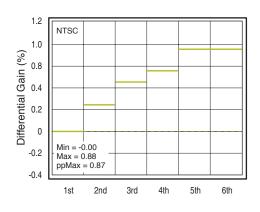

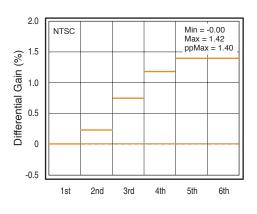

| dG                 | Differential Gain <sup>2</sup>                                                                     | Y, C, CV                                         |      | 1.4  | 3    | %               |

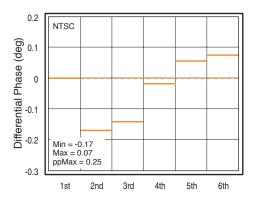

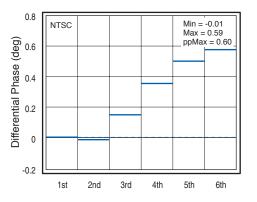

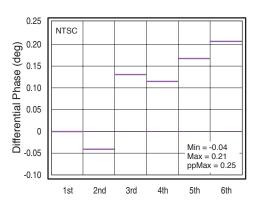

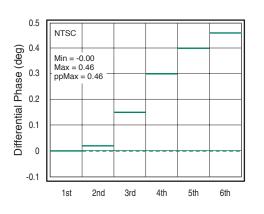

| dθ                 | Differential Phase <sup>2</sup>                                                                    | Y, C, CV                                         |      | 0.7  | 1.5  | 0               |

| THD                | Output Distortion (All Channels)                                                                   | $V_{OUT} = 1.8V_{pp}$ at 3.58MHz                 |      | 0.3  |      | %               |

| X <sub>TALK</sub>  | Crosstalk (Channel-to-Channel)                                                                     | at 3.58MHz                                       |      | -50  |      | dB              |

| PSRR               | PSRR (All Channels)                                                                                | DC                                               |      | 50   |      | dB              |

| SNR                | SNR Y, C Channel <sup>2</sup>                                                                      | NTC-7 weighting 4.2MHz lowpass                   | 70   | 75   |      | dB              |

|                    | SNR CV Channel <sup>2</sup>                                                                        | NTC-7 weighting 4.2MHz lowpass                   | 70   | 75   |      | dB              |

|                    | SNR EQ_NOTCH Channel <sup>2</sup>                                                                  | NTC-7 weighting 4.2MHz lowpass                   | 65   | 70   |      | dB              |

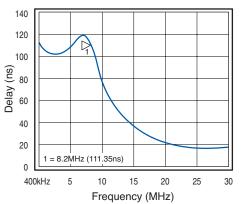

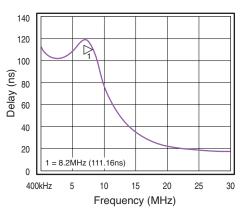

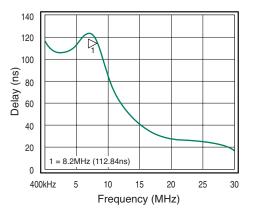

| t <sub>pd</sub>    | Propagation Delay (Y, C, CV)                                                                       | at 400kHz                                        |      | 112  |      | ns              |

| GD                 | Group Delay (Y, C, CV) <sup>2</sup>                                                                | at 3.58MHz (NTSC)                                | -5   | 0    | 5    | ns              |

| t <sub>skew</sub>  | Skew Between Y <sub>OUT</sub> and C <sub>OUT</sub> <sup>2</sup>                                    | at 1MHz                                          | -2   | 0    | 2    | ns              |

| t <sub>clgcv</sub> | Chroma-Luma Gain CV <sub>out</sub> 1                                                               | $f = 3.58MHz$ (ref to $Y_{IN}$ at 400kHz)        | 98   | 100  | 102  | %               |

| t <sub>CLDCV</sub> | Chroma-Luma Delay CV <sub>OUT</sub> <sup>1</sup>                                                   | $f = 3.58MHz$ (ref to $Y_{IN}$ at 400kHz)        | -10  | 0    | 10   | ns              |

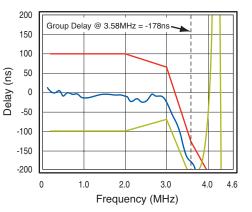

| GD <sub>EQ</sub>   | Group Delay EQ_NOTCH <sup>1</sup>                                                                  | $f = 3.58MHz$ (ref to $Y_{IN}$ at 400kHz)        | -195 | -180 | -165 | ns              |

| t <sub>clgeq</sub> | Chroma-Luma Gain EQ_NOTCH <sup>1</sup>                                                             | $f = 3.58MHz$ (ref to $Y_{IN}$ at 400kHz)        | 95   | 100  | 105  | %               |

| t <sub>CLDEQ</sub> | Chroma-Luma Delay EQ_NOTCH <sup>1</sup>                                                            | $f = 3.58MHz$ (ref to $Y_{IN}$ at 400kHz)        | -195 | -180 | -165 | ns              |

| dG <sub>EQ</sub>   | Differential Gain <sup>2</sup>                                                                     | EQ_NOTCH Channel                                 |      | 0.3  | 1    | %               |

| $d\theta_{EQ}$     | Differential Phase <sup>2</sup>                                                                    | EQ_NOTCH Channel                                 |      | 0.3  | 0.75 | %               |

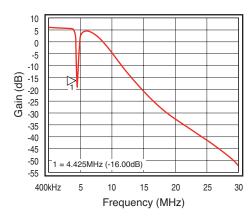

| MCF                | Modulator Channel Flatness <sup>1,3</sup>                                                          | EQ_NOTCH from 400kHz to 3.75MHz                  | -0.5 | 0    | 0.5  | dB              |

| AV <sub>PK</sub>   | Gain Peaking <sup>1</sup>                                                                          | EQ_NOTCH from >3.75MHz to 4.2MHz                 | -0.5 | 0    | 0.5  | dB              |

| Atten1             | Notch Attenuation 1 <sup>1</sup>                                                                   | EQ_NOTCH at 4.425MHz                             | 14   |      |      | dB              |

| Atten2             | Notch Attenuation 2 <sup>1</sup>                                                                   | EQ_NOTCH at 4.5MHz                               | 20   |      |      | dB              |

| Atten3             | Notch Attenuation 3 <sup>1</sup>                                                                   | EQ_NOTCH at 4.6MHz                               | 14   |      |      | dB              |

| t <sub>PASS</sub>  | Passband Group Delay, EQ_NOTCH <sup>1</sup>                                                        | f = 400kHz to f = 3MHz                           | -35  |      | 35   | ns              |

#### Notes:

1. 100% tested at 25°C.

2. Guaranteed by characterization.

3. Tested down to 400kHz, but guaranteed by design to 200kHz.

4. Sustained short circuit protection limited to 10 seconds.

$T_c = 25^{\circ}$ C,  $V_i = 1V_{pp}$ ,  $V_{CC} = 5$ V, all inputs AC-coupled with 0.1µF, all outputs are AC-coupled with 220µF into 150 $\Omega$ , referenced to 400kHz; unless otherwise noted.

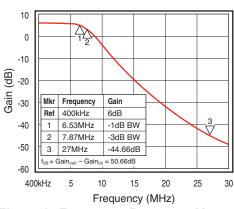

Figure 1. Frequency Response YOUT

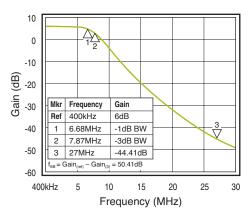

Figure 3. Frequency Response COUT

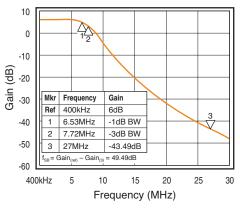

Figure 5. Frequency Response CV<sub>OUT</sub>

Figure 2. Group Delay vs. Frequency YOUT

Figure 4. Group Delay vs. Frequency COUT

Figure 6. Group Delay vs. Frequency CVOUT

$T_c = 25^{\circ}C$ ,  $V_i = 1V_{pp}$ ,  $V_{CC} = 5V$ , HD/N\_SD = 0,  $R_{SOURCE} = 37.5\Omega$ , all inputs AC-coupled with  $0.1\mu$ F, all outputs are AC-coupled with  $220\mu$ F into  $150\Omega$ , referenced to 400kHz; unless otherwise noted.

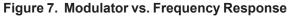

Figure 9. Differential Gain, MODOUT

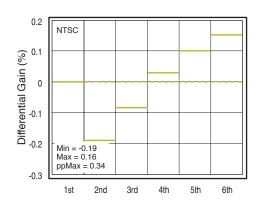

Figure 11. Noise vs. Freq. Modulator Channel

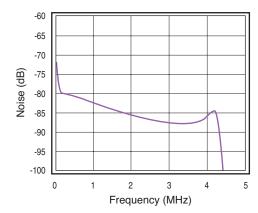

Figure 8. Delay Modulator Output

Figure 10. Differential Phase, MODOUT

Figure 12. Group Delay vs. Frequency

$T_c = 25^{\circ}C$ ,  $V_i = 1V_{pp}$ ,  $V_{CC} = 5V$ , HD/N\_SD = 0,  $R_{SOURCE} = 37.5\Omega$ , all inputs AC-coupled with  $0.1\mu$ F, all outputs are AC-coupled with  $220\mu$ F into  $150\Omega$ , referenced to 400kHz; unless otherwise noted.

Figure 13. Differential Gain, VOUT

Figure 15. Differential Gain, COUT

Figure 17. Differential Gain, CV<sub>OUT</sub>

Figure 14. Differential Phase, VOUT

Figure 16. Differential Phase, COUT

Figure 18. Differential Phase, CVOUT

$T_c = 25^{\circ}C$ ,  $V_i = 1V_{pp}$ ,  $V_{CC} = 5V$ , HD/N\_SD = 0,  $R_{SOURCE} = 37.5\Omega$ , all inputs AC-coupled with  $0.1\mu$ F, all outputs are AC-coupled with  $220\mu$ F into  $150\Omega$ , referenced to 400kHz; unless otherwise noted.

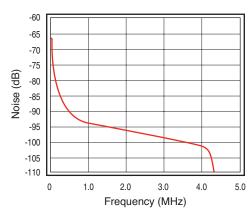

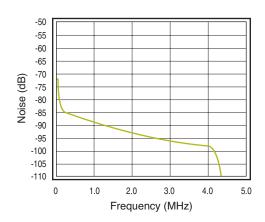

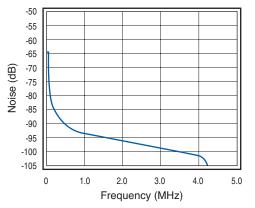

Figure 19. Noise vs. Frequency YOUT

Figure 21. Noise vs. Frequency CV<sub>OUT</sub>

Figure 20. Noise vs. Frequency COUT

## **Functional Description**

#### Introduction

This product is a two channel monolithic continuous time video filter designed for reconstructing the luminance and chrominance signals from an S-Video D/A source. Composite video output is generated by summing the Y and C outputs. The chip is designed to have AC coupled inputs and will work equally well with either AC or DC coupled outputs.

The reconstruction filters provide a 5th-order Butterworth response with group delay equalization. This provides a maximally flat response in terms of delay and amplitude. Each of the four outputs is capable of driving  $2V_{pp}$  into a 75 $\Omega$  load.

All channels are clamped during the sync interval to set the appropriate minimum output DC level. With this operation the effective input time constant is greatly reduced, which allows for the use of small low cost coupling capacitors. The net effect is that the input will settle to 10mV in 5ms for any DC shifts present in the input video signal.

In most applications the input coupling capacitors are  $0.1\mu$ F. The Y and C inputs typically sink  $1\mu$ A of current during active video, which normally tilts a horizontal line by 2mV at the Y output. During sync, the clamp restores this leakage current by sourcing an average of  $20\mu$ A over the clamp interval. Any change in the coupling capacitor values will affect the amount of tilt per line. Any reduction in tilt will come with an increase in settling time.

#### Luminance (Y) I/O

The typical luma input is driven by either a low impedance source of  $1V_{pp}$  or the output of a 75 $\Omega$  terminated line driven by the output of a current DAC. In either case, the input must be capacitively coupled to allow the sync-detect and DC restore circuitry to operate properly.

All outputs are capable of driving  $2V_{pp}$ , AC or DC-coupled, into either a single or dual video load. A single video load consists of a series  $75\Omega$  impedance matching resistor connected to a terminated  $75\Omega$  line, this presents a total of  $150\Omega$  of loading to the part. A dual load would be two of these in parallel which would present a total of  $75\Omega$  to the part. The gain of the Y, C and CV signals is 6dB with  $1V_{pp}$  input levels. Even when two loads are present the driver will produce a full  $2V_{pp}$  signal at its output pin.

#### Chrominance (C) I/O

The chrominance input can be driven in the same manner as the luminance input but is typically only a  $0.7V_{pp}$  signal.

Since the chrominance signal doesn't contain any DC content, the output signal can be AC coupled using as small as a  $0.1\mu$ F capacitor if DC-coupling is not desired.

#### Composite Video (CV) Output

The composite video output driver is same as the other outputs. When driving a dual load either output will still function if the other output connection is inadvertently shorted providing these loads are AC-coupled.

#### Equalizer/Notch (EQ\_NOTCH) Output

This output is designed to drive a  $600\Omega$  load to  $2V_{pp},$  which will meet its primary intention of driving a modulator load.

### Layout Considerations

General layout and supply bypassing play major roles in high-frequency performance and thermal characteristics. The FMS6406DEMO is a 4-layer board with a full power and ground plane. Following this layout configuration will provide the optimum performance and thermal characteristics. For optimum results, follow the steps below as a basis for high frequency layout:

- Include 1µF and 0.1µF ceramic bypass capacitors

- Place the 1µF capacitor within 0.75 inches of the power pin

- Place the 0.1µF capacitor within 0.1 inches of the power pin

- For multi-layer boards, use a large ground plane to help dissipate heat

- For 2-layer boards, use a ground plane that extends beyond the device by at least 0.5"

- Minimize all trace lengths to reduce series inductances

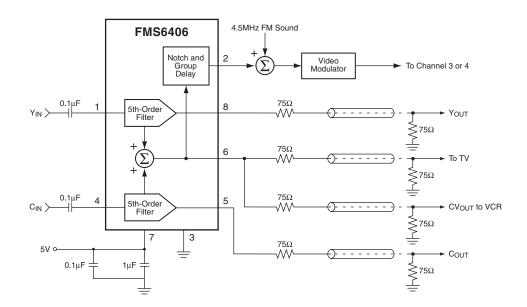

# **Mechanical Dimensions**

### 8-Lead Outline Package (SOIC)

FMS6406 Precision S-Video Filter with Summed Composite Output, Sound Trap, and Group Delay Compensation

#### TRADEMARKS

The following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is not intended to be an exhaustive list of all such trademarks.

FAST® ACEx™ ActiveArray™ FASTr™ FPS™ Bottomless™ Build it Now™ FRFET™ **CoolFET™** GlobalOptoisolator™ GTO™ **CROSSVOLT™** DOME™ HiSeC™ EcoSPARK™ I<sup>2</sup>C™ i-Lo™ E<sup>2</sup>CMOS™ EnSigna™ ImpliedDisconnect<sup>™</sup> FACT™ IntelliMAX™ FACT Quiet Series™ Across the board. Around the world.™ The Power Franchise<sup>®</sup> Programmable Active Droop™

ademarks. ISOPLANAR™ LittleFET™ MICROCOUPLER™ MicroFET™ MicroPak™ MICROWIRE™ MSX™ MSXPro™ OCX™ OCX™ OCXPro™ OPTOLOGIC® OPTOPLANAR™ PACMAN™ POP™ Power247™

PowerEdge™ PowerSaver™ PowerTrench<sup>®</sup> QFET<sup>®</sup> QS™ QT Optoelectronics™ RapidConfigure™ RapidConnect™ µSerDes™ ScalarPump™ SILENT SWITCHER<sup>®</sup> SMART START™ SPM™ Stealth™ SuperFET<sup>™</sup> SuperSOT<sup>™</sup>-3 SuperSOT<sup>™</sup>-6 SuperSOT<sup>™</sup>-8 SyncFET<sup>™</sup> TCM<sup>™</sup> TinyLogic<sup>®</sup> TINYOPTO<sup>™</sup> TruTranslation<sup>™</sup> UHC<sup>™</sup> UniFET<sup>™</sup> UltraFET<sup>®</sup> VCX<sup>™</sup> Wire<sup>™</sup>

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

#### As used herein:

1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

**PRODUCT STATUS DEFINITIONS**

2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

| Datasheet Identification | Product Status            | Definition                                                                                                                                                                                                                        |

|--------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance Information      | Formative or In<br>Design | This datasheet contains the design specifications for<br>product development. Specifications may change in<br>any manner without notice.                                                                                          |

| Preliminary              | First Production          | This datasheet contains preliminary data, and<br>supplementary data will be published at a later date.<br>Fairchild Semiconductor reserves the right to make<br>changes at any time without notice in order to improve<br>design. |

| No Identification Needed | Full Production           | This datasheet contains final specifications. Fairchild<br>Semiconductor reserves the right to make changes at<br>any time without notice in order to improve design.                                                             |

| Obsolete                 | Not In Production         | This datasheet contains specifications on a product<br>that has been discontinued by Fairchild semiconductor.<br>The datasheet is printed for reference information only.                                                         |