February 2007

# FAN7383 Half-Bridge Gate-Drive IC

### **Features**

- Floating Channel Designed for Bootstrap Operation to +600V.

- Typically 350mA/650mA Sourcing/Sinking Current Driving Capability for Both Channels

- Extended Allowable Negative V<sub>S</sub> Swing to -9.8V for Signal Propagation at V<sub>DD</sub>=V<sub>BS</sub>=15V

- High-Side Output in Phase of IN Signal

- Built-in UVLO Functions for Both Channels

- Built-in Common-Mode dv/dt Noise Canceling Circuit

- Typically Internal 330ns Minimum Dead-Time

- Programmable Turn-On Delay Time Control (Dead-Time)

### **Applications**

- SMPS

- Motor Drive Inverter

- Fluorescent Lamp Ballast

- HID Ballast

### **Description**

The FAN7383 is a half-bridge gate-drive IC with shutdown and programmable dead-time control functions for driving MOSFETs and IGBTs that operate up to +600V.

Fairchild's high voltage process and common-mode noise canceling technique give stable operation of high-side drivers under high-dv/dt noise circumstances.

An advanced level-shift circuit allows high-side gate driver operation up to  $V_S$ = -9.8V (typical) for  $V_{BS}$ =15V.

The UVLO circuits for both channels prevent malfunction when  $V_{DD}$  and  $V_{BS}$  are lower than the specified threshold voltage.

Output drivers typically source/sink 350mA/650mA, respectively, which is suitable for all kinds of half and full bridge inverter.

14-SOP

## **Ordering Information**

| Part Number              | Package | Pb-Free | Operating Temperature Range | Packing Method |

|--------------------------|---------|---------|-----------------------------|----------------|

| FAN7383M <sup>(1)</sup>  | 14-SOP  | Yes     | -40°C ~ 125°C               | Tube           |

| FAN7383MX <sup>(1)</sup> | 14-301  |         |                             | Tape & Reel    |

#### Note:

1. These devices passed wave soldering test by JESD22A-111.

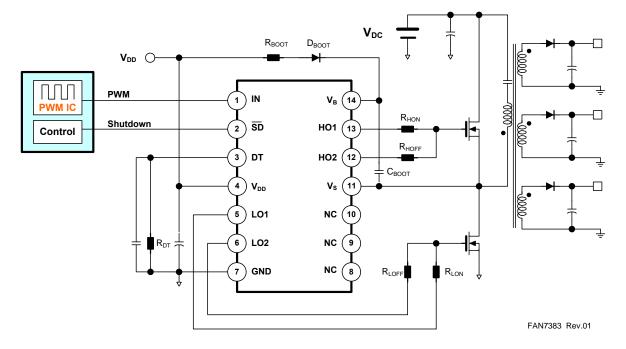

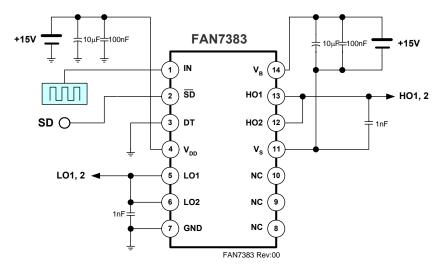

# **Typical Application Circuit**

Figure 1. Application Circuit for Half-Bridge Switching Power Supply

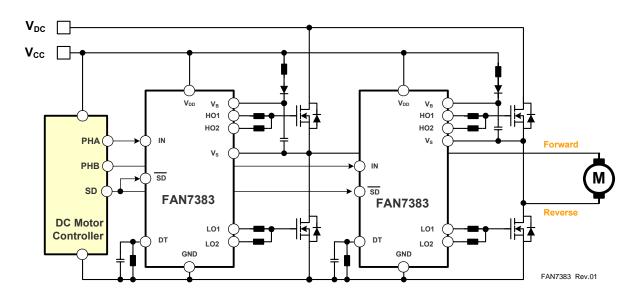

Figure 2. Application Circuit for Full-Bridge DC Motor Driver

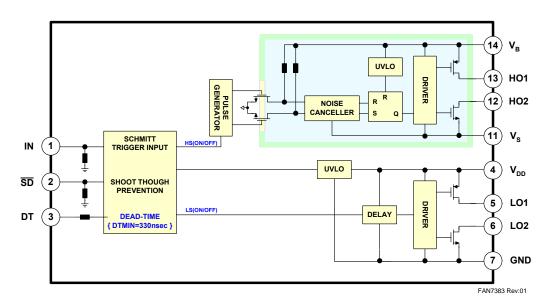

# **Internal Block Diagram**

Figure 3. Functional Block Diagram of FAN7383

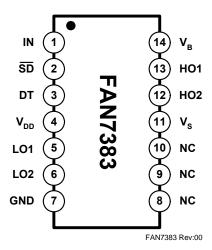

# **Pin Configuration**

Figure 4. Pin Configuration (Top View)

## **Pin Definitions**

| Pin# | Name            | Description                                           |  |

|------|-----------------|-------------------------------------------------------|--|

| 1    | IN              | Logic Input for Gate Driver                           |  |

| 2    | SD              | Logic Input for Shutdown (Active Low)                 |  |

| 3    | DT              | Programmable Dead-Time Control with External Resistor |  |

| 4    | V <sub>DD</sub> | Low-Side Supply Voltage                               |  |

| 5    | LO1             | Low-Side Driver Source Output                         |  |

| 6    | LO2             | Low-Side Driver Sink Output                           |  |

| 7    | GND             | Ground                                                |  |

| 8    | N.C.            | Not connected                                         |  |

| 9    | N.C.            | Not connected                                         |  |

| 10   | N.C.            | Not connected                                         |  |

| 11   | V <sub>S</sub>  | High-Side Floating Supply Return                      |  |

| 12   | HO2             | High-Side Driver Sink Output                          |  |

| 13   | HO1             | High-Side Driver Source Output                        |  |

| 14   | V <sub>B</sub>  | High-Side Floating Supply                             |  |

### **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.  $T_A = 25^{\circ}C$  unless otherwise specified.

| Symbol                              | Parameter                                  | Min.                | Max.                 | Unit |

|-------------------------------------|--------------------------------------------|---------------------|----------------------|------|

| V <sub>S</sub>                      | High-side offset voltage                   | V <sub>B</sub> -25  | V <sub>B</sub> +0.3  | V    |

| V <sub>B</sub>                      | High-side floating supply voltage          | -0.3                | 625                  | V    |

| V <sub>HO</sub>                     | High-side floating output voltage HO1, HO2 | V <sub>S</sub> -0.3 | V <sub>B</sub> +0.3  | V    |

| $V_{DD}$                            | Low-side and logic fixed supply voltage    | -0.3                | 25                   | V    |

| V <sub>LO</sub>                     | Low-side output voltage LO1, LO2           | -0.3                | V <sub>DD</sub> +0.3 | V    |

| V <sub>IN</sub>                     | Logic input voltage (IN)                   | -0.3                | V <sub>DD</sub> +0.3 | V    |

| V <sub>SD</sub>                     | Shutdown logic input voltage               | -0.3                | V <sub>DD</sub> +0.3 | V    |

| V <sub>DT</sub>                     | Dead-time control voltage                  | -0.3                | 5.0                  | V    |

| GND                                 | Logic ground                               | V <sub>DD</sub> -25 | V <sub>DD</sub> +0.3 | V    |

| dV <sub>S</sub> /dt                 | Allowable offset voltage slew rate         |                     | 50                   | V/ns |

| P <sub>D</sub> <sup>(2)(3)(4)</sup> | Power dissipation                          |                     | 1.0                  | W    |

| $\theta_{JA}$                       | Thermal resistance, junction-to-ambient    |                     | 110                  | °C/W |

| TJ                                  | Junction temperature                       |                     | 150                  | °C   |

| T <sub>STG</sub>                    | Storage temperature                        |                     | 150                  | °C   |

#### Notes:

- 2. When mounted on 76.2 x 114.3 x 1.6mm PCB. (FR-4 glass epoxy material).

- 3. Please refer to:

- JESD51-2: Integral circuits thermal test method environmental conditions Natural convection JESD51-3: Low effective thermal conductivity test board for leaded surface mount packages

- 4. Do not exceed P<sub>D</sub> under any circumstances.

### **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol          | Parameter                                | Condition | Min.               | Max.               | Unit |

|-----------------|------------------------------------------|-----------|--------------------|--------------------|------|

| V <sub>B</sub>  | High-side floating supply voltage        |           | V <sub>S</sub> +15 | V <sub>S</sub> +20 | V    |

| V <sub>S</sub>  | High-side floating supply offset voltage |           | 6-V <sub>DD</sub>  | 600                | V    |

| $V_{DD}$        | Low-side supply voltage                  |           | 15                 | 20                 | V    |

| V <sub>HO</sub> | High-side (HO) output voltage            |           | Vs                 | $V_{B}$            | V    |

| $V_{LO}$        | Low-side (LO) output voltage             |           | GND                | $V_{DD}$           | V    |

| V <sub>IN</sub> | Logic input voltage (IN)                 |           | GND                | $V_{DD}$           | V    |

| T <sub>A</sub>  | Ambient temperature                      |           | -40                | 125                | °C   |

### **Electrical Characteristics**

$V_{BIAS}$  ( $V_{DD}$ ,  $V_{BS}$ ) = 15.0V,  $R_{DT}$  = GND,  $T_A$  = 25°C, unless otherwise specified. The  $V_{IN}$  and  $I_{IN}$  parameters are referenced to GND. The  $V_O$  and  $I_O$  parameters are referenced to  $V_S$  and GND and are applicable to the respective outputs HO and LO.

| Symbol                                   | Parameter                                                                         | Condition                                             | Min. | Тур. | Max. | Unit |  |

|------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------|------|------|------|------|--|

| SUPPLY CURRENT SECTION                   |                                                                                   |                                                       |      |      |      |      |  |

| I <sub>QBS</sub>                         | Quiescent V <sub>BS</sub> supply current                                          | V <sub>IN</sub> =0V or 5V                             |      | 35   | 90   |      |  |

| I <sub>QDD</sub>                         | Quiescent V <sub>DD</sub> supply current                                          | $V_{IN}$ =0V or 5V, $R_{DT}$ =0 $\Omega$              |      | 650  | 900  |      |  |

| I <sub>SD</sub> <sup>(5)</sup>           | V <sub>DD</sub> supply current at shutdown mode                                   | SD=GND                                                |      | 650  | 900  |      |  |

| I <sub>PBS</sub>                         | Operating V <sub>BS</sub> supply current                                          | f <sub>IN</sub> =20kHz,rms value                      |      | 400  | 700  | μΑ   |  |

| I <sub>PDD</sub>                         | Operating V <sub>DD</sub> supply current                                          | $f_{IN}$ =20kHz,rms value, $R_{DT}$ =0 $\Omega$       |      | 950  | 1200 |      |  |

| I <sub>LK</sub>                          | Offset supply leakage current                                                     | V <sub>B</sub> =V <sub>S</sub> =600V                  |      |      | 10   |      |  |

| POWER S                                  | SUPPLY SECTION                                                                    |                                                       | •    | •    |      | •    |  |

| V <sub>DDUV+</sub><br>V <sub>BSUV+</sub> | V <sub>DD</sub> and V <sub>BS</sub> supply under-voltage positive going threshold |                                                       | 10.7 | 11.6 | 12.5 |      |  |

| V <sub>DDUV-</sub><br>V <sub>BSUV-</sub> | V <sub>DD</sub> and V <sub>BS</sub> supply under-voltage negative going threshold |                                                       | 10.0 | 10.8 | 11.6 | V    |  |

| V <sub>DDUVH</sub><br>V <sub>BSUVH</sub> | V <sub>DD</sub> and V <sub>BS</sub> supply under-voltage lockout hysteresis       |                                                       |      | 0.8  |      |      |  |

| GATE DR                                  | IVER OUTPUT SECTION                                                               |                                                       | •    | ,    |      |      |  |

| V <sub>OH</sub>                          | High-level output voltage, V <sub>BIAS</sub> -V <sub>O</sub>                      | I <sub>O</sub> =20mA                                  |      |      | 1.0  | V    |  |

| V <sub>OL</sub>                          | Low-level output voltage, V <sub>O</sub>                                          |                                                       |      |      | 0.6  | V    |  |

| I <sub>O+</sub>                          | Output high short-circuit pulse current                                           | V <sub>O</sub> =0V, V <sub>IN</sub> =5V with PW<10μs  | 250  | 350  |      | mA   |  |

| I <sub>O-</sub>                          | Output low short-circuit pulsed current                                           | V <sub>O</sub> =15V, V <sub>IN</sub> =0V with PW<10μs | 500  | 650  |      | mA   |  |

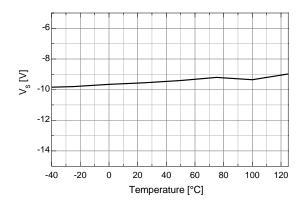

| Vs                                       | Allowable negative V <sub>S</sub> pin voltage for IN signal propagation to HO     |                                                       |      | -9.8 | -7.0 | V    |  |

| LOGIC IN                                 | LOGIC INPUT SECTION (INPUT AND SHUTDOWN)                                          |                                                       |      |      |      |      |  |

| V <sub>IH</sub>                          | Logic "1" input voltage                                                           |                                                       | 2.9  |      |      | V    |  |

| V <sub>IL</sub>                          | Logic "0" input voltage                                                           |                                                       |      |      | 1.2  | V    |  |

| I <sub>IN+</sub>                         | Logic "1" input bias current                                                      | V <sub>IN</sub> =5V                                   |      | 50   | 100  | μΑ   |  |

| I <sub>IN-</sub>                         | Logic "0" input bias current                                                      | V <sub>IN</sub> =0V                                   |      |      | 2.0  | μΑ   |  |

| SD+                                      | Shutdown "1" input voltage                                                        |                                                       |      |      | 1.2  | V    |  |

| SD-                                      | Shutdown "0" input voltage                                                        |                                                       | 2.9  |      |      | V    |  |

| R <sub>PD</sub>                          | Input pull-down resistance                                                        |                                                       |      | 100  |      | ΚΩ   |  |

### Note:

5. This parameter guaranteed by design.

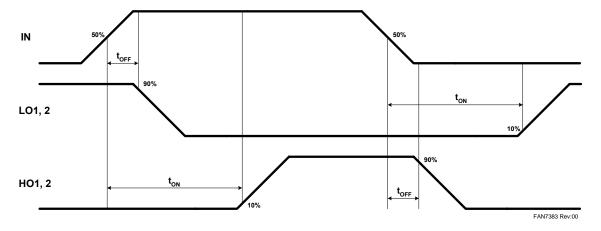

# **Dynamic Electrical Characteristics**

$V_{BIAS}\left(V_{DD},\,V_{BS}\right)=15.0V,\,V_{S}=GND,\,C_{L}=1000pF,\,R_{DT}=GND,\,and\,T_{A}=25^{\circ}C,\,unless\,otherwise\,specified.$

| Symbol                         | Parameter                        | Conditions                                | Min. | Тур. | Max. | Unit |

|--------------------------------|----------------------------------|-------------------------------------------|------|------|------|------|

| t <sub>ON</sub>                | Turn-on propagation delay        | V <sub>S</sub> =0V                        |      | 500  | 670  |      |

| t <sub>OFF</sub>               | Turn-off propagation delay       | V <sub>S</sub> =0V or 600V <sup>(5)</sup> |      | 170  | 250  |      |

| t <sub>R</sub>                 | Turn-on rise time                |                                           |      | 50   | 100  | ns   |

| t <sub>F</sub>                 | Turn-off fall time               |                                           |      | 30   | 80   |      |

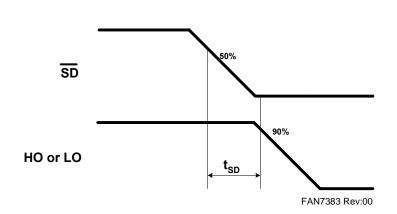

| t <sub>SD</sub> <sup>(5)</sup> | Shutdown propagation delay       |                                           |      | 100  | 180  |      |

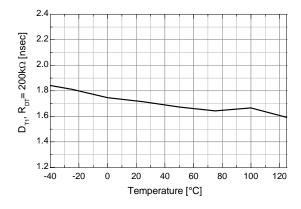

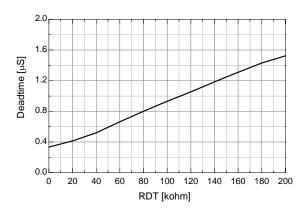

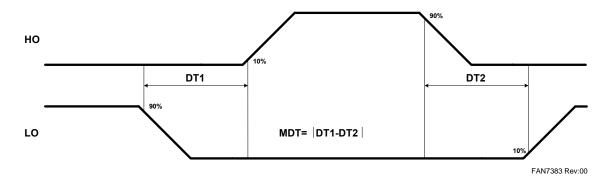

| DT1,                           | Dead-time LO OFF to HO ON and HO | $R_{DT}=0\Omega$                          | 250  | 330  | 420  | ns   |

| DT2                            | OFF to LO ON                     | R <sub>DT</sub> =200KΩ                    | 1.20 | 1.68 | 2.30 | μs   |

| DMT                            | Dead-time matching               | $R_{DT}=0\Omega$                          |      | 0    | 60   | ns   |

|                                |                                  | R <sub>DT</sub> =200KΩ                    |      | 0    | 150  | 115  |

### Note:

5. These parameters guaranteed by design.

## **Typical Characteristics**

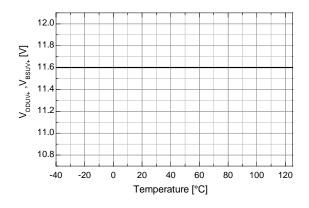

Figure 5.  $V_{DD}/V_{BS}$  UVLO (+) vs. Temperature

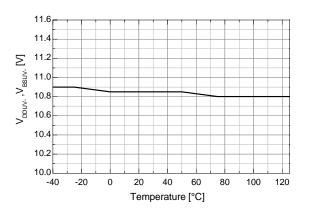

Figure 6. V<sub>DD</sub>/V<sub>BS</sub> UVLO (-) vs. Temperature

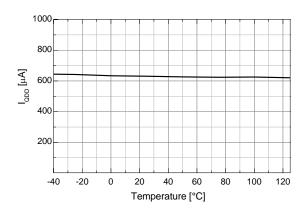

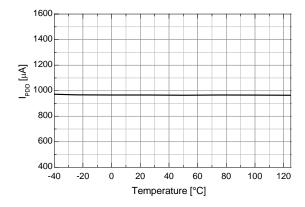

Figure 7.  $V_{DD}$  Quiescent Current vs. Temperature

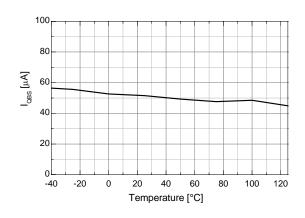

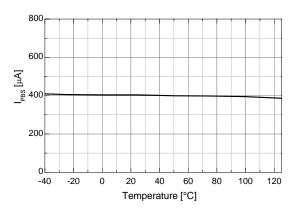

Figure 8. V<sub>BS</sub> Quiescent Current vs. Temperature

Figure 9.  $V_{\text{DD}}$  Operating Current vs. Temperature

Figure 10.  $V_{BS}$  Operating Current vs. Temperature

## **Typical Characteristics** (Continued)

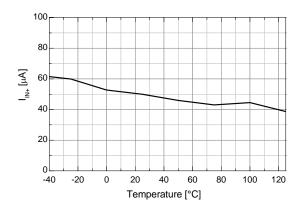

Figure 11. Logic Input Current vs. Temperature

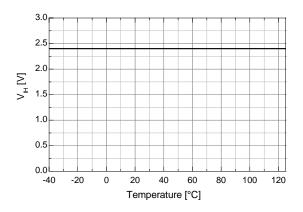

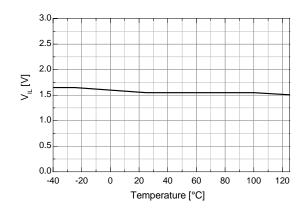

Figure 12. Logic Input High Voltage vs. Temperature

Figure 13. Logic Input Low Voltage vs. Temperature

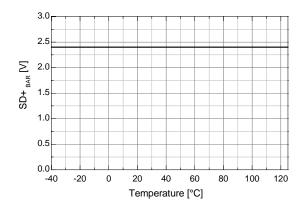

Figure 14.  $\overline{\text{SD}}$  Positive Threshold vs. Temperature

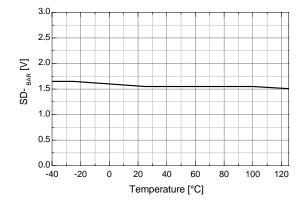

Figure 15. SD Negative Threshold vs. Temperature

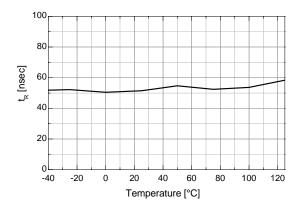

Figure 16. Rising Time vs. Temperature

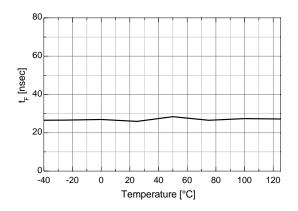

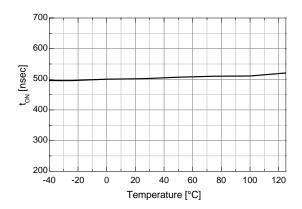

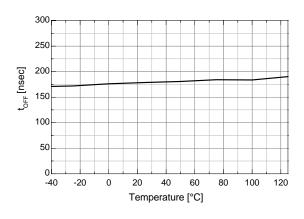

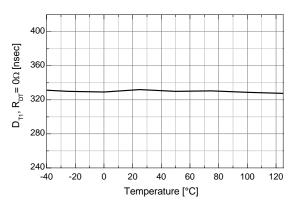

## Typical Characteristics (Continued)

Figure 17. Falling Time vs. Temperature

Figure 18. Turn-on Delay Time vs. Temperature

Figure 19. Turn-off Falling Time vs. Temperature

Figure 20. Dead-Time ( $R_{DT}$ =0k $\Omega$ ) vs. Temperature

Figure 21. Dead Time ( $R_{DT}$ =200 $k\Omega$ ) vs. Temperature

Figure 22. R<sub>DT</sub> vs. Dead Time

# **Typical Characteristics** (Continued)

Figure 23. Allowable Negative  $V_{\rm S}$  Voltage for Signal Propagation to High Side vs. Temperature

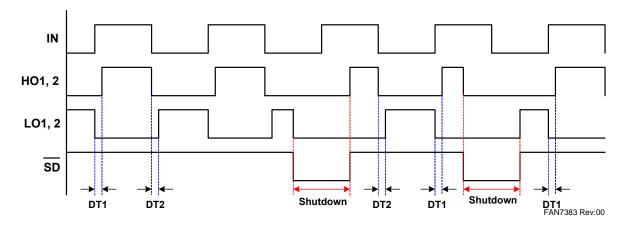

# **Switching Time Definitions**

Figure 24. Switching Time Test Circuit

Figure 25. Input / Output Waveforms

Figure 26. Switching Time Waveform Definitions

Figure 27. Shutdown Waveform Definition

Figure 28. Dead-Time Waveform Definition

### **Typical Application Information**

### 1. Normal Operating Consideration

The FAN7383 is a single PWM input half-bridge gatedrive IC with programmable dead-time and shutdown function.

The dead-time is set with a resistor (R<sub>DT</sub>) at the DT pin. The wide dead-time programming range provides the flexibility to optimize drive signal timing for a selection of switching devices (MOSFET or IGBT) and applications.

The turn-on time delay circuitry (Dead-Time) accommodates resistor values from  $0\Omega$  to  $200k\Omega$  with a dead-time proportional to the R<sub>DT</sub> resistance.

Grounding the DT pin programs the FAN7383 to drive both outputs with minimum dead time.

If the  $\overline{SD}$  pin voltage decrease below 1.2V in normal operation, the IC enters the shutdown mode.

### 2. Under-Voltage Lockout (UVLO)

The FAN7383 has an under-voltage lockout (UVLO) protection circuitry for high and low side channels to prevent malfunction when  $V_{DD}$  or  $V_{BS}$  is lower than the specified threshold voltage. The UVLO circuitry monitors the supply voltage ( $V_{DD}$ ) and bootstrap capacitor voltage ( $V_{BS}$ ) independently.

### 3. Layout Consideration

For optimum performance of high- and low-side gate drivers, cannot be achieved without taking due considerations must be taken during printed circuit board (PCB) layout.

#### 3.1 Supply Capacitors

If the output stages are able to quickly turn on the switching device with high value of current, the supply capacitors must be placed as close as possible to the device pins ( $V_{DD}$  and GND for the ground-tied supply,  $V_{B}$  and  $V_{S}$  for the floating supply) to minimize parasitic inductance and resistance.

### 3.2 Gate Drive Loop

Current loops behave like an antenna, able to receive and transmit noise. To reduce the noise coupling/emission and improve the power switch turn-on and off performances, gate drive loops must be reduced as much as possible.

#### 3.3 Ground Plane

Ground plane must not be placed under or nearby the high-voltage floating side to minimize noise coupling.

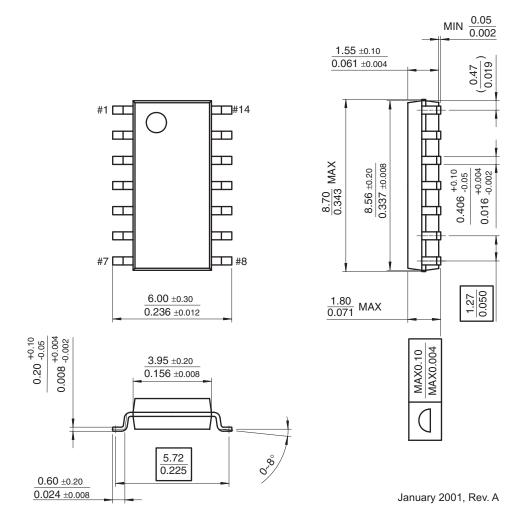

# **Package Dimensions**

### 14-SOP

Dimensions are in millimeters unless otherwise noted.

Figure 29. 14-Lead Small Outline Package (SOP)

#### **TRADEMARKS**

The following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is not intended to be an exhaustive list of all such trademarks.

$\mathsf{TinyLogic}^{\mathbb{8}}$ **ACEx**® HiSeC™ PowerTrench® TINYOPTO™ Across the board. Around the world.™ Programmable Active Droop™ i-Lo™ ActiveArrav™ **QFET** TinvPower™ ImpliedDisconnect™ QS™ Bottomless™ IntelliMAX™ TinyWire™ QT Optoelectronics™ TruTranslation™ Build it Now™ ISOPLANAR™ Quiet Series™ μSerDes™ CoolFET™ MICROCOUPLER™ RapidConfigure™  $CROSSVOLT^{\text{TM}}$ UHC® MicroPak™ CTL™ UniFET™ MICROWIRE™ RapidConnect™ Current Transfer Logic™ ScalarPump™ VCX™  $MSX^{TM}$ DOME™ SMART START™ Wire™  $MSXPro^{TM}$ E<sup>2</sup>CMOS™ SPM®  $OCX^{TM}$ EcoSPARK®

$OCXPro^{TM}$ EnSigna™ OPTOLOGIC® SuperSOT™-3 FACT Quiet Series™ **OPTOPLANAR®** SuperSOT™-6 **FACT**® SuperSOT™-8  $PACMAN^{\scriptscriptstyle{\mathsf{TM}}}$ FAST® РОР™ ТСМ™

$FASTr^{\scriptscriptstyle\mathsf{TM}}$ Power220<sup>®</sup> The Power Franchise® **FPS™**

Power247® FRFET® PowerEdge™ TinyBoost™ GlobalOptoisolator™ PowerSaver™ TinyBuck™

GTO™

#### **DISCLAIMER**

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN: NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

SuperFET™

### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

#### As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- 2. A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

### **PRODUCT STATUS DEFINITIONS**

#### **Definition of Terms**

| Datasheet Identification | Product Status         | Definition                                                                                                                                                                                               |

|--------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance Information      | Formative or In Design | This datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                       |

| Preliminary              | First Production       | This datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. |

| No Identification Needed | Full Production        | This datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design.                                                   |

| Obsolete                 | Not In Production      | This datasheet contains specifications on a product that has been discontinued by Fairchild Semiconductor. The datasheet is printed for reference information only.                                      |

Rev. 123