# FAN6206 Highly Integrated Dual-Channel Synchronous Rectification Controller for Dual-Forward Converter

### Features

SEMICONDUCTOR

- Highly Integrated Dual-Channel SR Controller

- Receives Synchronized Driving Signal from the Primary Side

- Internal Linear-Predict Timing Control for DCM Operation

- Ultra-Low V<sub>DD</sub> Operating Voltage for Different Output Voltage of PC Power

- V<sub>DD</sub> Over-Voltage Protection

- 14V Gate Driver Clamp

### **Applications**

- PC Power

- Server Power

- Open-Frame SMPS

### Description

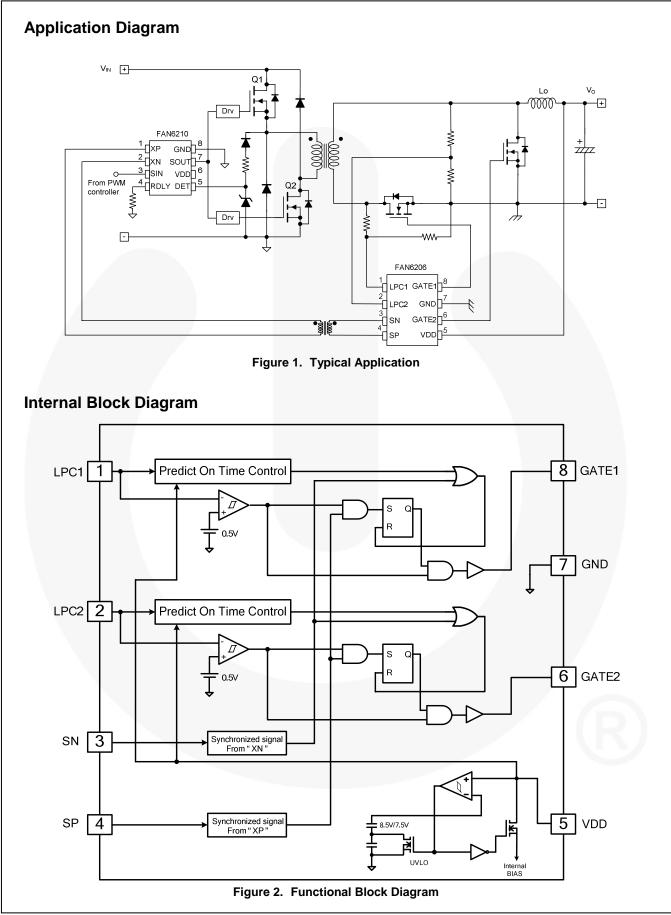

The highly integrated FAN6206 is a dual-channel synchronous rectification (SR) controller. FAN6206 allows design of a cost-effective power supply with fewer external components, especially suited for dual-forward topology used to obtain higher efficiency for ATX power supplies.

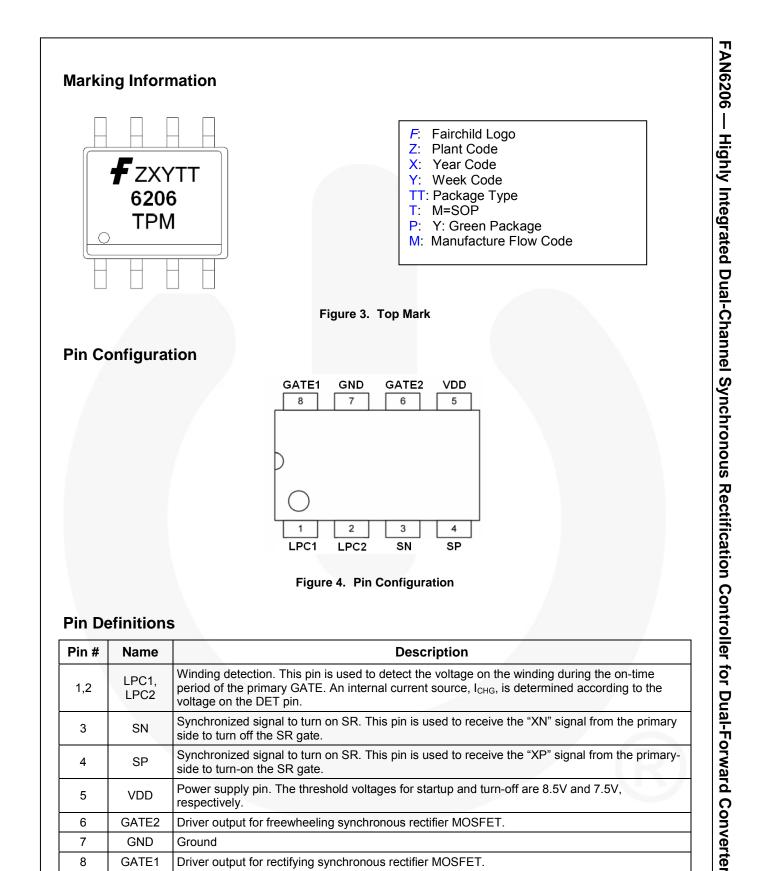

The primary-side control method provides synchronous rectification control for dual-forward converters that operate in continuous conduction mode (CCM). FAN6206 includes a proprietary linear-predict timing control mechanism for dual-forward converters that operate in discontinuous conduction mode (DCM) at fixed or variable frequency. PWM frequency tracking with secondary-side winding detection is provided by adding dividing resistors. The primary-side signals are generated from Fairchild's FAN6210 (Primary-Side Synchronous Rectifier Signal Trigger for Dual-Forward Converter). The primary-side signals are transferred through a pulse transformer to the secondary-side. The benefits of this technique include simple control method and improved power system reliability.

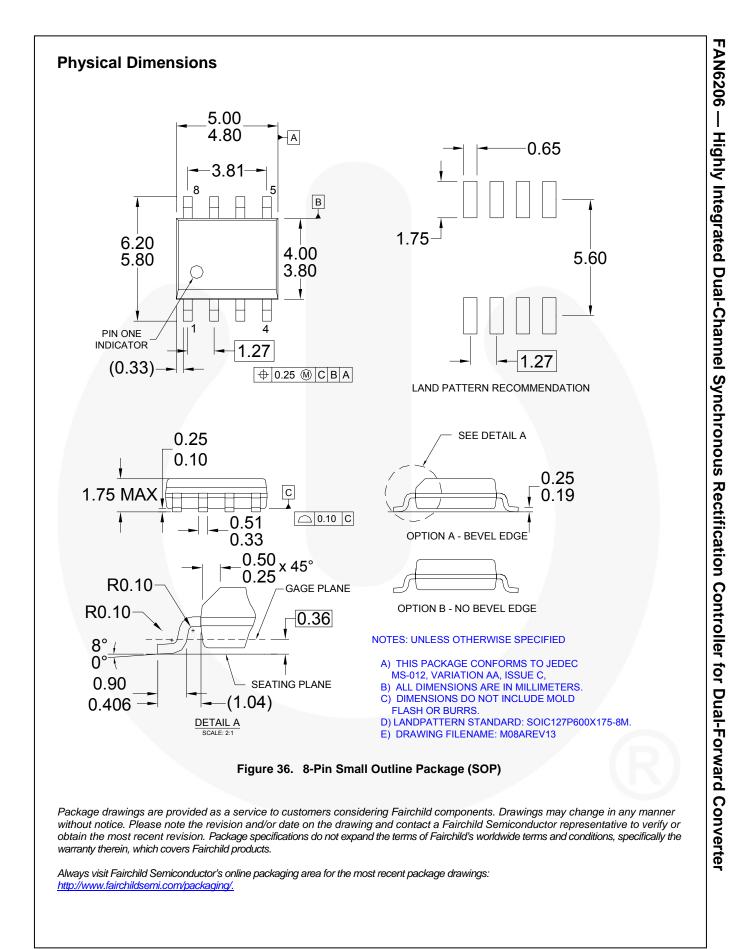

FAN6206 is available in 8-pin SOP package.

### **Ordering Information**

| Part Number | Operating<br>Temperature Range | Package                           | Packing<br>Method |

|-------------|--------------------------------|-----------------------------------|-------------------|

| FAN6206MY   | -40°C to +105°C                | 8-Pin Small Outline Package (SOP) | Tape & Reel       |

© 2010 Fairchild Semiconductor Corporation FAN6206 • Rev. 1.0.2

FAN6206 — Highly Integrated Dual-Channel Synchronous Rectification Controller for Dual-Forward Converter

respectively.

Ground

5

6

7

8

FAN6206 • Rev. 1.0.2

VDD

GATE2

GND

GATE1

Driver output for freewheeling synchronous rectifier MOSFET.

Driver output for rectifying synchronous rectifier MOSFET.

Power supply pin. The threshold voltages for startup and turn-off are 8.5V and 7.5V,

### **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol           | Parameter                                | Min. | Max. | Unit |

|------------------|------------------------------------------|------|------|------|

| V <sub>DD</sub>  | DC Supply Voltage                        |      | 30   | V    |

| V <sub>HV</sub>  | SP, SN                                   |      | 30   | V    |

| VL               | LPC                                      | -0.3 | 7.0  | V    |

| PD               | Power Dissipation at $T_A < 50^{\circ}C$ |      | 400  | mW   |

| Θ <sub>JA</sub>  | Junction to Ambient Thermal Resistance   |      | 130  | °C/W |

| $\Psi_{jt}$      | Junction to Top Thermal Characteristics  |      | 46   | °C/W |

| TJ               | Operating Junction Temperature           | -40  | +125 | °C   |

| T <sub>STG</sub> | Storage Temperature Range                | -55  | +150 | °C   |

| TL               | Lead Temperature, (Soldering 10 Seconds) |      | +260 | °C   |

| ESD              | Human Body Model, JESD22-A114            |      | 4.00 | kV   |

| ESD              | Charged Device Model, JESD22-C101        |      | 1.25 | κv   |

Notes:

1. Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device.

2. All voltage values, except differential voltages, are given with respect to GND pin.

### **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol         | Parameter                     | Min. | Max. | Unit |

|----------------|-------------------------------|------|------|------|

| T <sub>A</sub> | Operating Ambient Temperature | -40  | +105 | °C   |

## **Electrical Characteristics**

$V_{DD}$ =20V,  $T_A$ =25°C, unless otherwise specified.

| Symbol                   | Parameter Conditions                         |                                                         |     | Тур. | Max. | Units |

|--------------------------|----------------------------------------------|---------------------------------------------------------|-----|------|------|-------|

| V <sub>DD</sub> Section  |                                              |                                                         |     | 1    |      |       |

| V <sub>OP</sub>          | Continuously Operating Voltage               |                                                         |     |      | 25   | V     |

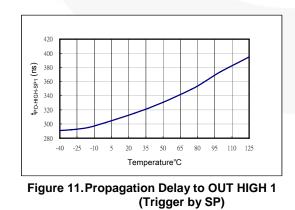

| V <sub>TH-ON1</sub>      | Turn-On Threshold Voltage                    | 8.0                                                     | 8.5 | 9.0  | V    |       |

| V <sub>TH-ON2</sub>      | Turn-On Threshold Voltage                    | 8.0                                                     | 8.5 | 9.0  | V    |       |

| $V_{\text{TH-OFF1}}$     | Turn-Off Threshold Voltage                   |                                                         | 7.0 | 7.5  | 8.0  | V     |

| $V_{\text{TH-OFF2}}$     | Turn-Off Threshold Voltage                   |                                                         | 7.0 | 7.5  | 8.0  | V     |

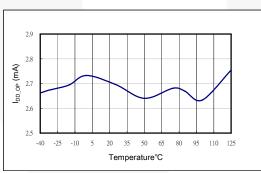

| I <sub>DD-OP</sub>       | Operating Current                            | V <sub>DD</sub> =15V, DET=50KHz                         |     | 3    | 5    | mA    |

| I <sub>DD-ST</sub>       | Startup Current                              | V <sub>DD</sub> = 7.5V                                  |     | 340  | 500  | μA    |

| $V_{\text{DD-OVP1}}$     | V <sub>DD</sub> Over-Voltage Protection 1    |                                                         | 20  | 21   | 22   | V     |

| V <sub>DD-OVP2</sub>     | V <sub>DD</sub> Over-Voltage Protection 2    |                                                         | 20  | 21   | 22   | V     |

| VDD-OVP-HYS1             | Hysteresis Voltage for V <sub>DD</sub> OVP 1 |                                                         | 1.2 | 1.7  | 2.2  | V     |

| $V_{\text{DD-OVP-HYS2}}$ | Hysteresis Voltage for $V_{DD}$ OVP 2        |                                                         | 1.2 | 1.7  | 2.2  | V     |

| t <sub>OVP1</sub>        | V <sub>DD</sub> OVP Debounce Time 1          |                                                         | 40  | 60   | 100  | μs    |

| t <sub>OVP2</sub>        | V <sub>DD</sub> OVP Debounce Time 2          |                                                         | 40  | 60   | 100  | μs    |

| Output Drive             | for SR MOSFET Section                        |                                                         |     |      |      |       |

| V <sub>Z1</sub>          | Output Voltage Maximum (Clamp) 1             | V <sub>DD</sub> = 20V                                   |     | 12   | 14   | V     |

| V <sub>Z2</sub>          | Output Voltage Maximum (Clamp) 2             | V <sub>DD</sub> = 20V                                   |     | 12   | 14   | V     |

| V <sub>OL1</sub>         | Output Voltage LOW 1                         | $V_{DD}$ =12V, $I_{O}$ =50mA                            |     |      | 0.5  | V     |

| V <sub>OL2</sub>         | Output Voltage LOW 2                         | $V_{DD}$ =12V, $I_{O}$ =50mA                            |     |      | 0.5  | V     |

| V <sub>OH1</sub>         | Output Voltage HIGH 1                        | $V_{DD}$ =12V, I <sub>O</sub> =50mA                     | 9   |      |      | V     |

| V <sub>OH2</sub>         | Output Voltage HIGH 2                        | $V_{DD}$ =12V, $I_{O}$ =50mA                            | 9   |      |      | V     |

| t <sub>R1</sub>          | Rising Time 1                                | $V_{DD}$ =12V, C <sub>L</sub> =7nF,<br>OUT=2V~9V        | 30  | 70   | 120  | ns    |

| t <sub>R2</sub>          | Rising Time 2                                | $V_{DD}$ =12V, C <sub>L</sub> =7nF,<br>OUT=2V~9V        | 30  | 70   | 120  | ns    |

| t⊧ı                      | Falling Time1                                | $V_{DD}$ =12V, C <sub>L</sub> =7nF,<br>OUT=9V~2V        | 20  | 50   | 100  | ns    |

| t <sub>F2</sub>          | Falling Time 2                               | V <sub>DD</sub> =12V, C <sub>L</sub> =7nF,<br>OUT=9V~2V | 20  | 50   | 100  | ns    |

| V <sub>Z1</sub>          | Output Voltage Maximum (Clamp)               | V <sub>DD</sub> = 20V                                   |     | 12   | 14   | V     |

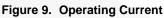

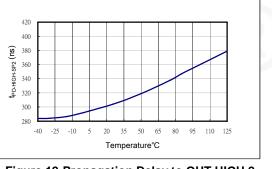

| t <sub>PD-HIGH-SP1</sub> |                                              | t <sub>R</sub> +t <sub>PD</sub> ,                       | 280 | 350  | 450  |       |

| t <sub>PD-HIGH-SP2</sub> | Propagation Delay to OUT HIGH                | (Trigger by SP),<br> SP-SN =5V                          | 280 | 350  | 450  | ns    |

| tpd-low-sn1              |                                              | t <sub>R</sub> +t <sub>PD</sub> ,                       | 180 | 250  | 350  |       |

| $t_{\text{PD-LOW-SN2}}$  | Propagation Delay to OUT LOW                 | (Trigger by SN),<br> SP-SN =5V                          | 180 | 250  | 350  | ns    |

| t <sub>PD-LOW-LPC1</sub> |                                              | t <sub>R</sub> +t <sub>PD</sub> ,                       | 100 | 150  | 200  |       |

| t <sub>PD-LOW-LPC2</sub> | Propagation Delay to OUT LOW                 | (Trigger by LPC)                                        | 100 | 150  | 200  | ns    |

| t <sub>ON-MAX1</sub>     | – Maximum On Time                            |                                                         | 12  | 13   | 14   | μs    |

| t <sub>ON-MAX2</sub>     |                                              |                                                         | 12  | 13   | 14   | μs    |

Continued on the following page...

$V_{DD}$ =20V,  $T_A$ =25°C, unless otherwise specified.

| Symbol                       | Parameter                                                           | Conditions                                                                                     | Min. | Тур. | Max. | Units |

|------------------------------|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------|------|------|-------|

| SP/SN Section                | on                                                                  |                                                                                                |      |      |      |       |

| V <sub>N-P(turn off)</sub> 1 | Threshold Voltage of $V_N$ - $V_P$ to Turn-Off SR MOS 1             | Sweep V <sub>N-P-</sub> from LOW to HIGH                                                       | 3    | 4    | 5    | V     |

| $V_{N-P(turn off) 2}$        | Threshold Voltage of $V_N$ - $V_P$ to Turn-Off SR MOS 2             |                                                                                                | 3    | 4    | 5    | V     |

| VP-N(turn on) 1              | Threshold Voltage of $V_P$ - $V_N$ to Turn-On SR MOS 1              | Sweep $V_{P-N-}$ from LOW to HIGH                                                              | 3    | 4    | 5    | V     |

| VP-N(turn on) 2              | Threshold Voltage of $V_P$ - $V_N$ to Turn-On SR MOS 2              | Sweep $V_{P-N-}$ from LOW to HIGH                                                              | 3    | 4    | 5    | V     |

| Ratio_sp-sn                  | Voltage Difference between SP and SN                                | V <sub>SP</sub> -V <sub>SN</sub>   /<br>MIN(V <sub>SP</sub> ,V <sub>SN</sub> )                 |      |      | 5    | %     |

| LPC Section                  |                                                                     |                                                                                                |      |      |      |       |

| Ratio_LPC-RES                | Charge Divide Discharge Current<br>Transfer Ratio vs. Input Voltage | Connect a Diode<br>1N4148 and Divider<br>(Ratio 12) to LPC,<br>$V_{DET} = 3V$ , $V_{LPC} = 3V$ | 2.79 | 3.00 | 3.21 |       |

| $V_{LPC-EN1}$                | LPC Enable Threshold Voltage 1                                      |                                                                                                | 1.8  | 2.0  | 2.2  | V     |

| V <sub>LPC-EN2</sub>         | LPC Enable Threshold Voltage 2                                      |                                                                                                | 1.8  | 2.0  | 2.2  | V     |

| V <sub>LPC-CLAMP1</sub>      | Lower Clamp Voltage 1                                               | Ι <sub>LPC</sub> = -5μΑ                                                                        | 0.10 | 0.25 | 0.40 | V     |

| V <sub>LPC-CLAMP2</sub>      | Lower Clamp Voltage 2                                               | Ι <sub>LPC</sub> = -5μΑ                                                                        | 0.10 | 0.25 | 0.40 | V     |

| ILPC-SOURCE1                 | Maximum Source Current 1                                            | V <sub>LPC</sub> = -0.3V                                                                       |      | 250  | 300  | μA    |

| ILPC-SOURCE2                 | Maximum Source Current 2                                            | $V_{LPC} = -0.3V$                                                                              |      | 250  | 300  | μA    |

| V <sub>LPC-LOW1</sub>        | Threshold Voltage for Disable<br>LPC Function                       |                                                                                                | 1.3  | 1.5  | 1.7  | V     |

| V <sub>LPC-LOW2</sub>        | Threshold Voltage for Disable<br>LPC Function                       |                                                                                                | 1.3  | 1.5  | 1.7  | v     |

| t <sub>LPC-LOW1</sub>        | Debounce Time for Disable LPC<br>Function                           | V <sub>LPC</sub> < V <sub>LPC-LOW</sub>                                                        | 70   | 100  | 130  | μs    |

| t <sub>LPC-LOW2</sub>        | Debounce Time for Disable LPC<br>Function                           | V <sub>LPC</sub> < V <sub>LPC-LOW</sub>                                                        | 70   | 100  | 130  | μs    |

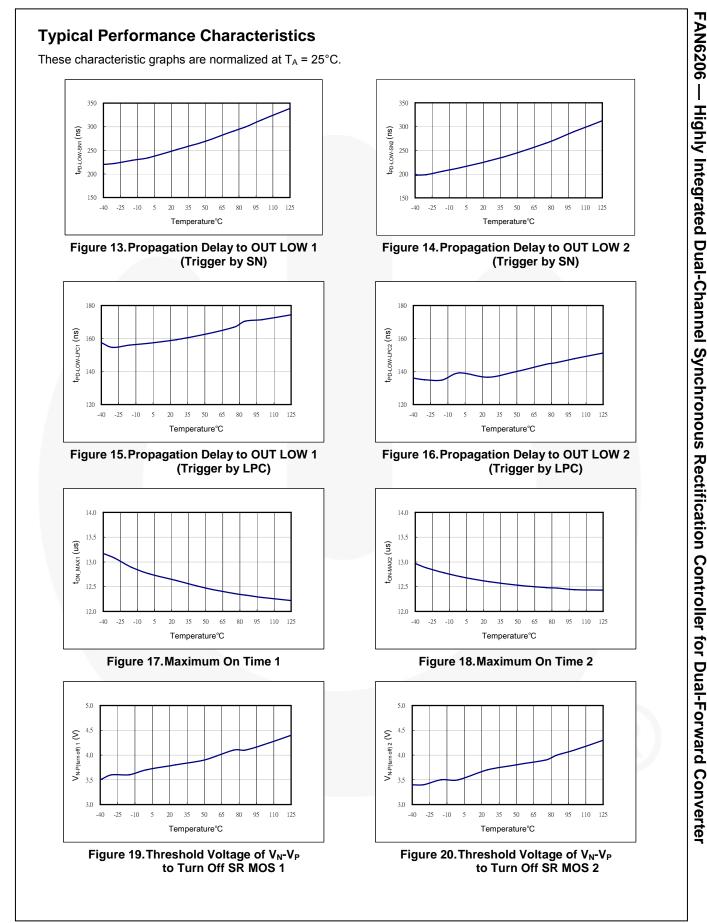

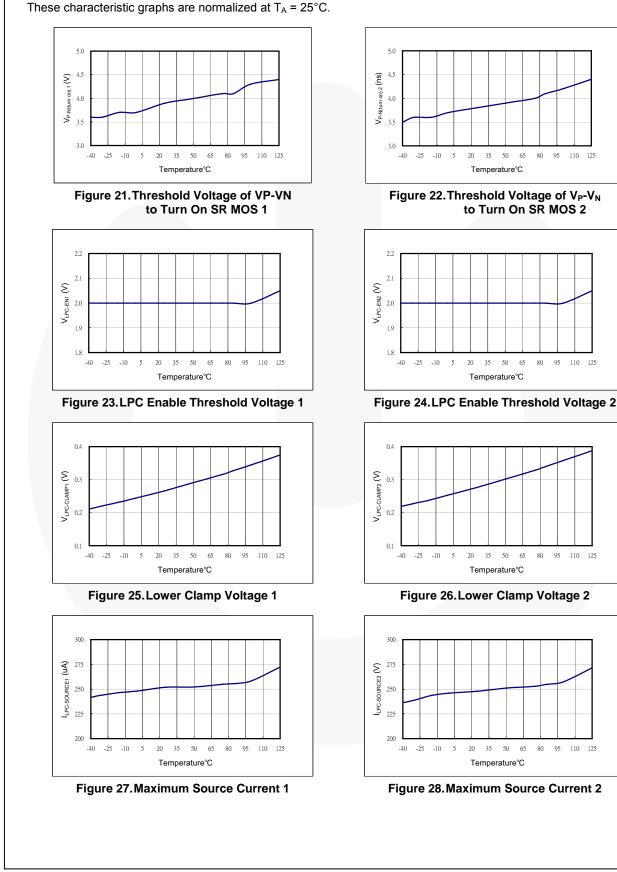

### **Typical Performance Characteristics**

These characteristic graphs are normalized at  $T_A = 25^{\circ}C$ .

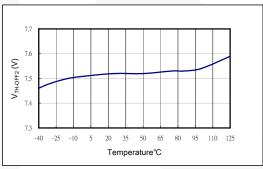

Figure 5. Turn-On Threshold Voltage 1

Figure 7. Turn-Off Threshold Voltage 1

Figure 8. Turn-Off Threshold Voltage 2

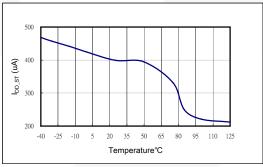

Figure 10. Startup Current

**Typical Performance Characteristics**

110 125

50 65

110 125

110 125

95 110 125

### **Function Description**

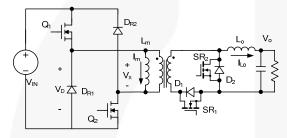

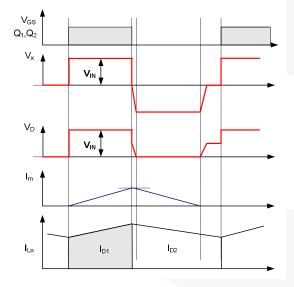

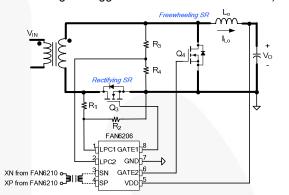

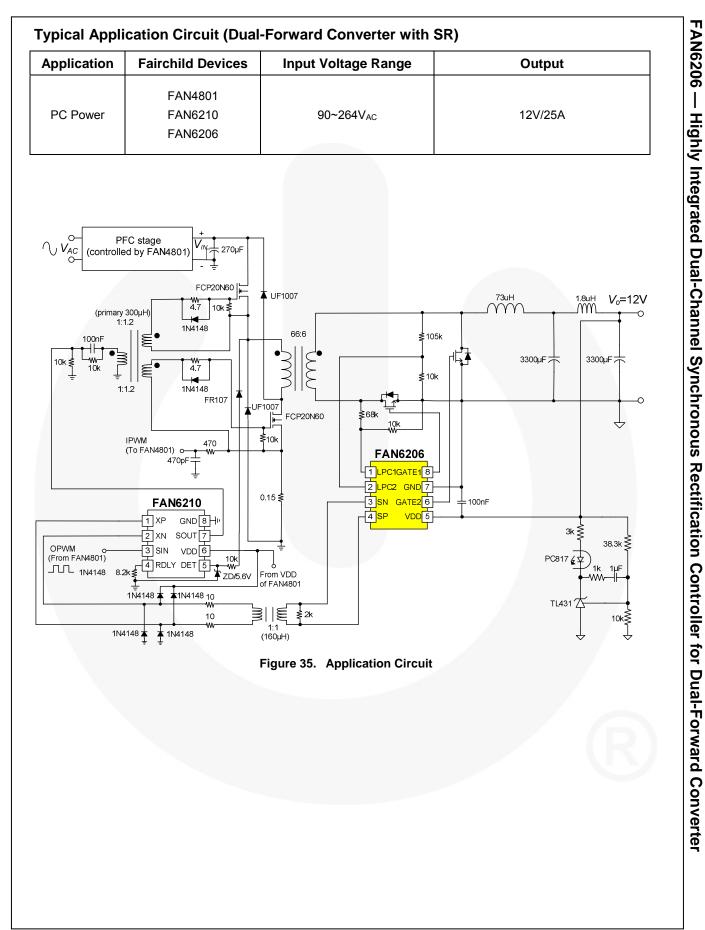

Figure 29 and Figure 30 show the simplified circuit diagram of a dual-forward converter and its key waveforms. Switches Q1 and Q2 are turned on and off together. Once Q<sub>1</sub> and Q<sub>2</sub> are turned on, input voltage is applied across the transformer primary side and power is delivered to the secondary side through the transformer, powering D1. During this time, the magnetizing current linearly increases. When Q1 and Q2 are turned off, the magnetizing current of the transformer forces the reset diodes ( $D_{R1}$  and  $D_{R2}$ ) and negative input voltage is applied across the transformer primary side. During this time, magnetizing current linearly decreases to zero and the secondary-side inductor current freewheels through diode D2. When synchronous rectifier SR1 and SR2 are used instead of diodes D<sub>1</sub> and D<sub>2</sub>, it is important to have proper timing between drive signals for SR1 and SR2.

Figure 29. Simplified Circuit Diagram of Dual-Forward Converter

Figure 31 shows a typical application circuit. When a dual-forward converter operates in continuous conduction mode, the SR gate signals (GATE1 and GATE2) are mainly controlled by SP and SN signals. SP and SN signals are transferred through a pulse transformer from XP and XN signals, which are generated by FAN6210 (Primary-Side Synchronous Rectifier Signal Trigger for Dual Forward Converter).

**Figure 31. Typical Application Circuit**

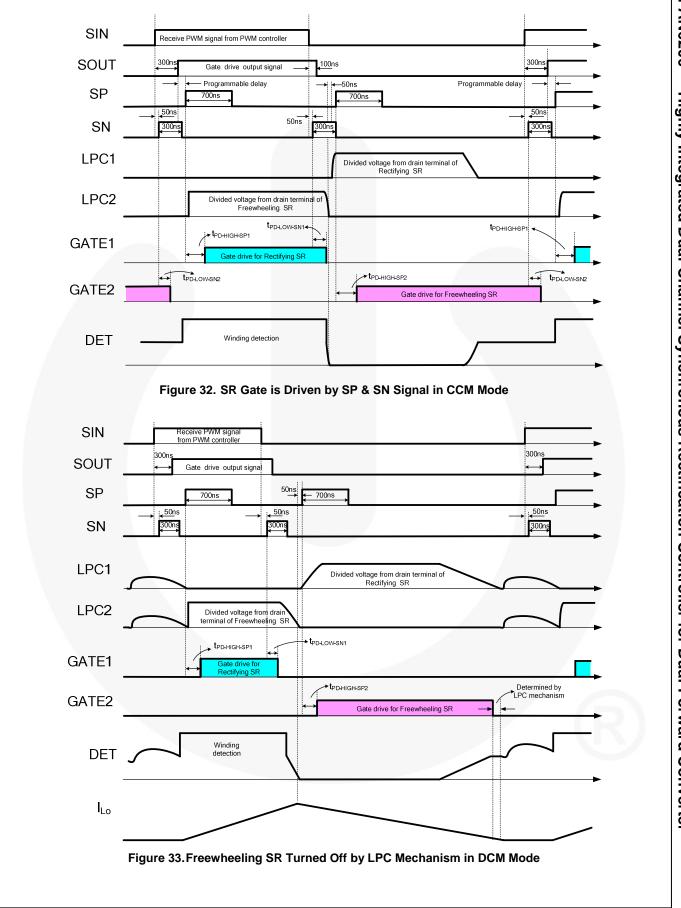

Figure 32 shows the timing diagram for continuous conduction mode (CCM). Figure 33 shows the timing diagram for discontinuous conduction mode (DCM).

The switching operation of SR MOSFETs  $Q_3$  and  $Q_4$  is determined by the SN and SP signals. FAN6206 turns on SR MOSFETs at the rising edge of the SP signal, while it turns off the SR MOSFETs at the rising edge of the SN signal. Within one switching cycle, SP and SN are obtained two times.

With a voltage divider  $R_1$  and  $R_2$  connected from LPC1 to secondary winding,  $R_3$  and  $R_4$  connected from LPC2 to secondary winding, the PWM timing sequences and frequency can be tracked precisely. The SR MOSFET is turned on by SP signal only when the voltage level on LPC1 or LPC2 pin is pulled LOW to GND.

During PWM-on period, the rectifying SR  $Q_3$  is turned on by the rising edge of the SP signal after a propagation delay ( $t_{PD-HIGH-SP1}$ ) and  $Q_3$  is turned off by the rising edge of the SN signal after a propagation delay ( $t_{PD-LOW-SN1}$ ). During PWM-off period, the freewheeling SR  $Q_4$  is turned on by the rising edge of the SP signal after a propagation delay ( $t_{PD-HIGH-SP2}$ ) and  $Q_4$  is turned off by the rising edge of the SN signal after a propagation delay ( $t_{PD-LOW-SN2}$ ) in CCM operation.

In DCM operation, the proprietary Linear-Predict Timing Control (LPC) technique can provide synchronous rectification control mechanism for freewheeling SR MOSFET. Since SN signal is sent following with PWM signal, the freewheeling SR MOSFET cannot be turned off in time by SN signal before  $I_{Lo}$  linearly decreases to zero. Therefore, the LPC mechanism is applied to turn off Q<sub>3</sub> in DCM mode.

#### **Linear-Predict Timing Control**

When a dual-forward converter operates in CCM or DCM; in PWM ton period, the VIN voltage is applied to the primary winding and the secondary inductor starts to rise linearly and store energy. The across voltage on secondary winding is coupled from primary winding and proportional to VIN. The SR controller can detect this winding voltage through a voltage divider and acquire the VIN level. According to this detected VIN level during PWM turn-on period, SR controller produces a charge current I<sub>CHG</sub> to charge internal capacitor, CT, of the SR controller. On the other hand, at PWM turn-off period, the energy stored in the secondary inductor is discharged. The SR controller also detects the output voltage level to modulate discharge current IDISCHG of internal capacitor, CT. Once the internal capacitor voltage reaches zero, SR controller turns off SR MOS immediately.

R<sub>4</sub> is connected between the LPC2 pin and the drain terminal of Q<sub>4</sub>. During PWM turn-on period, voltage on the LPC2 pin is pulled HIGH due to the secondary winding coupled from primary winding. At this moment, SR MOS is turned off and the internal body diode of SR MOS is reverse-biased. During PWM turn-off period, the potential on the primary winding reverses and the internal body diode starts to conduct output current. The voltage on the LPC2 pin is also pulled LOW to GND. R<sub>2</sub> is recommended as 10kΩ and the divided voltage level on the LPC1 pin is suggested between 3V~5V. If the voltage level of V<sub>0</sub> is 12V, the resistor values are recommended as 105kΩ for R<sub>3</sub> and 10kΩ for R<sub>4</sub>. The

turn-off timing of  $Q_4$  is determined by the ratio  $\frac{R_4}{R_3 + R_4}$

as Figure 34 shows. If  $\frac{R_4}{R_3 + R_4}$  decreases, Q<sub>4</sub> is turned

off earlier.

#### **Under-Voltage Lockout (UVLO)**

The power-on and off thresholds are fixed at 8.5V and 7.5V. The VDD pin is connected to a 12V output voltage terminal.

#### **VDD Pin Over-Voltage Protection**

The over-voltage conditions are usually caused by open feedback loops.  $V_{DD}$  over-voltage protection is built in to prevent damage if over voltage occurs. When the voltage on the VDD pin exceeds 21V, the SR controller turns off all of SR MOS operations.

Customers who inadvertently purchase counterfeit parts september and y problems such as loss of brand reputation, substandard performance, failed applications, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.

#### PRODUCT STATUS DEFINITIONS

| Datasheet Identification Product Status |                       | Definition                                                                                                                                                                                             |  |  |

|-----------------------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Advance Information                     | Formative / In Design | Datasheet contains the design specifications for product development. Specifications may change in<br>any manner without notice.                                                                       |  |  |

| Preliminary                             | First Production      | Datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild<br>Semiconductor reserves the right to make changes at any time without notice to improve design. |  |  |

| No Identification Needed                | Full Production       | Datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes<br>at any time without notice to improve the design.                                               |  |  |

| Obsolete                                | Not In Production     | Datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor.<br>The datasheet is for reference information only.                                                    |  |  |

Rev. 148

AN6206

— Highly Integrated Dual-Channel Synchronous Rectification Controller for Dual-Forward Converter