**DSP56651**

## Advance Information INTEGRATED CELLULAR BASEBAND PROCESSOR DEVELOPMENT IC

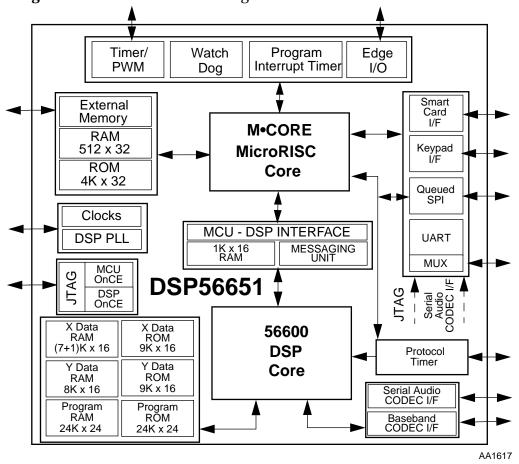

Motorola designed the RAM-based DSP56651 emulation device to support the rigorous demands of developing applications for the cellular subscriber market. The high level of on-chip integration in the DSP56651 and its volume production companion device DSP56652 minimizes application system design complexity and component count, resulting in very compact implementations. This integration also yields very low-power consumption and cost-effective system performance. The DSP56651 chip combines the power of Motorola's 32-bit M • CORE ™ MicroRISC Engine (MCU) and the DSP56600 digital signal processor (DSP) core with on-chip memory, protocol timer, and custom peripherals to provide a single-chip cellular base-band processor. **Figure 1** shows the basic block diagram of the DSP56651.

Figure 1-1 DSP56651 System Block Diagram

Development Part Only—Not intended for production. Requires a higher voltage than the production part

This document contains information on a new product. Specifications and information herein are subject to change without notice.

#### **TABLE OF CONTENTS**

| SECTION 1 | PIN AND SIGNAL DESCRIPTIONS |

|-----------|-----------------------------|

| SECTION 2 | SPECIFICATIONS              |

| SECTION 3 | PACKAGING                   |

| SECTION 4 | DESIGN CONSIDERATIONS4-1    |

| SECTION 5 | ORDERING INFORMATION        |

#### FOR TECHNICAL ASSISTANCE:

**Telephone:** 1 (800) 521-6274

Email: dsphelp@dsp.sps.mot.com

Internet: <a href="http://www.motorola-dsp.com">http://www.motorola-dsp.com</a>

#### **Data Sheet Conventions**

This data sheet uses the following conventions:

| OVERBAR      | Used to indicate a signal that is active when pulled low; for example, the $\overline{\text{RESET}}$ pin is active when low |                                                                                                   |                         |                         |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-------------------------|-------------------------|--|--|--|

| "asserted"   | Means that a high tru<br>signal is low                                                                                      | Means that a high true (active high) signal is high or that a low true (active low) signal is low |                         |                         |  |  |  |

| "deasserted" | Means that a high tru<br>signal is high                                                                                     | ue (active high) sign                                                                             | al is low or that a low | true (active low)       |  |  |  |

| Examples:    | Signal/Symbol                                                                                                               | Logic State                                                                                       | Signal State            | Voltage <sup>1</sup>    |  |  |  |

|              | $\overline{	ext{PIN}}$                                                                                                      | True                                                                                              | Asserted                | $V_{\rm IL}/V_{\rm OL}$ |  |  |  |

|              | PIN                                                                                                                         | False                                                                                             | Deasserted              | $V_{IH}/V_{OH}$         |  |  |  |

|              | PIN                                                                                                                         | True                                                                                              | Asserted                | $V_{IH}/V_{OH}$         |  |  |  |

|              | PIN                                                                                                                         | False                                                                                             | Deasserted              | $V_{\rm IL}/V_{\rm OL}$ |  |  |  |

Note: Values for  $V_{IL}$ ,  $V_{OL}$ ,  $V_{IH}$ , and  $V_{OH}$  are defined by individual product specifications.

#### **FEATURES**

#### RISC M•CORE MCU

- 32-bit load/store RISC architecture

- Fixed 16-bit instruction length

- 16-entry 32-bit general-purpose register file

- 32-bit internal address and data buses

- Efficient four-stage, fully interlocked execution pipeline

- Single-cycle execution for most instructions, two cycles for branches and memory accesses

- Special branch, byte, and bit manipulation instructions

- Support for byte, half-word, and word memory accesses

- Fast interrupt support via vectoring/auto-vectoring and a 16-entry dedicated alternate register file

#### **High Performance DSP56600 Core**

- $1 \times \text{engine (e.g., } 70 \text{ MHz} = 70 \text{ MIPS)}$

- Fully pipelined 16 × 16-bit parallel multiplier-accumulator (MAC)

- Two 40-bit accumulators including extension bits

- 40-bit parallel barrel shifter

- Highly parallel instruction set with unique DSP addressing modes

- Position-independent code support

- Nested hardware DO loops

- Fast auto-return interrupts

- On-chip support for software patching and enhancements

- Realtime trace capability via address bus visibility mode

#### **Features**

#### **On-chip Memories**

- 4K × 32-bit MCU ROM

- $512 \times 32$ -bit MCU RAM

- 24K × 24-bit DSP program ROM

- 24K × 24-bit DSP program RAM

- 18K × 16-bit DSP data ROM, split into 9K × 16-bit X and 9K x 16 Y data ROM spaces

- 16K  $\times$  16-bit DSP data RAM, split into (7+1)K  $\times$  16-bit X and 8K x 16-bit Y data RAM spaces

#### **On-chip Peripherals**

- Fully programmable phase-locked loop (PLL) for DSP clock generation

- External interface module (EIM) for glueless system integration

- External 22-bit address and 16-bit data MCU buses

- Thirty-two source MCU interrupt controller

- Intelligent MCU/DSP interface (MDI) dual 1K x 16-bit RAM (shares 1K DSP X data RAM) with messaging status and control

- Serial audio codec port

- Serial baseband codec port

- Protocol timer frees the MCU from radio channel timing events

- Queued serial peripheral interface (SPI)

- Keypad port capable of scanning up to an  $8 \times 8$  matrix keypad

- General-purpose MCU and DSP timers

- Pulse width modulation output

- Universal asynchronous receiver/transmitter (UART) with FIFO

- IEEE 1149.1-compliant boundary scan JTAG test access port (TAP)

- Integrated DSP/M CORE On-Chip Emulation (OnCE<sup>TM</sup>) module

- DSP address bus visibility mode for system development

- ISO 7816-compatible Smart Card port

#### **Operating Features:**

- Comprehensive static and dynamic power management

- M•CORE operating frequency: dc to 16.8 MHz at 2.4 V

- DSP operating frequency: dc to 58.8 MHz at 2.4 V

- Operating temperature: -40° to 85°C ambient

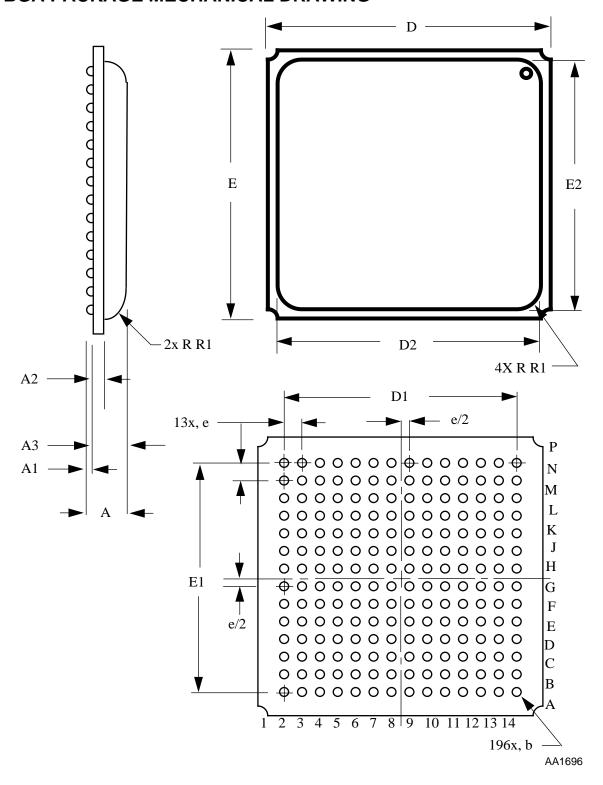

- Package option: 17 × 17 mm, 196-lead PBGA

#### **TARGET APPLICATIONS**

The DSP56651 is intended for the development of cellular subscriber applications and other applications needing both DSP and control processing.

#### PRODUCT DOCUMENTATION

The four manuals listed in **Table 1** are required for a complete description of the DSP56651 and are necessary to design with the part properly. Documentation is available from a local Motorola distributor, a Motorola semiconductor sales office, a Motorola Literature Distribution Center, or the World Wide Web.

Table 1 DSP56651 Documentation

| <b>Document Name</b>       | Description of Contents                                                                                        | Order Number  |

|----------------------------|----------------------------------------------------------------------------------------------------------------|---------------|

| DSP56600<br>Family Manual  | Detailed description of the DSP56600 family core processor architecture and instruction set                    | DSP56600FM/AD |

| M•CORE Reference<br>Manual | Detailed description of the M • CORE MCU and instruction set                                                   | MCORERM/AD    |

| DSP56652<br>User's Manual  | Detailed description of DSP56652 memory, peripherals, and interfaces, much of which are common to the DSP56651 | DSP56652UM/AD |

| DSP56651<br>Technical Data | DSP56651 pin and package descriptions; electrical and timing specifications                                    | DSP56651/D    |

**Product Documentation**

# SECTION 1 PIN AND SIGNAL DESCRIPTIONS

#### INTRODUCTION

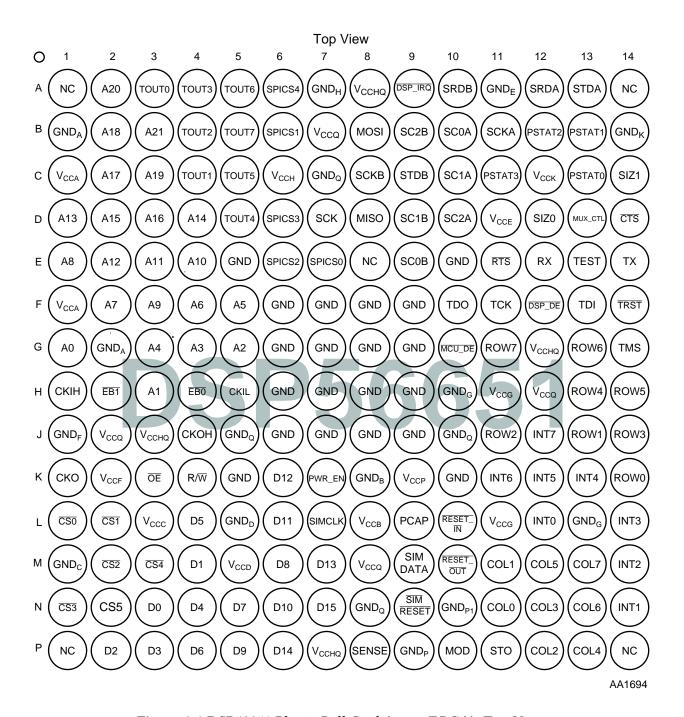

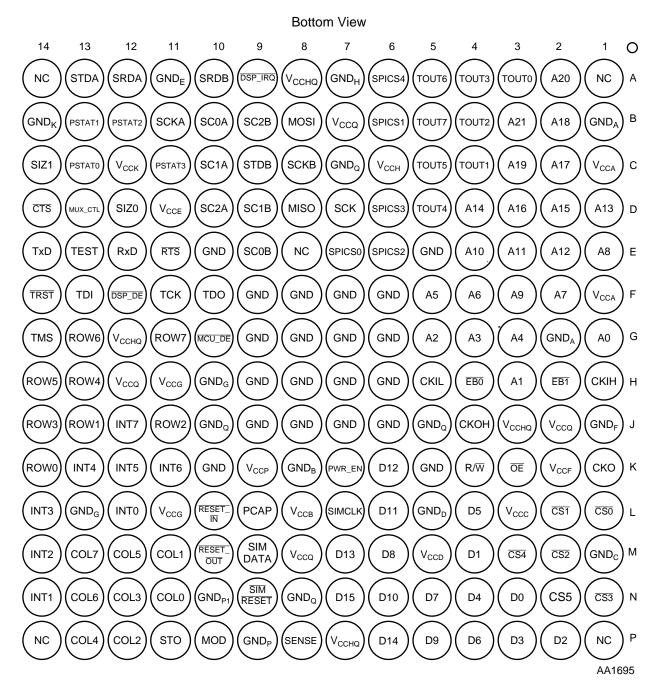

The pins and signals of the DSP56651 are described in the following sections. **Figure 1-1** and **Figure 1-2** on page 1-3 are top and bottom views of the package, respectively, showing the pin-outs. Subsequent tables list the pins by number and signal name. **Figure 1-3** on page 1-11 is a representational pin-out of the chip grouping the signals by their function. Subsequent tables identify the signals of each group.

#### **DSP56651 PIN DESCRIPTION**

The following section provides information about the available packages for this product, including diagrams of the package pinouts and tables describing how the signals of the DSP56651 are allocated for the 196-pin plastic ball grid array (PBGA) package. Top and bottom views of the PBGA package are shown in **Figure 1-1** and **Figure 1-2** on page 1-3 with their pin-outs.

#### **PBGA Package Description**

Figure 1-1 DSP56651 Plastic Ball Grid Array (PBGA), Top View

Figure 1-2 DSP56651 Plastic Ball Grid Array (PBGA), Bottom View

Table 1-1

DSP56651 PBGA Signal Identification by Pin Number

| Pin<br>No. | Signal Name                     | Pin<br>No. | Signal Name                 | Pin<br>No. | Signal Name      |

|------------|---------------------------------|------------|-----------------------------|------------|------------------|

| A1         | Not Connected (NC),<br>reserved | B12        | PSTAT2                      | D9         | SC1B             |

| A2         | A20                             | B13        | PSTAT1                      | D10        | SC2A             |

| A3         | TOUT0                           | B14        | $GND_K$                     | D11        | $V_{CCE}$        |

| A4         | TOUT3                           | C1         | $V_{CCA}$                   | D12        | SIZ0             |

| A5         | TOUT6                           | C2         | A17                         | D13        | MUX_CTL          |

| A6         | SPICS4                          | C3         | A19                         | D14        | CTS              |

| A7         | $GND_H$                         | C4         | TOUT1                       | E1         | A8               |

| A8         | $V_{CCHQ}$                      | C5         | TOUT5                       | E2         | A12              |

| A9         | DSP_IRQ                         | C6         | $V_{CCH}$                   | E3         | A11              |

| A10        | SRDB                            | C7         | $\mathrm{GND}_{\mathrm{Q}}$ | E4         | A10              |

| A11        | $GND_E$                         | C8         | SCKB                        | E5         | GND              |

| A12        | SRDA                            | C9         | STDB                        | E6         | SPICS2           |

| A13        | STDA                            | C10        | SC1A                        | E7         | SPICS0           |

| A14        | NC                              | C11        | PSTAT3                      | E8         | NC               |

| B1         | $GND_A$                         | C12        | V <sub>CCK</sub>            | E9         | SC0B             |

| B2         | A18                             | C13        | PSTAT0                      | E10        | GND              |

| В3         | A21                             | C14        | SIZ1                        | E11        | RTS              |

| B4         | TOUT2                           | D1         | A13                         | E12        | RxD              |

| B5         | TOUT7                           | D2         | A15                         | E13        | TEST             |

| B6         | SPICS1                          | D3         | A16                         | E14        | TxD              |

| В7         | $V_{CCQ}$                       | D4         | A14                         | F1         | V <sub>CCA</sub> |

| B8         | MOSI                            | D5         | TOUT4                       | F2         | A7               |

| В9         | SC2B                            | D6         | SPICS3                      | F3         | A9               |

| B10        | SC0A                            | D7         | SCK                         | F4         | A6               |

| B11        | SCKA                            | D8         | MISO                        | F5         | A5               |

Table 1-1

DSP56651 PBGA Signal Identification by Pin Number (Continued)

| Pin<br>No. | Signal Name | Pin<br>No. | Signal Name                 | Pin<br>No. | Signal Name      |

|------------|-------------|------------|-----------------------------|------------|------------------|

| F6         | GND         | Н3         | A1                          | J14        | ROW3             |

| F7         | GND         | H4         | EB0                         | K1         | СКО              |

| F8         | GND         | H5         | CKIL                        | K2         | V <sub>CCF</sub> |

| F9         | GND         | H6         | GND                         | K3         | ŌĒ               |

| F10        | TDO         | H7         | GND                         | K4         | $R/\overline{W}$ |

| F11        | TCK         | H8         | GND                         | K5         | GND              |

| F12        | DSP_DE      | H9         | GND                         | K6         | D12              |

| F13        | TDI         | H10        | $\mathrm{GND}_{\mathrm{G}}$ | K7         | PWR_EN           |

| F14        | TRST        | H11        | $V_{CCG}$                   | K8         | $GND_B$          |

| G1         | A0          | H12        | $V_{CCQ}$                   | K9         | V <sub>CCP</sub> |

| G2         | $GND_A$     | H13        | ROW4                        | K10        | GND              |

| G3         | A4          | H14        | ROW5                        | K11        | INT6             |

| G4         | A3          | J1         | $\mathrm{GND}_{\mathrm{F}}$ | K12        | INT5             |

| G5         | A2          | J2         | $V_{CCQ}$                   | K13        | INT4             |

| G6         | GND         | Ј3         | $V_{CCHQ}$                  | K14        | ROW0             |

| G7         | GND         | J4         | СКОН                        | L1         | CS0              |

| G8         | GND         | J5         | $\mathrm{GND}_{\mathrm{Q}}$ | L2         | CS1              |

| G9         | GND         | J6         | GND                         | L3         | V <sub>CCC</sub> |

| G10        | MCU_DE      | J7         | GND                         | L4         | D5               |

| G11        | ROW7        | J8         | GND                         | L5         | $GND_D$          |

| G12        | $V_{CCHQ}$  | J9         | GND                         | L6         | D11              |

| G13        | ROW6        | J10        | $\mathrm{GND}_{\mathrm{Q}}$ | L7         | SIMCLK           |

| G14        | TMS         | J11        | ROW2                        | L8         | V <sub>CCB</sub> |

| H1         | CKIH        | J12        | INT7                        | L9         | PCAP             |

| H2         | EB1         | J13        | ROW1                        | L10        | RESET_IN         |

Table 1-1

DSP56651 PBGA Signal Identification by Pin Number (Continued)

| Pin<br>No. | Signal Name | Pin<br>No. | Signal Name                 | Pin<br>No. | Signal Name       |

|------------|-------------|------------|-----------------------------|------------|-------------------|

| L11        | $V_{CCG}$   | M13        | COL7                        | P1         | NC                |

| L12        | INT0        | M14        | INT2                        | P2         | D2                |

| L13        | $GND_G$     | N1         | CS3                         | P3         | D3                |

| L14        | INT3        | N2         | CS5                         | P4         | D6                |

| M1         | $GND_C$     | N3         | D0                          | P5         | D9                |

| M2         | CS2         | N4         | D4                          | P6         | D14               |

| М3         | CS4         | N5         | D7                          | P7         | V <sub>CCHQ</sub> |

| M4         | D1          | N6         | D10                         | P8         | SENSE             |

| M5         | $V_{CCD}$   | N7         | D15                         | P9         | GND <sub>P</sub>  |

| M6         | D8          | N8         | $\mathrm{GND}_{\mathrm{Q}}$ | P10        | MOD               |

| M7         | D13         | N9         | SIMRESET                    | P11        | STO               |

| M8         | $V_{CCQ}$   | N10        | GND <sub>P1</sub>           | P12        | COL2              |

| M9         | SIMDATA     | N11        | COL0                        | P13        | COL4              |

| M10        | RESET_OUT   | N12        | COL3                        | P14        | NC                |

| M11        | COL1        | N13        | COL6                        |            |                   |

| M12        | COL5        | N14        | INT1                        |            |                   |

Table 1-2

DSP56651 PBGA Signal Identification by Name

| Signal Name | Pin<br>No. | Signal Name    | Pin<br>No. | Signal Name | Pin<br>No. |

|-------------|------------|----------------|------------|-------------|------------|

| A0          | G1         | СКОН           | J4         | D9          | P5         |

| A1          | Н3         | COL0           | N11        | D10         | N6         |

| A2          | G5         | COL1           | M11        | D11         | L6         |

| A3          | G4         | COL2           | P12        | D12         | K6         |

| A4          | G3         | COL3           | N12        | D13         | M7         |

| A5          | F5         | COL4           | P13        | D14         | P6         |

| A6          | F4         | COL5           | M12        | D15         | N7         |

| A7          | F2         | COL6           | N13        | DSP_DE      | F12        |

| A8          | E1         | COL7           | M13        | DSP_IRQ     | A9         |

| A9          | F3         | <del>CS0</del> | L1         | EB0         | H4         |

| A10         | E4         | <del>CS1</del> | L2         | EB1         | H2         |

| A11         | E3         | CS2            | M2         | GND         | E10        |

| A12         | E2         | CS3            | N1         | GND         | E5         |

| A13         | D1         | CS4            | M3         | GND         | F6         |

| A14         | D4         | CS5            | N2         | GND         | F7         |

| A15         | D2         | CTS            | D14        | GND         | F8         |

| A16         | D3         | D0             | N3         | GND         | F9         |

| A17         | C2         | D1             | M4         | GND         | G6         |

| A18         | B2         | D2             | P2         | GND         | G7         |

| A19         | С3         | D3             | Р3         | GND         | G8         |

| A20         | A2         | D4             | N4         | GND         | G9         |

| A21         | В3         | D5             | L4         | GND         | H6         |

| CKIH        | H1         | D6             | P4         | GND         | H7         |

| CKIL        | H5         | D7             | N5         | GND         | H8         |

| СКО         | K1         | D8             | M6         | GND         | H9         |

Table 1-2

DSP56651 PBGA Signal Identification by Name (Continued)

| Signal Name                 | Pin<br>No. | Signal Name      | Pin<br>No. | Signal Name | Pin<br>No. |

|-----------------------------|------------|------------------|------------|-------------|------------|

| GND                         | J6         | INT2             | M14        | RESET_OUT   | M10        |

| GND                         | J7         | INT3             | L14        | ROW0        | K14        |

| GND                         | J8         | INT4             | K13        | ROW1        | J13        |

| GND                         | J9         | INT5             | K12        | ROW2        | J11        |

| GND                         | K10        | INT6             | K11        | ROW3        | J14        |

| GND                         | K5         | INT7             | J12        | ROW4        | H13        |

| $GND_A$                     | B1         | MCU_DE           | G10        | ROW5        | H14        |

| $GND_A$                     | G2         | MISO             | D8         | ROW6        | G13        |

| $GND_B$                     | K8         | MOD              | P10        | ROW7        | G11        |

| $GND_C$                     | M1         | MOSI             | B8         | RTS         | E11        |

| $GND_D$                     | L5         | MUX_CTL          | D13        | RxD         | E12        |

| $GND_E$                     | A11        | NC               | A1         | SC0A        | B10        |

| $\mathrm{GND}_{\mathrm{F}}$ | J1         | NC               | A14        | SC0B        | E9         |

| $\mathrm{GND}_{\mathrm{G}}$ | H10        | NC               | E8         | SC1A        | C10        |

| $\mathrm{GND}_{\mathrm{G}}$ | L13        | NC               | P1         | SC1B        | D9         |

| $GND_H$                     | A7         | NC               | P14        | SC2A        | D10        |

| $GND_K$                     | B14        | ŌĒ               | К3         | SC2B        | В9         |

| $GND_P$                     | P9         | PCAP             | L9         | SCK         | D7         |

| GND <sub>P1</sub>           | N10        | PSTAT0           | C13        | SCKA        | B11        |

| $\mathrm{GND}_{\mathrm{Q}}$ | C7         | PSTAT1           | B13        | SCKB        | C8         |

| $\mathrm{GND}_{\mathrm{Q}}$ | J10        | PSTAT2           | B12        | SENSE       | P8         |

| $\mathrm{GND}_{\mathrm{Q}}$ | J5         | PSTAT3           | C11        | SIMCLK      | L7         |

| $\mathrm{GND}_{\mathrm{Q}}$ | N8         | PWR_EN           | K7         | SIMDATA     | M9         |

| INT0                        | L12        | $R/\overline{W}$ | K4         | SIMRESET    | N9         |

| INT1                        | N14        | RESET_IN         | L10        | SIZ0        | D12        |

Table 1-2

DSP56651 PBGA Signal Identification by Name (Continued)

| Signal Name | Pin<br>No. | Signal Name      | Pin<br>No. | Signal Name      | Pin<br>No. |

|-------------|------------|------------------|------------|------------------|------------|

| SIZ1        | C14        | TOUT0            | A3         | V <sub>CCF</sub> | K2         |

| SPICS0      | E7         | TOUT1            | C4         | V <sub>CCG</sub> | H11        |

| SPICS1      | В6         | TOUT2            | B4         | V <sub>CCG</sub> | L11        |

| SPICS2      | E6         | TOUT3            | A4         | V <sub>CCH</sub> | C6         |

| SPICS3      | D6         | TOUT4            | D5         | $V_{\rm CCHQ}$   | A8         |

| SPICS4      | A6         | TOUT5            | C5         | $V_{\rm CCHQ}$   | G12        |

| SRDA        | A12        | TOUT6            | A5         | $V_{\rm CCHQ}$   | J3         |

| SRDB        | A10        | TOUT7            | B5         | $V_{\rm CCHQ}$   | P7         |

| STDA        | A13        | TRST             | F14        | V <sub>CCK</sub> | C12        |

| STDB        | C9         | TxD              | E14        | V <sub>CCP</sub> | K9         |

| STO         | P11        | V <sub>CCA</sub> | C1         | $V_{CCQ}$        | В7         |

| TCK         | F11        | V <sub>CCA</sub> | F1         | $V_{CCQ}$        | J2         |

| TDI         | F13        | V <sub>CCB</sub> | L8         | $V_{CCQ}$        | H12        |

| TDO         | F10        | V <sub>CCC</sub> | L3         | $V_{CCQ}$        | M8         |

| TEST        | E13        | V <sub>CCD</sub> | M5         |                  |            |

| TMS         | G14        | V <sub>CCE</sub> | D11        |                  |            |

#### **DSP56651 SIGNAL DESCRIPTION**

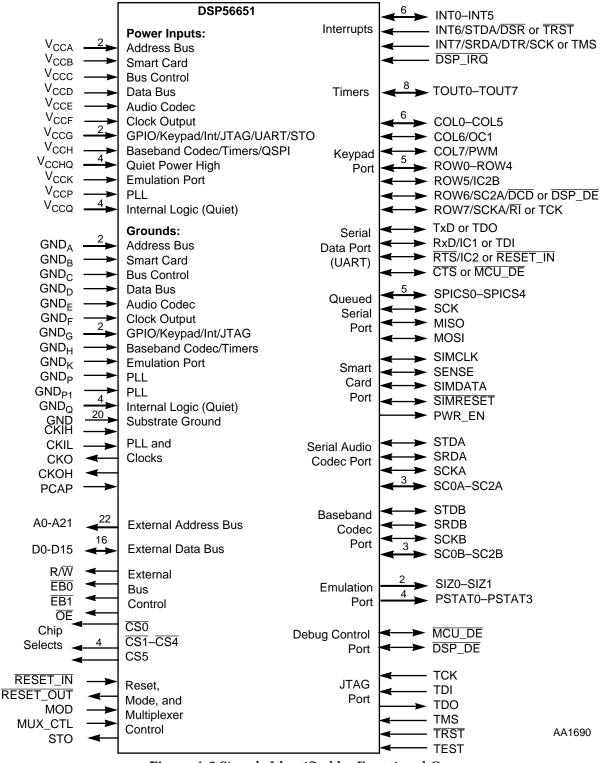

DSP56651 signals are organized into nineteen functional groups as summarized in **Table 1-3**. **Figure 1-3** is a diagram of DSP56651 signals by functional group.

Table 1-3

Signal Functional Group Allocations

| Functional Group                     |                 | Number<br>of<br>Signals | Detailed<br>Description |

|--------------------------------------|-----------------|-------------------------|-------------------------|

| Power (V <sub>CCX</sub> )            |                 | 20                      | Table 1-4               |

| Ground (GND <sub>X</sub> )           |                 | 17                      | Table 1-5               |

| Substrate ground (GND)               |                 | 20                      |                         |

| PLL and clocks                       |                 | 5                       | Table 1-6               |

| Address bus                          | External        | 22                      | Table 1-7               |

| Data bus                             | Interface       | 16                      | Table 1-8               |

| Bus control                          | Module<br>(EIM) | 4                       | Table 1-9               |

| Chip selects                         | 6               | Table 1-10              |                         |

| Reset, mode, and multiplexer control |                 | 5                       | Table 1-11              |

| External interrupts                  |                 | 9                       | Table 1-12              |

| Timers                               |                 | 8                       | Table 1-13              |

| Keypad port                          |                 | 16                      | Table 1-14              |

| Serial data port (UART)              |                 | 4                       | Table 1-15              |

| Serial control port (QSPI)           |                 | 8                       | Table 1-16              |

| Smart Card port (SIM)                |                 | 5                       | Table 1-17              |

| Serial audio codec port (SAP)        |                 | 6                       | Table 1-18              |

| Baseband codec port                  |                 |                         | Table 1-19              |

| Emulation port Develop-              |                 | 6                       | Table 1-20              |

| Debug control port ment              |                 | 2                       | Table 1-21              |

| JTAG test access port (TAP) and Test |                 | 6                       | Table 1-22              |

Figure 1-3 Signals Identified by Functional Group

#### **Power**

**Table 1-4** Power

| Power Names       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{CCA}$         | Address Bus power—These lines supply power to the address bus.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| V <sub>CCB</sub>  | Smart Card interface power—This line supplies isolated power for Smart Card Interface I/O drivers.                                                                                                                                                                                                                                                                                                                                                                                 |

| V <sub>CCC</sub>  | Bus control power—This line supplies power to the bus control logic.                                                                                                                                                                                                                                                                                                                                                                                                               |

| V <sub>CCD</sub>  | Data bus power—These lines supply power to the data bus.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| V <sub>CCE</sub>  | Audio codec port power—This line supplies power to audio codec I/O drivers.                                                                                                                                                                                                                                                                                                                                                                                                        |

| $V_{CCF}$         | Clock output power—This line supplies a quiet power source for the CKOUT output. Ensure that the input voltage to this line is well-regulated and uses an extremely low impedance path to tie to the $V_{CC}$ power rail. Use a 0.1 $\mu F$ bypass capacitor located as close as possible to the chip package to connect between the $V_{CCF}$ line and the $GND_F$ line.                                                                                                          |

| $V_{CCG}$         | <b>GPIO power</b> —This line supplies power to the GPIO, keypad, data port, interrupts, STO, and JTAG I/O drivers.                                                                                                                                                                                                                                                                                                                                                                 |

| V <sub>CCH</sub>  | <b>Baseband codec and timer power</b> —This line supplies power to the baseband codec, timer and QSPI I/O drivers.                                                                                                                                                                                                                                                                                                                                                                 |

| V <sub>CCHQ</sub> | <b>Quiet power high</b> —These lines supply a quiet power source to the pre-driver voltage converters. This value should be greater than or equal to the maximum value of the power supplies of the chip I/O drivers (i.e., the maximum of $V_{CCA}$ , $V_{CCB}$ , $V_{CCC}$ , $V_{CCD}$ , $V_{CCE}$ , $V_{CCF}$ , $V_{CCG}$ , $V_{CCH}$ , and $V_{CCK}$ ).                                                                                                                        |

| $V_{CCK}$         | <b>Emulation port power</b> —This line supplies power to the emulation port I/O drivers.                                                                                                                                                                                                                                                                                                                                                                                           |

| V <sub>CCP</sub>  | Analog PLL circuit power—This line is dedicated to the analog PLL circuits and must remain noise-free to ensure stable PLL frequency and performance. Ensure that the input voltage to this line is well-regulated and uses an extremely low impedance path to tie to the $V_{CC}$ power rail. Use a 0.1 $\mu F$ capacitor and a 0.01 $\mu F$ capacitor located as close as possible to the chip package to connect between the $V_{CCP}$ line and the GNDp and GND $_{P1}$ lines. |

| $V_{CCQ}$         | <b>Quiet power</b> —These lines supply a quiet power source to the internal logic circuits. Ensure that the input voltage to this line is well-regulated and uses an extremely low impedance path to tie to the $V_{CC}$ power rail. Use a 0.1 $\mu F$ bypass capacitor located as close as possible to the chip package to connect between the $V_{CCQ}$ lines and the $GND_Q$ lines.                                                                                             |

#### Ground

Table 1-5 Ground

| <b>Ground Names</b>         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $GND_A$                     | Address Bus ground—These lines connect system ground to the address bus.                                                                                                                                                                                                                                                                                                                                                                                    |

| $GND_B$                     | Smart Card interface ground—These lines connect system ground to the Smart Card bus.                                                                                                                                                                                                                                                                                                                                                                        |

| $GND_C$                     | Bus control ground—This line connects ground to the bus control logic.                                                                                                                                                                                                                                                                                                                                                                                      |

| $GND_D$                     | Data bus ground—These lines connect system ground to the data bus.                                                                                                                                                                                                                                                                                                                                                                                          |

| $GND_E$                     | <b>Audio codec port ground</b> —These lines connect system ground to the audio codec port.                                                                                                                                                                                                                                                                                                                                                                  |

| $\mathrm{GND}_{\mathrm{F}}$ | Clock output ground—This line supplies a quiet ground connection for the clock output drivers. Ensure that this line connects through an extremely low impedance path to ground. Use a 0.1 $\mu F$ bypass capacitor located as close as possible to the chip package to connect between the $V_{CCF}$ line and the $GND_F$ line.                                                                                                                            |

| $\mathrm{GND}_{\mathrm{G}}$ | <b>GPIO ground</b> —These lines connect system ground to GPIO, keypad, data port, interrupts, STO, and JTAG I/O drivers.                                                                                                                                                                                                                                                                                                                                    |

| $GND_H$                     | <b>Baseband codec and timer ground</b> —These lines connect system ground to the baseband codec, timer and QSPI I/O drivers.                                                                                                                                                                                                                                                                                                                                |

| $GND_K$                     | <b>Emulation port ground</b> —These lines connect system ground to the emulation port I/O drivers.                                                                                                                                                                                                                                                                                                                                                          |

| GND <sub>P</sub>            | Analog PLL circuit ground—This line supplies a dedicated quiet ground connection for the analog PLL circuits and must remain relatively noise-free to ensure stable PLL frequency and performance. Ensure that this line connects through an extremely low impedance path to ground. Use a 0.1 $\mu F$ capacitor and a 0.01 $\mu F$ capacitor located as close as possible to the chip package to connect between the $V_{CCP}$ line and the GND $_P$ line. |

| GND <sub>P1</sub>           | Analog PLL circuit ground—This line supplies a dedicated quiet ground connection for the analog PLL circuits and must remain relatively noise-free to ensure stable PLL frequency and performance. Ensure that this line connects through an extremely low impedance path to ground. Use a 0.1 $\mu F$ capacitor and a 0.01 $\mu F$ capacitor located as close as possible to the chip package to connect between the $V_{CCP}$ line and the GNDp line.     |

| $\mathrm{GND}_{\mathrm{Q}}$ | <b>Quiet ground</b> —These lines supply a quiet ground connection for the internal logic circuits. Ensure that this line connects through an extremely low impedance path to ground. Use a 0.1 $\mu F$ bypass capacitor located as close as possible to the chip package to connect between the $V_{CCQ}$ line and the $GND_Q$ line.                                                                                                                        |

| GND                         | Substrate ground—These lines must be tied to ground.                                                                                                                                                                                                                                                                                                                                                                                                        |

#### **PLL and Clock**

Table 1-6 PLL and Clock Signals

| Signal<br>Name | Signal<br>Type   | State<br>during<br>Reset | Signal Description                                                                                                                                                                                                                                                   |

|----------------|------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| СКІН           | Input            | Input                    | <b>High frequency clock input</b> —This signal provides the high frequency input clock. This clock may be other a CMOS square wave or sinusoid input.                                                                                                                |

| CKIL           | Input            | Input                    | <b>Low frequency clock input</b> —This signal provides the low frequency input clock and should be less than or equal to the frequency of CKIH. This is the default input clock after reset.                                                                         |

| СКО            | Output           | Driven<br>low            | DSP/MCU output clock—This signal provides an output clock synchronized to the DSP or MCU core internal clock phases, according the selected programming option. The choices of clock source and enabling/disabling the output signal are software selectable.        |

| СКОН           | Output           | Driven<br>low            | <b>High frequency clock output</b> —This signal provides an output clock derived from the CKIH input. This signal can be enabled or disabled by software.                                                                                                            |

| PCAP           | Input/<br>Output | Indeter-<br>minate       | <b>PLL capacitor</b> —This signal is used to connect the required external filter capacitor to the PLL filter. Connect one end of the capacitor to PCAP and the other to $V_{CCP}$ . The value of the capacitor is specified in <b>Section 2</b> of this data sheet. |

#### **Address Bus**

Table 1-7

Address Bus Signals

| Signal<br>Names | Signal<br>Type | State<br>during<br>Reset | Signal Description                                                                                                                                                                    |

|-----------------|----------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0-A21          | Output         | Driven<br>low            | Address bus—These signals specify the address for external memory accesses. If there is no external bus activity, A0–A21 remain at their previous values to reduce power consumption. |

#### **Data Bus**

Table 1-8

Data Bus Signals

| Signal<br>Names | Signal<br>Type   | State<br>during<br>Reset | Signal Description                                                                                                                                                                                                                                                     |

|-----------------|------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0-D15          | Input/<br>Output | Input                    | <b>Data bus</b> —These signals provide the bidirectional data bus for external memory accesses. D0–D15 are held in the previous logic state when there is no external bus activity and during hardware reset. This is done with weak "keepers" inside the I/O buffers. |

#### **Bus Control**

Table 1-9

Bus Control Signals

| Signal<br>Name | Signal<br>Type | State<br>during<br>Reset | Signal Description                                                                                                                                                                                                                                                                     |

|----------------|----------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R/W            | Output         | Driven<br>high           | <b>Read/write</b> —This signal indicates the bus access type. A high signal indicates a bus read. A low signal indicates a write to the bus. When accessing memory it can also be used as write enable (WE) signal. When accessing a peripheral chip, the signal acts as a read/write. |

| EB0            | Output         | Driven<br>high           | <b>Enable byte 0</b> —When driven low, this signal indicates access to data byte 0 (D8–D15) during a read or write cycle. This pin may also act as a write byte enable, if so programmed. This output is used when accessing 16-bit wide SRAM.                                         |

| EB1            | Output         | Driven<br>high           | <b>Enable byte 1</b> —When driven low, this signal indicates access to data byte 1 (D0–D7) during a read or write cycle. This pin may also act as a write byte enable, if so programmed. This output is used when accessing 16-bit wide SRAM.                                          |

| ŌĒ             | Output         | Driven<br>high           | <b>Bus select</b> —When driven low, this signal indicates that the current bus access is a read cycle and enables slave devices to drive the data bus with a read.                                                                                                                     |

## **Chip Selects**

Table 1-10

Chip Select Signals

| Signal Name | Signal<br>Type | State<br>during<br>Reset | Signal Description                                                                                                                                                                                                                                                                                        |

|-------------|----------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS0         | Output         | Chip-<br>driven          | Chip select 0—This signal is asserted low based on the decode of the internal address bus bits A[31:24] and is typically used as the external flash memory chip select. After reset, accesses using this CS have a default of 15 wait states.                                                             |

| CS1-CS4     | Output         | Driven<br>high           | Chip select 1-chip select 4—These signals are asserted low based on the decode of the internal address bus bits A[31:24] of the access address.  When not selected as chip select signals, these signals become general purpose outputs (GPOs). After reset, these signals are GPOs that are driven high. |

| CS5         | Output         | Driven<br>low            | Chip select 5—This signal is asserted high based on the decode of the internal address bus bits A[31:24] of the access address.  When not selected as a chip select signal, this signal becomes a GPO. After reset, this signal is a GPO that is driven low.                                              |

### Reset, Mode, and Multiplexer Control

Table 1-11

Reset, Mode, and Multiplexer Control Signals

| Signal Name | Signal<br>Type | State<br>during<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------|----------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET_IN    | Input          | Input                    | Reset input—This signal is an active low Schmitt trigger input that provides a reset signal to the internal circuitry. The input is valid if it is asserted for at least three CKIL clock cycles. This pin has a $47k\Omega$ pull-up resistor. Note: If MUX_CTL is held high, the $\overline{RTS}$ signal of the serial data port (UART) becomes the $\overline{RESET}$ _IN input line. (See Table 1-15 on page 1-26.)                                                                                                                                                                                                                                                  |

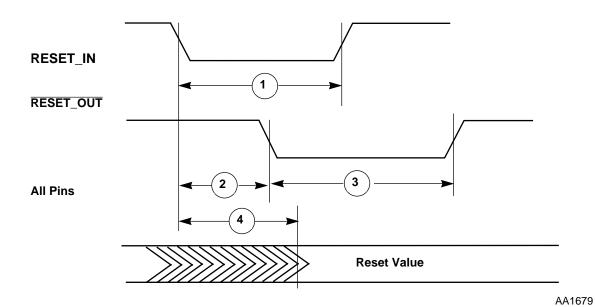

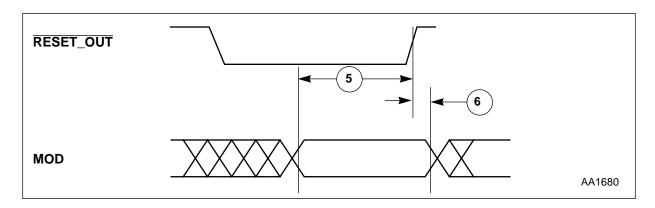

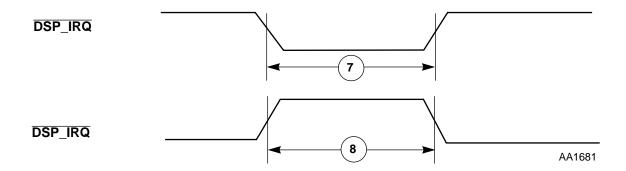

| RESET_OUT   | Output         | Pulled<br>low            | Reset output—This signal is asserted low for at least seven CKIL clock cycles under one of the following conditions:  • RESET_IN is pulled low for at least three CKIL clock cycles  • The alternate RESET_IN signal is enabled by MUX_CTL and is pulled low for at least three CKIL clock cycles  • The watchdog count expires This signal is asserted immediately after the qualifier detects a valid RESET_IN signal, remains asserted during RESET_IN assertion, and is stretched for at least seven more CKIL clock cycles after RESET_IN is deasserted. Three CKIL clock cycles before RESET_OUT is deasserted, the MCU boot mode is latched from the MOD signal. |

| MOD         | Input          | Input                    | Mode select—This signal selects the MCU boot mode during hardware reset. If MOD is driven low at least four CKIL clock cycles before RESET_OUT is deasserted, then the internal MCU ROM ignores the first access and the M•CORE fetches the first word from the first location the external flash memory. If MOD is driven high four CKIL clock cycles before RESET_OUT deassertion, then the internal MCU ROM is enabled and the M•CORE fetches the first word from the first location in the internal ROM.                                                                                                                                                            |

Table 1-11 Reset, Mode, and Multiplexer Control Signals (Continued)

| Signal Name | Signal<br>Type | State<br>during<br>Reset |                                                                                                       | Signal Description                                                                                                                                                                                                                                      |                                                                                                            |

|-------------|----------------|--------------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| MUX_CTL     | Input          | Input                    | alternate set of pins                                                                                 | l—This input allows the dost to be used for RESET_IN, e JTAG signals as defined l                                                                                                                                                                       | the debug control                                                                                          |

|             |                |                          | ]                                                                                                     | Normal                                                                                                                                                                                                                                                  | Alternate                                                                                                  |

|             |                |                          | (MU                                                                                                   | X_CTL low)                                                                                                                                                                                                                                              | (MUX_CTL high)                                                                                             |

|             |                |                          | Interrupt signals 1                                                                                   | INT6/STDA/ <del>DSR</del>                                                                                                                                                                                                                               | TRST                                                                                                       |

|             |                |                          |                                                                                                       | INT7/SRDA/DTR/SCLK                                                                                                                                                                                                                                      | TMS                                                                                                        |

|             |                |                          | Keypad signals                                                                                        | ROW6/SC2A/ <del>DCD</del>                                                                                                                                                                                                                               | DSP_DE                                                                                                     |

|             |                |                          | (See <b>Table 1-14</b> ) on page 1-22)                                                                | ROW7/SCKA/RI                                                                                                                                                                                                                                            | TCK                                                                                                        |

|             |                |                          | Serial Data Port                                                                                      | TxD                                                                                                                                                                                                                                                     | TDO                                                                                                        |

|             |                |                          |                                                                                                       | RxD/IC1                                                                                                                                                                                                                                                 | TDI                                                                                                        |

|             |                |                          | (See <b>Table 1-15</b>                                                                                | RTS/IC2A                                                                                                                                                                                                                                                | RESET_IN                                                                                                   |

|             |                |                          | on page 1-26)                                                                                         | CTS                                                                                                                                                                                                                                                     | MCU_DE                                                                                                     |

|             |                |                          | MUX_CTL is driver  Note: The user is normal and provisions a such a smooth uses to drive (such as the | ven low, the normal function high, the alternate function responsible to ensure that all alternate functions are made in the on-chip had oth switch. The external cover this signal must ensure the JTAG TMS and TRST signs with inactive values during | transition between ade smoothly. No ardware to assure ommand converter hat critical pins als and RESET_IN) |

|             |                |                          | The MUX_CTL sign                                                                                      | nal has an internal 100 k $\Omega$ p                                                                                                                                                                                                                    | oull-down resistor.                                                                                        |

| STO         | Output         | Chip<br>driven           | Soft turn off—This is not affected by re                                                              | is a general purpose outpueset.                                                                                                                                                                                                                         | ıt pin. Its logic state                                                                                    |

For Reset, mode, and MUX control signals equipped with resistors, all pull-ups and pull-downs are automatically disconnected when the pin is an output.

## Interrupts

Table 1-12

Interrupt Signals

| Signal<br>Name | Signal<br>Type     | State<br>during<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------|--------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

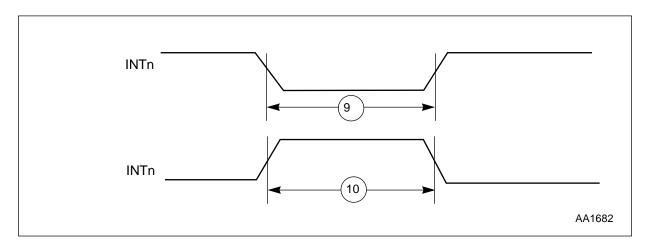

| INT0-INT3      | Input or<br>Output | Input                    | Interrupt 0-interrupt 3—These signals can be programmed as interrupt inputs or GPIO signals. The signals have on-chip 100 $k\Omega$ pull-up resistors.                                                                                                                                                                                                                                                                                                                                            |

|                |                    |                          | As Schmitt trigger interrupt inputs the signals can be programmed to be level sensitive, positive edge-triggered, or negative edge-triggered. When edge-triggered, triggering occurs at a voltage level and is not directly related to the fall time of the interrupt signal; however, as signal fall time of the interrupt signal increases, the probability of generating multiple interrupts due to this noise also increases.  The signals are GPIOs when not programmed as interrupts. After |

|                |                    |                          | reset, the default state for these signals is general purpose input (GPI).                                                                                                                                                                                                                                                                                                                                                                                                                        |

| INT4-INT5      | Input or<br>Output | Input                    | Interrupt 4–interrupt 5—These signals can be programmed as interrupt inputs or GPIO signals, and have $10\text{-}27\text{k}\Omega$ pull-up resistors.                                                                                                                                                                                                                                                                                                                                             |

|                |                    |                          | As Schmitt trigger interrupt inputs, the signals can be programmed to be level sensitive, positive edge-triggered, or negative edge-triggered. When edge-triggered, triggering occurs at a voltage level and is not directly related to the fall time of the interrupt signal; however, as signal fall time of the interrupt signal increases, the probability of generating multiple interrupts due to this noise also increases.                                                                |

|                |                    |                          | The signals are GPIOs when not programmed as interrupts. After reset, the default state for these signals is GPI.                                                                                                                                                                                                                                                                                                                                                                                 |

Table 1-12

Interrupt Signals (Continued)

| Signal<br>Name | Signal<br>Type      | State<br>during<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------|---------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Normal:        |                     |                          | MUX_CTL driven low                                                                                                                                                                                                                                                                                                                                                                                                                 |

| INT6           | Input or<br>Output  | Input                    | Interrupt 6—When selected, this signal can be programmed as an interrupt input or a GPIO signal, and has a $47k\Omega$ pull-up resistor.                                                                                                                                                                                                                                                                                           |

|                |                     |                          | As a Schmitt trigger interrupt input, the signal can be programmed to be level sensitive, positive edge-triggered, or negative edge-triggered. When edge-triggered, triggering occurs at a voltage level and is not directly related to the fall time of the interrupt signal; however, as signal fall time of the interrupt signal increases, the probability of generating multiple interrupts due to this noise also increases. |

| STDA           | Output              |                          | <b>Audio codec serial transmit data</b> (alternate)—When programmed as STDA, this signal transmits data from the serial transmit shift register in the serial audio codec port.                                                                                                                                                                                                                                                    |

|                |                     |                          | Note: When this signal is used as STDA, the primary STDA signal is disabled. (See <b>Table 1-18</b> on page 1-31.)                                                                                                                                                                                                                                                                                                                 |

| DSR            | Output              |                          | <b>Data set ready</b> —When programmed as GPIO output, this signal can be used as the $\overline{DSR}$ output for the serial data port. (See <b>Table 1-15</b> on page 1-26)                                                                                                                                                                                                                                                       |

|                |                     |                          | The signal is a GPIO when not programmed as one of the above functions. After reset, the default state for this signal is GPI.                                                                                                                                                                                                                                                                                                     |

| Alternate:     | MUX_CTL driven high |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TRST           | Input               | Input                    | <b>Test Reset</b> —When selected, this signal acts as the TRST input for the JTAG TAP controller. The signal is a Schmitt trigger input that asynchronously initializes the JTAG test controller when asserted.                                                                                                                                                                                                                    |

|                |                     |                          | Note: When this signal is enabled, the primary TRST signal is disconnected from the TAP controller. (See <b>Table 1-22</b> .)                                                                                                                                                                                                                                                                                                      |

Table 1-12

Interrupt Signals (Continued)

| Signal<br>Name | Signal<br>Type      | State<br>during<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------|---------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Normal:        |                     |                          | MUX_CTL driven low                                                                                                                                                                                                                                                                                                                                                                                                                 |

| INT7           | Input or<br>Output  | Input                    | Interrupt 7—When selected, this signal can be programmed as an interrupt input or a GPIO signal, and has a $47k\Omega$ pull-up resistor.                                                                                                                                                                                                                                                                                           |

|                |                     |                          | As a Schmitt trigger interrupt input, the signal can be programmed to be level sensitive, positive edge-triggered, or negative edge-triggered. When edge-triggered, triggering occurs at a voltage level and is not directly related to the fall time of the interrupt signal; however, as signal fall time of the interrupt signal increases, the probability of generating multiple interrupts due to this noise also increases. |

| SRDA           | Input               |                          | <b>Audio codec serial receive data</b> (alternate)—When programmed as SRDA, this signal receives data into the serial receive shift register in the serial audio codec port.                                                                                                                                                                                                                                                       |

|                |                     |                          | Note: When this signal is used as SRDA, the primary SRDA signal is disabled. (See <b>Table 1-18</b> on page 1-31.)                                                                                                                                                                                                                                                                                                                 |

| DTR            | Input               |                          | <b>Data terminal ready</b> —When programmed as GPIO, this signal is used as the $\overline{DTR}$ positive and negative edge-triggered interrupt input for the serial data port. (See <b>Table 1-15</b> on page 1-26.)                                                                                                                                                                                                              |

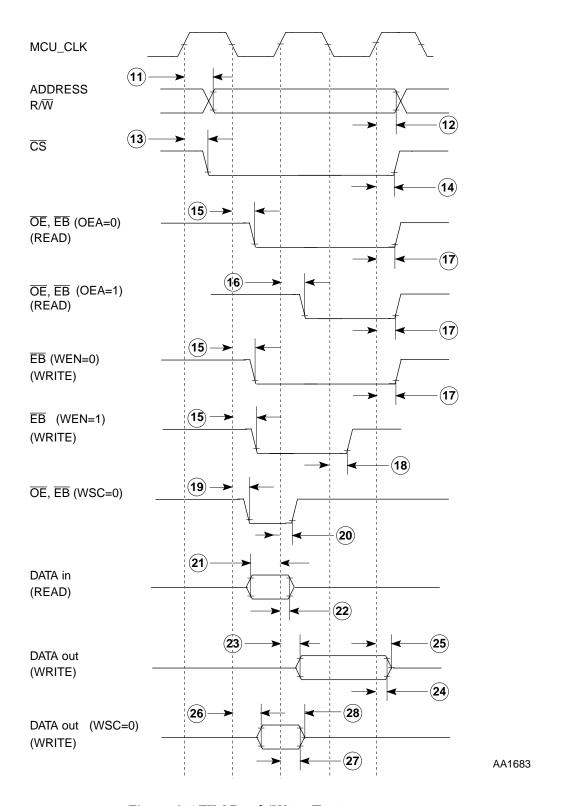

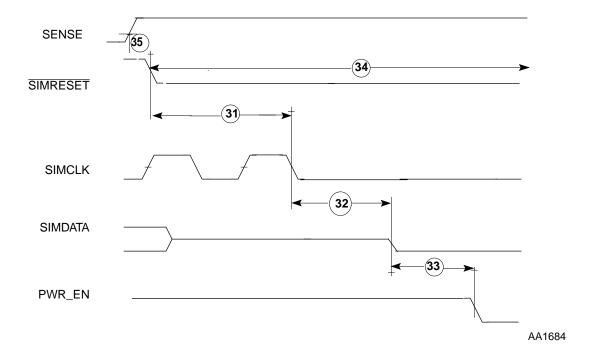

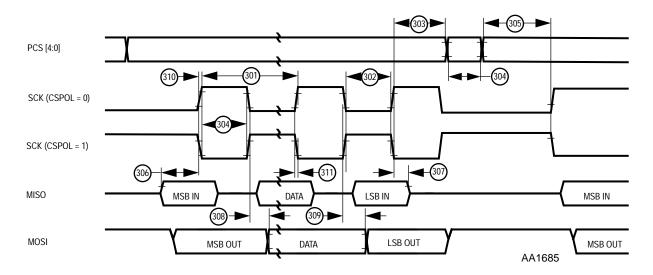

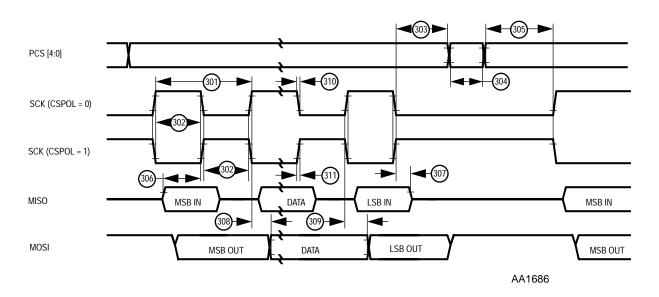

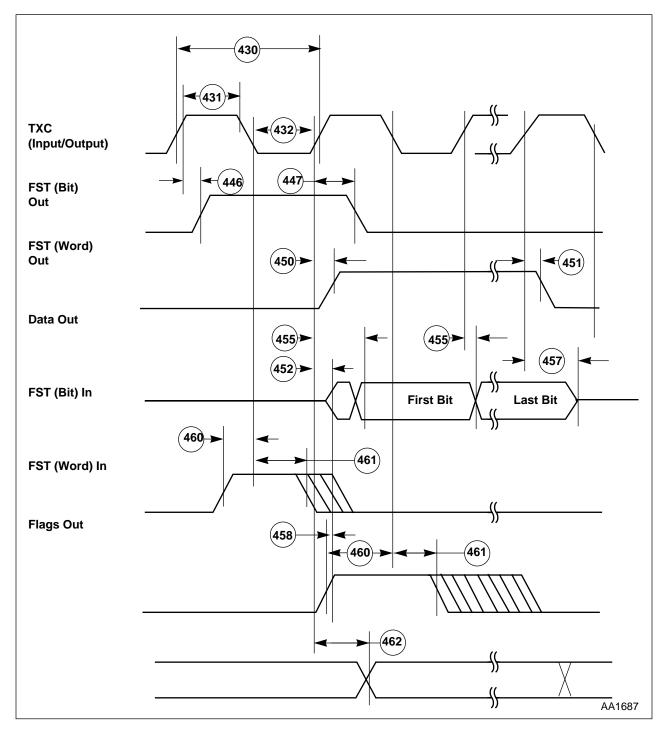

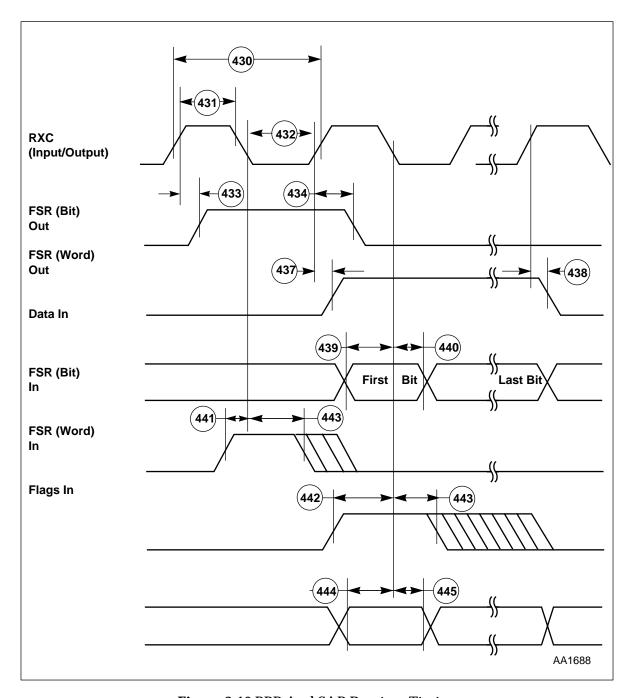

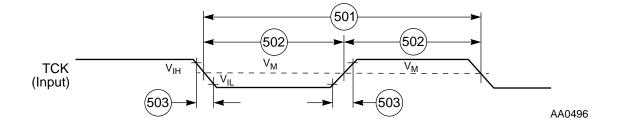

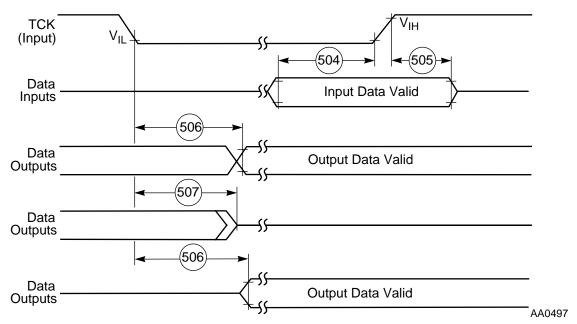

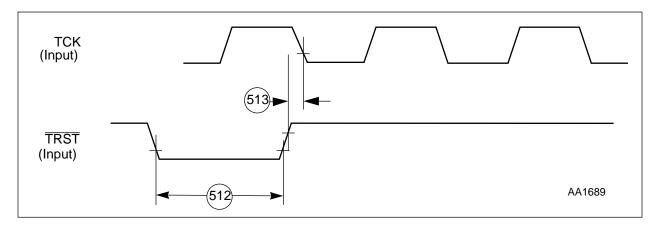

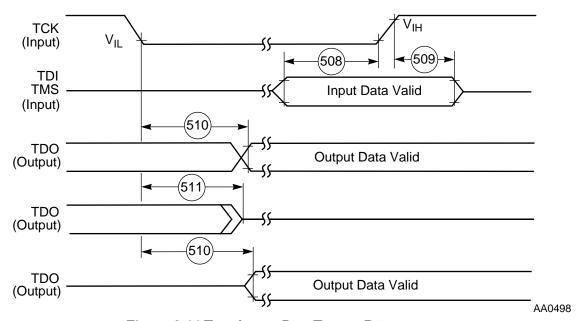

| SCLK           | Input               |                          | <b>Serial clock</b> –When so programmed, this signal provides the input clock for the serial data port (UART). (See <b>Table 1-15</b> on page 1-26.)                                                                                                                                                                                                                                                                               |